# 16-CHANNEL, 12-BIT DATA ACQUISITION SYSTEM

## **FEATURES**

- Multiplexer, instrumentation amp, S/H, A/D and control logic in a 62-pin package

- Three state output buffer

- Instrumentation amp with selectable gain ranging 1 to 1000

- $\blacksquare$  Single-ended (-16) and differential (-8) inputs

- 50 kHz minimum throughput

# **DESCRIPTION**

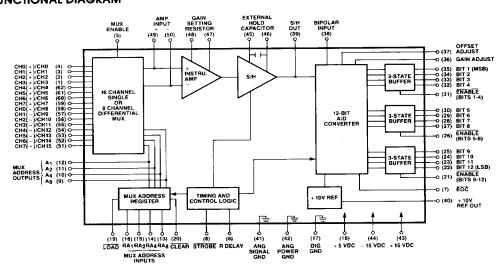

The HS9403-8 and 9403-16 provide complete 12-bit data acquisition functionality in a single, 62-pin package. The 9403 includes 8- or 16-channel multiplexing, a programmable gain instrumentation amplifier, sample-hold circuit, 10V buffered reference, 12-bit  $10\mu$ sec A/D and three-state output buffers.

The 9403 is flexible enough to accept full scale input ranges from  $\pm$  10 mV to  $\pm$  10V. Three-state output buffers allow output data to be accessed in any combination of three 4-bit bytes. Expansion to 32 single-ended or 16 differential inputs can be achieved with the addition of only 2 ICs.

The 9403 is packaged in a 62-pin, hermeticallysealed, ceramic package. Temperature ranges available are 0°C to 70°C for commercial versions and –55°C to 125°C with MIL-STD-883C screening for military grades.

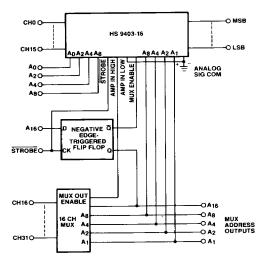

# **FUNCTIONAL DIAGRAM**

# **SPECIFICATIONS**

| (Typical @ +25°C and nominal power                      | er supplies unless otherwise specified)          |

|---------------------------------------------------------|--------------------------------------------------|

| ANALOG INPUTS                                           | HS 9403                                          |

| Number of Input Channels<br>HS 9403-8<br>HS 9403-16     | 8 Differential<br>16 Single-Ended                |

| Input Voltage Range <sup>1</sup><br>Unipolar<br>Bipolar | 0 to +10V<br>±10V                                |

| Common Mode Voltage Range                               | ± 11V min                                        |

| CMRR<br>G = 1 (1 kHz)<br>G = 1000 (60 Hz)               | 74 dB<br>110 dB                                  |

| Input Bias Current                                      | ±50 pA typ                                       |

| Bias Current Drift                                      | Doubles every 10 °C                              |

| Input Offset Current                                    | ± 25 pA typ. ± 100 pA max                        |

| Offset Current Drift                                    | Doubles every 10°C                               |

| Input Offset Voltage                                    | ±2 mV                                            |

| Offset Voltage Drift                                    | (20 + 7G)µ V/°C                                  |

| Voltage Noise (RTI) <sup>2</sup> G = 1 G = 1000         | 150 μ V (RMS)³<br>1.6 μ V (RMS)³                 |

| Input Resistance                                        | 1012                                             |

| Input Capacitance<br>OFF Channel                        | 10 pF                                            |

| ON Channel 9403-8<br>9403-16                            | 50 pF<br>100 pF                                  |

| 2.02.12                                                 | 100 μ                                            |

| DIGITAL INPUTS                                          |                                                  |

| Logic Levels<br>Logic ''1''<br>Logic ''0''              | + 2V min, + 5.3V max<br>- 0.3V min, + 0.8V max   |

| Logic Loading<br>Logic "1"<br>Logic "0"                 | 20 μA<br>-0.2 mA                                 |

| STATIC PERFORMANCE4                                     |                                                  |

| No Missing Codes                                        | Guaranteed over operating temperature range      |

| Integral Linearity Error                                | ± 1/4 LSB typ, ± 1/2 LSB max                     |

| Differential Linearity Error                            | ± 1/4 LSB typ, ± 1/2 LSB max                     |

| Unipolar Offset Error <sup>5</sup>                      | ± 0.025% FSR typ,<br>± 0.1% FSR <sup>6</sup> max |

| Bipolar Zero Errors                                     | ± 0.025% FSR typ,<br>± 0.1% FSR <sup>6</sup> max |

| Gain Errors                                             | ± 0.025% typ, ± 0.2% max                         |

| + 10V REFERENCE                                         |                                                  |

| Output Voltage                                          | + 10.000V ± 10 mV                                |

| Output Voltage Drift                                    | ±3 ppm/°C typ, ±8 ppm/°C max                     |

| DYNAMIC PERFORMANCE                                     |                                                  |

| Throughput Hate                                         | 50 kHz min                                       |

| DINAMIC PERFORMANCE                   |                           |

|---------------------------------------|---------------------------|

| Throughput Rate                       | 50 kHz min                |

| S/H Acquisition Time <sup>7</sup>     | 9 μ sec typ, 10 μ sec max |

| A/D Conversion Time                   | 10 μ sec max              |

| Aperture Delay                        | 25 nsec typ               |

| Sample-Hold Droop                     | 0.1 μ V/μ sec             |

| Feedthrough (@ 1 kHz)8                | ± 0.01% max               |

| MUX Crosstalk (@ 1 kHz)               | – 80 dB min               |

| Strobe Command Pulse Width            | 40 nsec min               |

| Setup Time Digital Inputs to Strobe9  | 50 nsec min               |

| Hold Time Digital Inputs from Strobe9 | 50 nsec max               |

| ENABLE                                |                           |

| Tri State to Valid                    | 40 nsec max               |

| Valid to Tri State                    | 30 nsec max               |

|                                       |                           |

| DRIFT | CHARA | CTERIS      | TICS10 |

|-------|-------|-------------|--------|

| Unici | CHARL | IC I EI IIO | 1100   |

| Integral Linearity     | ±1 ppm/°C typ, ±2 ppm/°C max   |

|------------------------|--------------------------------|

| Differential Linearity | ± 1 ppm/°C typ, ± 2 ppm/°C max |

| Unipolar Offset        | ±3 ppm/°C typ, ±7 ppm/°C max   |

| Bipolar Zero           | ±3 ppm/°C typ, ±10 ppm/°C max  |

| Gain                   | ±8 ppm/°C typ. ±20 ppm/°C max  |

# DIGITAL OUTPUTS

Logic Levels

Fanout

| Logic "1"                                         | 2.4V min                         |

|---------------------------------------------------|----------------------------------|

| Logic "0"                                         | 0.4V max                         |

| Logic Coding<br>Unipolar Ranges<br>Bipolar Ranges | Straight binary<br>Offset binary |

| Fanout                                            | 5 TTL Loads                      |

## **POWER SUPPLIES** Power Supply Range

| + 4.5V to + 5.5V                                                     |

|----------------------------------------------------------------------|

| 55 mA typ, 55 mA max<br>68 mA typ, 60 mA max<br>32 mA typ, 45 mA max |

| 1.4W typ, 2.0W max                                                   |

| 0.005%/% max                                                         |

| 0.01%/% max                                                          |

|                                                                      |

+ 14.5V to + 15.5V

#### TEMPERATURE RANGE

| Operating C-Option | 0°C to +70°C        |

|--------------------|---------------------|

| Operating B-Option | - 55 °C to + 125 °C |

| Storage            | - 65°C to + 150°C   |

#### **ABSOLUTE MAXIMUM RATINGS**

| +VCC                  | -0.5V to + 18V                |

|-----------------------|-------------------------------|

| -VCC                  | + 0.5V to - 18V               |

| VDD                   | -0.3 to +7V                   |

| Analog Input Channels | ±35V                          |

| Digital Inputs        | -0.3 to V <sub>DD</sub> +0.3V |

|                       |                               |

#### NOTES:

- 1. For unity gain

- 2. Referred to input.

- 3. Measured at output of S/H.

- 4. Specifications refer to entire system from MUX input to A/D output with instrumentation amplifier  $G\!=\!1.$

- Initial offset and gain errors are adjustable to zero with optional external potentiometers. 6. FSR = full scale range. Unipolar FSR = 10V, Bipolar FSR = 20V. For a 12-bit system, 1 LSB = 0.024% FSR.

- Includes MUX switching and settling time, instrumentation amp unity gain settling time and S/H acquisition time. Specified for 10V step settling to 0.01% FSR.

- Measured at S/H output with S/H in hold mode. 9. Includes MUX address, MUX enable, clear and load inputs

- 10. Unipolar 10V FSR is the basis for parts per million specifications.

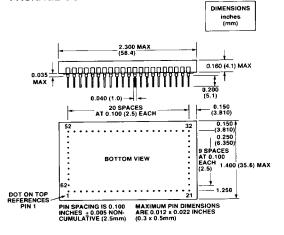

#### PACKAGE OUTLINE

# PIN ASSIGNMENTS

| PIN      | FUNCTION<br>HS 0403 15                   | FUNCTION<br>HS 9403-8 |

|----------|------------------------------------------|-----------------------|

| NO.      | HS 9403-16                               | CH3(+)IN              |

| 1 1      | CH3 IN                                   | CH2(+)IN              |

| 2        | CH2 IN                                   | CH1(+)IN              |

| 3        | CH1 IN                                   | CH0(+)IN              |

| 4        | CHO IN                                   | CHU(+)III             |

| 5        | MUX ENABLE                               |                       |

| 6        | R DELAY                                  |                       |

| 7        | EOC<br>STROBE                            |                       |

| В        | A8                                       |                       |

| 9        | A4 AUX ADDDESS OUT                       |                       |

| 10       | A2 MUX ADDRESS OUT                       |                       |

| 12       | A1                                       |                       |

| 13       | RAB                                      |                       |

| 14       | DAA                                      |                       |

| 15       | RA2 MUX ADDRESS IN                       |                       |

| 16       | RA1                                      |                       |

| 17       | DIGITAL GROUND                           |                       |

| 18       | +5V                                      |                       |

| 19       | LOAD ENABLE                              |                       |

| 20       | CLEAR ENABLE                             |                       |

| 21       | ENABLE (BITS 9-12)                       |                       |

| 22       | BIT 12 OUT (LSB)                         |                       |

| 23       | BIT 11 OUT                               |                       |

| 24       | BIT 10 OUT                               |                       |

| 25       | BIT 9 OUT                                |                       |

| 26       | ENABLE (BITS 5-8)                        |                       |

| 27       | BIT 8 OUT                                |                       |

| 28       | BIT 7 OUT                                |                       |

| 29       | BIT 6 OUT                                |                       |

| 30       | BIT 5 OUT                                |                       |

| 31       | ENABLE (BITS 1-4)                        |                       |

| 32       | BIT 4 OUT                                |                       |

| 33       | BIT 3 OUT                                |                       |

| 34       | BIT 2 OUT                                | ļ                     |

| 35       | BIT 1 OUT (MSB)                          | Ĩ                     |

| 36       | GAIN ADJ                                 |                       |

| 37       | OFFSET ADJ                               | ļ                     |

| 38       | BIPOLAR INPUT                            |                       |

| 39       | SAMPLE/HOLD OUT                          |                       |

| 40       | + 10V REFERENCE OUT ANALOG SIGNAL GROUND |                       |

| 41<br>42 | ANALOG SIGNAL GROUND                     | İ                     |

| 42       | + 15V                                    |                       |

| 44       | - 15V                                    |                       |

| 45       | EXTERNAL HOLD CAP HIGH                   |                       |

| 46       | EXTERNAL HOLD CAP LOW                    |                       |

| 47       | R GAIN LOW                               |                       |

| 48       | R GAIN HIGH                              |                       |

| 49       | INSTRU. AMP (+) INPUT                    |                       |

| 50       | INSTRU. AMP (-) INPUT                    |                       |

| 51       | CH15 IN                                  | CH7(-)IN              |

| 52       | CH14 IN                                  | CH6(-)IN              |

| 53       | CH13 IN                                  | CH5(-)IN              |

| 54       | CH12 IN                                  | CH4(-)IN              |

| 55       | CH11 IN                                  | CH3(-)IN              |

| 56       | CH10 IN                                  | CH2(-)IN              |

| 57       | CH9 IN                                   | CH1(-)IN              |

| 58       | CH8 IN                                   | CH0(-)IN              |

| 59       | CH7 IN                                   | CH7(+)IN              |

| 60       | CH6 IN                                   | CH6(+)IN              |

| 61       | CH5 IN                                   | CH5(+)IN              |

| 62       | CH4 IN                                   | CH4(+)IN              |

# **DIGITAL PIN FUNCTIONS**

| FUNCTION           | PIN NO. | LOGIC<br>STATE           | DESCRIPTION                                                                                        |

|--------------------|---------|--------------------------|----------------------------------------------------------------------------------------------------|

| MUX ENABLE         | 5       | ''0''                    | Disables internal MUX<br>Enables internal MUX                                                      |

| ĒOC                | 7       | "0"<br>"1"<br>"1" to "0" | Signal acquisition cycle in<br>progress<br>A/D conversion in progress<br>Conversion complete       |

| STROBE             | 8       | "1" to "0"               | Initiates acquisition and conversion of analog signal                                              |

| MUX ADDRESS<br>OUT | 9-12    |                          | Output of MUX address<br>register, Straight binary<br>coding                                       |

| MUX ADDRESS<br>IN  | 13-16   | :                        | Selects MUX for random<br>address mode. Straight<br>binary coding                                  |

| LOAD               | 19      | "0"<br>"1"               | Random address mode initiated on falling edge of STROBE Sequential address mode                    |

| CLEAR              | 20      | ''0''                    | Forces MUX address to CHO on next falling edge of STROBE regardless of LOAD and MUX address inputs |

| ENABLE             | 21      | ''0''                    | Enables three-state outputs bits 9-12                                                              |

| (BITS 9-12)        |         | "1"                      | Disables three-state out-<br>puts bits 9-12                                                        |

| ENABLE             | 26      | 0,,                      | Enables three-state output                                                                         |

| (BITS 5-8)         |         | "1"                      | Disables three-state out-<br>puts bits 5-8                                                         |

| ENABLE             | 31      | ''0''                    | Enables three-state outputs outputs bits 1-4                                                       |

| (BITS 1-4)         |         | "1"                      | Disables three-state out-<br>puts bits 1-4                                                         |

# **ANALOG PIN FUNCTIONS**

| FUNCTION                      | PIN NO. | DESCRIPTION                                                                                                                                                                         |

|-------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R DELAY                       | 6       | Connect external resistor to<br>lengthen S/H acquisition time<br>when instrumentation AMP is<br>set for high gain (for normal<br>operation, R DELAY tied to<br>+5V).                |

| GAIN ADJUST                   | 36      | External gain adjust (optional)                                                                                                                                                     |

| OFFSET ADJUST                 | 37      | External offset adjust (optional)                                                                                                                                                   |

| BIPOLAR INPUT                 | 38      | For unipolar operation (0 to<br>+ 10V), connect to pin 39 (S/H<br>OUT). For Bipolar operation<br>(± 10V), connect to pin 40<br>(+ 10V REF OUT)                                      |

| S/H OUTPUT                    | 39      | Sample-Hold output                                                                                                                                                                  |

| + 10V REF OUT                 | 40      | Buffered + 10V reference output                                                                                                                                                     |

| EXTERNAL HOLD<br>CAPACITOR    | 45, 46  | Add external polypropylene, polystyrene or tellon hold capacitor to improve S/H droop rate (optional)                                                                               |

| R GAIN                        | 47, 48  | Optional gain selection point.<br>R=20k/(G-1). Leave open for<br>G=1                                                                                                                |

| INSTRUMENTATION<br>AMP INPUTS | 49, 50  | Use when adding additional external multiplexers for expanded single-ended or differential operation (see Applications Information). Connect pin 50 to analog common for Hs 9403-16 |

# **APPLICATIONS INFORMATION**

#### NOTES:

- Input channels are protected to 20V beyond power supplies.

- To improve sample-hold droop rate, an external hold capacitor may be connected between external hold cap pins 45 and 46. Polypropylene or teflon capacitors are recommended for best results. Acquisition time must be increased accordingly.

3. R GAIN (

$$\Omega$$

) =  $\frac{20,000}{(GAIN-1)}$  (±0.1% typical)

To increase acquisition time allotment, connect a resistor from R DELAY (pin 6) to +5V (pin 18).

R DELAY (Q) =

$$\frac{AMP \text{ settling time}}{10^9}$$

-9K (see Table 1)

| INPUT<br>RANGE | GAIN | R GAIN<br>(R) | AMP<br>SETTLING<br>TIME | R DELAY | THROUGHPUT | SYSTEM<br>ACCURACY |

|----------------|------|---------------|-------------------------|---------|------------|--------------------|

| ± 10V          | 1    | None          | 9 µ sec                 | None    | 55 5 kHz   | 0.009%             |

| ±5V            | 2    | 20.0k         | 9 <b>µ</b> sec          | None    | 55.5 kHz   | 0.009%             |

| ± 2.5V         | 4    | 6 667k        | 9 <b>µ</b> sec          | None    | 55.5 kHz   | 0.009%             |

| ± 1V           | 10   | 2 222k        | 9 µ sec                 | None    | 55.5 kHz   | 0.009%             |

| ± 200 mV       | 50   | 408 2         | 16 µsec                 | 7K      | 40.0 kHz   | 0.010%             |

| ± 100 mV       | 100  | 202 0         | 30 µsec                 | 21K     | 25 6 kHz   | 0.011%             |

| ± 50 mV        | 200  | 100 5         | 60 µsec                 | 51K     | 14.5 kHz   | 0.016%             |

| + 20 mV        | 500  | 40 D8         | 144 µsec                | 135K    | 6.5 kHz    | 0.035%             |

| ± 10 mV        | 1000 | 20 02         | 288 µsec                | 279K    | 3.3 kHz    | 0.069%             |

Table 1. Input Range Parameters

# **MUX CHANNEL ADDRESSING**

The HS 9403-8 and HS 9403-16 are capable of having their input multiplexer channels either randomly or sequentially addressed.

| ADDRESS<br>MODE            | MUX<br>ENABLE | LOAD | CLEAR | ADDRESS<br>INPUTS | ADDRESS<br>OUTPUTS | STROBE     |

|----------------------------|---------------|------|-------|-------------------|--------------------|------------|

| Random                     | 1             | 0    | ,     | Next channel      | On channel         | 1" to "0"  |

| Sequential                 | 1             | 1    | 1     | Don't care        | On channel         | "1" to "0" |

| Free-Running<br>Sequential | 1             | 1    | 1     | Don't care        | On channel         | "1" to "0" |

Table 2.

#### RANDOM ADDRESS

Set LOAD (pin 19) to LOGIC "0". The next falling edge of STROBE will load the MUX channel address present on pin 13 to pin 16. Address inputs must be stable 50 nsec before and after falling edge of STROBE pulse.

# TRIGGERED SEQUENTIAL ADDRESS

Set LOAD (pin 19) and CLEAR (pin 20) to LOGIC "1". Applying a falling edge trigger pulse to STROBE (pin 8). This negative transition causes the contents of the address counter to increment by one followed by a sample-hold acquisition and A/D conversion. Changing digital data appearing at the address inputs will not affect the HS 9403 when it is in the sequential address mode.

# FREE-RUNNING SEQUENTIAL ADDRESS

Set LOAD (pin 19) and CLEAR (pin 20) to LOGIC "1" Connect EOC (pin 7) and STROBE (pin 8) together. The falling edge of EOC will increment channel address. When the EOC goes low, the digital output data is valid for the previous channel for approximately 10 sec while the multiplexer is switching channels and the S/H is acquiring the new signal.

# **VALID OUTPUT**

During the conversion (EOC high), the output of the A/D is changing during the successive approximation sequence. If the outputs are connected to a Data Bus, the enable inputs (pins 21, 26 and 31) must be held high to prevent invalid data from reaching the bus. If data is to be read immediately after conversion is completed, connect EOC to ENABLE (bits 1-4), ENABLE (bits 5-8) and ENABLE (bits 9-12), pins 21, 26 and 31. This will tri-state the outputs during conversion and enable them during the acquisition period.

| ADDRESS INPUTS |    |     | JTS | MUX    | CHANNEL  |            |

|----------------|----|-----|-----|--------|----------|------------|

| A8             | A4 | A2  | A1  | ENABLE | SELECTED |            |

| Х              | Х  | Х   | Х   | 0      | None     |            |

| 0              | 0  | 0   | 0   | 1      | 0        |            |

| 0              | 0  | 0   | 1   | 1      | 1        |            |

| 0              | 0  | 1   | 0   | 1      | 2        |            |

| 0              | 0  | 1 1 | 1   | 1      | 3        |            |

| 0              | 1  | 0   | 0   | 1      | 4        |            |

| 0              | 1  | 0   | 1   | 1      | 5        |            |

| 0              | 1  | 1   | 0   | 1      | 6        |            |

| 0              | .1 | 1   | 1   | 1      | 7        | HS 9403-8  |

| 1              | 0  | Го  | 0   | 1      | 8        |            |

| 1              | 0  | 0   | 1   | 1      | 9        |            |

| 1              | 0  | 1   | 0   | 1      | 10       |            |

| 1              | 0  | 1   | 1   | 1 1    | 11       |            |

| 1              | 1  | 0   | 0   | 1      | 12       |            |

| 1              | 1  | 0   | 1   | 1      | 13       | [          |

| 1              | 1  | 1   | 0   | 1      | 14       |            |

| 1              | 1  | 1   | 1   | 11     | 15       | HS 9403-16 |

Table 3. MUX Channel Addressing

# **APPLICATIONS INFORMATION (continued)**

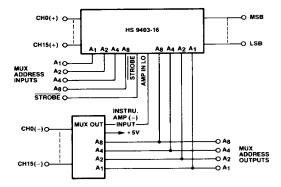

## INPUT EXPANSION

The HS 9403 can be easily expanded to 32 singleended channels or 16 differential channels. When extending channel capacity, the multiplexer settling time must be extended through the use of R DELAY (pin 6).

Figure 2. 16-Channel Differential Input Expansion

Figure 3. 32-Channel Single-Ended Input Expansion

# ORDERING INFORMATION

| MODEL<br>NUMBER   | TEMPERATURE<br>RANGE | DESCRIPTION                                                |

|-------------------|----------------------|------------------------------------------------------------|

| HS 9403C-8        | 0°C to +70°C         | 8 differential input, 12-bit, data acqusition system (DAS) |

| HS 9403C-16       | 0°C to +70°C         | 16 single-ended input, 12-bit,<br>DAS                      |

| HS 9403B-8        | -55°C to +125°C      | 8 differential input, 12-bit, DAS<br>MIL-STD-883C          |

| HS 9403B-16       | -55°C to +125°C      | 16 single-ended input, 12-bit,<br>DAS MIL-STD-883C         |

| HS 9403C-16<br>FP | 0°C to +70°C         | 16 single-ended input in flat pack                         |

| HS 9403B-16<br>FP | -55°C to +125°C      | 16 single-ended input, in flat<br>pack, MIL-STD-883C       |

Specifications subject to change without notice

**CAUTION:** ESD (Electro-Static Discharge) sensitive device. Permanent damage may occur when unconnected devices are subjected to high energy electro-static fields. Unused devices must be stored in conductive foam or shunts. Protective foam should be discharged to the destination socket before devices are removed. Devices should be handled at static safe workstations only. Unused digital inputs must be grounded or tied to the logic supply voltage. Unless otherwise noted, the voltage at any digital input should never exceed the supply voltage by more than 0.5 volts or go below — volts. If this condition cannot be maintained, limit input current on digital inputs by using series resistors or contact Hybrid Systems for technical assistance.

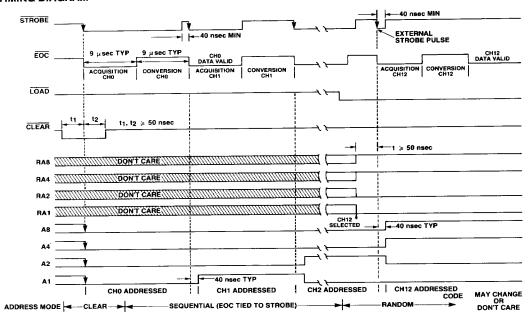

#### **TIMING DIAGRAM**

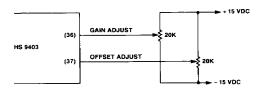

## OFFSET AND GAIN ADJUST CONNECTIONS

The HS 9403 offset and gain adjustments may be made by connecting two 20K trim potentiometers as shown below:

Figure 1. Offset and Gain Adjust Connections

Offset Adjustment — Connect the OFFSET potentiometer as shown above and apply an analog input voltage equivalent to + ½ LSB if operating in a unipolar mode or - FS + ½ LSB if operating in a bipolar mode. While performing repeated conversions, adjust the offset potentiometer down until all output bits are "0". Then adjust up until the LSB just turns to a "1"

Gain Adjust — Connect the gain potentiometer as shown and apply an analog input voltage equivalent to +FS-11/2 LSB. While performing repeated conversions, adjust the gain potentiometer up until all the output bits are "1". Then adjust down until the LSB just turns to "0".

#### NOTE

Since the offset adjustments effects the gain of the system, offset voltage must be adjusted first.

# DIGITAL OUTPUT CODING

|              | UNIPOLAR<br>0 to + 10V | STRAIGHT BINARY |      |      |      |

|--------------|------------------------|-----------------|------|------|------|

| +FS -1 LSB   | + 9.9976               | + 4.9988        | 1111 | 1111 | 1111 |

| +½ FS        | + 5.0000               | + 2.5000        | 1000 | 0000 | 0000 |

| +1 LSB       | + 0.0024               | + 0.0012        | 0000 | 0000 | 0001 |

| ZERO         | 0.0000                 | 0.0000          | 0000 | 0000 | 0000 |

|              | BIPOLAR<br>± 10V       | OFFSET BINARY   |      |      |      |

| + FS - 1 LSB | + 9.9951               | + 4.9976        | 1111 | 1111 | 1111 |

| + ½ FS       | + 5.0000               | + 2.5000        | 1100 | 0000 | 0000 |

| + 1 LSB      | + 0.0049               | + 0.0024        | 1000 | 0000 | 0001 |

| ZERO         | 0.0000                 | 0.0000          | 1000 | 0000 | 0000 |

| - FS + 1 LSB | - 9.9951               | - 4.9976        | 0000 | 0000 | 0001 |

| - FS         | - 10.000               | - 5.0000        | 0000 | 0000 | 0000 |

# **GROUNDING CONSIDERATIONS**

The HS 9403 brings out separate pins for analog power ground, analog signal grounds, and digital ground. All three should be connected together as close to the unit as possible and connected to system analog ground. If the ground pins cannot be connected directly at the package, wide low resistive ground lines should be used and a non-polarized capacitor (0.1 to 1  $\mu$  F) should be connected between analog and digital ground directly at the package.

Internal 0.01  $\mu$ F ceramic decoupling capacitors are used in the device. However, it is advisable to add a 1  $\mu$ F or 10  $\mu$ F tantalum capacitor to each power supply pin from the central ground point to minimize power supply noise problems.