**AN 105**

# Interfacing the 400KHz X24129 Serial EEPROM to the Motorola 68HC11 Microcontroller

by Applications Staff

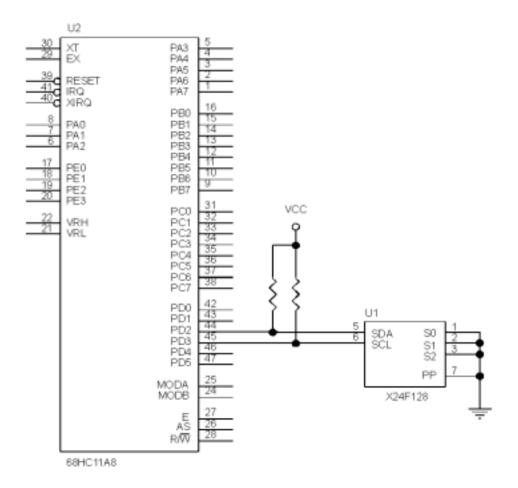

This application note demonstrates how the Xicor X24129 Serial EEPROM can be interfaced to the 68HC11 microcontroller family when connected as shown in Figure 1. The interface uses two general

purpose port D pins to interface to the serial memory. The 68HC11 assembly code listing for this application note can be obtained from the Xicor website at http://www.xicor.com

Figure 1. Typical hardware connection for interfacing an X24129EEPROM to the 68HC11 microcontroller.

```

DESCRIPTION:

* *

* *

This file contains general utility routines written in 68HC11 assembly

** language used to interface the M68HC11 to the XICOR Two-wire X24129

** Serial E2PROM. The interface between the 68HC11 and X24129 device

* *

consists of a clock (SCL) and a bidirectional data line (SDA). The

** communication interface uses 2 pins from Port D(PD3 = SCL and PD2 = SDA).

** Other components may reside on this bus provided that they do not have the

same device identifier byte as the Serial E2PROM.

* *

The following table lists all the subroutines in this file with a brief

* *

description:

* *

* *

START: Generate the start condition

* *

STOP: Generate the stop condition

* *

RESET: Issues the appropriate commands to force device reset

* *

ProgPage: Transfer from RAM buffer to serial memory page

* *

ProgByte: Transfer from RAM buffer to serial memory byte

* *

SeqRead: Read multiple bytes, starting from current address pointer

RandomRead: Read a byte from a specific memory location

ACKPoll: Return when the write cycle completes.

* *

OutACK: Process the acknowledge output cycle

* *

GetACK: process the acknowledge from the slave device

* *

The Main program loop programs a test string into the Serial E2PROM. After

* *

entire string is programmed, the content of the programmed page is read.

** The read data is stored in the internal RAM. A utility program can be

* *

written to verify that the buffer content matches the test string.

* *

**************************

INTERNAL RAM

RAMBASE

EQU

$0000

THE INTERNAL RAM BASE ADDRESS(Default)

RAMBASE

EQU

RAM BUFFER ADDRESS

RAMBuff

RAMBASE+$FF

STACK

EQU

*******************

PROGRAM CONSTANTS

*******************

EQU

$20

PORT D WOM CONTROL BIT

MOWG

SDAbit

EQU

$04

PORT D BITS FUNCTIONING AS BIDIRECTIONAL

SCLbit

EQU

$08

SERIAL DATA (SDA) AND SERIAL CLOCK (SCL)

PageN0

EQU

$00

PAGE NUMBER OF THE SERIAL MEMORY

BLX

EQU

$18

BLX BITS POSITION IN WPR

$02

WEL BIT POSITION IN WPR

WEL

EQU

$04

EQU

RWEL BIT POSITION IN WPR

RWEL

WPEN

EQU

$80

WPEN BIT POSITION IN WPR

EQU

0000010b WEL CONTROL BYTE

WELon

RWELon

EQU

00000110b RWEL CONTROL BYTE

```

| MaxDelay<br>SeqReadSiz                                                                               | EQU<br>e EQU                                                                                     | \$1000<br>16                      | NUMBER OF TIMES TO CHECK ACKNOWLEDGE POLLING<br>BYTE COUNTS TO SHIFT OUT USING SEQ READ                                                                        |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DeviceID<br>HiADDRmask<br>WPR_ADDR<br>PageSize                                                       | EQU<br>EQU<br>EQU<br>EQU                                                                         | \$50<br>\$3F<br>\$FFFF<br>32      | DEVICE SELECT SHIFTED ONE BIT TO THE RIGHT<br>MASK FOR UPPER ADDRESS BYTE<br>WPR PHYSICAL ADDRESS LOCATION (BYTE ACCESS)<br>BYTES PER PAGE                     |

| *****                                                                                                | *****                                                                                            | *****                             | *************                                                                                                                                                  |

| *                                                                                                    | I                                                                                                | NTERNAL REGI                      | STERS AND CONTROL BLOCK                                                                                                                                        |

| ********************                                                                                 |                                                                                                  |                                   |                                                                                                                                                                |

|                                                                                                      |                                                                                                  |                                   |                                                                                                                                                                |

| PORTD                                                                                                | EQU                                                                                              | \$08                              | PORT D DATA REGISTER                                                                                                                                           |

| DDRD                                                                                                 | EQU                                                                                              | \$09                              | DATA DIRECTION REGISTER FOR PORT D                                                                                                                             |

| SPCR                                                                                                 | EQU                                                                                              | \$28                              | SPI CONTROL REGISTER                                                                                                                                           |

| ******                                                                                               | *****                                                                                            | *****                             | ************                                                                                                                                                   |

| * RESET VECTOR ENTRY POINT                                                                           |                                                                                                  |                                   |                                                                                                                                                                |

| *****                                                                                                | *****                                                                                            | *****                             | ***********                                                                                                                                                    |

|                                                                                                      |                                                                                                  |                                   |                                                                                                                                                                |

| ORG                                                                                                  | \$FFFE                                                                                           | RESE                              | T VECTOR ADDRESS TO PROGRAM ENTRY                                                                                                                              |

| FDB                                                                                                  | \$E000                                                                                           | JUMP                              | TO BEGINNING OF EXECUTABLE CODE                                                                                                                                |

| + ACCEMPLE                                                                                           | D DEGLITA                                                                                        | MENTE ODI EN                      | The                                                                                                                                                            |

| " ASSEMBLE                                                                                           | K KEQUIKE                                                                                        | MENT- CPU TY                      | P.E.                                                                                                                                                           |

| P68H11                                                                                               |                                                                                                  |                                   |                                                                                                                                                                |

|                                                                                                      |                                                                                                  |                                   |                                                                                                                                                                |

|                                                                                                      |                                                                                                  |                                   |                                                                                                                                                                |

|                                                                                                      |                                                                                                  |                                   |                                                                                                                                                                |

|                                                                                                      |                                                                                                  |                                   |                                                                                                                                                                |

|                                                                                                      | *****                                                                                            | *****                             | **********                                                                                                                                                     |

| *                                                                                                    |                                                                                                  | ST                                | ART OF USER CODE *                                                                                                                                             |

| *                                                                                                    |                                                                                                  | ST                                |                                                                                                                                                                |

| * *****                                                                                              | *****                                                                                            | ST                                | ART OF USER CODE *                                                                                                                                             |

| * ********  ORG \$E0                                                                                 | *****                                                                                            | ST                                | ART OF USER CODE *                                                                                                                                             |

| * *******  ORG \$E0 MAIN:                                                                            | ******                                                                                           | ST                                | **************************************                                                                                                                         |

| * ********  ORG \$E0                                                                                 | *****                                                                                            | ST                                | ART OF USER CODE *                                                                                                                                             |

| * *******  ORG \$E0 MAIN:  lds                                                                       | ********<br>00<br>#STACK                                                                         | ST<br>******                      | **************************************                                                                                                                         |

| * *******  ORG \$E0 MAIN:  lds                                                                       | ********<br>00<br>#STACK                                                                         | ST<br>******                      | **************************************                                                                                                                         |

| * *******  ORG \$E0 MAIN:  lds                                                                       | ********<br>00<br>#STACK                                                                         | ST<br>*********<br>(FFER BEFORE   | **************************************                                                                                                                         |

| * *******  ORG \$E0 MAIN:  lds  * INITIALI                                                           | ********  00  #STACK  ZE THE BU                                                                  | ST<br>*********<br>IFFER BEFORE   | **************************************                                                                                                                         |

| * *******  ORG \$E0 MAIN: lds  * INITIALI  ldy ldx InitRAM:                                          | ********  00  #STACK  ZE THE BU  #RAMBuff                                                        | ST<br>*********<br>IFFER BEFORE   | * ART OF USER CODE *  ************************  * LOAD STACK POINTER  PROGRAMMING THE CONTENT TO A PAGE  * IY = RAM BUFFER ADDRESS  * IX = TEST STRING ADDRESS |

| * *******  ORG \$E0 MAIN: lds  * INITIALI  ldy ldx                                                   | ********  00  #STACK  ZE THE BU  #RAMBuff                                                        | ST<br>*********<br>IFFER BEFORE   | * ART OF USER CODE *  **********************************                                                                                                       |

| * *******  ORG \$E0 MAIN: lds  * INITIALI  ldy ldx InitRAM: ldaa staa                                | ********  00  #STACK  ZE THE BU  #RAMBuff #TestStr                                               | ST<br>*********<br>IFFER BEFORE   | * ART OF USER CODE *  ************************  * LOAD STACK POINTER  PROGRAMMING THE CONTENT TO A PAGE  * IY = RAM BUFFER ADDRESS  * IX = TEST STRING ADDRESS |

| * *******  ORG \$E0 MAIN: lds  * INITIALI  ldy ldx InitRAM: ldaa staa iny                            | ********  00  #STACK  ZE THE BU  #RAMBuff #TestStr  0,x                                          | ST<br>*********<br>IFFER BEFORE   | **************************************                                                                                                                         |

| * *******  ORG \$E0 MAIN: lds  * INITIALI  ldy ldx InitRAM: ldaa staa iny inx                        | ********  00  #STACK  ZE THE BU  #RAMBuff #TestStr  0,x                                          | ST<br>*********<br>IFFER BEFORE   | **************************************                                                                                                                         |

| * *******  ORG \$E0 MAIN: lds  * INITIALI  ldy ldx InitRAM: ldaa staa iny inx tsta                   | ********  00  #STACK  ZE THE BU  #RAMBuff  #TestStr  0,x 0,y                                     | ST<br>*********<br>IFFER BEFORE   | **************************************                                                                                                                         |

| * *******  ORG \$E0 MAIN: lds  * INITIALI  ldy ldx InitRAM: ldaa staa iny inx tsta bne               | ********  00  #STACK  ZE THE BU  #RAMBuff  #TestStr  0,x 0,y  InitRAM                            | ST<br>*********<br>IFFER BEFORE   | **************************************                                                                                                                         |

| * *******  ORG \$E0 MAIN: lds  * INITIALI  ldy ldx InitRAM: ldaa staa iny inx tsta bne ldx           | ********  00  #STACK  ZE THE BU  #RAMBuff  #TestStr  0,x 0,y  InitRAM  #\$1000                   | ST **********  OFFER BEFORE  Ting | * X***********************************                                                                                                                         |

| * *******  ORG \$E0 MAIN: lds  * INITIALI  ldy ldx InitRAM: ldaa staa iny inx tsta bne ldx bset      | ********  00  #STACK  ZE THE BU  #RAMBuff  #TestStr  0,x  0,y  InitRAM  #\$1000  SPCR,X,#        | ST **********  OFFER BEFORE  Ting | * X***********************************                                                                                                                         |

| * *******  ORG \$E0 MAIN: lds  * INITIALI  ldy ldx InitRAM: ldaa staa iny inx tsta bne ldx bset ldaa | ********  00  #STACK  ZE THE BU  #RAMBuff  #TestStr  0,x  0,y  InitRAM  #\$1000  SPCR,X,#  #\$0C | ST **********  OFFER BEFORE  Ting | * X***********************************                                                                                                                         |

| * *******  ORG \$E0 MAIN: lds  * INITIALI  ldy ldx InitRAM: ldaa staa iny inx tsta bne ldx bset      | ********  00  #STACK  ZE THE BU  #RAMBuff  #TestStr  0,x  0,y  InitRAM  #\$1000  SPCR,X,#        | ST **********  OFFER BEFORE  Ting | * X***********************************                                                                                                                         |

```

staa

PORTD, X

* RESET THE INTERFACE STATE MACHINE

jsr

Reset

ldd

#WPR_ADDR

* READ THE WPR CONTENT AND FIND THE

RandomRead

* BLOCKS THAT ARE LOCKED. IF BOTH

* WPEN BIT AND WP PIN ARE HIGH THEN

bita

#WPEN

bne

WPEN_OFF

* BLx BITS ARE PROTECTED (WRITES ARE

* PERMITTED WHEN WP IS BROUGHT LOW).

... WARNING ...

MAKE SURE THAT WP PIN IS LOW BEFORE ATTEMPTING TO WRITE NEW VALUE TO

THE WPR WHEN WPEN BIT IS SET.

WPEN_OFF:

* SKIP IF THE BLx BITS ARE

bita

#BLX

beq

NO_BLX

* CLEAR (NO BLOCKS ARE PROTECTED)

clra

* CLEAR THE BLOCK LOCK BITS (UNPROTECT

* THE ENTIRE DEVICE), WAIT FOR

jsr

ProgBL

* WRITE OPERATION TO COMPLETE

jsr

ACKPoll

NO_BLX:

* SET THE WRITE ENABLE BIT

jsr

SetWEL

ldd

#WPR_ADDR

* READ THE WPR CONTENT AND

jsr

RandomRead

* CHECK THAT WEL BIT

* IS SET HIGH

#WEL

bita

* ELSE ITS A FAILURE

bne

WRITES_EN

* CHECK THE DEVICE/CONNECTIONS*STOP*

bra

WRITES_EN:

ldd

#PageNO

* D = PAGE NUMBER OF THE SERIAL MEMORY

ldy

* IY = RAM BUFFER ADDRESS

#RAMBuff

* TRANSFER BUFFER CONTENT TO THE PAGE

jsr

ProgPage

ACKPoll

* WAIT TILL COMPLETION OF PAGE PROG.

jsr

ldy

#RAMBuff

* IY = RAM BUFFER ADDRESS

ldaa

#$58

* LOAD THE DATE TO BE WRITTEN IN THE Y

* REGISTER, ASCII 'X'

staa

0,Y

* LOAD THE ADDRESS TO THE ACCUM

ldd

#PageNO

* TRANSFER BUFFER CONTENT TO THE BYTE

jsr

ProgByte

* WAIT TILL COMPLETION OF BYTE PROG.

jsr

ACKPoll

* RESET THE WRITE ENABLE BIT

jsr

ClrWEL

* D = PAGE NUMBER OF THE SERIAL MEMORY

ldd

#PageNO

ldy

#RAMBuff

* IY = RAM BUFFER ADDRESS

* SETUP THE ADDRESS POINTER AND READ

jsr

RandomRead

* FIRST BYTE, SAVE IT TO THE BUFFER

staa

0,Y

* ADJUST THE RAM BUFFER POINTER

iny

ldaa

#.HIGH.PageNO

* LOAD THE UPPER BYTE OF ADDRESS

* SPECIFY BYTE COUNT FOR SEQ. READ OP

ldab

#$20

jsr

SeqRead

* READ/STORE THE REMAINING DATA

* END OF MAIN

bra

*************************

*** Name: SeqRead

*** Description: Read sequentially from the serial memory

*** Function: This subroutine extracts contents of the serial memory and stores

* * *

them into the specified RAM buffer. The total number of bytes to

* * *

read should be provided along with the buffer address. This

* * *

routine assumes that the address pointer has already been

* * *

initialized using the InByte routine.

*** Calls:

Start, SlavAddr, InByte, OutACK, StopRead

*** Input:

IY = RAM Buffer Base Address, A = High Order Address

```

```

B = Number of bytes to read

*** Output:

None

*** Register Usage:

A, B, IY

*************************

SeqRead:

jsr

* START

Start

* [C=1] READ OPERATION BIT

sec

* SEND THE SLAVE ADDRESS BYTE

SlavAddr

jsr

SeqReadNxt:

* START READING FROM THE CURRENT ADDRESS

jsr

InByte

* TOTAL NUMBER OF BYTES TO READ OUT OF

staa

0,Y

* SERIAL MEMORY

iny

decb

beq

SeqReadEnd

* SEND AN ACKNOWLEDGE TO THE DEVICE

jsr

OutACK

bra

SeqReadNxt

SeqReadEnd:

* END OF READ OPERATION

jmp

StopRead

*****************

*** Name: RandomRead

*** Description: Reads content of the serial memory at a specific location.

*** Function: This subroutine sends out the command to read the content of a

* * *

memory location specified in the (D) register.

*** Calls:

Start, InByte, SlavAddr, OutByte, StopRead

*** Input:

D = Address of the byte

*** Output:

A = Read value

*** Register Usage:

Α

*******************

RandomRead:

psha

* SAVE ADDRESS TO STACK

* START

jsr

Start

* [C=0] WRITE OPERATION BIT

clc

* SEND THE SLAVE ADDRESS BYTE

jsr

SlavAddr

* RETRIEVE ADDRESS FROM STACK

pula

* LOAD THE UPPER BYTE OF THE PAGE

jsr

OutByte

tba

* LOAD THE LOWER BYTE OF THE PAGE

* ADDRESS AND SHIFT OUT TO THE DEVICE

OutByte

jsr

* START

jsr

Start

* [C=1] READ OPERATION BIT

sec

* SEND THE SLAVE ADDRESS BYTE

SlavAddr

jsr

* SHIFT IN A BYTE FROM THE DEVICE

jsr

InByte

StopRead

* END OPERATION

jmp

*******************

*** Name: StopRead

*** Description: Terminate read operation

*** Function: This subroutine is called at the end of a read operation. The

***

routine generates the last ACK clock cycle followed by a stop

* * *

command. The last ACK bit clock cycle differs from the normal

ACK bit in that the SDA line is held high. This action notifies

***

the serial memory that it should suspend operation.

*** Calls:

ClockPulse, Stop

*** Input:

None

*** Output:

None

```

October, 2000 www.xicor.com 5 of 14

```

*** Register Usage:

None

**********************

StopRead:

* MAKE SURE THAT THE DATA LINE IS HIGH

bset

PORTD,X,#SDAbit

* CHANGE THE PDx DIRECTION TO OUTPUT

DDRD,X,#SDAbit

jsr

ClockPulse

* END OPERATION

Stop

jmp

*******************

*** Name: ProgPage

*** Description: Update a page of the serial memory

*** Function: This subroutine transfers the contents of the given buffer to the

serial memory. The caller program must supply the page

***

number of the serial memory to update and the base address

* * *

of the RAM buffer.

*** Calls:

Start, SlavAddr, OutByte, Stop

*** Input:

IY = RAM Buffer Base Address, D(AB) = Page Number

*** Output:

None

*** Register Usage: A,B

*************************

ProgPage:

psha

* SAVE ADDRESS TO THE STACK

Start

* START

isr

* [C=0] WRITE OPERATION BIT

clc

* SEND THE SLAVE ADDRESS BYTE

jsr

SlavAddr

* RETRIEVE ADDRESS FROM STACK

pula

OutByte

* LOAD THE UPPER BYTE OF THE PAGE ADDRESS

jsr

tba

* LOAD THE LOWER BYTE OF THE PAGE ADDRESS

* MASK OUT THE UNWANTED LOWER BITS

anda

#$0E0

* AND SHIFT OUT TO THE DEVICE

jsr

OutByte

* TRANSFER CONTENT OF THE RAM BUFFER

ldab

#PageSize

ProgPageNxt:

* TO THE SERIAL MEMORY MEMORY

ldaa 0,Y

* IY SHOULD BE POINTING TO THE BUFFER

jsr

OutByte

ldaa

#$0FF

* COVER UP YOUR TRACKS AS BUFFER IS

* READ AND STORED TO THE SERIAL MEMORY

staa

0,Y

* TOTAL NUMBER OF BYTES TRANSFERED

iny

* TO THE SERIAL MEMORY SHOULD NOT EXCEED

decb

bne

ProgPageNxt

* THE PAGE SIZE

* END OF THE OPERATION

jmp

Stop

*************************

*** Name: ProgByte

*** Description: Update a byte of the serial memory

*** Function: This subroutine transfers a byte located in the Y register to the

serial memory.

***

*** Calls:

Start, SlavAddr, OutByte, Stop

*** Input:

IY = RAM Buffer Base Address,

*** Output:

None

*** Register Usage:

A,B

*****************

ProgByte:

```

October, 2000 www.xicor.com 6 of 14

\*\*\* Register Usage:

A, IY

#### **Application Note**

```

psha

* SAVE ADDRESS TO THE STACK

* START

jsr

Start

* [C=0] WRITE OPERATION BIT

clc

* SEND THE SLAVE ADDRESS BYTE

jsr

SlavAddr

* RETRIEVE ADDRESS FROM STACK

pula

* LOAD THE UPPER BYTE OF THE PAGE ADDRESS

jsr

OutByte

* LOAD THE LOWER BYTE OF THE PAGE ADDRESS

tba

* AND SHIFT OUT TO THE DEVICE

jsr

OutByte

* TO THE SERIAL MEMORY MEMORY

ldaa

0,Y

* IY SHOULD BE POINTING TO THE BYTE DATA

jsr

OutByte

* END OF THE OPERATION

Stop

jmp

*************************

*** Name: EnProgWPR

*** Description: Enable updates to Write Protect Register (WPR)

*** Function: This subroutine writes the appropriate sequence to the serial memory

to enable updating of the WPR. The ProgWPEN and ProgBL routines

***

must call this subroutine before writes to the WPR are allowed.

* * *

Once this sequence is activated, the only way to exit this mode

***

is by writing to the WPR or resetting the serial memory.

*** Calls:

RandomRead, SetWEL, SetRWEL

*** Input:

None

*** Output:

A = INITIAL WPR VALUE

A, B

*** Register Usage:

***********************

EnProgWPR:

ldd

#WPR_ADDR

* READ THE WPR CONTENT AND

* TEST THE STATUS OF

jsr

RandomRead

bita

#WEL

* THE WEL BIT AND

bne

ProgWPR_1

* SKIP IF ITS SET

psha

* ALL WRITES TO THE WPR ARE DISALLOWED

* WHEN THE WEL IS CLEAR, SEND SET WEL

jsr

SetWEL

* COMMAND

pula

ProgWPR_1:

bita

#RWEL

* CHECK THE RWEL BIT AND

* SKIP IF ITS SET

bne

ProgWPR_2

psha

* WRITING TO BLOCK-LOCK BITS OR WPEN

* BIT REQUIRE THAT RWEL TO BE SET,

SetRWEL

jsr

* SEND SET RWEL COMMAND

pula

ProgWPR_2:

rts

*******************

*** Name: ProgBL

*** Description: Update Block Lock bits in WPR of the serial memory

*** Function: This subroutine writes to the WPR of the serial memory and

***

changes the BL1:0. The caller program must supply the new values

***

for the BL1:0 bits. This routine retains the original state of

* * *

the WPEN bit.

*** Calls:

AddrWPR, EnProgWPR, OutByte, Stop

*** Input:

A[1:0] = BL[1:0]

*** Output:

None

```

October, 2000 www.xicor.com 7 of 14

```

*****************************

ProgBL:

anda

#$03

* MASK OUT THE UNWANTED BITS

* SHIFT THE BLx BITS TO THE

asla

asla

* BIT POSITIONS 4:3

asla

* SAVE THE BLx NEW VALUES AND

psha

* ENABLE WRITING TO THE WPR

EnProgWPR

jsr

* CREATE THE DATA PATTERN BY MASKING

#$9A

anda

* IN THE DESIRED BIT PATTERN AND

oraa

#$02

* SAVING STATUS OF WPEN BIT

tsy

* SET THE BLx BITS PER REQUESTED PATTERN

О,у

oraa

О,у

* SAVE THE WPR VALUE ONTO THE STACK

staa

AddrWPR

* GENERATE WPR WRITE COMMAND

jsr

* SHIFT OUT WPR PATTERN

pula

jsr

OutByte

* TO THE DEVICE

jmp

Stop

*******************

*** Name: ProgWPEN

*** Description: Update Write Protect Enable bit in WPR of the serial memory

*** Function: This subroutine writes to the WPR of the serial memory and

***

changes the WPEN bit. The caller program must supply the new

***

value of the WPEN bit. The state of the BL1:0 bits are preserved.

*** Calls:

AddrWPR, EnProgWPR, OutByte, Stop

*** Input:

*** Output:

None

*** Register Usage:

A, IY

******************

ProgWPEN:

* LOAD THE STATUS FLAGS

clra

* MASK OUT THE UNWANTED BITS

rora

* SAVE THE WPEN BIT NEW VALUE AND

psha

* ENABLE WRITING TO THE WPR

EnProgWPR

jsr

* CREATE THE DATA PATTERN BY MASKING

anda

#$9A

#$02

* IN THE DESIRED BIT PATTERN AND

oraa

* SAVING STATUS OF WPEN BIT

tsy

* SET THE WPEN BIT PER AS REQUESTED

oraa

0,у

* SAVE THE WPR VALUE ONTO THE STACK

staa 0,y

AddrWPR

* GENERATE WPR WRITE COMMAND

jsr

* SHIFT OUT WPR PATTERN

pula

OutByte

* TO THE DEVICE

isr

jmp

Stop

*************************

*** Name: SetWEL

*** Description: Set the Write Enable Latch (WEL) bit in the WPR of the serial memory.

*** Function: This subroutine writes to the WPR of the serial memory and

***

sets the WEL bit.

*** Calls:

AddrWPR, OutByte, Stop

*** Input:

NONE

*** Output:

NONE

*** Register Usage:

```

October, 2000 www.xicor.com 8 of 14

```

SetWEL:

* GENERATE WPR WRITE COMMAND

jsr

AddrWPR

* SHIFT OUT WEL-ON PATTERN

ldaa

#WELon

* TO THE DEVICE

jsr

OutByte

jmp

Stop

*******************

*** Name: ClrWEL

*** Description: Reset the Write Enable Latch (WEL) bit in the WPR of the serial memory.

*** Function: This subroutine writes to the WPR of the serial memory and

resets the WEL bit.

*** Calls:

AddrWPR, OutByte, Stop

*** Input:

NONE

*** Output:

NONE

*** Register Usage:

*******************

ClrWEL:

jsr

AddrWPR

* GENERATE WPR WRITE COMMAND

* SHIFT OUT WEL-OFF PATTERN

clra

* TO THE DEVICE

jsr

OutByte

jmp

Stop

*****************

*** Name: SetRWEL

*** Description: Set Register Write Enable Latch bit in the WPR of the serial memory.

*** Function: This subroutine writes to the WPR of the serial memory and

***

sets the RWEL bit.

AddrWPR, OutByte, Stop

*** Calls:

*** Input:

NONE

*** Output:

NONE

*** Register Usage:

*************************

SetRWEL:

AddrWPR

* GENERATE WPR WRITE COMMAND

jsr

ldaa #RWELon

* SHIFT OUT RWEL-ON PATTERN

* TO THE DEVICE

jsr OutByte

jmp

Stop

*************************

*** Name: AddrWPR

*** Description: Initiate write operation to the WPR of the serial memory.

*** Function: This subroutine issues the WPR address and write instruction

***

to the serial memory.

*** Calls:

Start, SlavAddr, OutByte

*** Input:

NONE

*** Output:

NONE

*** Register Usage:

A,B

*************************

AddrWPR:

ldd

#WPR_ADDR

psha

* SAVE ADDRESS TO STACK

```

October, 2000 www.xicor.com 9 of 14

```

jsr Start

* START [ C = OPERATION BIT ]

* [C=0] WRITE OPERATION BIT

clc

jsr

SlavAddr

* SEND THE SLAVE ADDRESS BYTE

* RETRIEVE ADDRESS FROM STACK

pula

OutByte

* LOAD THE UPPER BYTE OF ADDRESS

jsr

* LOAD THE LOWER BYTE OF ADDRESS

tba

OutByte

* AND SHIFT OUT TO THE DEVICE

jmp

*************************

*** Name: SlavAddr

*** Description: Build the slave address for the serial memory.

*** Function: This subroutine concatenates the bit fields for Device ID,

the high address bits and the command bit. The resultant

byte is then transmitted to the serial memory.

*** Calls:

OutByte

*** Input:

D(AB) = Page number

***

C = COMMAND BIT (=0 WRITE, =1 READ)

*** Output:

None

*** Register Usage:

SlavAddr:

ldaa #$50 * LOAD DEVICEID INTO ACCUM

rola * MERGE THE COMMAND BIT

jmp OutByte * SEND THE SLAVE ADDRESS

************************

*** Name: OutByte

*** Description: Sends a byte to the serial memory

*** Function: This subroutine shifts out a byte, MSB first, through the

* * *

assigned SDA/SCL lines on port D.

*** Calls:

ClockPulse, GetACK

*** Input:

A = Byte to be sent

*** Return Value:

None

*** Register Usage:

*******************

OutByte:

DDRD,X,#SDAbit

* CHANGE THE PDx DIRECTION TO OUTPUT

bset

sec

OutByteNxt:

* SHIFT OUT THE BYTE, MSB FIRST

rola

bcc

OutByte0

bset.

PORTD, X, #SDAbit

OutByte1

bra

OutByte0:

bclr

PORTD, X, #SDAbit

OutByte1:

jsR

ClockPulse

* CLOCK THE DATA INTO THE SERIAL MEMORY

#10000000b

* MEMORY

cmpa

* LOOP IF ALL THE BITS HAVE

clc

* NOT BEEN SHIFTED OUT

bne

OutByteNxt

* CHECK FOR AN ACK FROM THE DEVICE

jmp

GetACK

```

October, 2000 www.xicor.com 10 of 14

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

```

*** Name: InByte

*** Description: Shifts in a byte from the serial memory

*** Function: This subroutine shifts in a byte, MSB first, through the

***

assigned SDA/SCL lines on port D. After the byte is received

* * *

this subroutine does not send out an ACK bit to the serial memory.

*** Calls:

ClockPulse

*** Input:

None

*** Return Value:

A = Received byte

*** Register Usage:

Α

***********************

InByte:

ldaa

#0000001b

DDRD,X,#SDAbit

* CHANGE THE PDx DIRECTION TO INPUT

bclr

InByteNxt:

ClockPulse

* CLOCK THE SERIAL MEMORY MEMORY AND SHIFT

* INTO ACC. THE LOGIC LEVEL ON THE SDA

rola

bcc

InByteNxt

* LINE. THE DEVICE OUTPUTS DATA ON SDA,

* MSB FIRST

rts

*************************

*** Name: ClockPulse

*** Description: Generate a clock pulse

*** Function: This subroutine forces a high-low transition on the

* * *

assigned SCL line on port D. It also samples the SDA

* * *

line state during high clock period.

*** Calls:

None

*** Input:

None

*** Return Value:

C = SDA line status

*** Register Usage:

None

*******************

ClockPulse:

* FORCE SCL LINE HIGH. BASED

bset PORTD, X, #SCLbit

* ON AN 8MHz CRYSTAL FREQ. THE SYSTEM

nop

nop

clc

* BUS CYCLE TIME IS 0.5 MICROSEC.

PORTD,X,#SDAbit,ClockPulseLo *

brclr

sec

ClockPulseLo:

bclr PORTD, X, #SCLbit * LOWER THE CLOCK LINE

*******************

*** Name: OutACK

*** Description: Send out an ACK bit to the serial memory

*** Function: This subroutine changes the direction of the SDA pin on port D

***

and then clocks an ACK bit to the serial memory. The ACK

* * *

cycle acknowledges a properly received data by lowering the

* * *

SDA line during this period (9th clock cycle of a received

* * *

byte). The direction of the SDA pin is programmed as input

***

prior to returning to the caller.

*** Calls:

ClockPulse

*** Input:

None

```

```

*** Return Value:

None

*** Register Usage:

None

OutACK:

PORTD,X,#SDAbit

bclr

* MAKE SURE THAT THE DATA LINE IS LOW

* CHANGE THE PDx DIRECTION TO OUTPUT

bset

DDRD,X,#SDAbit

ClockPulse

ami

*******************

*** Name: GetACK

*** Description: Clock the serial memory for an ACK cycle

*** Function: This subroutine changes the direction of the SDA pin on port D

and then clocks the serial memory. It returnes the sampled

* * *

logic level on the SDA during high clock cycle. The serial memory

* * *

acknowledges a properly received command/data by lowering the

***

SDA line during this period (9th clock cycle of a transmitted

***

byte). If the SDA state is HIGH, it signifies that either it

***

did not receive the correct number of clocks or it's stuck in

previously initiated write command,

*** Calls:

ClockPulse

*** Input:

None

*** Return Value:

C = ACKnowledge bit

*** Register Usage:

None

******************

GetACK:

DDRD,X,#SDAbit

bclr

* CHANGE THE PDx DIRECTION TO INPUT

* CLOCK THE SERIAL MEMORY

jsr

ClockPulse

DDRD,X,#SDAbit

* CHANGE THE PDx DIRECTION TO OUTPUT

bset

*******************

*** Name: ACKPoll

*** Description: Wait for an ACK from the serial memory

*** Function: This subroutine sends a slave address to the serial memory and

* * *

monitors the SDA for an ACK signal. It returns if a low

* * *

logic level is detected on the SDA during high clock cycle of

the acknowledge cycle. The serial memory does not respond to any

***

commands with an acknowledge bit while the store operation

* * *

is in progress. If no ACK is received another slave address is

***

sent to the serial memory. The number of iteration is specified

by the MaxDelay constant.

*** Calls:

Start, SlavAddr, Stop

*** Input:

None

*** Return Value:

C = ACKnowledge bit [=0 ACK ,=1 No ACK was received]

*** Register Usage: A, B, IY

***********

*********

ACKPoll:

* LOAD MAX NO. OF ACK POLLING CYCLE

ldy

#MaxDelay

ACKPollnxt:

jsr

Start

* START THE ACK POLL CYCLE AND

ldd

#PageNO

* D = PAGE NUMBER OF THE SERIAL MEMORY

* [C=0] WRITE OPERATION BIT

clc

SlavAddr

* SEND THE SLAVE ADDRESS. THEN

isr

```

```

* OPERATION BY A STOP CONDITION.

isr

Stop

ACKPollExit

* EXIT IF THE ACK WAS RECEIVED

bcc

dey

* LOOP WHILE THE MAXIMUM NO. OF CYCLES

bne

ACKPollnxt

ACKPollExit:

rts

*******************

*** Name: Start

*** Description: Send a start command to the serial memory

*** Function: This subroutine generates a start condition on the bus. The start

condition is defined as a high-low transition on the SDA

***

line while the SCL is high. The start is used at the beginning

***

of all transactions.

*** Calls:

None

*** Input:

None

*** Return Value:

*** Register Usage:

None

*************************

Start:

* FORCE THE SDA LINE HIGH

PORTD,X,#SDAbit

bset

PORTD,X,#SCLbit

PORTD,X,#SDAbit

* FORCE THE SCL CLOCK LINE HIGH

bset

* BEFORE TAKING THE SDA LOW

bclr

nop

nop

nop

nop

PORTD, X, #SCLbit * FORCE THE SCL LOW

bclr

*************************

*** Name: Stop

*** Description: Send stop command to the serial memory

*** Function: This subroutine generates a stop condition on the bus. The stop

condition is defined as a low-high transition on the SDA

***

line while the SCL is high. The stop is used to indicate end

of current transaction.

*** Calls:

None

*** Input:

None

*** Return Value:

None

*** Register Usage:

None

*************************

Stop:

PORTD,X,#SDAbit

* FORCE THE SDA LOW BEFORE TAKING

bclr

* THE SCL CLOCK LINE HIGH

PORTD,X,#SCLbit

bset

nop

nop

nop

nop

PORTD, X, #SDAbit * FORCE THE SDA HIGH (IDLE STATE)

bset

rts

*****

*** Name: Reset

```

October, 2000 www.xicor.com 13 of 14

END

### **Application Note**

```

*** Description: Resets the serial memory

*** Function: This subroutine is written for the worst case. System interruptions

***

caused by brownout or soft error conditions that reset the main

* * *

CPU may have no effect on the internal Vcc sensor and reset

* * *

circuit of the serial memory. These are unpredictable and

* * *

random events that may leave the serial memory interface

* * *

logic in an unknown state. Issuing a Stop command may not be

* * *

sufficient to reset the serial memory.

*** Calls:

Start, Stop

*** Input:

None

*** Return Value:

None

*** Register Usage:

В

*************************

Reset:

ldab

* APPLY 10 CLOCKS TO THE DEVICE. EACH

#$0A

ResetNxt:

jsr

Start

* CYCLE CONSISTS OF A START/STOP

* THIS WILL TERMINATE PENDING WRITE

jsr

Stop

decb

* COMMAND AND PROVIDES ENOUGH CLOCKS

* FOR UNSHIFTED BITS OF A READ

bne

ResetNxt

* OPERATION

rts

TestString: FCC

'xICOR MAKES IT MEMORABLE!'

FCB

$00

************************

*** END OF X24320/640/128 SERIAL MEMORY INTERTERFACE SOURCE CODE

*************************

```

October, 2000 www.xicor.com 14 of 14