### **FEATURES**

- Centronics®-compatible

- Up to 250 kbytes/second transfer rate

- 128-byte FIFO

- Improved interrupt schemes

- Vectored interrupt to allow jump into proper service routine

- Interrupt on FIFO threshold

- Interrupts on timer expiration and external status, e.g., PAPER EMPTY, ERROR, TIMEOUT, etc.

- Programmable FIFO threshold for receive and transmit

- Bi-directional operation

- Independent general-purpose timer

- Multiple CL-CD1190s can be cascaded using interrupt daisy-chain scheme

- Programmable strobe and acknowledge widths from 0.64 μs to 40.8 μs

- 6 general-purpose I/O pins

- 3 inputs and 3 outputs

#### Other Features

- Local loopback capability

- System clock up to 25 MHz

- Packaged in a 68-pin PLCC

- Pin-compatible with the CL-CD1400

- Advanced, low-power CMOS process technology

# Intelligent Printer/Scanner Interface Controller

### **OVERVIEW**

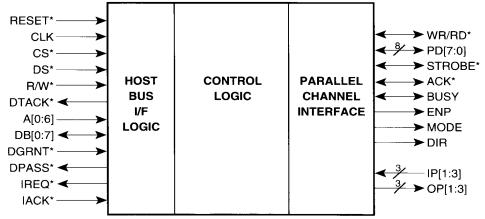

The CL-CD1190 is a flexible, buffered interface controller for parallel data transfer to and from printers and scanners. It provides a 128-byte FIFO with the necessary logic for both the parallel interface and an interrupt or polled host interface. It also provides a flexible parallel interface compatible with industry-standard specifications, such as those used on Centronics high-speed line printers.

The interface is extended to accommodate bi-directional devices such as optical page scanners. The CL-CD1190 is flexible enough to be used on either the controller or peripheral side of a parallel interface, providing a high-speed solution for both controller and peripheral manufacturers. Two CL-CD1190s can be connected to provide a simple, but fast bi-directional parallel connection between two hosts.

(cont. next page)

## Functional Block Diagram

(\*) denotes a negative true signal

October 1993

038566 \_ \_ \_

### **OVERVIEW** (cont.)

Other parallel controllers provide nothing more than a temporary holding register. They have no FIFO storage, and the host CPU must manipulate the handshake signals directly — often causing one or more interrupts per byte. Host CPU overhead with these controllers is very high.

The most important advantage in using the CL-CD1190 is the reduction in CPU overhead. The CL-CD1190 automatically handles the handshake signals, and the deep FIFO allows the host to transfer up to 128 bytes without further intervention. The CL-CD1190 can operate in either interrupt- or polled-mode environments.

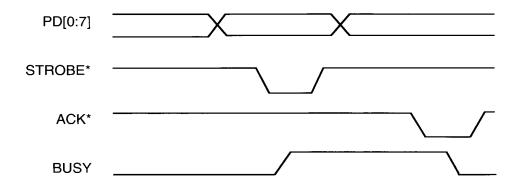

For example, suppose the CL-CD1190 is used to send data in an interrupt-driven system. When the host receives an interrupt, it immediately transfers 128 bytes to the CL-CD1190. The CL-CD1190 will then automatically present each byte on the parallel

data lines, wait for specified setup time, and assert STROBE\* for the specified duration. The CL-CD1190 then waits for the ACK\* signal back from the printer, and presents the next byte to the printer. It repeats this until the FIFO is empty, and only then does it generate another interrupt to the host.

The CL-CD1190 can be programmed with several options. Full or partial handshake can be specified, and the widths of the key handshake pulses (STROBE\* and ACK\*) are determined by the values programmed in appropriate registers. In the transmit direction, the CL-CD1190 can optionally be programmed to change <CR> characters to <NL> characters, and/or insert a <CR> before each <NL>.

Three general-purpose input pins, three output pins, and the on-chip timer provide additional flexibility for various applications.

### **CL-CD1190 Timing Diagram**

(\*) denotes a negative true signal

### **Industry Standard Compatibility**

| CL-CD1190                                                                            | Centronics<br>Peripheral                                              | Dataproducts<br>Peripheral                                            | Hewlett Packard<br>Controller                                                                        |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Data Signals                                                                         |                                                                       |                                                                       |                                                                                                      |

| PD0-I/O<br>PD1-I/O<br>PD2-I/O<br>PD3-I/O<br>PD4-I/O<br>PD5-I/O<br>PD6-I/O<br>PD7-I/O | D1-I<br>D2-I<br>D3-I<br>D4-I<br>D5-I<br>D6-I<br>D7-I<br>D8-I-optional | D1-I<br>D2-I<br>D3-I<br>D4-I<br>D5-I<br>D6-I<br>D7-I<br>D8-I-optional | DATA1-I/O<br>DATA2-I/O<br>DATA3-I/O<br>DATA4-I/O<br>DATA5-I/O<br>DATA6-I/O<br>DATA7-I/O<br>DATA8-I/O |

| Control Signals                                                                      |                                                                       |                                                                       |                                                                                                      |

| BUSY-I/O<br>STROBE*-I/O<br>WR/RD*-I/O<br>ACK*-I/O                                    | BUSY-O<br>STROBE*-I<br>—<br>ACKNLG*-O                                 | READY-O<br>STROBE*-I<br>—<br>DEMAND*-O                                | BUSY-I/O<br>nSTROBE-I/O<br>WR/RD*-O<br>nACKNLG-I                                                     |

| Auxiliary Control Signals                                                            |                                                                       |                                                                       |                                                                                                      |

| IP [1,2,3]<br>OP [1,2,3]<br>—<br>ENP,<br>MODE, DIR                                   | FAULT*-O<br>PE-O<br>SLCT-O<br>—<br>INPUT-PRIME*-I                     | PARITY-ERROR*-O<br>PAPER-O<br>ON-LINE-O<br>INPUT-PRIME*-I             | nFAULT-I<br>ERROR-I<br>SELECT-I<br>nRESET*-O<br>nSELECTIN-O                                          |

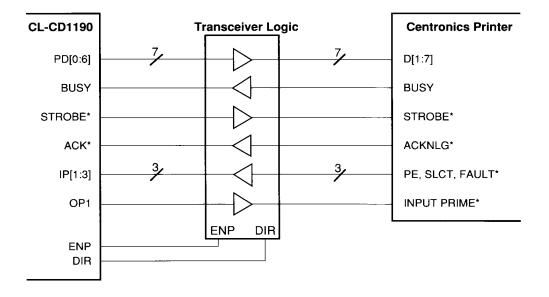

### **Applications Example — Centronics Printer Interface**