**User's Manual**

# V831<sup>™</sup>

32-bit Microprocessor

Hardware

μ**PD705101**

Document No. U12273EJ4V0UM00 (4th edition) Date Published January 1999 N CP(K)

© NEC Corporation 1997 Printed in Japan [MEMO]

# **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

# **(2)** HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

V830, V831, and V830 family are trademarks of NEC Corporation.

Windows is either a registered trademark or a trademark of Microsoft Corporation in the United State and/or other countries.

UNIX is a registered trademark licensed by X/Open Company Limited in the US and other countries.

# The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

# MAJOR REVISIONS IN THIS EDITION

| Page   | Contents                                                                         |

|--------|----------------------------------------------------------------------------------|

| p. 35  | Change of 3.1 Internal Peripheral I/O Space                                      |

| p. 50  | Addition of 4.7 Interrupt Requests by External Input Pins                        |

| p. 51  | Change of the description in 5.2 External I/O Cycle                              |

| p. 64  | Change of the description in 5.5 (4) Classification by data bus width            |

| p. 86  | Change of the description in 6.2 Address Space and Block                         |

| p. 92  | Addition of 6.4 Wait Control by READY pin                                        |

| p. 118 | Change of description in 8.7.3 Request from internal peripheral hardware         |

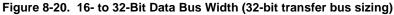

| p. 123 | Change of Figure 8-20. 16- to 32-Bit Data Bus Width (32-bit transfer bus sizing) |

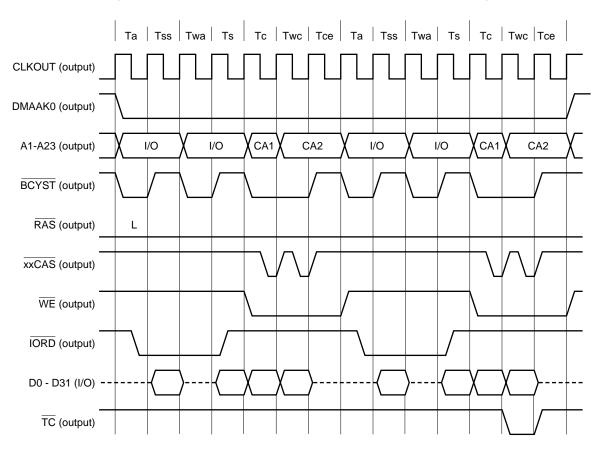

| p. 124 | Change of Figure 8-21. 16- to 16-Bit Data Bus Width (32-bit transfer bus sizing) |

| p. 141 | Addition of Caution to 9.2.5 (2) (b) Starting transmission/reception             |

| р. 176 | Change of the description in 13.2.2 (3) Releasing by RESET pin input             |

| p. 178 | Change of the description in 13.3.2 (2) Releasing by RESET pin input             |

| p. 181 | Change of the description in 14.3 Reset                                          |

The mark  $\star$  shows major revised points.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- · Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- · Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

| NEC Electronics Inc. (U.S.)     | NEC Electronics (Germany) GmbH | NEC Electronics Hong Kong Ltd.      |

|---------------------------------|--------------------------------|-------------------------------------|

| Santa Clara, California         | Benelux Office                 | Hong Kong                           |

| Tel: 408-588-6000               | Eindhoven, The Netherlands     | Tel: 2886-9318                      |

| 800-366-9782                    | Tel: 040-2445845               | Fax: 2886-9022/9044                 |

| Fax: 408-588-6130               | Fax: 040-2444580               |                                     |

| 800-729-9288                    |                                | NEC Electronics Hong Kong Ltd.      |

|                                 | NEC Electronics (France) S.A.  | Seoul Branch                        |

| NEC Electronics (Germany) GmbH  | Velizy-Villacoublay, France    | Seoul, Korea                        |

| Duesseldorf, Germany            | Tel: 01-30-67 58 00            | Tel: 02-528-0303                    |

| Tel: 0211-65 03 02              | Fax: 01-30-67 58 99            | Fax: 02-528-4411                    |

| Fax: 0211-65 03 490             |                                |                                     |

|                                 | NEC Electronics (France) S.A.  | NEC Electronics Singapore Pte. Ltd. |

| NEC Electronics (UK) Ltd.       | · · · ·                        | United Square, Singapore 1130       |

| · · ·                           | Spain Office                   | Tel: 65-253-8311                    |

| Milton Keynes, UK               | Madrid, Spain                  |                                     |

| Tel: 01908-691-133              | Tel: 01-504-2787               | Fax: 65-250-3583                    |

| Fax: 01908-670-290              | Fax: 01-504-2860               |                                     |

|                                 |                                | NEC Electronics Taiwan Ltd.         |

| NEC Electronics Italiana s.r.l. | NEC Electronics (Germany) GmbH | Taipei, Taiwan                      |

| Milano, Italy                   | Scandinavia Office             | Tel: 02-2719-2377                   |

| Tel: 02-66 75 41                | Taeby, Sweden                  | Fax: 02-2719-5951                   |

| Fax: 02-66 75 42 99             | Tel: 08-63 80 820              |                                     |

|                                 | Fax: 08-63 80 388              | NEC do Brasil S.A.                  |

|                                 | 1 47. 00 00 00 000             | Electron Devices Division           |

|                                 |                                |                                     |

Electron Devices Division Rodovia Presidente Dutra, Km 214 07210-902-Guarulhos-SP Brasil Tel: 55-11-6465-6810 Fax: 55-11-6465-6829

J98. 11

# PREFACE

#### This manual is intended for user engineers who wish to understand the functions of the V831 Readers ( $\mu$ PD705101) and design application systems using it.

Purpose This manual explains the hardware functions of the V831 in the following organization.

Organization The volumes of the V831 User's Manual are available: hardware (this manual) and architecture (V830 Family<sup>™</sup> User's Manual - Architecture) manuals.

|             | Hardware<br>• General                                                        | Architecture <ul> <li>Register Set</li> </ul>                     |

|-------------|------------------------------------------------------------------------------|-------------------------------------------------------------------|

|             | Pin Function                                                                 | Data Set                                                          |

|             | CPU Function                                                                 | Address Space                                                     |

|             | <ul> <li>Internal peripheral function</li> </ul>                             | Instruction                                                       |

|             | Appendix                                                                     | Interrupt and exception                                           |

|             |                                                                              |                                                                   |

| How to Read | It is assumed that the readers of this                                       | s manual have a general knowledge of electricity, logic circuits, |

| This Manual | and microcomputers.                                                          |                                                                   |

|             |                                                                              |                                                                   |

|             | To understand the instruction function                                       |                                                                   |

|             | $\rightarrow$ Refer to the V830 Family Us                                    | er's Manual - Architecture.                                       |

|             | To check the detailed function of a re                                       | edister whose name is known                                       |

|             | $\rightarrow$ Refer to Appendix A Register                                   | -                                                                 |

|             |                                                                              |                                                                   |

|             | To understand the overall functions                                          | of the V831                                                       |

|             | ightarrow Read this manual in the orde                                       | r of Table of Contents.                                           |

|             |                                                                              |                                                                   |

| Legend      | Data significance: Left: higher digits,                                      |                                                                   |

|             | Active low: $\overline{\mathbf{x}\mathbf{x}\mathbf{x}}$ (top bar over pin or | -                                                                 |

|             | Memory map address: Top: high-or                                             |                                                                   |

|             | <b>Note</b> : Explanation of part of text                                    | marked Note                                                       |

|             | Caution: Item to be especially note                                          | d.                                                                |

|             | Remark : Supplement                                                          |                                                                   |

|             | Numeric notation: Binary xxxx or                                             | xxxxB                                                             |

|             | Decimal XXXX                                                                 |                                                                   |

|             | Hexadecimal >                                                                | xxxH                                                              |

|             | Prefix indicating power of 2 (address                                        |                                                                   |

|             | K (kilo) : 2 <sup>10</sup> =                                                 |                                                                   |

|             | M (mega) : 2 <sup>20</sup> =                                                 |                                                                   |

|             | G (giga) : 2 <sup>30</sup> =                                                 | 1024 <sup>3</sup>                                                 |

|             |                                                                              |                                                                   |

**Related documents** The related documents referred to in this publication may include preliminary versions. However, preliminary versions are not marked as such.

# Document related to V831

| Document Name                            | Document No. |

|------------------------------------------|--------------|

| V831 User's manual - Hardware            | This manual  |

| V830 Family User's Manual - Architecture | U12496E      |

| V831 Data Sheet                          | U12979E      |

# Document related to development tools (user's manual)

|                      | Document No. |                                        |         |

|----------------------|--------------|----------------------------------------|---------|

| CA830 (C compiler)   |              | Operation (UNIX <sup>™</sup> based)    | U11013E |

|                      |              | Operation (Windows <sup>™</sup> based) | U11068E |

|                      |              | Assembly language                      | U11014E |

|                      |              | C language                             | U11010E |

|                      |              | Project manager                        | U11991E |

| RX830 (real-time OS) | ITRON1       | Fundamental                            | U11730E |

|                      |              | Installation                           | U11731E |

|                      |              | Technical                              | U11713E |

|                      | μITRON       | Fundamental                            | U13152E |

|                      | Ver. 3.0     | Installation                           | U13151E |

|                      |              | Technical                              | U13150E |

# CONTENTS

| CHAPT | ER 1    | GENERAL                                    |

|-------|---------|--------------------------------------------|

| 1.1   | Featu   | res19                                      |

| 1.2   | Applic  | cation Fields 20                           |

| 1.3   | Order   | ing Information 2'                         |

| 1.4   | Pin Co  | onfiguration (Top View) 2'                 |

| 1.5   | Intern  | al Block Configuration 23                  |

| 1.6   | Intern  | al Units                                   |

|       |         |                                            |

| CHAPT | ER 2    | PIN FUNCTION                               |

| 2.1   | Pin Fu  | Inction List 27                            |

| 2.2   | Pin St  | atus                                       |

| 2.3   | Pin Fu  | Inction                                    |

|       | 2.3.1   | Address bus                                |

|       | 2.3.2   | Data bus                                   |

|       | 2.3.3   | Bus control signals                        |

|       | 2.3.4   | System control signals                     |

|       | 2.3.5   | Interrupt control signals                  |

|       | 2.3.6   | DRAM control signals                       |

|       | 2.3.7   | DMA control signals                        |

|       | 2.3.8   | Real-time pulse control signals            |

|       | 2.3.9   | Serial control signals                     |

|       | 2.3.10  | Port control signals                       |

|       | 2.3.11  | Debug control signals                      |

|       |         |                                            |

| CHAPT | ER 3    | CPU FUNCTION                               |

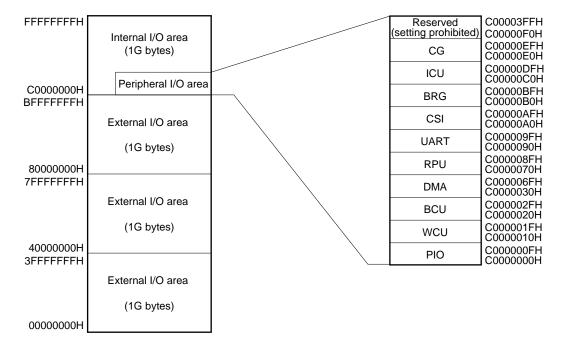

| 3.1   | Intern  | al Peripheral I/O Space 35                 |

|       | 3.1.1   | Notes                                      |

| 3.2   | CPU (   | Core System Registers 30                   |

|       |         |                                            |

| CHAPT | ER 4    | INTERRUPT/EXCEPTION PROCESSING FUNCTION    |

| 4.1   | Interru | upt/Exception Processing 37                |

|       | 4.1.1   | Interrupt/exception processing types       |

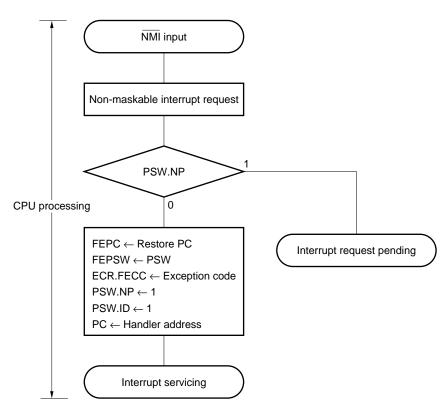

| 4.2   | Non-M   | Askable Interrupt                          |

|       | 4.2.1   | Servicing non-maskable interrupt           |

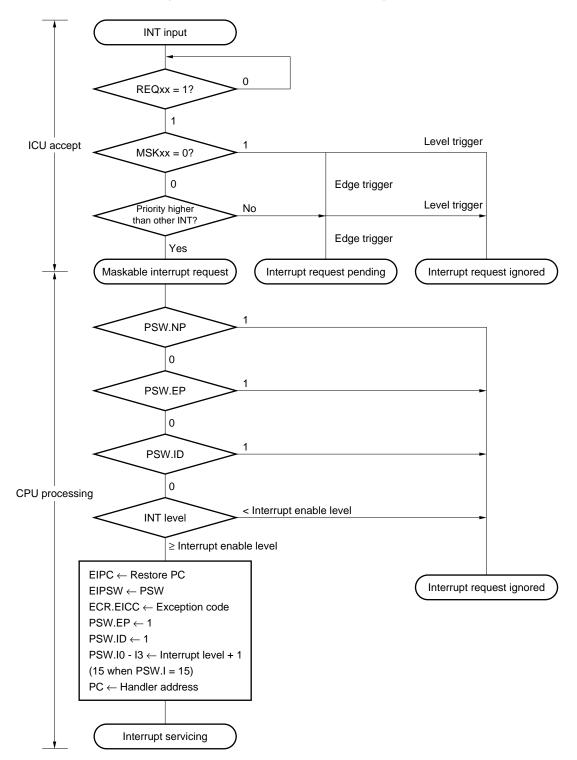

| 4.3   | Maska   | able Interrupts 40                         |

|       | 4.3.1   | Maskable interrupt servicing format 40     |

|       | 4.3.2   | Priority of maskable interrupt 42          |

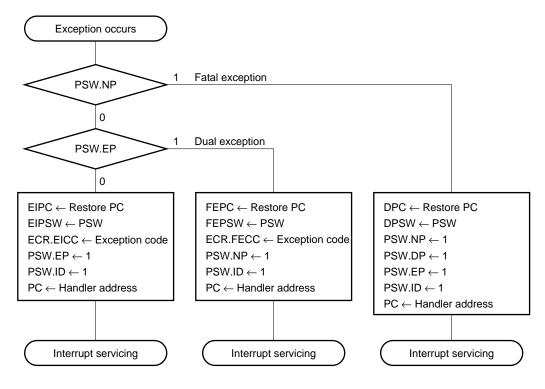

| 4.4   | Excep   | tion Processing 43                         |

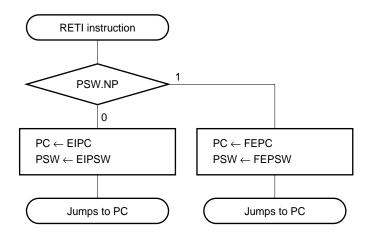

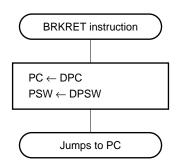

| 4.5   | Resto   | ring from Exception/Interrupt 44           |

|       | 4.5.1   | Restoring from exception/interrupt 44      |

|       | 4.5.2   | Restoring from fatal exception routine     |

| 4.6   | Interru | upt Control Registers 44                   |

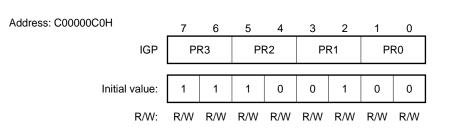

|       | 4.6.1   | Interrupt group priority register (IGP) 45 |

|       | 4.6.2   | Interrupt clear register (ICR)             |

|       | 4.6.3   | Interrupt request register (IRR)           |

|       | 4.6.4  | Interrupt request mask register (IMR)           | 47 |

|-------|--------|-------------------------------------------------|----|

|       | 4.6.5  | ICU mode register (IMOD)                        | 48 |

| 4.7   | Interr | upt Requests by External Input Pins             | 50 |

|       |        |                                                 |    |

| CHAPT |        | BUS CONTROL FUNCTION                            | 51 |

|       |        | ires                                            | 51 |

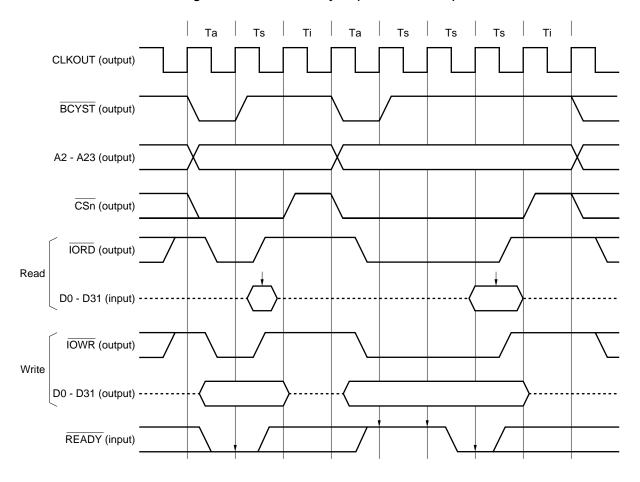

| 5.2   | Exter  | nal I/O Cycle                                   | 51 |

|       | 5.2.1  | Byte access control                             | 52 |

| 5.3   | SRAN   | /I (ROM) Cycle                                  | 53 |

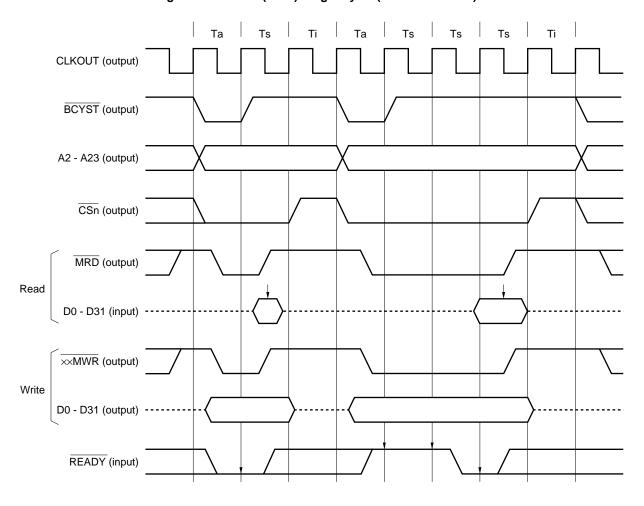

|       | 5.3.1  | SRAM (ROM) single cycle                         | 55 |

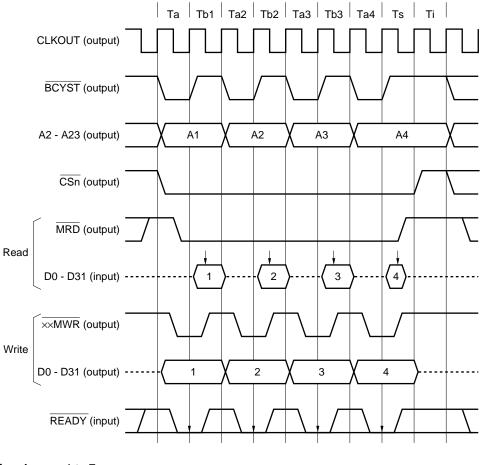

|       | 5.3.2  | SRAM (ROM) burst cycle                          | 57 |

|       | 5.3.3  | Byte access control                             | 59 |

| 5.4   | Page   | ROM Cycle                                       | 60 |

|       | 5.4.1  | Page-ROM single cycle                           | 60 |

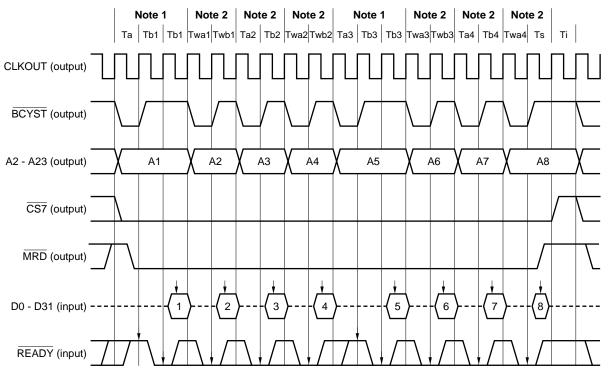

|       | 5.4.2  | Page-ROM burst cycle                            | 60 |

| 5.5   | DRAN   | /I Cycle                                        | 63 |

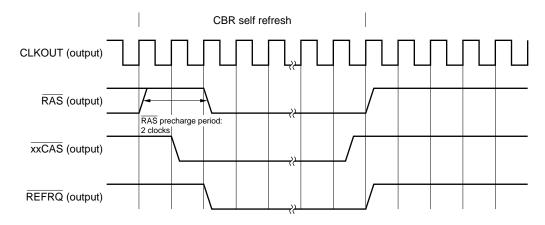

|       | 5.5.1  | DRAM single cycle                               | 65 |

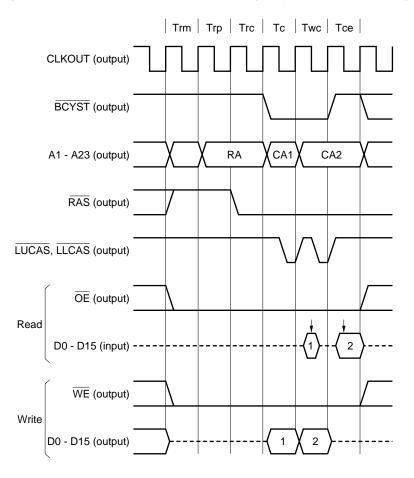

|       | 5.5.2  | DRAM burst cycle                                | 68 |

|       | 5.5.3  | Timing control                                  | 72 |

|       | 5.5.4  | Byte access control                             | 74 |

|       | 5.5.5  | Refresh control                                 | 75 |

| 5.6   | Idle S | tate                                            | 77 |

| 5.7   | Bus S  | Sizing                                          | 77 |

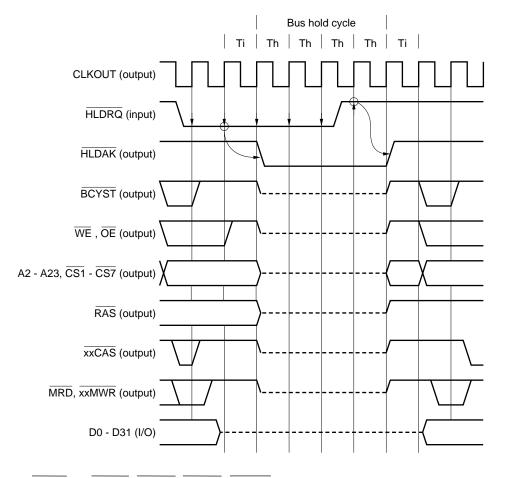

| 5.8   | Bus H  | lold Cycle                                      | 82 |

| 5.9   | Bus A  | Arbitration                                     | 83 |

| 5.10  | Write  | Buffer Operation                                | 84 |

| 5.11  | Mem    | ory Mapped I/O                                  | 84 |

|       |        |                                                 |    |

| CHAPT | ER 6   | WAIT CONTROL FUNCTION                           | 85 |

| 6.1   | Featu  | ires                                            | 85 |

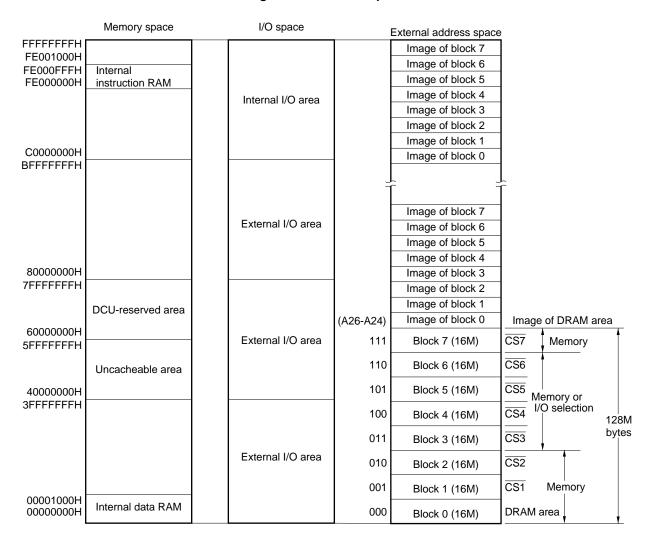

| 6.2   | Addre  | ess Space and Block                             | 86 |

| 6.3   | Wait   | Control Registers                               | 87 |

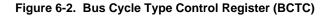

|       | 6.3.1  | Bus cycle type control register (BCTC)          | 87 |

|       | 6.3.2  | Data bus width control register (DBC)           | 88 |

|       | 6.3.3  | Programmable wait control register 0 (PWC0)     | 89 |

|       | 6.3.4  | Programmable wait control register 1 (PWC1)     | 90 |

|       | 6.3.5  | Programmable idle control register (PIC)        | 91 |

| 6.4   | Wait   | Control by READY Pin                            | 92 |

|       | 6.4.1  | Sampling timing of READY pin                    | 92 |

|       | 6.4.2  | When using both READY pin and programmable wait | 92 |

|       |        |                                                 |    |

| СНАРТ | ER 7   | MEMORY ACCESS CONTROL FUNCTION                  | 93 |

| 7.1   | Featu  | ires                                            | 93 |

| 7.2   | DRAM   | A Control Function                              | 93 |

|       | 7.2.1  | Address multiplex function                      | 94 |

|       | 7.2.2  | Judgment of on-page/off-page                    | 94 |

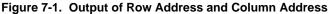

|       | 7.2.3  | DRAM configuration register (DRC)               | 94 |

|       |        |                                                 |    |

| 7.3    | Page-            | ROM Control Function                                              | 98  |

|--------|------------------|-------------------------------------------------------------------|-----|

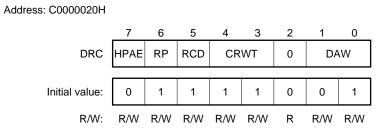

|        | 7.3.1            | Page-ROM configuration register (PRC)                             | 98  |

|        |                  |                                                                   |     |

| CHAPTI |                  | DMA FUNCTION                                                      | 99  |

| 8.1    |                  | res                                                               | 99  |

| 8.2    |                  | guration                                                          | 100 |

| 8.3    |                  | Control Registers                                                 | 101 |

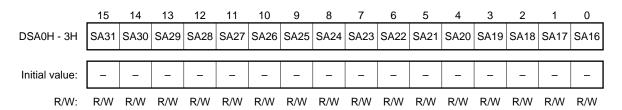

|        | 8.3.1            | DMA source address registers 0 through 3 (DSA0 through DSA3)      | 101 |

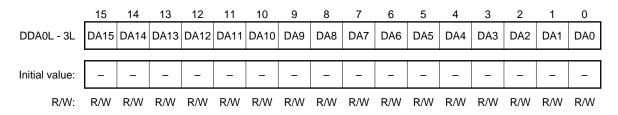

|        | 8.3.2            | DMA destination address registers 0 through 3 (DDA0 through DDA3) | 103 |

|        | 8.3.3            | DMA byte count registers 0 through 3 (DBC0 through DBC3)          | 104 |

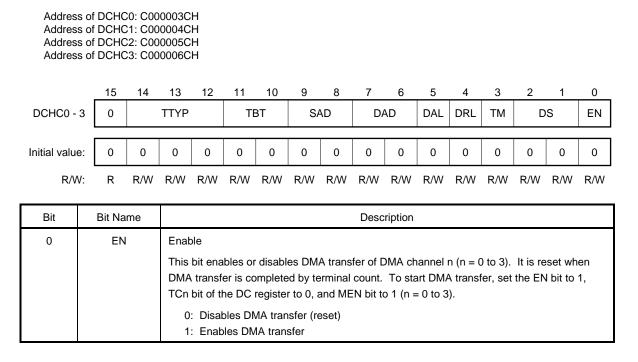

|        | 8.3.4            | DMA channel control registers 0 through 3 (DCHC0 through DCHC3)   | 106 |

|        | 8.3.5            | DMA control register (DC)                                         | 109 |

| 8.4    | Trans            | fer Mode                                                          | 110 |

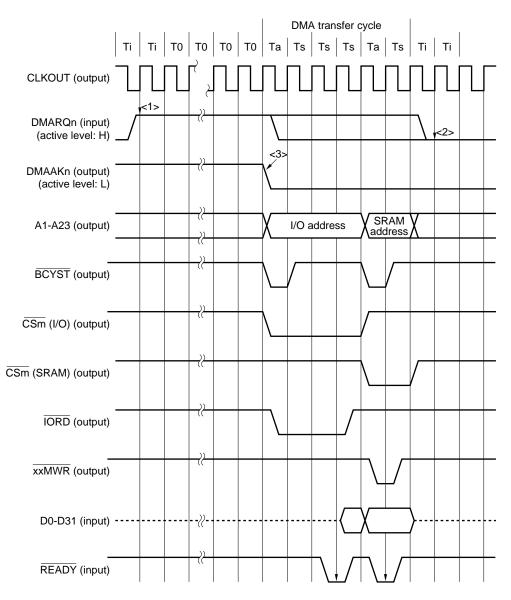

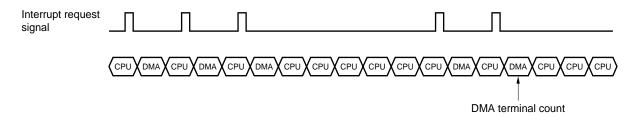

|        | 8.4.1            | Single transfer mode                                              | 110 |

|        | 8.4.2            | Demand transfer mode                                              | 111 |

| 8.5    | DMA              | Transfer Type and Subject to Transfer                             | 111 |

|        | 8.5.1            | Two-cycle transfer                                                | 111 |

|        | 8.5.2            | Subject to transfer                                               | 112 |

| 8.6    | Priori           | ties of DMA Channels                                              | 113 |

| 8.7    | DMA <sup>-</sup> | Transfer Request                                                  | 113 |

|        | 8.7.1            | Request from DMARQ pin                                            | 113 |

|        | 8.7.2            | Request from software                                             | 117 |

|        | 8.7.3            | Request from internal peripheral hardware                         | 118 |

| 8.8    |                  | Transfer End Interrupt                                            | 119 |

|        | 8.8.1            | TCn bit reference and DMA transfer end interrupt                  | 119 |

| 8.9    |                  | Transfer End Output                                               | 121 |

|        |                  |                                                                   | 122 |

| 0110   | 8.10.1           |                                                                   | 122 |

|        |                  | Temporary stop by HLDRQ signal or refresh                         | 122 |

| 8 11   |                  | Sizing during DMA Transfer                                        | 123 |

| 0.11   | Dus C            |                                                                   | 125 |

| СНАРТІ | ER 9             | SERIAL INTERFACE FUNCTION                                         | 125 |

| 9.1    | Asyno            | chronous Serial Interface (UART)                                  | 125 |

|        | 9.1.1            | General                                                           | 125 |

|        | 9.1.2            | Features                                                          | 126 |

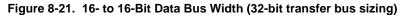

|        | 9.1.3            | Configuration                                                     | 127 |

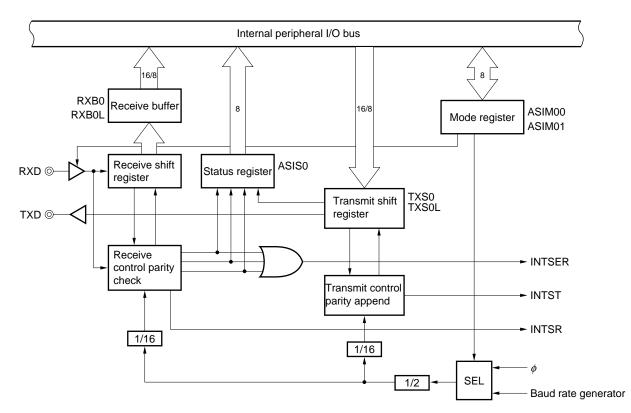

|        | 9.1.4            | Mode registers and control registers                              | 128 |

|        | 9.1.5            | Interrupt requests                                                | 134 |

|        | 9.1.6            | Basic operation                                                   | 135 |

| 92     |                  | ed Serial Interface (CSI)                                         | 137 |

| 0.2    | 9.2.1            | Features                                                          | 137 |

|        | 9.2.1            | Configuration                                                     | 137 |

|        | 9.2.2            | -                                                                 | 137 |

|        |                  | Mode registers and control registers                              |     |

|        | 9.2.4            | Pin function                                                      | 140 |

| 0.0    | 9.2.5<br>Poud    | Basic operation                                                   | 140 |

| 9.3    |                  | Rate Generator                                                    | 142 |

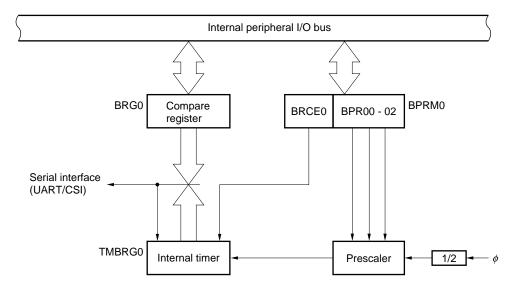

|        | 9.3.1            | Configuration and function                                        | 142 |

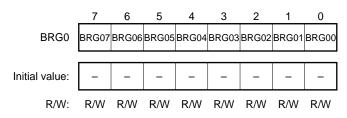

|        | 9.3.2            | Baud rate generator compare register (BRG0)                       | 145 |

| 9.3.3 Baud rate generator prescaler mode register (BPRM0) | 146 |

|-----------------------------------------------------------|-----|

|                                                           |     |

| CHAPTER 10 TIMER/COUNTER FUNCTION                         | 147 |

| 10.1 Features                                             | 147 |

| 10.2 Configuration                                        | 148 |

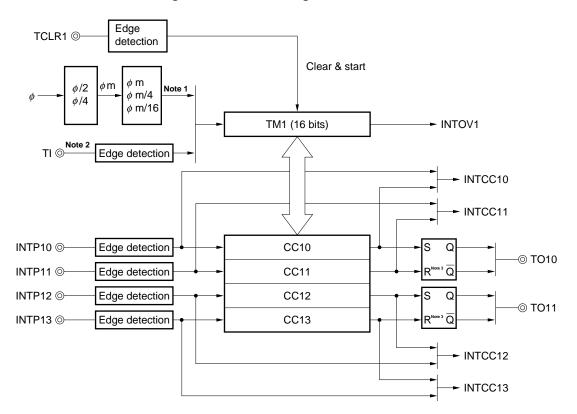

| 10.2.1 Timer 1                                            | 149 |

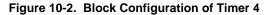

| 10.2.2 Timer 4                                            | 151 |

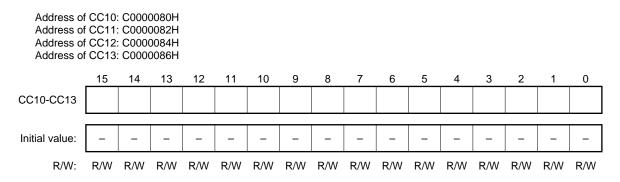

| 10.2.3 Capture/compare registers (CC10 through CC13)      | 152 |

| 10.3 Timer/Counter Control Registers                      | 154 |

| 10.3.1 Timer unit mode register (TUM1)                    | 154 |

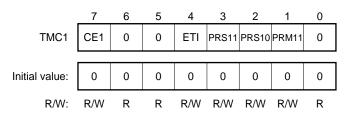

| 10.3.2 Timer control register 1 (TMC1)                    | 156 |

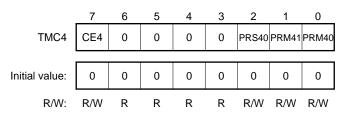

| 10.3.3 Timer control register 4 (TMC4)                    | 157 |

| 10.3.4 Timer output control register (TOC1)               | 158 |

| 10.3.5 ICU mode register (IMOD)                           | 159 |

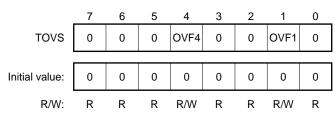

| 10.3.6 Timer overflow status register (TOVS)              | 159 |

| 10.4 Operation                                            | 160 |

| 10.4.1 Timer 1                                            | 160 |

| 10.4.2 Timer 4                                            | 161 |

| 10.5 Notes                                                | 162 |

|                                                           |     |

| CHAPTER 11 PORT FUNCTION                                  | 165 |

| 11.1 Configuration                                        | 165 |

| 11.2 Port Control Register                                | 167 |

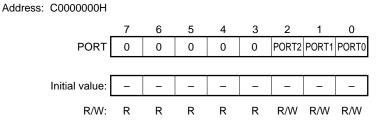

| 11.2.1 I/O port register (PORT)                           | 167 |

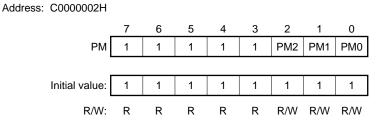

| 11.2.2 I/O mode register (PM)                             | 167 |

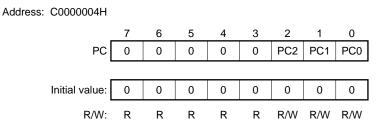

| 11.2.3 Port control mode register (PC)                    | 168 |

| CHAPTER 12 CLOCK GENERATION FUNCTION                      | 169 |

| 12.1 Configuration                                        | 169 |

| 12.2 Selecting Input Clock                                | 170 |

| 12.2.1 Lockup time                                        | 170 |

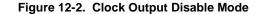

| 12.3 Clock Output Control                                 | 170 |

| 12.3.1 Clock output disable mode                          | 170 |

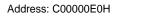

| 12.4 Clock Control Registers                              | 171 |

| 12.4.1 Clock control register (CGC)                       | 171 |

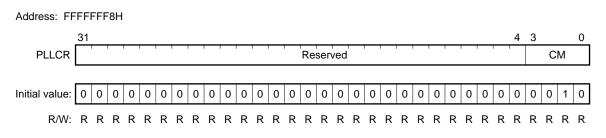

| 12.4.2 PLL control register (PLLCR)                       | 172 |

| CHAPTER 13 STANDBY FUNCTION                               | 173 |

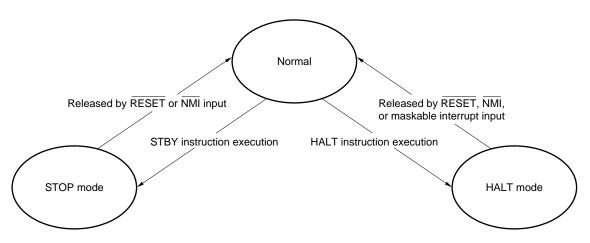

| 13.1 Standby Mode                                         | 173 |

| 13.2 HALT mode                                            | 174 |

| 13.2.1 Setting and operating status of HALT mode          | 174 |

| 13.2.2 Releasing HALT mode                                | 175 |

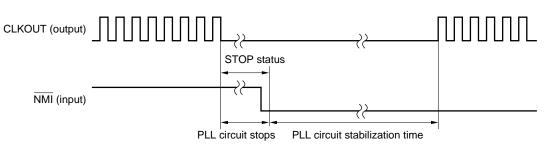

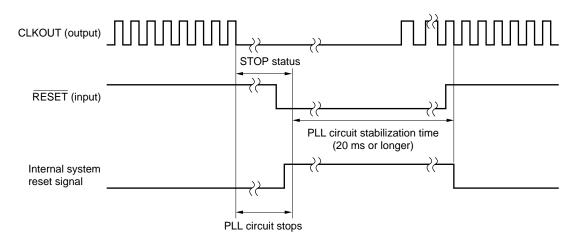

| 13.3 STOP Mode                                            | 176 |

| 13.3.1 Setting and operating status of STOP mode          | 176 |

| 13.3.2 Releasing STOP mode                                | 177 |

| 13.4 Ensuring Oscillation Stabilization Time              | 178 |

| CHAPTER 14 RESET/NMI CONTROL FUNCTION |     |

|---------------------------------------|-----|

| 14.1 Features                         |     |

| 14.2 Non-Maskable Interrupt (NMI)     |     |

| 14.3 Reset                            |     |

| 14.3.1 Pin function                   |     |

| 14.3.2 Initialize                     | 183 |

| CHAPTER 15 DEBUG/TRACE FUNCTION       |     |

| 15.1 Features                         | 185 |

|                                       |     |

| APPENDIX A REGISTER INDEX             | 187 |

# LIST OF FIGURES (1/3)

| Figure | No. Title                                                                    | Page |  |

|--------|------------------------------------------------------------------------------|------|--|

| 3-1    | Internal Peripheral I/O Map                                                  | 35   |  |

| 4-1    | Processing Flow of Non-Maskable Interrupt                                    | 39   |  |

| 4-2    | Maskable Interrupt Servicing Flow                                            | 41   |  |

| 4-3    | Exception Processing Flow                                                    | 43   |  |

| 4-4    | Flow of Restoration from Exception/Interrupt                                 | 44   |  |

| 4-5    | Flow of Restoration from Fatal Exception Routine                             | 44   |  |

| 4-6    | Interrupt Group Priority Register (IGP)                                      | 45   |  |

| 4-7    | Interrupt Clear Register (ICR)                                               | 46   |  |

| 4-8    | Interrupt Request Register (IRR)                                             | 47   |  |

| 4-9    | Interrupt Request Mask Register (IMR)                                        | 47   |  |

| 4-10   | ICU Mode Register (IMOD)                                                     | 49   |  |

| 5-1    | External I/O Cycle (32-bit bus mode)                                         | 52   |  |

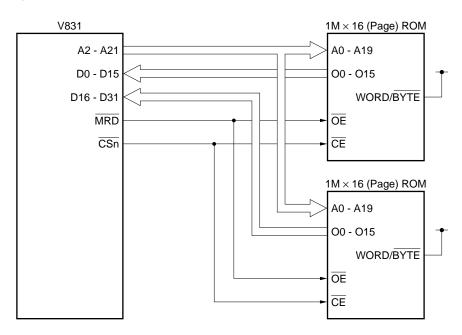

| 5-2    | Example of Connection of 16M ROM (1M $\times$ 16) (in 32-bit bus mode)       | 53   |  |

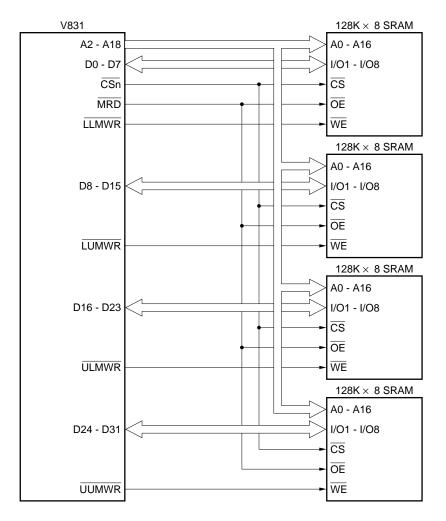

| 5-3    | Example of Connection of 1M SRAM (128K $	imes$ 8) (in 32-bit bus mode)       | 54   |  |

| 5-4    | SRAM (ROM) Single Cycle (32-bit bus mode)                                    | 56   |  |

| 5-5    | SRAM (ROM) Burst Cycle                                                       | 58   |  |

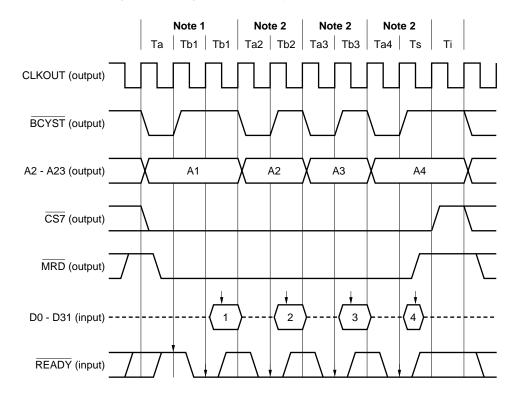

| 5-6    | Page-ROM Burst Cycle (32-bit bus mode)                                       | 61   |  |

| 5-7    | Page-ROM Burst Cycle (16-bit bus mode, 8-byte page size)                     | 62   |  |

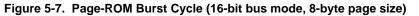

| 5-8    | Example of Connection with 16M EDO-DRAM (1M $	imes$ 16) (in 16-bit bus mode) | 64   |  |

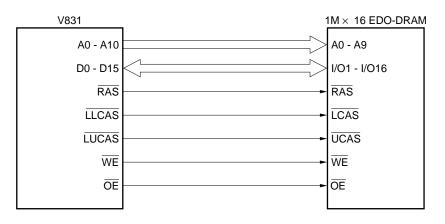

| 5-9    | Example of Connection with 16M EDO-DRAM (1M $	imes$ 16) (in 32-bit bus mode) | 64   |  |

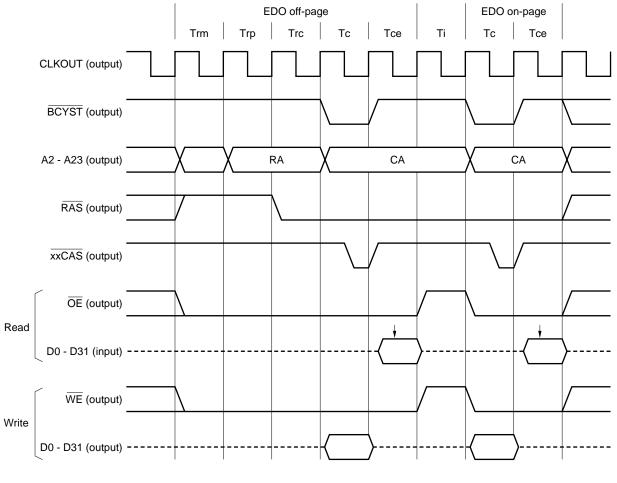

| 5-10   | DRAM Single 1-Clock CAS on-page/off-page Cycle (32-bit bus mode)             | 66   |  |

| 5-11   | DRAM Single 2-Clock CAS on-page/off-page Cycle (32-bit bus mode)             | 67   |  |

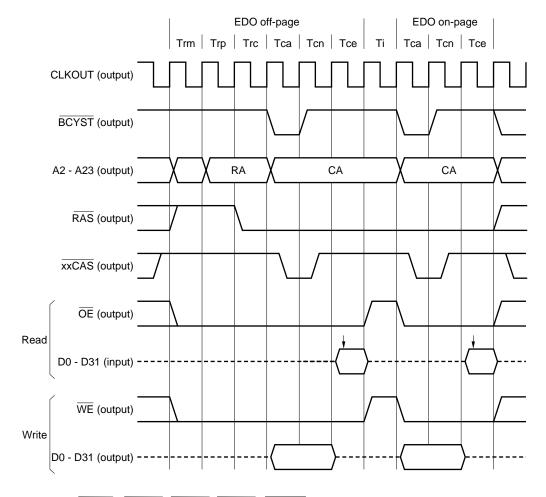

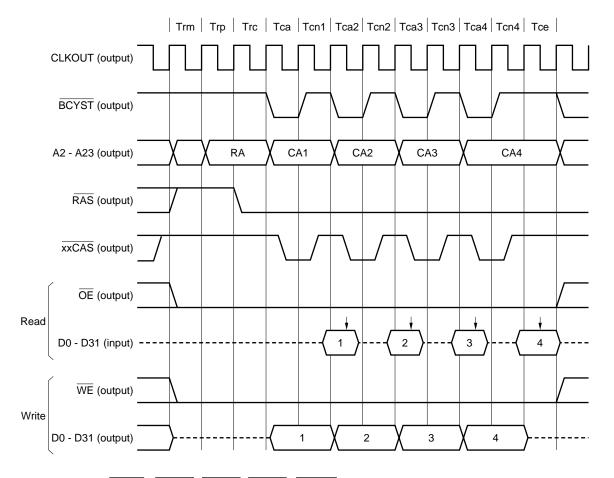

| 5-12   | DRAM Burst 1-Clock CAS off-page Cycle (32-bit bus mode)                      | 69   |  |

| 5-13   | DRAM Burst 1-Clock CAS on-page Cycle (32-bit bus mode)                       | 70   |  |

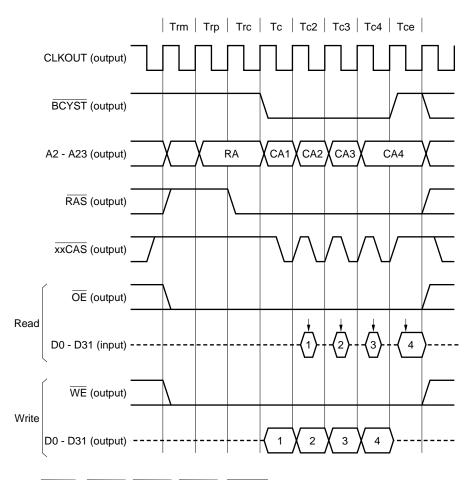

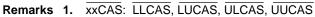

| 5-14   | DRAM Burst 2-Clock CAS off-page Cycle (32-bit bus mode)                      | 71   |  |

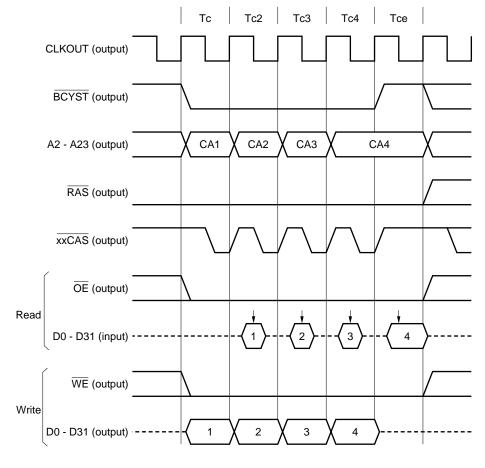

| 5-15   | DRAM Burst 2-Clock CAS on-page Cycle (32-bit bus mode)                       | 72   |  |

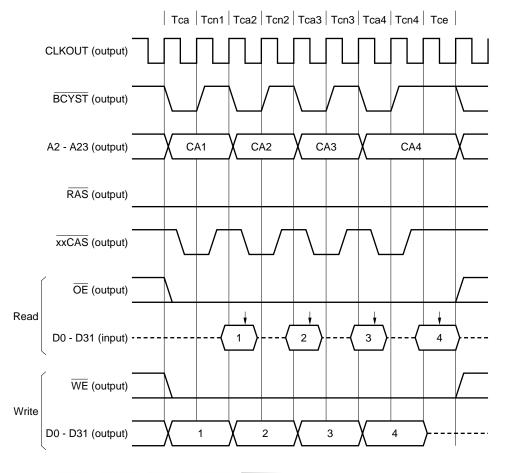

| 5-16   | DRAM Access Timing (burst off-page cycle)                                    | 73   |  |

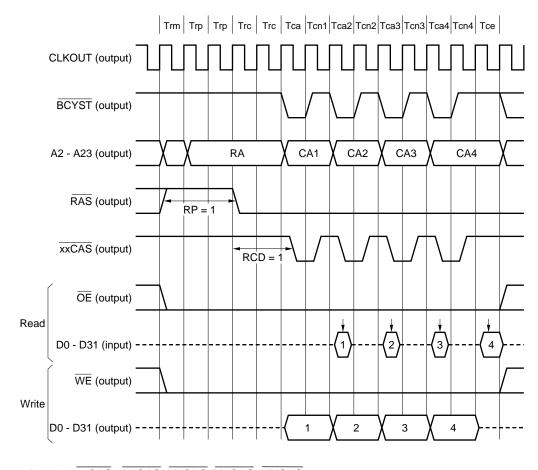

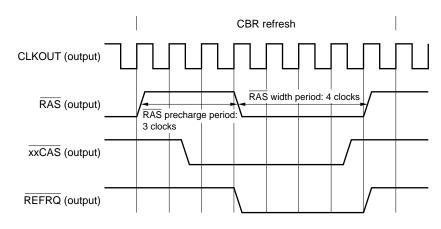

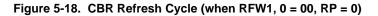

| 5-17   | CBR Refresh Cycle (when RFW1, 0 = 01, RP = 1)                                | 75   |  |

| 5-18   | CBR Refresh Cycle (when RFW1, 0 = 00, RP = 0)                                | 76   |  |

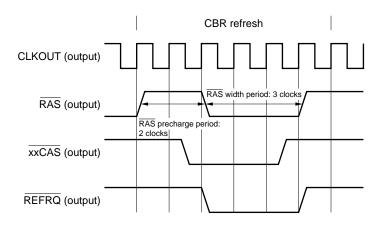

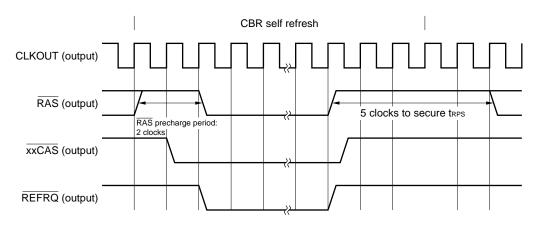

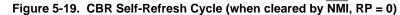

| 5-19   | CBR Self-Refresh Cycle (when cleared by $\overline{\text{NMI}}$ , RP = 0)    | 76   |  |

| 5-20   | CBR Self-Refresh Cycle (when cleared by RESET, RP = 0)                       | 77   |  |

| 5-21   | Additional Access in DRAM Single Cycle due to Bus Sizing                     | 78   |  |

| 5-22   | Additional Access in DRAM Burst Cycle due to Bus Sizing                      | 79   |  |

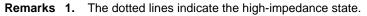

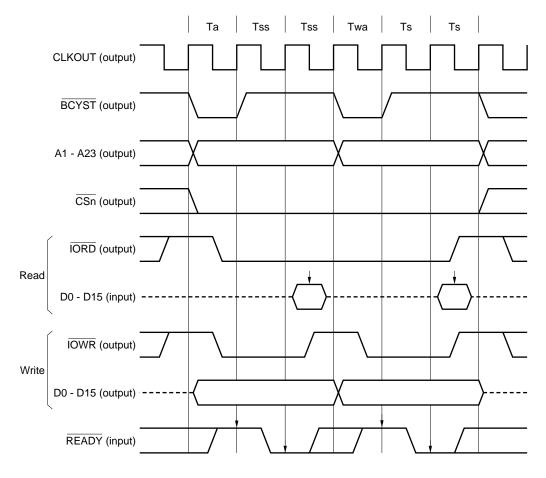

| 5-23   | Additional Access in I/O Cycle due to Bus Sizing                             | 80   |  |

| 5-24   | Additional Access in SRAM Single Cycle due to Bus Sizing                     | 81   |  |

| 5-25   | Bus Hold Cycle                                                               | 82   |  |

| 6-1    | Address Space                                                                | 86   |  |

| 6-2    | Bus Cycle Type Control Register (BCTC)                                       | 87   |  |

| 6-3    | Data Bus Width Control Register (DBC)                                        | 88   |  |

| 6-4    | Programmable Wait Control Register 0 (PWC0)                                  | 89   |  |

| 6-5    | Programmable Wait Control Register 1 (PWC1)                                  | 90   |  |

# LIST OF FIGURES (2/3)

| Figure I | No. Title                                                               | Page |

|----------|-------------------------------------------------------------------------|------|

|          |                                                                         |      |

| 6-6      | Programmable Idle Control Register (PIC)                                | 91   |

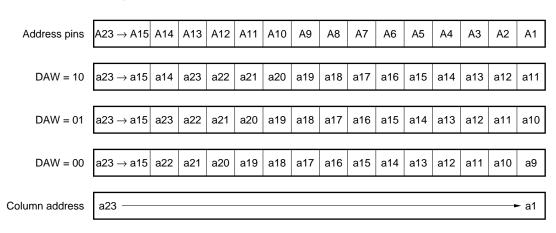

| 7-1      | Output of Row Address and Column Address                                | 94   |

| 7-2      | DRAM Configuration Register (DRC)                                       | 95   |

| 7-3      | Refresh Control Register (RFC)                                          | 97   |

| 7-4      | Page-ROM Configuration Register (PRC)                                   | 98   |

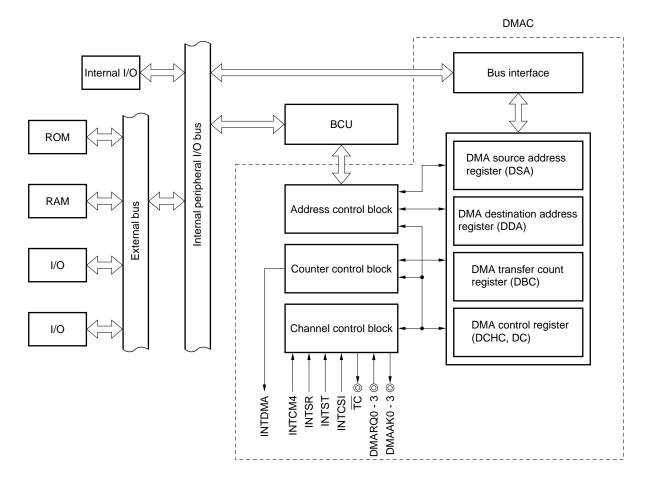

| 8-1      | DMAC Block Diagram                                                      | 100  |

| 8-2      | DMA Source Address Registers 0H through 3H (DSA0H through DSA3H)        | 101  |

| 8-3      | DMA Source Address Registers 0L through 3L (DSA0L through DSA3L)        |      |

| 8-4      | DMA Destination Address Registers 0H through 3H (DDA0H through DDA3H)   |      |

| 8-5      | DMA Destination Address Registers 0L through 3L (DDA0L through DDA3L)   |      |

| 8-6      | DMA Byte Count Registers 0 through 3 (DBC0 through DBC3)                |      |

| 8-7      | DMA Channel Control Registers 0 through 3 (DCHC0 through DCHC3)         |      |

| 8-8      | DMA Control Register (DC)                                               |      |

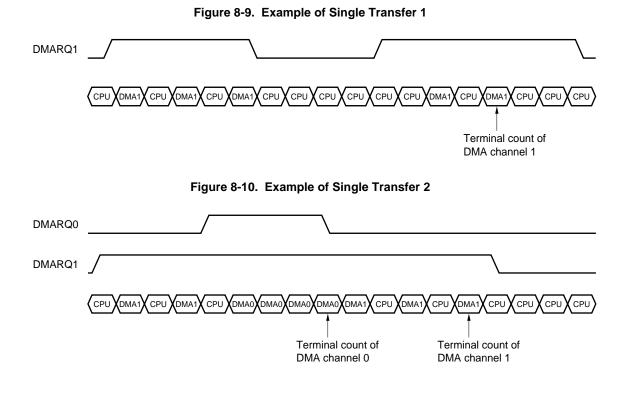

| 8-9      | Example of Single Transfer 1                                            |      |

| 8-10     | Example of Single Transfer 2                                            |      |

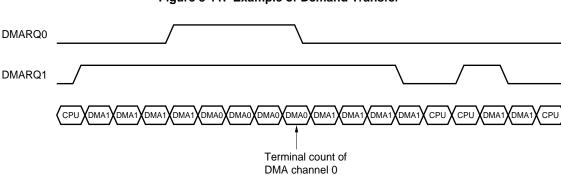

| 8-11     | Example of Demand Transfer                                              |      |

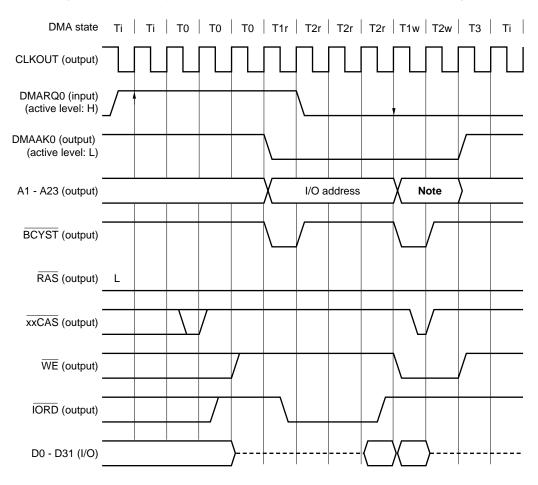

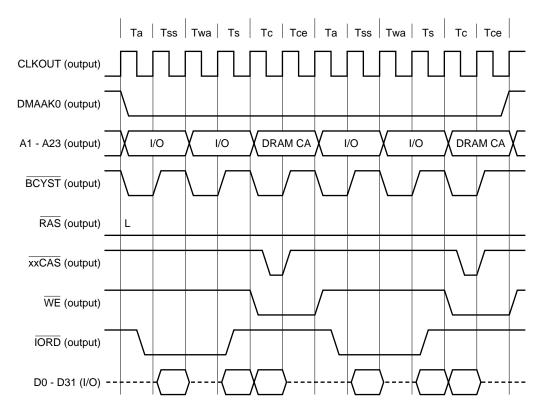

| 8-12     | Two-Cycle Demand Transfer (external I/O to DRAM (on-page))              |      |

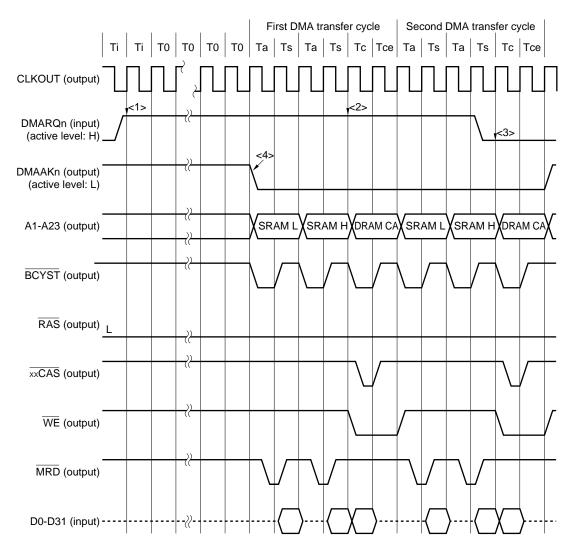

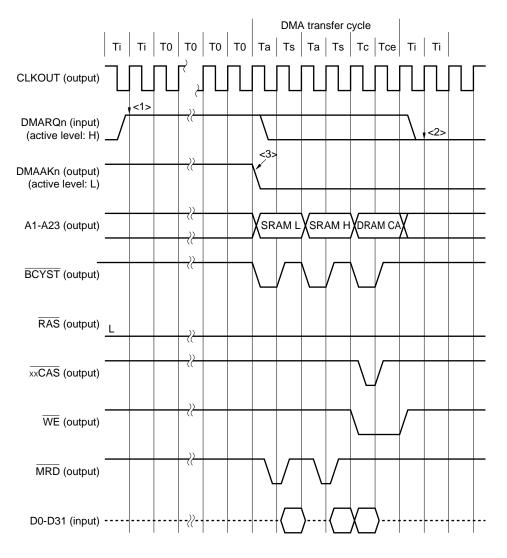

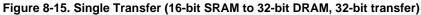

| 8-13     | Two-Cycle Demand Transfer (16-bit SRAM to 32-bit DRAM, 32-bit transfer) |      |

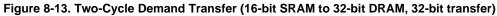

| 8-14     | Two-Cycle Demand Transfer (32-bit DRAM to 16-bit SRAM, 32-bit transfer) |      |

| 8-15     | Single Transfer (16-bit SRAM to 32-bit DRAM, 32-bit transfer)           |      |

| 8-16     | Single Transfer (8-bit I/O to 32-bit SRAM, 8-bit transfer)              |      |

| 8-17     | Example of Transfer on Request from Internal Peripheral Hardware        |      |

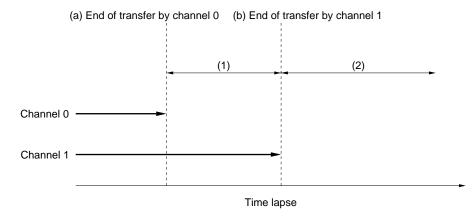

| 8-18     | Transfer End Processing of Channels 0 and 1                             |      |

| 8-19     | DMA Transfer End Output Timing                                          |      |

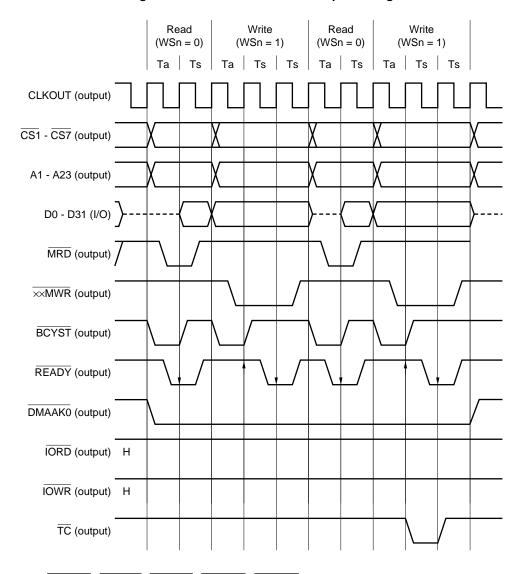

| 8-20     | 16- to 32-Bit Data Bus Width (32-bit transfer bus sizing)               |      |

| 8-21     | 16- to 16-Bit Data Bus Width (32-bit transfer bus sizing)               |      |

| 0        |                                                                         |      |

| 9-1      | Block Diagram of UART                                                   | 127  |

| 9-2      | Asynchronous Serial Interface Mode Register 00 (ASIM00)                 | 128  |

| 9-3      | Asynchronous Serial Interface Mode Register 01 (ASIM01)                 | 130  |

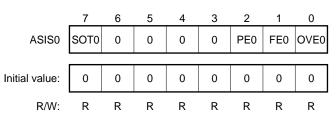

| 9-4      | Asynchronous Serial Interface Status Register (ASIS0)                   | 131  |

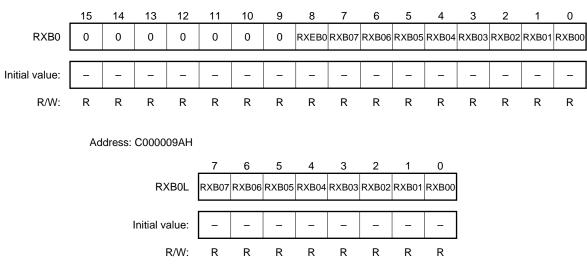

| 9-5      | Receive Buffer (RXB0, RXB0L)                                            | 132  |

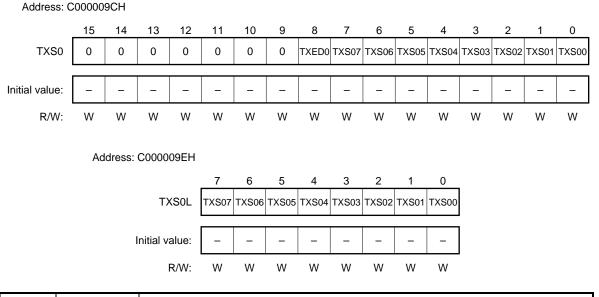

| 9-6      | Transmit Shift Register (TXS0, TXS0L)                                   | 133  |

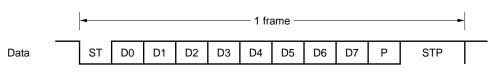

| 9-7      | Transmit Data Format of UART                                            | 135  |

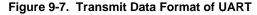

| 9-8      | Block Diagram of CSI                                                    | 137  |

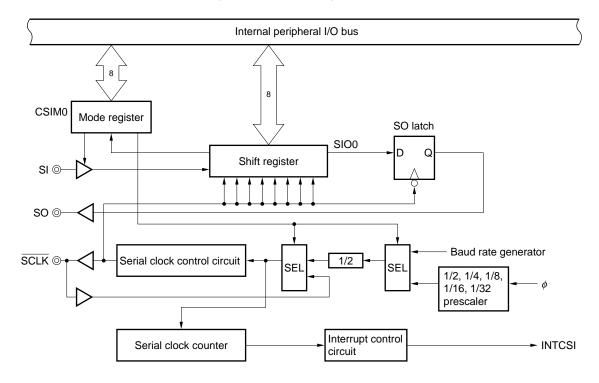

| 9-9      | Clocked Serial Interface Mode Register 0 (CSIM0)                        | 138  |

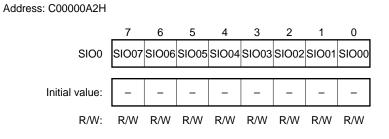

| 9-10     | Serial I/O Shift Register 0 (SIO0)                                      | 139  |

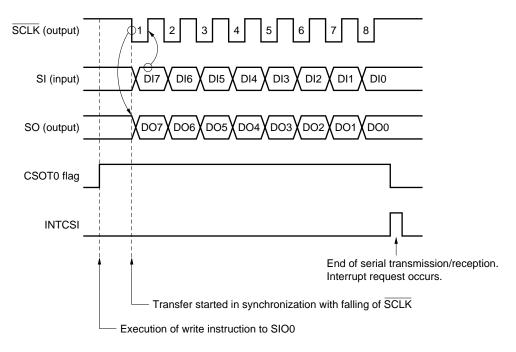

| 9-11     | CSI Transfer Timing                                                     | 140  |

| 9-12     | Block Configuration of Baud Rate Generator (BRG)                        | 142  |

| 9-13     | Baud Rate Generator Compare Register (BRG0)                             | 145  |

| 9-14     | Baud Rate Generator Prescaler Mode Register (BPRM0)                     | 146  |

# LIST OF FIGURES (3/3)

| Figure | No. Title                                                              | Page  |  |

|--------|------------------------------------------------------------------------|-------|--|

| 10-1   | Black Configuration of Timor 4                                         | 1 1 0 |  |

| -      | Block Configuration of Timer 1                                         | 148   |  |

| 10-2   | Block Configuration of Timer 4                                         | 149   |  |

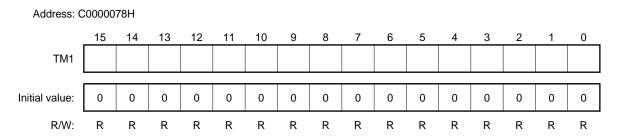

| 10-3   | Timer 1 (TM1)                                                          | 149   |  |

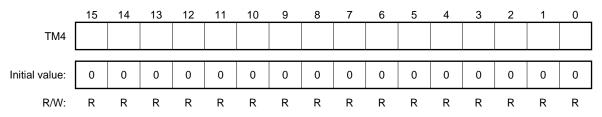

| 10-4   | Timer 4 (TM4)                                                          | 151   |  |

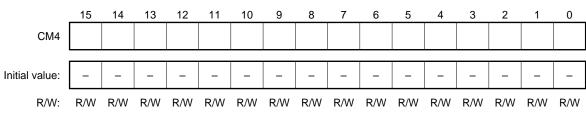

| 10-5   | Compare Register (CM4)                                                 | 151   |  |

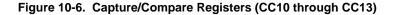

| 10-6   | Capture/Compare Registers (CC10 through CC13)                          | 152   |  |

| 10-7   | Timer Unit Mode Register (TUM1)                                        | 154   |  |

| 10-8   | Timer Control Register 1 (TMC1)                                        | 156   |  |

| 10-9   | Timer Control Register 4 (TMC4)                                        | 157   |  |

| 10-10  | Timer Output Control Register (TOC1)                                   | 158   |  |

| 10-11  | Timer Overflow Status Register (TOVS)                                  | 159   |  |

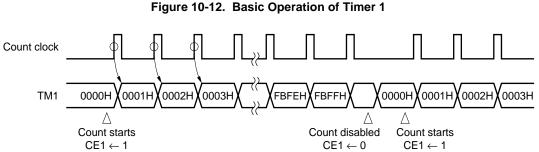

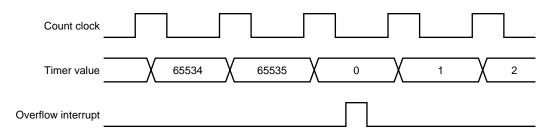

| 10-12  | Basic Operation of Timer 1                                             | 160   |  |

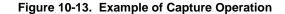

| 10-13  | Example of Capture Operation                                           | 161   |  |

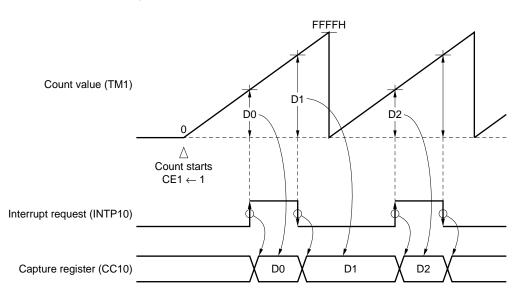

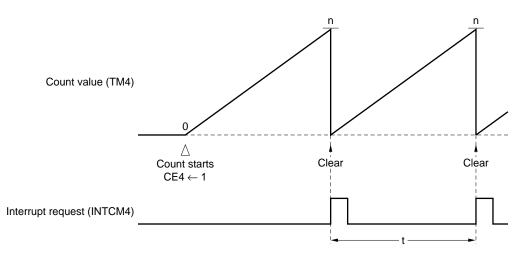

| 10-14  | Basic Operation of Timer 4                                             | 161   |  |

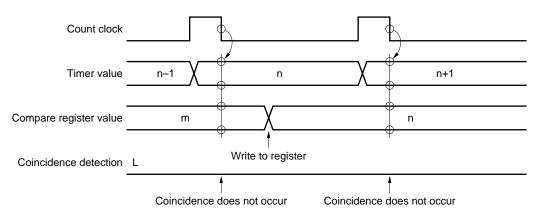

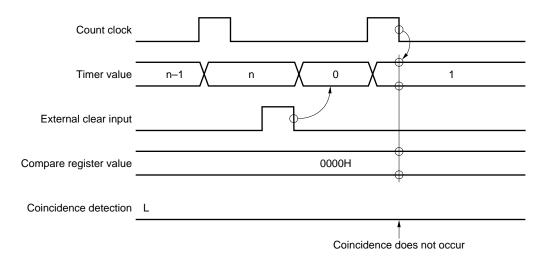

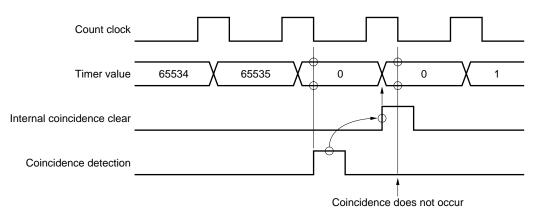

| 10-15  | Example of Compare Operation                                           | 162   |  |

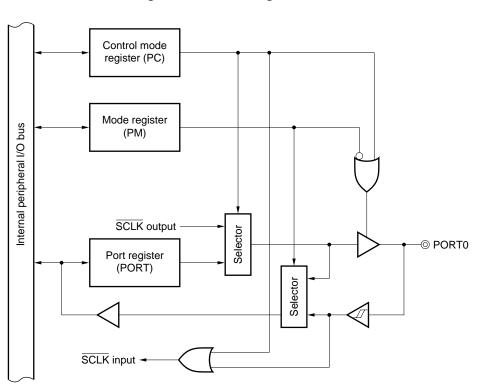

| 11-1   | Block Diagram of Port 0                                                | 165   |  |

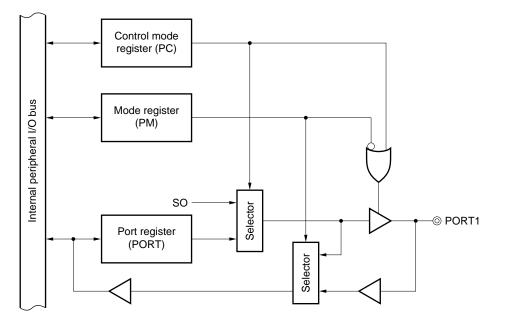

| 11-2   | Block Diagram of Port 1                                                | 166   |  |

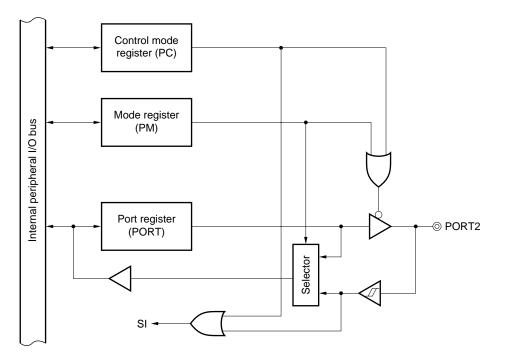

| 11-3   | Block Diagram of Port 2                                                | 166   |  |

| 11-4   | I/O Port Register (PORT)                                               | 167   |  |

| 11-5   | I/O Mode Register (PM)                                                 | 167   |  |

| 11-6   | Port Control Mode Register (PC)                                        | 168   |  |

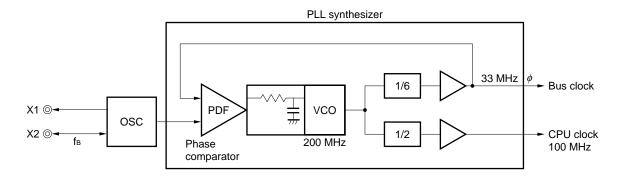

| 12-1   | Block Diagram of Clock Generation Function                             | 169   |  |

| 12-2   | Clock Output Disable Mode                                              | 170   |  |

| 12-3   | Clock Control Register (CGC)                                           | 171   |  |

| 12-4   | PLL Control Register (PLLCR)                                           | 172   |  |

| 13-1   | Status Transition                                                      | 174   |  |

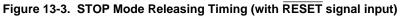

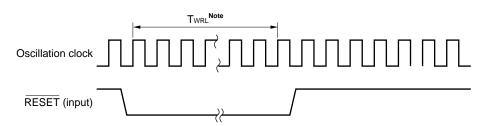

| 13-2   | STOP Mode Releasing Timing (with $\overline{\text{NMI}}$ signal input) | 179   |  |

| 13-3   | STOP Mode Releasing Timing (with RESET signal input)                   | 179   |  |

| 14-1   | Accepting Reset Signal                                                 | 182   |  |

| Table | No. Title                                                                                    | Page |

|-------|----------------------------------------------------------------------------------------------|------|

| 2-1   | Status of Each Pin                                                                           | 29   |

| 4-1   | Interrupt List                                                                               | 37   |

| 4-2   | Interrupt List (Maskable interrupts)                                                         | 38   |

| 4-3   | Relation between Priority, Exception Code, Handler Address, and Interrupt Priority           |      |

| 4-4   | Correspondence between Each Bit of Interrupt Control Registers and Interrupt Request Signals |      |

| 5-1   | 32-Bit Data Bus (××MWR)                                                                      | 59   |

| 5-2   | 16-Bit Data Bus (xxMWR)                                                                      | 59   |

| 5-3   | 32-Bit Data Bus (xxCAS)                                                                      | 74   |

| 5-4   | 16-Bit Data Bus (××CAS)                                                                      |      |

| 5-5   | RAS Active Period                                                                            | 75   |

| 5-6   | Values of Bus Control Signals during Idle Period                                             | 77   |

| 7-1   | Address Compared by on-page/off-page Judgment                                                | 94   |

| 9-1   | Start Condition                                                                              | 141  |

| 9-2   | BRG Setting Data                                                                             | 144  |

| 10-1  | Capture/Compare Registers                                                                    | 153  |

| 11-1  | Operation in Control Mode                                                                    | 165  |

| 12-1  | Multiplication Function by PLL Synthesizer                                                   | 169  |

| 13-1  | Operation of Clock Generator in Standby Mode                                                 | 173  |

| 13-2  | Operating Status in HALT Mode                                                                | 175  |

| 13-3  | Releasing HALT Mode by Interrupt Request                                                     | 176  |

| 13-4  | Operating Status in STOP Mode                                                                | 177  |

| 14-1  | Status of Output Pin Immediately after Reset                                                 | 182  |

| 14-2  | Initial Value of Each Register after Reset                                                   | 183  |

# LIST OF TABLES

[MEMO]

# CHAPTER 1 GENERAL

The V831 is a 32-bit RISC microprocessor for embedded control applications, with a high-performance 32-bit V830<sup>TM</sup> ( $\mu$ PD705100) processor core and many peripheral functions such as a DRAM/ROM controller, 4-channel DMA controller, real-time pulse unit, serial interface, and interrupt controller.

In addition to high interrupt response speed and optimized pipeline structure, the V831 offers sum-of-products operation instructions, concatenated shift instructions, and high-speed branch instructions to realize multimedia functions, and therefore, can provide high performance in multimedia systems such as internet/intra-net systems, car navigation systems, high-performance television, and color FAXes.

# 1.1 Features

| • | CPU function                                            |                                        |  |  |

|---|---------------------------------------------------------|----------------------------------------|--|--|

|   | V830-compatible instructions                            |                                        |  |  |

|   | Instruction cache                                       | : 4K bytes                             |  |  |

|   | Instruction RAM                                         | ,                                      |  |  |

|   |                                                         | : 4K bytes                             |  |  |

|   | Data cache                                              | : 4K bytes                             |  |  |

|   | Data RAM                                                | : 4K bytes                             |  |  |

|   | Minimum number of instruction execution cycle           | s: 1 cycle                             |  |  |

|   | Memory space and I/O space                              | : 4G bytes each                        |  |  |

|   | Number of general-purpose registers                     | : 32 bits × 32                         |  |  |

| • | Interrupt/exception function                            |                                        |  |  |

|   | Non-maskable: External input: 1                         |                                        |  |  |

|   | Maskable : External input : 8 (of which 4               | are multiplexed with internal sources) |  |  |

|   | Internal source: 11 types                               |                                        |  |  |

|   | Priority can be specified in 4 groups.                  |                                        |  |  |

| • | Bus control function                                    |                                        |  |  |

|   | Chip select output: 8 blocks (RAS + 7 $\overline{CS}$ ) |                                        |  |  |

|   | Memory and I/O space selectable for 4 $\overline{CS}$   |                                        |  |  |

|   | Linear address space of each block: 16M bytes           |                                        |  |  |

| • | Wait control function                                   |                                        |  |  |

|   | DRAM space : Software control of 0 c                    | or 1 wait state                        |  |  |

|   | Other memory spaces : Software control of 0 to          | o 7 wait states                        |  |  |

|   | I/O space : Software control of 0 to                    |                                        |  |  |

|   | Idle state : 0 to 3 states can be in                    |                                        |  |  |

|   |                                                         | 36116U.                                |  |  |

| • | Memory access control function                              |         |  |  |  |

|---|-------------------------------------------------------------|---------|--|--|--|

|   | DRAM hiper page mode supported                              |         |  |  |  |

|   | Page mode of Page-ROM supported                             |         |  |  |  |

| • | • DMA function                                              |         |  |  |  |

|   | 4 channels                                                  |         |  |  |  |

|   | Maximum number of transfers : 16,777,216 (2 <sup>24</sup> ) |         |  |  |  |

|   | Transfer type : 2-cycle transfer                            |         |  |  |  |

|   | Transfer mode : Single transfer and demand transfer         |         |  |  |  |

|   | Programmable wait function                                  |         |  |  |  |

| • | Serial interface function                                   |         |  |  |  |

|   | Asynchronous serial interface (UART) : 1 channel            |         |  |  |  |

|   | Clocked serial interface (CSI) : 1 channel                  |         |  |  |  |

|   | On-chip dedicated baud rate generator: 1 channel            |         |  |  |  |

| • | Timer/counter function                                      |         |  |  |  |

|   | 16-bit timer/event counter : 1 channel                      |         |  |  |  |

|   | Timer output : 2                                            |         |  |  |  |

|   | 16-bit capture/compare register: 4                          |         |  |  |  |

|   | 16-bit interval timer : 1 channel                           |         |  |  |  |

| • | Port function                                               |         |  |  |  |

|   | 3 I/O ports                                                 |         |  |  |  |

| • | Clock generation function                                   |         |  |  |  |

|   | PLL clock synthesizer                                       |         |  |  |  |

| • | Standby function                                            |         |  |  |  |

|   | HALT and STOP modes                                         |         |  |  |  |

| • | Debug function                                              |         |  |  |  |

|   | Debug-dedicated synchronous serial interface: 1 channel     |         |  |  |  |

|   | Trace-dedicated interface : 1 channel                       |         |  |  |  |

|   | Trace function : Branch PC trace and data                   | a trace |  |  |  |

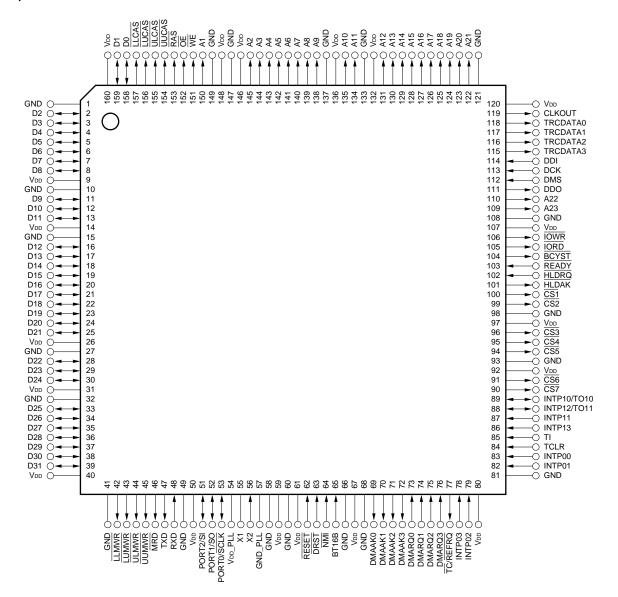

| • | Package                                                     |         |  |  |  |

|   | 160-pin plastic LQFP (24 $	imes$ 24 mm)                     |         |  |  |  |

# 1.2 Application Fields

- Internet/intra-net systems

- Car navigation

- High-performance television

- Color FAX

# 1.3 Ordering Information

| Part Number         | Package                                                |

|---------------------|--------------------------------------------------------|

| μPD705101GM-100-8ED | 160-pin plastic LQFP (fine pitch) ( $24 \times 24$ mm) |

# 1.4 Pin Configuration (Top View)

• 160-pin plastic LQFP (fine pitch) (24 × 24 mm)

#### μPD705101GM-100-8ED

21

# Pin names

| A1 to A23                                          | : Address Bus                       | NMI      | : Non-Maskable Interrupt Request    |

|----------------------------------------------------|-------------------------------------|----------|-------------------------------------|

| BCYST                                              | : Bus Cycle Start                   | OE       | : Output Enable                     |

| BT16B                                              | : Boot Bus Size 16 bit              | PORT0 to | PORT2                               |

| CLKOUT                                             | : Clock Out                         |          | : Port                              |

| $\overline{\text{CS1}}$ to $\overline{\text{CS1}}$ | 7 : Chip Select                     | RAS      | : Row Address Strobe                |

| D0 to D31                                          | : Data Bus                          | READY    | : Ready                             |

| DCK                                                | : Debug Clock                       | REFRQ    | : Refresh Request                   |

| DDI                                                | : Debug Data Input                  | RESET    | : Reset                             |

| DDO                                                | : Debug Data Output                 | RXD      | : Receive Data                      |

| DMAAK0 to                                          | DMAAK3                              | SCLK     | : Serial Clock                      |

|                                                    | : DMA Acknowledge                   | SI       | : Serial Input                      |

| DMARQ0 t                                           | o DMARQ3                            | SO       | : Serial Output                     |

|                                                    | : DMA Request                       | TC       | : Terminal Count                    |

| DMS                                                | : Debug Mode Select                 | TCLR     | : Timer Clear                       |

| DRST                                               | : Debug Reset                       | ТΙ       | : Timer Input                       |

| GND                                                | : Ground                            | TO10, TO | 11: Timer Output                    |

| GND_PLL                                            | : PLL Ground                        | TRCDATA  | A0 to TRCDATA3                      |

| HLDAK                                              | : Hold Acknowledge                  |          | : Trace Data                        |

| HLDRQ                                              | : Hold Request                      | TXD      | : Transmit Data                     |

| INTP00 to                                          | INTP03, INTP10 to INTP13            | ULCAS    | : Upper Lower Column Address Strobe |

|                                                    | : Interrupt Request From Peripheral | ULMWR    | : Upper Lower Memory Write          |

| IORD                                               | : I/O Read                          | UUCAS    | : Upper Upper Column Address Strobe |

| IOWR                                               | : I/O Write                         | UUMWR    | : Upper Upper Memory Write          |

| LLCAS                                              | : Lower Lower Column Address Strobe | Vdd      | : Power Supply                      |

| LLMWR                                              | : Lower Lower Memory Write          | Vdd_PLL  | : PLL Power Supply                  |

| LUCAS                                              | : Lower Upper Column Address Strobe | WE       | : Write Enable                      |

| LUMWR                                              | : Lower Upper Memory Write          | X1, X2   | : Crystal Resonator                 |

| MRD                                                | : Memory Read                       |          |                                     |

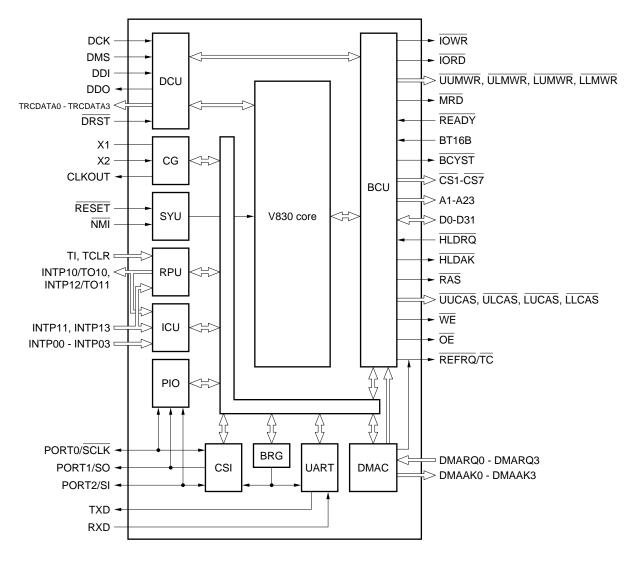

# 1.5 Internal Block Configuration

The internal block configuration of the V831 is as shown below.

# 1.6 Internal Units

The internal units of the V831 and their functions are as follows:

# (1) Bus control unit (BCU)

Controls the address bus, data bus, and control bus pins. The major functions of BCU are as follows:

#### (a) Bus arbitration

Arbitrates the bus mastership among bus masters (CPU, DRAMC, DMAC, and external bus masters). The bus mastership can be changed after completion of the bus cycle under execution, and in an idle state.

# (b) Wait control

Controls eight areas in the 16M-byte space corresponding to a RAS signal and seven chip select signals  $(\overline{CS1}$  through  $\overline{CS7}$ ). Generates chip select signals, controls wait states, and selects the type of bus cycle.

#### (c) DRAM controller

Generates RAS and four CAS signals, and controls access to DRAM. The hyper page mode of DRAM is supported and DRAM can be accessed in two types of cycle: normal access (off-page) and hyper page access (on-page).

#### (d) ROM controller

Accessing ROM with page access function is supported. The bus cycle immediately before and addresses are compared, and wait states are controlled in the normal access (off-page) and page access (on-page) modes. A page width of 8 bytes to 16 bytes can be supported.

#### (2) Interrupt controller (ICU)

Services maskable interrupt requests (INTP00 through INTP03, and INTP10 through INTP13) from internal peripheral hardware and external sources. The priorities of these interrupt requests can be specified in units of four groups, and edge-triggered or level-triggered interrupts can be nested.

#### (3) DMA controller (DMAC)

Transfers data between memory and I/O in the place of the CPU. The transfer type is 2-cycle transfer. Two transfer modes, single transfer and demand transfer, are available.

#### (4) Serial interface (UART/CSI/BRG)

One asynchronous serial interface (UART) channel and one clocked serial interface (CSI) channel is provided. As the serial clock source, the output of the baud rate generator (BRG) and the bus clock can be selected.

# (5) Real-time pulse unit (RPU)

Provides timer/counter functions. The on-chip 16-bit timer/event counter and 16-bit interval timer can be used to calculate pulse intervals and frequencies, and to output programmable pulses.

# (6) Clock generator (CG)

A frequency 3 times higher than that of a resonator connected to the X1 and X2 pins is supplied as the operating clock of the CPU. In addition, a bus clock (with the same cycle as the input clock) is also supplied as the operating clock of the peripheral units. An external clock can be also input instead of connecting a resonator.

# (7) Port (PIO)

Provides port functions. Three I/O ports are available. The pins of these ports can be used as port pins or serial control pin.

# (8) System control unit (SYU)

A circuit that rejects noise on the RESET signal (input)/NMI signal (input) is provided.

# (9) Debug control unit (DCU)

A circuit to realize mapping and trace functions is provided to implement basic debugging functions.

[MEMO]

# CHAPTER 2 PIN FUNCTION

# 2.1 Pin Function List

|                                                                       | 1              | T                                              | (1/2)           |

|-----------------------------------------------------------------------|----------------|------------------------------------------------|-----------------|

| Pin Name                                                              | I/O            | Function                                       | Multiplexed Pin |

| D0 - D31                                                              | 3-state I/O    | Data bus                                       |                 |

| A1 - A23                                                              | 3-state output | Address bus                                    |                 |

| UUCAS                                                                 |                | Column address strobe (most significant byte)  | —               |

| ULCAS                                                                 |                | Column address strobe (second byte)            | —               |

| LUCAS                                                                 |                | Column address strobe (third byte)             | —               |

| LLCAS                                                                 |                | Column address strobe (least significant byte) | —               |

| RAS                                                                   |                | Row address strobe/chip select                 | —               |

| UUMWR                                                                 |                | Memory write strobe (most significant byte)    | —               |

| ULMWR                                                                 |                | Memory write strobe (second byte)              | _               |

| LUMWR                                                                 |                | Memory write strobe (third byte)               | _               |

| LLMWR                                                                 |                | Memory write strobe (least significant byte)   | _               |

| MRD                                                                   |                | Memory read strobe                             | —               |

| WE                                                                    |                | DRAM write strobe                              | _               |

| OE                                                                    |                | DRAM read strobe                               | —               |

| IORD                                                                  |                | I/O read strobe                                | _               |

| IOWR                                                                  |                | I/O write strobe                               | _               |

| REFRQ                                                                 |                | DRAM refresh request                           | TC              |

| $\overline{\text{CS1}}, \overline{\text{CS2}}, \overline{\text{CS7}}$ |                | Memory chip select                             | _               |

| CS3 - CS6                                                             |                | Memory chip select / I/O chip select           | _               |

| BCYST                                                                 |                | Bus cycle start                                | —               |

| BT16B                                                                 | Input          | Specifies bus size on boot                     | _               |

| READY                                                                 |                | Enables end of bus cycle                       |                 |

| DMARQ0 - DMARQ3                                                       |                | DMA request (CH0 through CH3)                  | —               |

| DMAAK0 - DMAAK3                                                       | Output         | DMA enable (CH0 through CH3)                   |                 |

| TC                                                                    |                | DMA transfer end                               | REFRQ           |

| RXD                                                                   | Input          | UART data input                                | _               |

| TXD                                                                   | Output         | UART data output                               | —               |

| SI                                                                    | Input          | CSI data input                                 | PORT2           |

| SO                                                                    | Output         | CSI data output                                | PORT1           |

| SCLK                                                                  | I/O            | CSI clock I/O                                  | PORT0           |

| ТІ                                                                    | Input          | Timer 1 count clock input                      | —               |

| TCLR                                                                  | 1              | Timer 1 clear, start                           | —               |

| TO10                                                                  | Output         | RPU pulse output                               | INTP10          |

| TO11                                                                  | 1              |                                                | INTP12          |

|                        |                |                                                                    | (2/2)           |

|------------------------|----------------|--------------------------------------------------------------------|-----------------|

| Pin Name               | I/O            | Function                                                           | Multiplexed Pin |

| INTP10                 | Input          | Interrupt request                                                  | TO10            |

| INTP11                 |                |                                                                    |                 |

| INTP12                 |                |                                                                    | TO11            |

| INTP13                 |                |                                                                    |                 |

| INTP00 - INTP03        |                |                                                                    |                 |

| HLDRQ                  |                | Bus request                                                        |                 |

| HLDAK                  | Output         | Bus enable                                                         |                 |

| NMI                    | Input          | Non-maskable interrupt request                                     |                 |

| RESET                  |                | System reset                                                       |                 |

| PORT0                  | I/O            | Port                                                               | SCLK            |

| PORT1                  |                |                                                                    | SO              |

| PORT2                  |                |                                                                    | SI              |

| X1                     | _              | Connects crystal resonator. (Opened when external clock is input.) | -               |

| X2                     | Input          | Connects crystal resonator or inputs external clock.               | _               |

| CLKOUT                 | Output         | Bus clock output                                                   | _               |

| DCK                    | Input          | Debug clock input                                                  | —               |

| DDI                    |                | Debug data input                                                   | _               |

| DDO                    | 3-state output | Debug data output                                                  | —               |

| DMS                    | Input          | Debug mode select                                                  | _               |

| DRST                   |                | Reset input (debug module)                                         | —               |

| TRCDATA0 -<br>TRCDATA3 | Output         | Trace data output                                                  | —               |

| Vdd                    | _              | Positive power supply                                              | _               |

| GND                    |                | Ground potential                                                   | _               |

|                        |                | Positive power supply for PLL (internal clock generator)           |                 |

| GND_PLL                | 7              | Ground potential for PLL (internal clock generator)                | _               |

# 2.2 Pin Status

Table 2-1 shows the operating status of each pin.

| Operating Status<br>Pin    | Reset        | Bus Hold     | HALT Mode    | STOP Mode |

|----------------------------|--------------|--------------|--------------|-----------|

| CLKOUT                     | Clock output | Clock output | Clock output | 0         |

| CS1 - CS7                  | 1            | Hi-Z         | Note 1       | 1         |

| A1 - A23                   | Undefined    | Hi-Z         | Note 1       | Undefined |

| D0 - D31                   | Hi-Z         | Hi-Z         | Note 1       | Hi-Z      |

| BCYST                      | 1            | Hi-Z         | Note 1       | 1         |

| MRD                        | 1            | Hi-Z         | Note 1       | 1         |

| ŌĒ                         | 1            | Hi-Z         | Note 1       | 1         |

| WE                         | 1            | Hi-Z         | Note 1       | 1         |

| LLMWR, LUMWR, ULMWR, UUMWR | 1            | Hi-Z         | Note 1       | 1         |

| IORD                       | 1            | Hi-Z         | Note 1       | 1         |

| IOWR                       | 1            | Hi-Z         | Note 1       | 1         |

| HLDAK                      | 1            | 0            | Note 1       | 1         |

| RAS                        | 1            | Hi-Z         | Note 1       | 0 Note 2  |

| LLCAS, UUCAS, UUCAS        | 1            | Hi-Z         | Note 1       | O Note 3  |

| TC/REFRQ                   | 1            | Hi-Z         | Note 1       | 0 Note 4  |

| Table 2-1. | Status of | Each Pin |

|------------|-----------|----------|

|------------|-----------|----------|

**Notes 1**. DMA operation can be performed in the HALT mode.

- 2. The status before the STOP mode is retained if CBR self-refresh is disabled.

- 3. 1 if CBR self-refresh is disabled.

- 4. 1 if CBR self-refresh is disabled. If TC is selected, however, TC signal is output.

- **Remark** 0 : Low-level output

- 1 : High-level output

- Hi-Z : high impedance

# 2.3 Pin Function

# 2.3.1 Address bus

# (1) A1 through A23 (Address Bus) --- 3-state output

The address bus outputs address signals when the V831 accesses an external main memory or I/O unit. An address space of  $2^{24}$  bytes can be accessed. The address signals change at the rising edge of the bus clock.

# 2.3.2 Data bus

# (1) D0 through D31 (Data Bus) --- 3-state I/O

The data bus inputs or outputs write data or read data when the V831 accesses an external main memory or I/O unit. These data signals change at the rising edge of the bus clock.

# 2.3.3 Bus control signals

# (1) READY (Ready) --- Input

This signal extends the bus cycle to match it to the access time of the memory or I/O. It is sampled at the rising edge of the bus clock immediately after the read/write signal. Be sure to observe the setup/hold time of the READY input; otherwise, the operation will not be guaranteed.

# (2) HLDRQ (Hold Request) --- Input

This pin requests the CPU for the bus mastership. It is sampled at the rising edge of the bus clock.

# (3) HLDAK (Hold Acknowledge) --- Output

This is an acknowledge signal in response to the HLDRQ input.

When the CPU receives the HLDRQ signal, it asserts the HLDAK signal active. When HLDRQ is deasserted inactive, the CPU deasserts the HLDAK signal inactive, and is granted the bus mastership again.

# (4) MRD (Memory Read) --- 3-state output

This is a strobe signal indicating that the bus cycle under execution is a read cycle of the external memory. It changes in synchronization with the falling of the bus clock.

If the Page-ROM cycle continues, however, this signal is always active. It is always inactive in the refresh cycle.

# (5) LLMWR (Lower Lower Memory Write) --- 3-state output

This is a strobe signal for a data write to the external memory. It validates the least significant byte of the data bus. This signal changes in synchronization with the falling of the bus clock.

# (6) LUMWR (Lower Upper Memory Write) --- 3-state output

This is a strobe signal for a data write to the external memory. It validates the third byte of the data bus. This signal changes in synchronization with the falling of the bus clock.

# (7) ULMWR (Upper Lower Memory Write) --- 3-state output

This is a strobe signal for a data write to the external memory. It validates the second byte of the data bus. This signal changes in synchronization with the falling of the bus clock.