# SSI 32R2020R/2021R/2023R

5V, 2, 4, 6, 10-Channel Thin-Film Read/Write Device

March 1994

#### DESCRIPTION

0394 - rev.

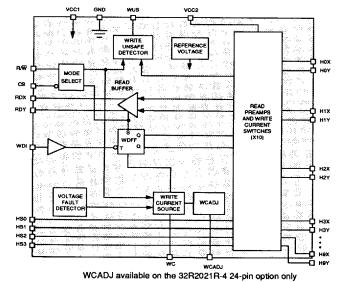

The SSI 32R2020R/2021R/2023R are bipolar monolithic integrated circuits designed for use with two-terminal recording heads. They provide a low noise read amplifier, write current control, and data protection circuitry for up to ten channels. The SSI 32R2020R/2021R/2023R provide internal 320Ω damping resistors. Damping resistors are switched in during write mode and switched out during read mode. Power supply fault protection is provided by disabling the write current generator during power sequencing. System write to read recovery time is significantly improved by controlling the read channel common mode output voltage shift in the write mode. The 32R2021R option provides the user with a controllable write current adjustment feature.

The SSI 32R2020R/2021R/2023R require only +5V power supplies and are available in a variety of packages. They are hardware compatible with the 32R4610A/4611A read/write devices.

### **FEATURES**

- +5V ±10% supply

- Low power

- PD = 130 mW read mode (Nom)

- PD = 3.3 mW idle (Nom)

- High Performance:

- Multiple galn options

- Input noise = 0.56 nV/√Hz (Nom)

- Input capacitance = 16 pF (Nom)

- Write current range = 5-35 mA

- · Self switching damping resistance

- Designed for two-terminal thin-film or MIG heads with inductance up to 5.0 μH

- Pin compatible with the 32R4610AR/4611AR

- · Write unsafe detection

- Power supply fault protection

- Head short to ground protection

## **BLOCK DIAGRAM**

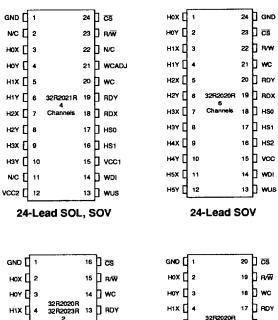

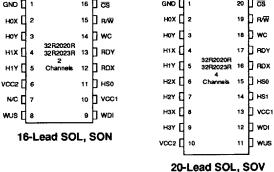

### **PIN DIAGRAM**

20-Lead SOL

CAUTION: Use handling procedures necessary for a static sensitive component.

■ 8253965 0014165 000 ■

3R-1

#### **FUNCTIONAL DESCRIPTION**

The SSI 32R2020R/2021R/2023R have the ability to address up to 10 two-terminal heads and provide write drive or read amplification. Mode control and head selection are described in Tables 1 and 2. The TTL inputs  $R/\overline{W}$  and  $\overline{CS}$  have internal pull-up resistors to prevent an accidental write condition. HS0, HS1, HS2 and HS3 have internal pulldown resistors. Internal clamp circuitry will protect the IC from a head short to ground condition in any mode.

**TABLE 1: Mode Select**

| CS | R/W | Mode  |

|----|-----|-------|

| 0  | 0   | Write |

| 0  | 1   | Read  |

| 1  | 0   | Idle  |

| 1  | 1   | Idle  |

**TABLE 2: Head Select**

| HS3 | HS2 | HS1 | HS0 | Head |

|-----|-----|-----|-----|------|

| 0   | 0   | 0   | 0   | 0    |

| 0   | 0   | 0   | 1   | 1    |

| 0   | 0   | 1   | 0   | 2    |

| 0   | 0   | 1   | 1   | 3    |

| 0   | 1   | 0   | 0   | 4    |

| 0   | 1   | 0   | 1   | 5    |

| 0   | 1   | 1   | 0   | 6    |

| 0   | 1   | 1   | 1   | 7    |

| 1   | 0   | 0   | 0   | 8    |

| 1   | 0   | 0   | 1   | 9    |

#### WRITE MODE

Taking both  $\overline{\text{CS}}$  and  $R/\overline{\text{W}}$  low selects write mode which configures the SSI 32R2020R/2021R/2023R as a current switch and activates the Write Unsafe (WUS) detector circuitry. Head current is toggled between the X and Y side of the selected head on each high to low transition of the Write Data Input (WDI). Changing from read or idle mode to write mode initializes the Write Data Flip-Flop to pass write current into the "X" pin. In this case, the Y side of the head will be higher potential

than the X side. The magnitude of the write current (0-pk) is given by:

$$Iw = \frac{K \cdot Vwc}{Rwc}$$

Rwc is connected from pin WC to GND. Note the actual head current Ix, y is given by:

$$Ix, y = \frac{Iw}{1 + Rh/Rd}$$

Where:

Rh = Head resistance plus external wire resistance

Rd = Damping resistance

In write mode a  $320\Omega$  damping resistor is switched in across the Hx, Hy ports.

The 32R2021R adds a feature which allows the user to adjust the lw current by a finite amount. The WCADJ pin is used to adjust write current for write operations on different zones of the disk. It is used by switching a separate write current adjust resistor in and out on the WCADJ pin or by connecting a DAC to that pin to sink a controllable amount of current. The WCADJ pin is nominally biased to VCC/2. Sinking current from this pin to ground will divert a proportional amount of current from the actual head current while maintaining a constant current through the WC resistor and VCC. Allowing WCADJ to float or pulling it high will cut off the circuit and it will have no effect. A TTL gate can be used as a switch with a small degradation in accuracy. The amount of write current decrease is shown below:

Iw head (decrease) (mA) = (29 • Vwcadu/Rwcadu)

where:

VwcadJ = VCC/2 (volts)

Rwcadu = write current adjust setting resistor ( $k\Omega$ )

Example: For a 7.25 mA head current decrease,

RWCADJ =  $(27 \cdot 2.5) / 7.25 = 10 \text{ k}\Omega$

#### **POWER SUPPLY FAULT PROTECTION**

A voltage fault detection circuit improves data security by disabling the write current generator during a voltage fault or power startup regardless of mode. Note that WUS does not necessarily turn on to flag a power supply fault condition.

### **HEAD SHORT TO GROUND PROTECTION**

The 2020R/2021R/2023R provides a head short to ground protection circuit in any mode. In idle or read mode, current out of the head port will not exceed 20 mA if any head is shorted to ground. In write mode, if any head is shorted to ground (regardless if it is selected or not) the write current generator will turn off, the WUS flag will go high, and current will be limited to less than 1 mA out of the head port.

#### **WRITE UNSAFE**

Any of the following conditions will be indicated as a high level on the Write Unsafe, WUS, open collector output.

- · WDI frequency too low

- Device in read mode

- Chip disabled

- No head current

- Head opened (not active on 32R2023R)

- · Head short to ground

To insure proper WUS operation, the product of write current, WDI frequency, and head inductance should be less than 500 mA•µH•MHz. To insure no false WUS trigger, the product of head current and head resistance (lx,y•Rh) should be between 100 mV and 1.7V.

**WDI frequency too low** is detected if the WDI frequency falls below 500 kHz (typ). Consult the WUS Safe to Unsafe timing for range of frequency detection.

**Device in read mode** and **chip disabled** will flag WUS if  $R/\overline{W}$  is high or  $\overline{CS}$  is high.

No head current will flag WUS if Rwc =  $\infty$  and the selected head is present.

**Head opened** will flag WUS if Rh =  $\infty$  and under the condition that VCC/lw < 0.25 V/mA (not active on 32R2023R).

**Head short to ground** is described in the preceding paragraph.

Upon entering write mode, WUS is valid after two high to low transitions of WDI following the required readwrite transition time (0.6 µs max).

#### **READ MODE**

The read mode configures the SSI 32R2020R/2021R/2023R as a low noise differential amplifier and deactivates the write current generator. The damping resistor is switched out of the circuit allowing a high impedance input to the read amplifier. The RDX and RDY output are driven by emitter followers. They should be AC coupled to the load. The (X,Y) inputs are non-inverting to the (X,Y) outputs.

Note that in idle or write mode, the read amplifier is deactivated and RDX, RDY outputs become high impedance. This facilitates multiple R/W applications (wired-OR RDX, RDY) and minimizes voltage drifts when switching from write to read mode. Note also that the write current source is deactivated for both the read and idle mode.

#### IDLE MODE

Taking  $\overline{\text{CS}}$  high selects the idle mode which switches the RDX and RDY outputs into a high impedance state and deactivates the device. Power consumption in this mode is held to a minimum.

3B-3

### PIN DESCRIPTION

| NAME                    | TYPE | DESCRIPTION                                                               |

|-------------------------|------|---------------------------------------------------------------------------|

| HS0, HS1, †<br>HS2, HS3 | 1    | Head Select: selects one of ten heads                                     |

| CS                      | i    | Chip Select: a high inhibits the chip                                     |

| R∕W †                   | 1    | Read/Write : a high selects read mode                                     |

| wus +                   | 0    | Write Unsafe: a high indicates an unsafe writing condition                |

| WDI +                   | 1    | Write Data In: changes the direction of the current in the recording head |

| H0X - H9X;<br>H0Y - H9Y | 1/0  | X, Y Head Connections                                                     |

| RDX, RDY +              | 0    | X, Y Read Data: differential read data output                             |

| WC +                    |      | Write Current: used to set the magnitude of the write current             |

| WCADJ* †                |      | Write Current Adjust: Used to fine tune the write current                 |

| VCC1                    | 1    | +5V Supply                                                                |

| VCC2                    | 1    | +5V Supply for Write current drivers                                      |

| GND                     |      | Ground                                                                    |

|                         |      | 4-pin option only                                                         |

<sup>†</sup> When more than one R/W device is used, signals can be wire OR'ed

### **ELECTRICAL SPECIFICATIONS**

### **ABSOLUTE MAXIMUM RATINGS**

Operation above maximum ratings may permanently damage the device.

| PARAMETER                |      | RATING                |

|--------------------------|------|-----------------------|

| DC Supply Voltage        | VCC1 | -0.3 to +6 VDC        |

|                          | VCC2 | -0.3 to +6 VDC        |

| Write Current            | lw   | 60 mA                 |

| Digital Input Voltage    | Vin  | -0.3 to VCC1 +0.3 VDC |

| Head Port Voltage        | VH   | -0.3 to VCC2 +0.3 VDC |

| Output Current: RDX, RDY | 10   | -6 mA                 |

|                          | WUS  | +8 mA                 |

| Storage Temperature      | Tstg | -65 to +150°C         |

### **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                      |             | RATING        |  |

|--------------------------------|-------------|---------------|--|

| DC Supply Voltage              | VCC1 = VCC2 | 5 ±10% VDC    |  |

| Operating Junction Temperature | Tj          | +25 to +135°C |  |

| Recommended Head Load Range    | Lh          | 0.3 - 5.0 μΗ  |  |

### **DC CHARACTERISTICS**

Recommended operating conditions apply unless otherwise specified.

| PARAMETER           | CONDITION   | MIN | NOM        | MAX          | UNIT |

|---------------------|-------------|-----|------------|--------------|------|

| VCC1 Supply Current | Read Mode   |     | 18         | 25           | mA   |

|                     | Write Mode  |     | 22         | 29           | mA   |

|                     | Idle Mode   |     | 0.6        | 0.95         | mA   |

| VCC2 Supply Current | Read Mode   |     | 8          | 11           | mA   |

|                     | Write Mode  |     | 4 + lw     | 7 + lw       | mA   |

|                     | Idle Mode   |     | 0          | 0.2          | mA   |

| Power Dissipation   | Read Mode   |     | 130        | 200          | mW   |

|                     | Write Mode  |     | 130 + 4 lw | 200 + 4.3 lw | mW   |

|                     | Idle Mode   |     | 3.3        | 6.5          | mW   |

| VCC1 Fault Voltage  | lw < 0.2 mA | 3.5 | 3.9        | 4.2          | VDC  |

#### **DIGITAL INPUTS**

| Input Low Voltage (Vil)      |                |      | 0.8 | VDC |

|------------------------------|----------------|------|-----|-----|

| Input High Voltage (Vil)     |                | 2.0  |     | VDC |

| Input Low Current            | Vil = 0.8V     | -0.4 |     | mA  |

| Input High Current           | Vih = 2.0V     |      | 100 | mA  |

| WUS Output Low Voltage (Vol) | lol = 2 mA max |      | 0.5 | VDC |

### WRITE CHARACTERISTICS

Recommended operating conditions apply unless otherwise specified.

| Write Current Constant                 | "K" |                      |      |       | 0.99 |       |

|----------------------------------------|-----|----------------------|------|-------|------|-------|

| Write Current Voltage                  | Vwc |                      | 1.15 | 1.25  | 1.35 | V     |

| WCADJ Voltage<br>SSI 32R2021R          |     | lwcadu = 0 to 0.5 mA | 2.0  | VCC/2 | 3.0  | VDC   |

| Ihead(Decrease)/IwcadJ<br>SSI 32R2021R |     |                      | 23   | 27    | 31   | mA/mA |

| lwcatu Range<br>SSI 32R2021R           |     |                      | 0.0  |       | 0.5  | mA    |

3B-5

#### WRITE CHARACTERISTICS (continued)

Recommended operating conditions apply unless otherwise specified.

| PARAMETER                               | ·                 | CONDITION            | MiN | NOM  | MAX | UNIT    |

|-----------------------------------------|-------------------|----------------------|-----|------|-----|---------|

| Differential Head Vo                    | oltage Swing      |                      | 4.2 | 5.6  |     | Vpp     |

|                                         |                   | Open Head Iw = 20 mA | 3.4 | 5.0  |     | Vpp     |

| Unselected Head C                       | urrent            |                      |     |      | 1   | mA (pk) |

| Head Differential Da<br>Resistance (Rd) | amping<br>32R2020 |                      |     | 2650 |     | Ω       |

|                                         | 32R2020R          |                      |     | 320  |     | Ω       |

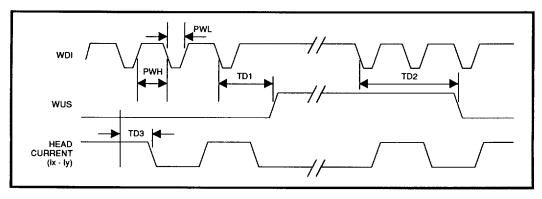

| WDI Pulse Width                         | Vil ≥ 0.2V        | PWH                  | 10  |      |     | ns      |

|                                         |                   | PWL                  | 5   |      |     | ns      |

| Write Current Rang                      | e (lw)            |                      | 5   |      | 35  | mA      |

| Head Differential Load                  | d Capacitance     |                      |     |      | 25  | pF      |

### **READ CHARACTERISTICS**

Recommended operating conditions apply unless otherwise specified. CL (RDX, RDY) < 20 pF, RL (RDX, RDY) = 1 k $\Omega$ .

| Differential Voltage Gain     |        | Vin = 1 mVpp @1 MHz (V                                                               | 160 | 200  | 240  | V/V    |

|-------------------------------|--------|--------------------------------------------------------------------------------------|-----|------|------|--------|

|                               |        |                                                                                      | 250 | 300  | 350  | V/V    |

|                               |        | (Z'                                                                                  | )   | 400  |      | V/V    |

| Voltage BW                    | -1dB   | Zs  < 5Ω, Vin = 1 mVpp                                                               | 20  |      |      | MHz    |

|                               | -3dB   | $ Zs  < 5\Omega$ , Vin = 1 mVpp                                                      | 45  |      |      | MHz    |

| Input Noise Voltage           |        | BW = 15 MHz, Lh = 0, Rh = 0                                                          |     | 0.56 | 0.75 | nV/√Hz |

| Differential Input Capacitar  | nce    | Vin = 1 mVpp, $f = 5$ MHz                                                            |     | 16   | 22   | рF     |

| Differential Input Resistance | e      | Vin = 1 mVpp, $f = 5$ MHz                                                            | 720 | 1200 |      | Ω      |

| Dynamic Range                 |        | AC input voltage where gain falls to 90% of its small signal gain value, $f = 5$ MHz | 2   |      |      | m∨pp   |

| Common Mode Rejection I       | Ratio  | Vin = 0 VDC + 100 mVpp<br>@ 5 MHz                                                    | 55  |      |      | dB     |

| Power Supply Rejection Ra     | atio   | 100 mVpp @ 5 MHz on VCC                                                              | 50  |      |      | dB     |

| Channel Separation            |        | Unselected channels driven with Vin = 0 VDC + 100 mVpp                               | 55  |      |      | dB     |

| Output Offset Voltage         |        | (V)                                                                                  | )   |      | ±300 | mV     |

|                               |        |                                                                                      |     |      | ±300 | m۷     |

|                               |        | (Z)                                                                                  | )   |      | ±400 | mV     |

| Single Ended Output Resis     | stance | f = 5 MHz                                                                            |     |      | 50   | Ω      |

| Output Current                |        | AC coupled load, RDX to RDY                                                          | 0.9 |      |      | mA     |

3B-6

**...** 8253965 0014170 478 **....**

### READ CHARACTERISTICS (continued)

| PARAMETER            | CONDITION | MIN     | NOM   | MAX     | UNIT |

|----------------------|-----------|---------|-------|---------|------|

| RDX, RDY Common Mode |           | 0.4 VCC | VCC/2 | 0.6 VCC | VDC  |

| Output Voltage       |           |         |       |         |      |

### **SWITCHING CHARACTERISTICS**

Recommended operating conditions apply unless otherwise specified. IW = 20 mA, Lh = 1.0  $\mu$ H, Rh = 30 $\Omega$  f(Data) = 5 MHz.

| PARAME   | TER                  | CONDITIONS                                                                              | MIN | NOM  | MAX | UNIT |

|----------|----------------------|-----------------------------------------------------------------------------------------|-----|------|-----|------|

| R/W      | Read to Write        | R/W to 90% of write current                                                             |     | 0.1  | 0.6 | μs   |

|          | Write to Read        | R/W to 90% of<br>100 mV Read signal envelope                                            |     | 0.1  | 0.6 | μs   |

| CS       | Unselect to Select   | CS to 90% of write current or to 90% of 100 mV 10 MHz                                   |     | 0.2  | 1   | μs   |

|          | Select to Unselect   | CS to 10% of write current                                                              |     | 0.11 | 0.6 | μs   |

| HS0,1 to | any Head             | To 90% of 100 mV 10 MHz<br>Read signal envelope                                         |     | 0.11 | 0.6 | μs   |

| WUS:     | Safe to Unsafe (TD1) | Write mode, loss of WDI<br>transitions. Defines maximum<br>WDI period for WUS operation | 0.6 | 2.0  | 3.6 | μs   |

|          | Unsafe to Safe (TD2) | Fault cleared, from first neg<br>WDI transition                                         |     | 0.1  | 0.6 | μs   |

| Head Cur | rent:                |                                                                                         |     |      |     |      |

|          | WDI to Ix - Iy (TD3) | from 50% points, Lh = 0, Rh = 0                                                         |     | 3    | 10  | ns   |

|          | Asymmetry            | WDI has 1 ns rise/fall time,<br>Lh = 0, Rh = 0                                          |     |      | 1.0 | ns   |

|          | Rise/fall Time       | 10% to 90% points, Lh = 0, Rh = 0                                                       |     | 4    | 6   | ns   |

|          | Rise/fall Time       | Lh = 1 μH, Rh = 30Ω                                                                     |     | 15   |     | ns   |

FIGURE 1: Write Mode Timing Diagram

3B-7

**304 🚾** 8253965 0014171 304

## PACKAGE PIN DESIGNATIONS

These pins are No Connect on the 8-Channel version

CAUTION: Use handling procedures necessary for a static sensitive component.

### **ORDERING INFORMATION**

| DEVICE   | CHANNELS | PACKAGE | READ<br>GAIN | DAMPING<br>RESISTOR | ORDER<br>NUMBER | PACKAGE<br>MARK |

|----------|----------|---------|--------------|---------------------|-----------------|-----------------|

| 32R2020R | 2        | 16 SOL  | 300          | 320Ω                | 32R2020R-2CL    | 32R2020R-2CL    |

|          | 2        | 16 SON  | 300          | 320Ω                | 32R2020R-2CN    | 32R2020R-2CN    |

|          | 4        | 20 SOL  | 300          | 320Ω                | 32R2020R-4CL    | 32R2020R-4CL    |

|          | 4        | 20 SOV  | 300          | 320Ω                | 32R2020R-4CV    | 32R2020R-4CV    |

|          | 4        | 20 SOL  | 200          | -                   | 32R2020V-4CL    | 32R2020V-4CL    |

|          | 4        | 20 SOV  | 400          | 320Ω                | 32R2020RZ-4CV   | 32R2020RZ-4CV   |

|          | 6        | 24 SOV  | 300          | 320Ω                | 32R2020R-6CV    | 32R2020R-6CV    |

|          | 6        | 36 SOV  | 300          | -                   | 32R2020-6CV     | 32R2020-6CM     |

|          | 8        | 36 SOM  | 300          | 320Ω                | 32R2020R-8CM    | 32R2020R-8CM    |

|          | 8        | 36 SOM  | 300          | -                   | 32R2020-8CM     | 32R2020-8CM     |

|          | 10       | 36 SOM  | 300          | 320Ω                | 32R2020R-10CM   | 32R2020R-10CM   |

|          | 10       | 36 SOM  | 300          | -                   | 32R2020-10CM    | 32R2020-10CM    |

| 32R2021  | 4        | 24 SOV  | 300          | 3.20Ω               | 32R2021R-10CV   | 32R2021R-10CV   |

| 32R2023  | 2        | 16 SOL  | 300          | 320Ω                | 32R2023R-2CL    | 32R2023R-2CL    |

|          | 2        | 16 SON  | 300          | 320Ω                | 32R2023R-2CN    | 32R2023R-2CN    |

|          | 4        | 20 SOV  | 300          | 320Ω                | 32R2023R-4CV    | 32R2023R-4CV    |

No responsibility is assumed by Silicon Systems for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Silicon Systems. Silicon Systems reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that the data sheet is current before placing orders.

Silicon Systems, Inc., 14351 Myford Road, Tustin, CA 92680-7022 (714) 573-6000, FAX (714) 573-6914

0394 - rev.

Patent Pending ©1990 Silicon Systems, Inc.

3B-9

8253965 0014173 187 🖿