# 32Kx32 EEPROM MODULE, SMD 5962-94614

#### **FEATURES**

- Access Times of 90, 120, 150ns

- MIL-STD-883 Compliant Devices Available

- Packaging:

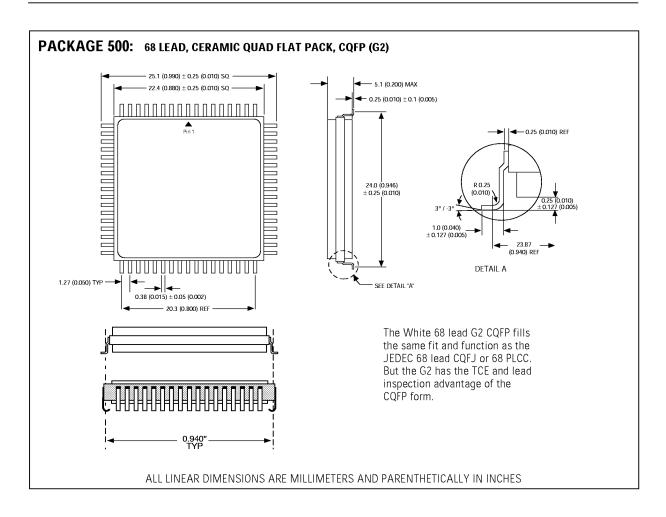

- 68 lead, Hermetic CQFP (G2), 22mm (0.880 inch) square (Package 500). Designed to fit JEDEC 68 lead 0.990" CQFJ footprint (Fig. 2)

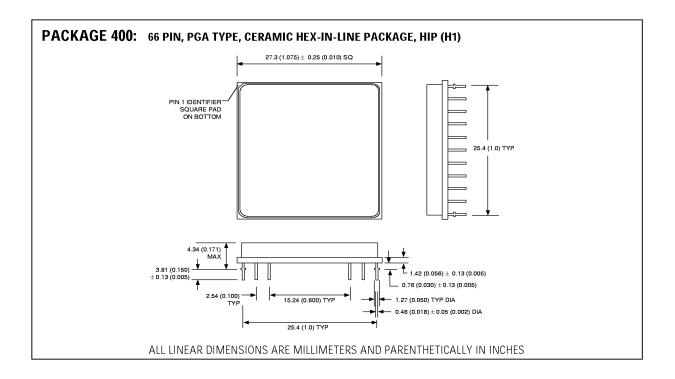

- 66-pin, PGA Type, 1.075 inch square, Hermetic Ceramic HIP (Package 400)

- Data Retention at 25°C, 10 Years

- Write Endurance, 10,000 Cycles

- Organized as 32Kx32; User Configurable 64Kx16 or 128Kx8

- Commercial, Industrial and Military Temperature Ranges

- Automatic Page Write Operation

- Page Write Cycle Time: 10ms Max

- Data Polling for End of Write Detection

- Hardware and Software Data Protection

- TTL Compatible Inputs and Outputs

- 5 Volt Power Supply

- Low Power CMOS, 10mA Standby Typical

- Built-in Decoupling Caps and Multiple Ground Pins for Low Noise Operation

#### FIG. 1 PIN CONFIGURATION FOR WE32K32N-XH1X **TOP VIEW PIN DESCRIPTION** 12 23 45 I/O<sub>0-31</sub> Data Inputs/Outputs OI/O8 OWE2 OI/O15 An-14 Address Inputs WE1-4 Write Enables I/O<sub>25</sub> \( \overline{CS}\_4 \( \overline{O}\_{30} \( \overline{O}\_{30} \) OI/O₃ OCS₂ OI/O14 CS1-4 Chip Selects OI/O10 OGND OI/O13 I/O<sub>28</sub> \( \overline{WE}\_4 \) I/O<sub>29</sub> \( \overline{O}\_2 \) ΟE Output Enable OA13 OI/O11 OI/O12 A6 0 1/O27 0 1/O28 0 Power Supply OA14 OA10 OŒ A7 ( A3 ( A<sub>0</sub>O GND Ground ONC OA11 ONC NC A4 A<sub>1</sub>O Not Connected OWE₁ ONC OA12 As ( ) $A_2$ **BLOCK DIAGRAM** WE<sub>1</sub> CS<sub>1</sub> WE<sub>2</sub>CS<sub>2</sub> WE<sub>3</sub> CS<sub>3</sub> WE4 CS4 ONC OVCC OI/O7 ŌE OI/O₀ OCS₁ OI/O₀ OI/O1 ONC ○I/O<sub>5</sub> I/O<sub>17</sub> GND I/O<sub>21</sub> 32K x 8 32K v 8 32K x 8 32K x 8 I/O<sub>18</sub> O I/O<sub>19</sub> O I/O<sub>20</sub> O OI/O₂ OI/O₃ OI/O₄ 8 8 33 55 66 8 1/00-7 I/O8-15 I/O16-23 1/024-31

#### FIG. 2 PIN CONFIGURATION FOR WE32K32-XG2X **TOP VIEW PIN DESCRIPTION** ON OF THE PROPERTY OF THE PROP I/O<sub>0-31</sub> Data Inputs/Outputs A<sub>0-14</sub> Address Inputs **W**E1-4 Write Enables I/O<sub>0</sub> [] 10 60 1/016 1/01 [ 11 59 1/017 CS<sub>1-4</sub> Chip Selects 1/02 [ 12 58 1/018 ŌĒ Output Enable 1/03 [ 13 57 1/019 Vcc Power Supply 1/04 🛚 14 56 1/020 GND Ground I/O<sub>5</sub> [] 15 55 | 1/021 NC Not Connected I/O6 [ 16 54 1/022 1/07 🛮 17 53 1/023 GND [ 18 52 GND I/O8 [] 19 51 1/024 1/09 20 50 1/025 1/010 [21 49 1/026 1/011 22 48 1/027 I/O12 23 47 1/028 I/O13 [ 24 46 1/029 I/O14 [ 25 45 1/030 I/O15 [ 26 44 1 1/031 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 **BLOCK DIAGRAM** WE1 CS1 WE2 CS2 WE<sub>3</sub> CS<sub>3</sub> WE4CS4 ŌĒ 0.940" 32K x 8 32K x 8 The White 68 lead G2 CQFP fills 32K x 8 32K x 8 the same fit and function as the JEDEC 68 lead CQFJ or 68 PLCC. But the G2 has the TCE and lead inspection advantage of the I/O16-23 1/024-31 1/00-7 I/O8-15 CQFP form.

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                | Symbol |               | Unit |

|------------------------------------------|--------|---------------|------|

| Operating Temperature                    | TA     | -55 to +125   | °C   |

| Storage Temperature                      | Tstg   | -65 to +150   | °C   |

| Signal Voltage Relative to GND           | VG     | -0.6 to +6.25 | ٧    |

| Voltage on $\overline{\text{OE}}$ and A9 |        | -0.6 to +13.5 | ٧    |

#### NOTE:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

| Parameter              | Symbol | Min  | Max       | Unit |

|------------------------|--------|------|-----------|------|

| Supply Voltage         | Vcc    | 4.5  | 5.5       | ٧    |

| Input High Voltage     | Vін    | 2.0  | Vcc + 0.3 | ٧    |

| Input Low Voltage      | VIL    | -0.5 | +0.8      | ٧    |

| Operating Temp. (Mil.) | Ta     | -55  | +125      | °C   |

| Operating Temp. (Ind.) | TA     | -40  | +85       | °C   |

#### **TRUTH TABLE**

| cs | ŌE | WE | Mode        | Data I/O        |

|----|----|----|-------------|-----------------|

| Н  | Х  | Χ  | Standby     | High Z          |

| L  | L  | Н  | Read        | Data Out        |

| L  | Н  | L  | Write       | Data In         |

| Х  | Н  | Χ  | Out Disable | High Z/Data Out |

| Х  | Х  | Н  | Write       | ·               |

| Х  | L  | Х  | Inhibit     |                 |

## CAPACITANCE

$(TA = 25^{\circ} C)$

| Parameter                                   | Symbol     | Condition            | Max | Unit |

|---------------------------------------------|------------|----------------------|-----|------|

| Address Input Capacitance<br>OE Capacitance | Cad<br>Coe | Vin = 0V, f = 1.0MHz | 50  | pF   |

| CS <sub>1-4</sub> Capacitance               | Ccs        | VIN = 0V, f = 1.0MHz | 20  | pF   |

| WE <sub>1-4</sub> Capacitance               | Cwe        | VIN = 0V, f = 1.0MHz | 20  | pF   |

| Data I/O Capacitance                        | Cı/o       | Vin = 0V, f = 1.0MHz | 20  | pF   |

This parameter is guaranteed by design but not tested.

### **DC CHARACTERISTICS**

$(Vcc = 5.0V, GND = 0V, TA = -55^{\circ}C to +125^{\circ}C)$

| Parameter                          | Symbol      | Conditions                                                      | <u>-90</u> |      | <u>-120</u> |      | <u>-150</u> |      | Units |

|------------------------------------|-------------|-----------------------------------------------------------------|------------|------|-------------|------|-------------|------|-------|

|                                    |             |                                                                 | Min        | Max  | Min         | Max  | Min         | Max  |       |

| Input Leakage Current              | lu          | Vcc = 5.5, $Vin = GND$ to $Vcc$                                 |            | 10   |             | 10   |             | 10   | μΑ    |

| Output Leakage Current             | ILO x 32    | $\overline{CS}$ = ViH, $\overline{OE}$ = ViH, Vout = GND to Vcc |            | 10   |             | 10   |             | 10   | μΑ    |

| Operating Supply Current x 32 Mode | ICC x 32    | $\overline{CS} = VIL, \overline{OE} = VIH, f = 5MHz$            |            | 250  |             | 200  |             | 150  | mA    |

| Standby Current                    | IsB         | $\overline{CS} = V_{IH}, \overline{OE} = V_{IH}, f = 5MHz$      |            | 2.5  |             | 2.5  |             | 2.5  | mA    |

| Output Low Voltage                 | <b>V</b> ol | IOL = 2.1mA, Vcc = 4.5V                                         |            | 0.45 |             | 0.45 |             | 0.45 | V     |

| Output High Voltage                | Vон         | $IoH = -400\mu A$ , $Vcc = 4.5V$                                | 2.4        |      | 2.4         |      | 2.4         |      | ٧     |

NOTE: DC test conditions:  $V_{IH} = V_{CC} -0.3V$ ,  $V_{IL} = 0.3V$

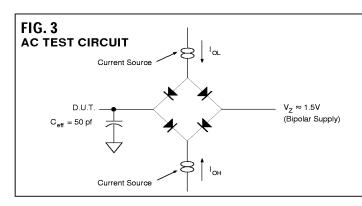

### **AC TEST CONDITIONS**

| Parameter                        | Тур                | Unit |

|----------------------------------|--------------------|------|

| Input Pulse Levels               | VIL = 0, VIH = 3.0 | ٧    |

| Input Rise and Fall              | 5                  | ns   |

| Input and Output Reference Level | 1.5                | ٧    |

| Output Timing Reference Level    | 1.5                | ٧    |

#### NOTES

Vz is programmable from -2V to +7V. loL & loH programmable from 0 to 16mA. Tester Impedance Zo =  $75 \Omega$ .

Vz is typically the midpoint of VoH and VoL.

$\text{lo}_L$  & 10H are adjusted to simulate a typical resistive load circuit. ATE tester includes jig capacitance.

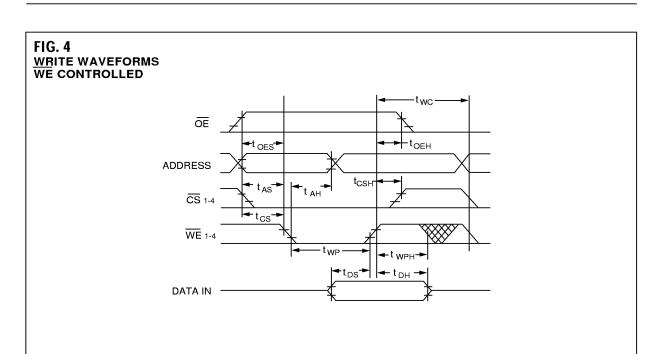

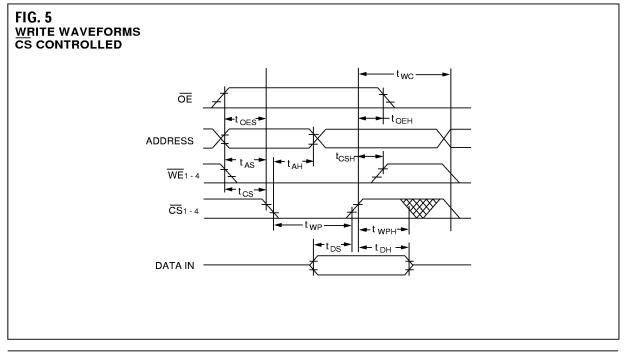

## WRITE

$\frac{A \text{ write cycle is } initiated}{WE \text{ or } \overline{CS} \text{ with } \overline{CS} \text{ or } \overline{WE} \text{ low. The address is latched on the falling edge of } \overline{CS} \text{ or } \overline{WE} \text{ whichever } \underline{occurs } \text{ last. The data is latched by the rising edge of } \overline{CS} \text{ or } \overline{WE}, \text{ whichever occurs } \text{first. A byte write operation will automatically continue to completion.}$

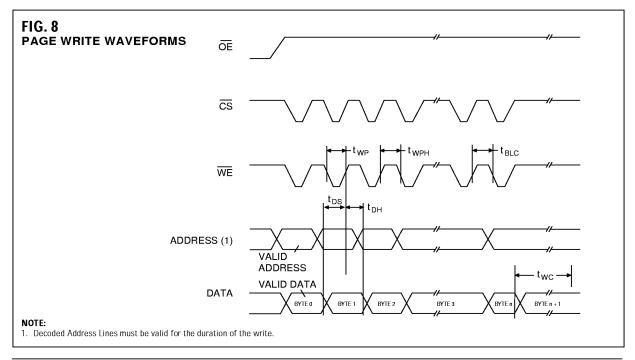

### WRITE CYCLE TIMING

Figures 4 and 5 show the write cycle timing relationships. A write cycle begins with address application, write enable and chip select. Chip select is accomplished by placing the  $\overline{\text{CS}}$  line low. Write enable consists of setting the  $\overline{\text{WE}}$  line low. The write cycle begins when the last of either  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  goes low.

The  $\overline{WE}$  line transition from high to low also initiates an internal 150  $\mu sec$  <u>del</u>ay timer to permit page mode operation. Each subsequent  $\overline{WE}$  transition from high to low that occurs before the completion of the 150  $\mu sec$  time out will restart the timer from zero. The operation of the timer is the same as a retriggerable one-shot.

### **AC WRITE CHARACTERISTICS**

$(Vcc = 5.0V, GND = 0V, TA = -55^{\circ}C to +125^{\circ}C)$

| WRITE CYCLE                  |        | -:  | 90  | -1  | 20  | -1  | 50  |      |

|------------------------------|--------|-----|-----|-----|-----|-----|-----|------|

| Write Cycle Parameter        | Symbol | Min | Max | Min | Max | Min | Max | Unit |

| Write Cycle Time, TYP = 6ms  | twc    |     | 10  |     | 10  |     | 10  | ms   |

| Address Set-up Time          | tas    | 0   |     | 30  |     | 30  |     | ns   |

| Write Pulse Width (WE or CS) | twp    | 100 |     | 150 |     | 150 |     | ns   |

| Chip Select Set-up Time      | tcs    | 0   |     | 0   |     | 0   |     | ns   |

| Address Hold Time            | tан    | 50  |     | 100 |     | 100 |     | ns   |

| Data Hold Time               | tрн    | 0   |     | 10  |     | 10  |     | ns   |

| Chip Select Hold Time        | tcsh   | 0   |     | 0   |     | 0   |     | ns   |

| Data Set-up Time             | tos    | 50  |     | 100 |     | 100 |     | ns   |

| Write Pulse Width High       | twрн   | 50  |     | 50  |     | 50  |     | ns   |

| Output Enable Set-up Time    | toes   | 10  |     | 10  |     | 10  |     | ns   |

| Output Enable Hold Time      | tоен   | 10  |     | 10  |     | 10  |     | ns   |

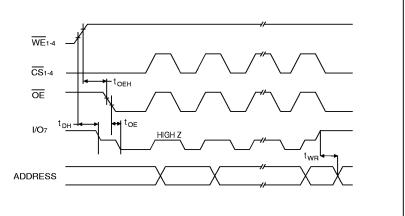

## **READ**

The WE32K32-XHX stores data at the memory location determined by the address pins. When  $\overline{\text{CS}}$  and  $\overline{\text{OE}}$  are low and  $\overline{\text{WE}}$  is high, this data is present on the outputs. When  $\overline{\text{CS}}$  and  $\overline{\text{OE}}$  are high, the outputs are in a high impedance state. This 2 line control prevents bus contention.

## AC READ CHARACTERISTICS (See Figure 6)

$(Vcc = 5.0V, GND = 0V, TA = -55^{\circ}C to +125^{\circ}C)$

| READ CYCLE                             | Symbol | -:  | 90  | -1: | 20  | -1  | 50  | Unit |

|----------------------------------------|--------|-----|-----|-----|-----|-----|-----|------|

| Parameter                              |        | Min | Max | Min | Max | Min | Max |      |

| Read Cycle Time                        | trc    | 90  |     | 120 |     | 150 |     | ns   |

| Address Access Time                    | tacc   |     | 90  |     | 120 |     | 150 | ns   |

| CS Access Time                         | tacs   |     | 90  |     | 120 |     | 150 | ns   |

| Output Hold from Add. Change, OE or CS | tон    | 0   |     | 0   |     | 0   |     | ns   |

| Output Enable to Output Valid          | toe    |     | 50  |     | 85  |     | 85  | ns   |

| Chip Select or OE to Output in High Z  | tor    |     | 50  |     | 70  |     | 70  | ns   |

## **DATA POLLING**

The WE32K32-XXX offers a data polling feature which allows a faster method of writing to the device. Figure 7 shows the timing diagram for this function. During a byte or page write cycle, an attempted read of the last byte written will result in the complement of the written data on D7 (for each chip.) Once the write cycle has been completed, true data is valid on all outputs and the next cycle may begin. Data polling may begin at any time during the write cycle.

### **DATA POLLING CHARACTERISTICS**

$(Vcc = 5.0V, GND = 0V, TA = -55^{\circ}C to +125^{\circ}C)$

| Parameter           | Symbol | Min | Max | Unit |

|---------------------|--------|-----|-----|------|

| Data Hold Time      | tон    | 10  |     | ns   |

| OE Hold Time        | toeh   | 10  |     | ns   |

| OE To Output Valid  | toe    |     | 100 | ns   |

| Write Recovery Time | twr    | 0   |     | ns   |

#### **PAGE WRITE OPERATION**

The WE32K32-XXX has a page write operation that allows one to 64 bytes of data to be written into the device and consecutively loads during the internal programming period. Successive bytes may be loaded in the same manner after the first data byte has been loaded. An internal timer begins a time out operation at each write cycle. If another write cycle is completed within 150µs or less, a new time out period begins. Each write cycle restarts the delay period. The write cycles can be continued as long as the interval is less than the time out period.

The usual procedure is to increment the least significant address lines from A0 through A5 at each write cycle. In this manner a page of up to 64 bytes can be loaded in to the EEPROM in a burst mode before beginning the relatively long interval programming cycle.

After the  $150\mu s$  time out is completed, the EEPROM begins an internal write cycle. During this cycle the entire page of bytes will be written at the same time. The internal programming cycle is the same regardless of the number of bytes accessed.

#### **PAGE WRITE CHARACTERISTICS**

(Vcc = 5.0V, GND = 0V, TA = -55°C to +125°C)

| PAGE MODE WRITE CHARACTERISTICS |        |     |     |     |     |     |     |      |

|---------------------------------|--------|-----|-----|-----|-----|-----|-----|------|

| Parameter                       | Symbol | -9  | 90  | -1  | 20  | -19 | 50  | Unit |

|                                 |        | Min | Max | Min | Max | Min | Max |      |

| Write Cycle Time, TYP = 6ms     | twc    |     | 10  |     | 10  |     | 10  | ms   |

| Data Set-up Time                | tos    | 50  |     | 100 |     | 100 |     | ns   |

| Data Hold Time                  | tон    | 0   |     | 10  |     | 10  |     | ns   |

| Write Pulse Width               | twp    | 100 |     | 150 |     | 150 |     | ns   |

| Byte Load Cycle Time            | tвьс   |     | 150 |     | 150 |     | 150 | μs   |

| Write Pulse Width High          | twpн   | 50  |     | 50  |     | 50  |     | ns   |

White Microelectronics • Phoenix, AZ • (602) 437-1520

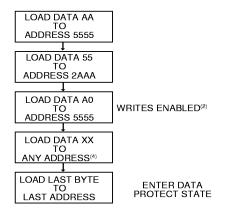

### FIG. 9 **SOFTWARE BLOCK DATA** PROTECTION ENABLE ALGORITHM(1)

#### NOTES:

- 1. Data Format: D7 D0 (Hex):

Address Format: A14 A0 (Hex).

2. Write Protect state will be activated at end of write even if no other data is loaded.

- 3. Write Protect state will be deactivated at end of write period even if no other data is loaded.

- 4. 1 to 64 bytes of data may be loaded.

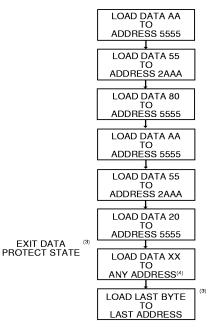

### FIG. 10 SOFTWARE BLOCK DATA PROTECTION DISABLE ALGORITHM<sup>(1)</sup>

#### NOTES:

- Data Format: D7 D0 (Hex); Address Format: A14 - A0 (Hex).

- Write Protect state will be activated at end of write even if no other data is loaded.

- Write Protect state will be deactivated at end of write period even if no other data is loaded.

- 4. 1 to 64 bytes of data may be loaded.

### **SOFTWARE DATA PROTECTION**

A software write protection feature may be enabled or disabled by the user. When shipped by White Microelectronics, the WE32K32-XXX has the feature disabled. Write access to the device is unrestricted.

To enable software write protection, the user writes three access code bytes to three special internal locations. Once write protection has been enabled, each write to the EEPROM must use the same three byte write sequence to permit writing. After setting software data protection, any attempt to write to the device without the three-byte command sequence will start the internal write timers. No data will be written to the device, however, for the duration of twc. The write protection feature can be disabled by a six byte write sequence of specific data to specific locations. Power transitions will not reset the software write protection.

Each 32KByte block of the EEPROM has independent write protection. One or more blocks may be enabled and the rest disabled in any combination. The software write protection guards against inadvertent writes during power transitions, or unauthorized modification using a PROM programmer.

### HARDWARE DATA PROTECTION

These features protect against inadvertent writes to the WE32K32-XXX. These are included to improve reliability during normal operation:

#### a) Vcc power on delay

As Vcc climbs past 3.8V typical the device will wait 5msec typical before allowing write cycles.

#### b) Vcc sense

While below 3.8V typical write cycles are inhibited.

#### c) Write inhibiting

Holding  $\overline{\text{OE}}$  low and either  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  high inhibits write cycles.

### d) Noise filter

Pulses of <8ns (typ) on  $\overline{\text{WE}}$  or  $\overline{\text{CS}}$  will not initiate a write cycle.

| DEVICETYPE             | SPEED | PACKAGE             | SMD NO           |

|------------------------|-------|---------------------|------------------|

| 32K x 32 EEPROM Module | 150ns | 66 pin HIP (H1)     | 5962-94614 01HXX |

| 32K x 32 EEPROM Module | 120ns | 66 pin HIP (H1)     | 5962-94614 02HXX |

| 32K x 32 EEPROM Module | 90ns  | 66 pin HIP (H1)     | 5962-94614 03HXX |

| 32K x 32 EEPROM Module | 150ns | 68 lead CQFP/J (G2) | 5962-94614 01HMX |

| 32K x 32 EEPROM Module | 120ns | 68 lead CQFP/J (G2) | 5962-94614 02HMX |

| 32K x 32 EEPROM Module | 90ns  | 68 lead CQFP/J (G2) | 5962-94614 03HMX |