## S3C94A5/F94A5

# 8-BIT CMOS MICROCONTROLLER USER'S MANUAL

**Revision 1.1**

## **Important Notice**

The information in this publication has been carefully checked and is believed to be entirely accurate at the time of publication. Samsung assumes no responsibility, however, for possible errors or omissions, or for any consequences resulting from the use of the information contained herein.

Samsung reserves the right to make changes in its products or product specifications with the intent to improve function or design at any time and without notice and is not required to update this documentation to reflect such changes.

This publication does not convey to a purchaser of semiconductor devices described herein any license under the patent rights of Samsung or others.

Samsung makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Samsung assume any liability arising out of the application or use of any product or circuit and specifically disclaims any and all liability, including without limitation any consequential or incidental damages.

S3C94A5/F94A5 8-Bit CMOS Microcontroller User's Manual, Revision 1.1 Publication Number: 21.1-S3-C94A5/F94A5-072005

© 2005 Samsung Electronics

"Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts.

Samsung products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, for other applications intended to support or sustain life, or for any other application in which the failure of the Samsung product could create a situation where personal injury or death may occur.

Should the Buyer purchase or use a Samsung product for any such unintended or unauthorized application, the Buyer shall indemnify and hold Samsung and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, expenses, and reasonable attorney fees arising out of, either directly or indirectly, any claim of personal injury or death that may be associated with such unintended or unauthorized use, even if such claim alleges that Samsung was negligent regarding the design or manufacture of said product.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior written consent of Samsung Electronics.

Samsung Electronics' microcontroller business has been awarded full ISO-14001 certification (BVQ1 Certificate No. 9330). All semiconductor products are designed and manufactured in accordance with the highest quality standards and objectives.

Samsung Electronics Co., Ltd. San #24 Nongseo-Ri, Giheung- Eup Yongin-City, Gyeonggi-Do, Korea C.P.O. Box #37, Suwon 449-900

TEL: (82)-(031)-209-1934 FAX: (82) (331) 209-1889

Home-Page URL: Http://www.samsungsemi.com/

Printed in the Republic of Korea

### **NOTIFICATION OF REVISIONS**

ORIGINATOR: Samsung Electronics, LSI Development Group, Ki-Heung, South Korea

**PRODUCT NAME:** S3C94A5/F94A5 8-bit CMOS Microcontroller

**DOCUMENT NAME:** S3C94A5/F94A5 User's Manual, Revision 1.1

**DOCUMENT NUMBER:** 21.1-S3-C94A5/F94A5-072005

**EFFECTIVE DATE:** July, 2005

**SUMMARY:** As a result of additional product testing and evaluation, some specifications

published in the S3C94A5/F94A5 User's Manual, Revision 1, have been changed. These changes for S3C94A5/F94A5 microcontroller, which are described in detail in the *Revision Descriptions* section below, are related to the

followings:

Chapter 17. Electrical Data

**DIRECTIONS:** Please note the changes in your copy (copies) of the S3C94A5/F94A5 User's

Manual, Revision 1. Or, simply attach the Revision Descriptions of the next

page to S3C94A5/F94A5 User's Manual, Revision 1.

## **REVISION HISTORY**

| Revision | Date           | Remark                                      |  |

|----------|----------------|---------------------------------------------|--|

| 0        | July, 2004     | Preliminary spec for internal release only. |  |

| 1        | February, 2005 | First edition. Reviewed by Finechips.       |  |

| 1.1      | July, 2005     | Second edition. Reviewed by Finechips.      |  |

## **REVISION DESCRIPTIONS**

#### 1. ELECTRICAL DATA

Table 17-1. Absolute Maximum Ratings

$(T_A = 25^{\circ}C)$

| Parameter             | Symbol           | Conditions          | Rat         | ing                      | Unit |

|-----------------------|------------------|---------------------|-------------|--------------------------|------|

| Supply voltage        | V <sub>DD</sub>  | -                   | - 0.3 t     | - 0.3 to + 6.5           |      |

| Input voltage         | V <sub>I</sub>   | Ports 1–5           | - 0.3 to    | V <sub>DD</sub> + 0.3    | V    |

| Output voltage        | V <sub>O</sub>   | -                   | - 0.3 to    | $-0.3$ to $V_{DD} + 0.3$ |      |

| Output current High   | I <sub>OH</sub>  | One I/O pin active  | -           | 15                       |      |

|                       |                  | All I/O pins active | 42-SDIP     | <b>- 60</b>              | mA   |

|                       |                  |                     | 44-QFP      | <b>- 90</b>              | 1    |

| Output current Low    | I <sub>OL</sub>  | One I/O pin active  | + :         | 30                       |      |

|                       |                  | All I/O pin active  | 42-SDIP     | + 100                    | mA   |

|                       |                  |                     | 44-QFP      | + 150                    |      |

| Operating temperature | T <sub>A</sub>   | -                   | – 25 to     | o + 85                   | °C   |

| Storage temperature   | T <sub>STG</sub> | _                   | -65 to +150 |                          | °C   |

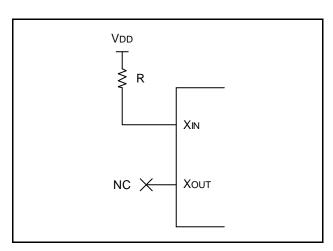

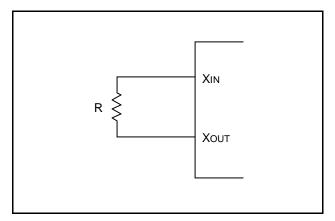

#### Table 17-9. External RC Oscillation (Mode 2) Characteristics

$(T_A = -25 \,^{\circ}C \text{ to } + 85 \,^{\circ}C, \, V_{DD} = 2.7 \, \text{V} \text{ to } 5.5 \, \text{V})$

| Parameter                                    | Symbol             | Conditions                                                           | Min        | Тур | Max | Unit |

|----------------------------------------------|--------------------|----------------------------------------------------------------------|------------|-----|-----|------|

| RC oscillator frequency range <sup>(1)</sup> | f <sub>ERC</sub>   | T <sub>A</sub> = 25 °C                                               | 4          | -   | 8   | MHz  |

| Accuracy of RC oscillation (2)               | ACC <sub>ERC</sub> | $V_{DD} = 3.3 \text{ V}, T_A = 25 ^{\circ}\text{C}$                  | <b>-</b> 7 | -   | +7  | %    |

|                                              |                    | $V_{DD} = 3.3 \text{ V},$ $T_{A} = -25 \text{ °C to } 85 \text{ °C}$ | <b>–15</b> | -   | +15 |      |

| RC oscillator setup time (3)                 | t <sub>SUERC</sub> | T <sub>A</sub> = 25 °C                                               | _          | _   | 10  | ms   |

#### NOTES:

- 1. The frequency is adjusted by external resistor.

- 2. The min/max frequencies are within the range of RC OSC frequency (4 MHz to 8 MHz).

- 3. Data based on characterization results, not tested in production.

- 4. The external resistor is connected between  $V_{DD}$  and  $X_{IN}$  pin  $(X_{OUT}$  pin should be open).

#### **Preface**

The S3C94A5/F94A5 Microcontroller User's Manual is designed for application designers and programmers who are using the S3C94A5/F94A5 microcontroller for application development. It is organized in two parts:

Part I Programming Model Part II Hardware Descriptions

Part I contains software-related information to familiarize you with the microcontroller's architecture, programming model, instruction set, and interrupt structure. It has six chapters:

| Chapter 1 | Product Overview | Chapter 4 | Control Registers   |

|-----------|------------------|-----------|---------------------|

| Chapter 2 | Address Spaces   | Chapter 5 | Interrupt Structure |

Chapter 3 Addressing Modes Chapter 6 SAM88RCRI Instruction Set

Chapter 1, "Product Overview," is a high-level introduction to the S3C94A5/F94A5 with a general product description, and detailed information about individual pin characteristics and pin circuit types.

Chapter 2, "Address Spaces," explains the S3C94A5/F94A5 program and data memory, internal register file, and mapped control registers, and explains how to address them. Chapter 2 also describes working register addressing, as well as system and user-defined stack operations.

Chapter 3, "Addressing Modes," contains detailed descriptions of the six addressing modes that are supported by the CPU.

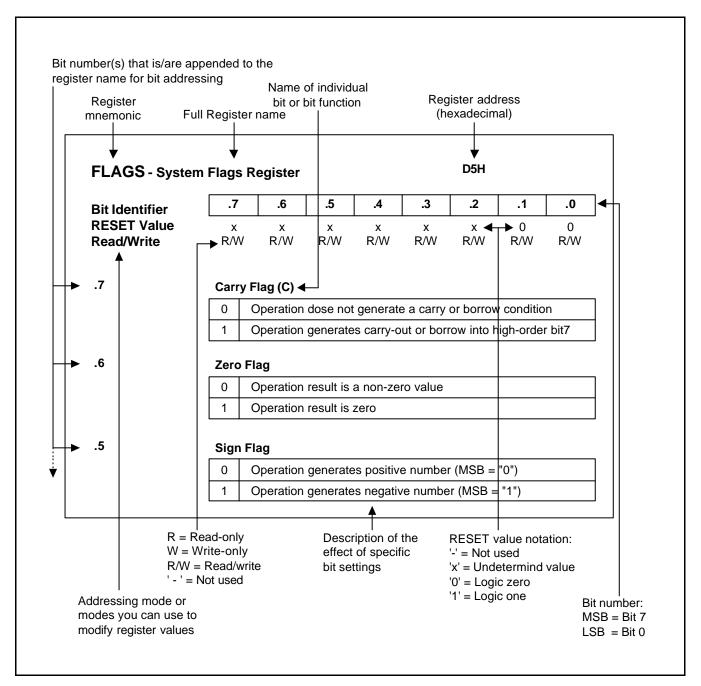

Chapter 4, "Control Registers," contains overview tables for all mapped system and peripheral control register values, as well as detailed one-page descriptions in standard format. You can use these easy-to-read, alphabetically organized, register descriptions as a quick-reference source when writing programs.

Chapter 5, "Interrupt Structure," describes the S3C94A5/F94A5 interrupt structure in detail and further prepares you for additional information presented in the individual hardware module descriptions in part II.

Chapter 6, "SAM88RCRI Instruction Set," describes the features and conventions of the instruction set used for all S3C9-series microcontrollers. Several summary tables are presented for orientation and reference. Detailed descriptions of each instruction are presented in a standard format. Each instruction description includes one or more practical examples of how to use the instruction when writing an application program.

A basic familiarity with the information in part I will help you to understand the hardware module descriptions in Part II. If you are not yet familiar with the SAM88RCRI product family and are reading this manual for the first time, we recommend that you first read chapters 1–3 carefully. Then, briefly look over the detailed information in chapters 4, 5, and 6. Later, you can reference the information in part I as necessary.

Part II contains detailed information about the peripheral components of the S3C94A5/F94A5 microcontrollers. Also included in part II are electrical, mechanical, MTP, and development tools data. It has 14 chapters:

| Chapter 7  | Clock Circuit        | Chapter 14 | Watch Timer                        |

|------------|----------------------|------------|------------------------------------|

| Chapter 8  | RESET and Power-Down | Chapter 15 | 10-Bit Analog-To-Digital Converter |

| Chapter 9  | I/O Ports            | Chapter 16 | Serial I/O Interface               |

| Chapter 10 | Basic Timer          | Chapter 17 | Electrical Data                    |

| Chapter 11 | 16-bit Timer 0       | Chapter 18 | Mechanical Data                    |

| Chapter 12 | 16-bit Timer 1       | Chapter 19 | S3F94A5 Flash MCU                  |

| Chapter 13 | 8-bit Timer 2        | Chapter 20 | Development Tools                  |

Two order forms are included at the back of this manual to facilitate customer order for S3C94A5/F94A5 microcontroller: the Mask ROM Order Form, and the Mask Option Selection Form. You can photocopy these forms, fill them out, and then forward them to your local Samsung Sales Representative.

## **Table of Contents**

## Part I — Programming Model

| Chapter 1          | Product Overview          |      |

|--------------------|---------------------------|------|

| S3C94A5/F94A5      | duct Family               | 1-1  |

|                    |                           |      |

|                    |                           |      |

| Pin Descriptions.  |                           | 1-6  |

| Pin Circuit Diagra | ams                       | 1-8  |

| Chapter 2          | Address Spaces            |      |

|                    |                           |      |

|                    | (ROM)                     |      |

|                    |                           |      |

| •                  | ture                      |      |

|                    | g Register Area (C0H-CFH) |      |

| Chapter 3          | Addressing Modes          |      |

| Overview           |                           | 3-1  |

|                    | ing Mode (R)              |      |

|                    | Addressing Mode (IR)      |      |

|                    | ng Mode (X)               |      |

|                    | lode (DA)                 |      |

|                    | Mode (RA)                 |      |

| irrimediate iviode | (IM)                      | 3-12 |

| Chapter 4                                    | Control Registers                                                                      |                   |

|----------------------------------------------|----------------------------------------------------------------------------------------|-------------------|

| Overview                                     |                                                                                        | 4-1               |

| Chapter 5                                    | Interrupt Structure                                                                    |                   |

| Overview                                     |                                                                                        | 5-1               |

| Interrupt Pro<br>Enable/Disa<br>Interrupt Pe | ocessing Control Pointsable Interrupt Instructions (EI, DI)ending Function Typesiority | 5-1<br>5-1<br>5-2 |

| Interrupt Se                                 | ource Service Sequence<br>rvice Routines                                               | 5-3               |

|                                              | 94A5 Interrupt Structure                                                               |                   |

| Chapter 6                                    | SAM88RCRI Instruction Set                                                              |                   |

| Overview                                     |                                                                                        | 6-1               |

| Register Ad                                  | ddressing                                                                              | 6-1               |

|                                              | Modes                                                                                  |                   |

|                                              | ster (FLAGS)                                                                           |                   |

|                                              | ptions                                                                                 |                   |

|                                              | Set Notation                                                                           |                   |

|                                              | odes<br>Descriptions                                                                   |                   |

| ii iStruction t                              | Descriptions                                                                           | 0-10              |

## Part II — Hardware Descriptions

| Chapter 7                                                                    | Clock Circuit                                                                                                     |                          |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------|

| System Clock I<br>CPU Clock I<br>Main Oscilla<br>Clock Status<br>System Cloc | ck Circuit  Notation  Itor Circuits  S During Power-Down Modes  Ck Control Register (CLKCON)  I Register (STPCON) | 7-1<br>7-1<br>7-2<br>7-3 |

| Chapter 8                                                                    | RESET and Power-Down                                                                                              |                          |

| Overview Power-Down Mode Stop Mode Idle Mode                                 | eset Values                                                                                                       |                          |

| Chapter 9                                                                    | I/O Ports                                                                                                         |                          |

| Port Data Re Port 1 Port 2 Port 3 Port 4                                     | egisters                                                                                                          | 9-2<br>9-3<br>9-7<br>9-9 |

| Chapter 10                                                                   | Basic Timer                                                                                                       |                          |

|                                                                              | Control Devictor (DTCON)                                                                                          |                          |

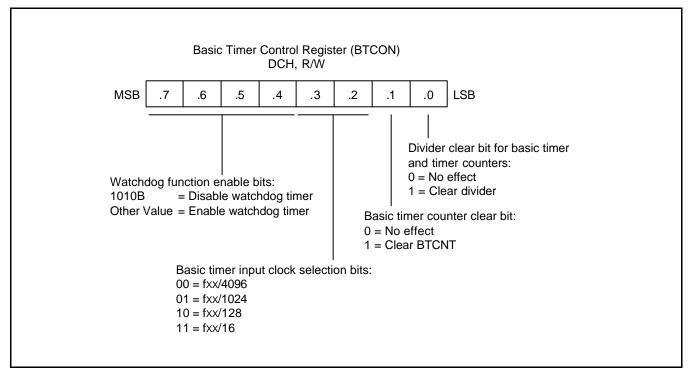

| Basic Timer                                                                  | Control Register (BTCON)                                                                                          | 10-2                     |

| Chapter 11    | 16-bit Timer 0                   |      |

|---------------|----------------------------------|------|

| Overview      |                                  | 11-1 |

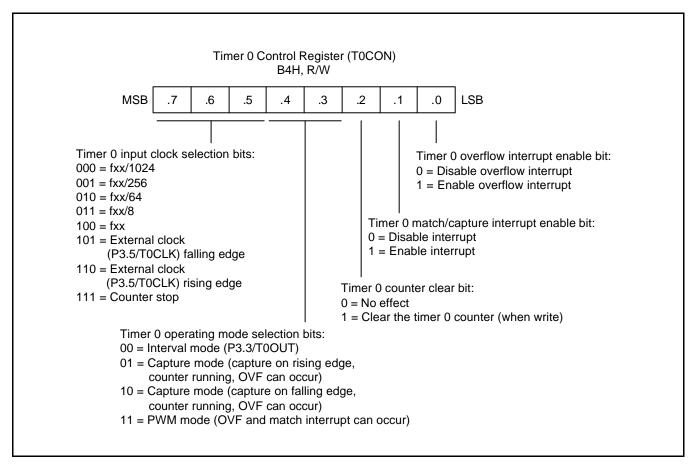

|               | er 0 Control Register (T0CON)    |      |

|               | ction Description                |      |

| Chapter 12    | 16-bit Timer 1                   |      |

|               |                                  |      |

|               | er 1 Control Register (T1CON)    |      |

| Timer 1 Fund  | ction Description                | 12-4 |

| Chapter 13    | 8-bit Timer 2                    |      |

| Overview      |                                  | 13-1 |

| Timer/Counte  | er 2 Control Register (T2CON)    | 13-1 |

| Timer 2 Fund  | ction Description                | 13-4 |

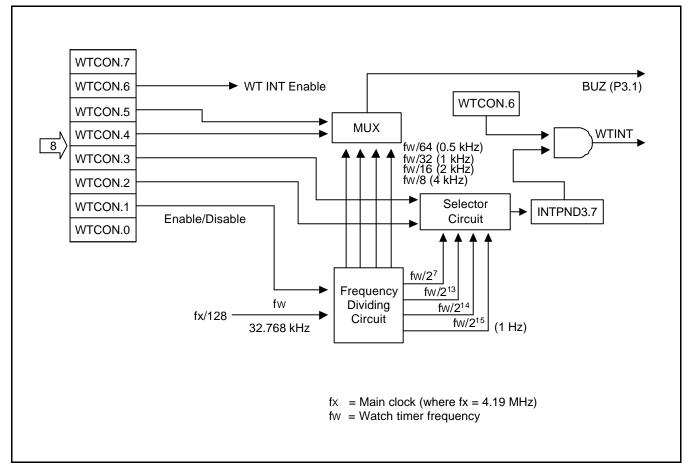

| Chapter 14    | Watch Timer                      |      |

| Overview      |                                  | 14-1 |

|               | Control Register (WTCON)         |      |

|               | · Circuit Diagram                |      |

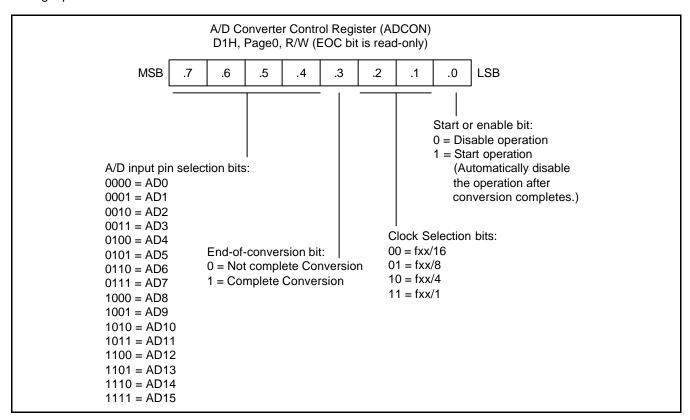

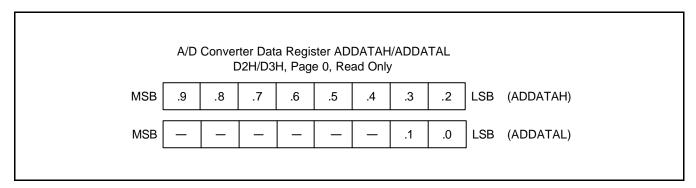

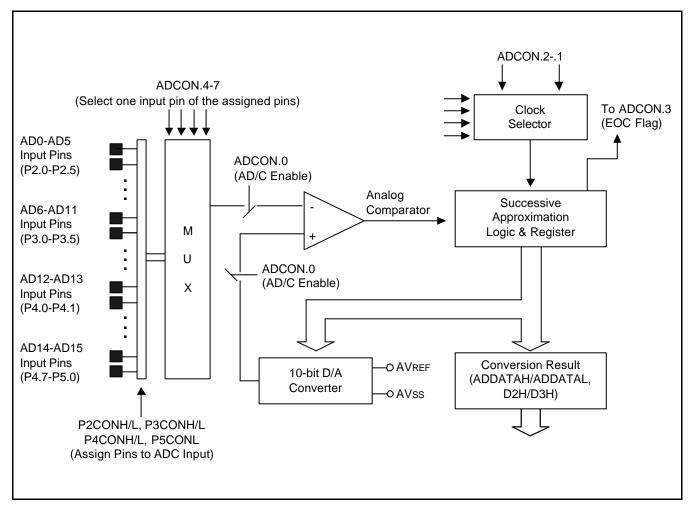

| Chapter 15    | 10-Bit Analog-To-Digital Convert | er   |

| Overview      |                                  | 15-1 |

| •             | on                               |      |

|               | iming                            |      |

|               | er Control Register (ADCON)      |      |

|               | rence Voltage Levels             |      |

| Block Diagram |                                  | 15-4 |

| Chapter 16        | Serial I/O Interface  |      |

|-------------------|-----------------------|------|

| Overview          |                       | 16-  |

|                   | g Procedure           |      |

| SIO Control I     | Registers (SIOCON)    | 16-2 |

| SIO Pre-Scal      | ller Register (SIOPS) | 16-3 |

| SIO Block Diagran | m                     | 16-3 |

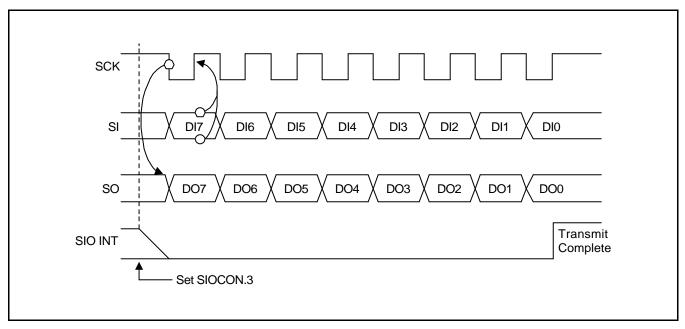

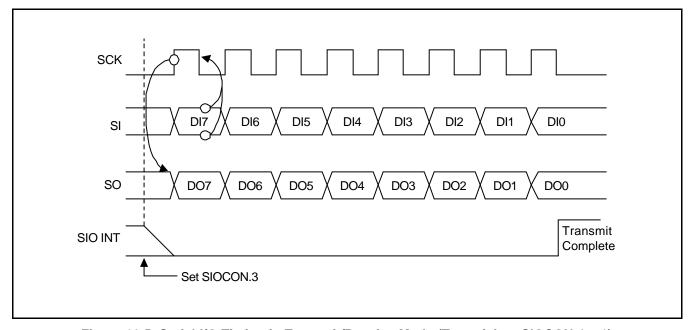

| Serial I/O Tin    | ning Diagram (SIO)    | 16-4 |

| Chapter 17        | Electrical Data       |      |

| Overview          |                       | 17-  |

| <b>.</b>          |                       |      |

| Chapter 18        | Mechanical Data       |      |

| Overview          |                       | 10 / |

| Overview          |                       | 10-  |

| Chapter 19        | S3F94A5 Flash MCU     |      |

| Ovontion          |                       | 10-7 |

|                   | ode Characteristics   |      |

|                   |                       |      |

| Chapter 20        | Development Tools     |      |

| Overview          |                       | 20-  |

| SHINE             |                       | 20-^ |

| SAMA Asser        | mbler                 | 20-^ |

|                   |                       |      |

|                   |                       |      |

| •                 | ds                    |      |

|                   | get Board             |      |

|                   | election (SAM8)       |      |

|                   |                       |      |

| Stop I ED         |                       | 20.1 |

## **List of Figures**

| Figure<br>Number | Title                                                          | Page<br>Number |

|------------------|----------------------------------------------------------------|----------------|

| 1-1              | Block Diagram                                                  | 1-3            |

| 1-2              | S3C94A5/F94A5 Pin Assignments (44-QFP-1010B)                   |                |

| 1-3              | S3C94A5/F94A5 Pin Assignments (42-SDIP-600)                    |                |

| 1-4              | Pin Circuit Type B (nRESET)                                    |                |

| 1-5              | Pin Circuit Type E                                             |                |

| 1-6              | Pin Circuit Type E-2 (P5.1–P5.6)                               |                |

| 1-7              | Pin Circuit Type E-4 (P1, P4.2–P4.6)                           |                |

| 1-8              | Pin Circuit Type F-16 (P2, P5.0)                               |                |

| 1-9              | Pin Circuit Type F-16A (P3, P4.0, P4.1, P4.7)                  |                |

| 2-1              | S3C94A5/F94A5 Program Memory Address Space                     | 2-2            |

| 2-2              | Smart Option                                                   | 2-4            |

| 2-3              | Internal Register File Organization                            | 2-5            |

| 2-4              | 16-Bit Register Pairs                                          | 2-6            |

| 2-5              | Stack Operations                                               | 2-7            |

| 3-1              | Register Addressing                                            | 3-2            |

| 3-2              | Working Register Addressing                                    | 3-2            |

| 3-3              | Indirect Register Addressing to Register File                  | 3-3            |

| 3-4              | Indirect Register Addressing to Program Memory                 | 3-4            |

| 3-5              | Indirect Working Register Addressing to Register File          | 3-5            |

| 3-6              | Indirect Working Register Addressing to Program or Data Memory | 3-6            |

| 3-7              | Indexed Addressing to Register File                            | 3-7            |

| 3-8              | Indexed Addressing to Program or Data Memory with Short Offset | 3-8            |

| 3-9              | Indexed Addressing to Program or Data Memory with Long Offset  | 3-9            |

| 3-10             | Direct Addressing for Load Instructions                        | 3-10           |

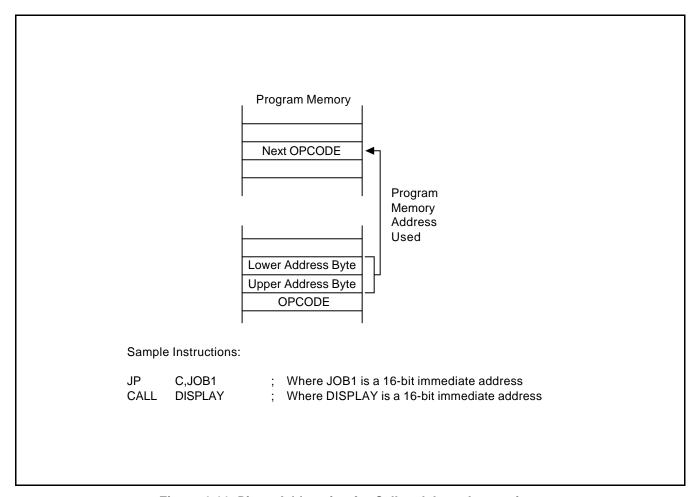

| 3-11             | Direct Addressing for Call and Jump Instructions               | 3-11           |

| 3-12             | Relative Addressing                                            |                |

| 3-13             | Immediate Addressing                                           | 3-12           |

## List of Figures (Continued)

| Figure<br>Number | Title                                                         | Page<br>Number |

|------------------|---------------------------------------------------------------|----------------|

| 4-1              | Register Description Format                                   | 4-4            |

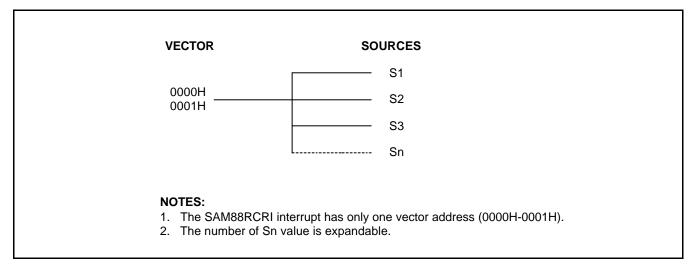

| 5-1              | S3C9-Series Interrupt Type                                    | 5-1            |

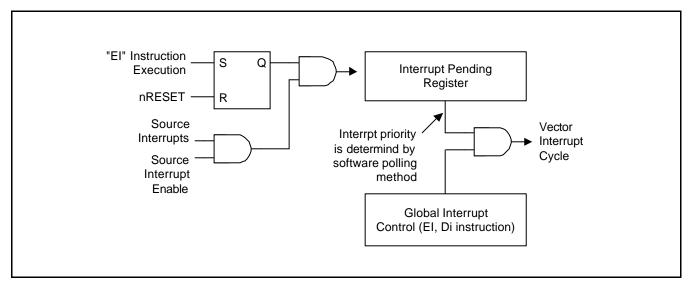

| 5-2              | Interrupt Function Diagram                                    | 5-2            |

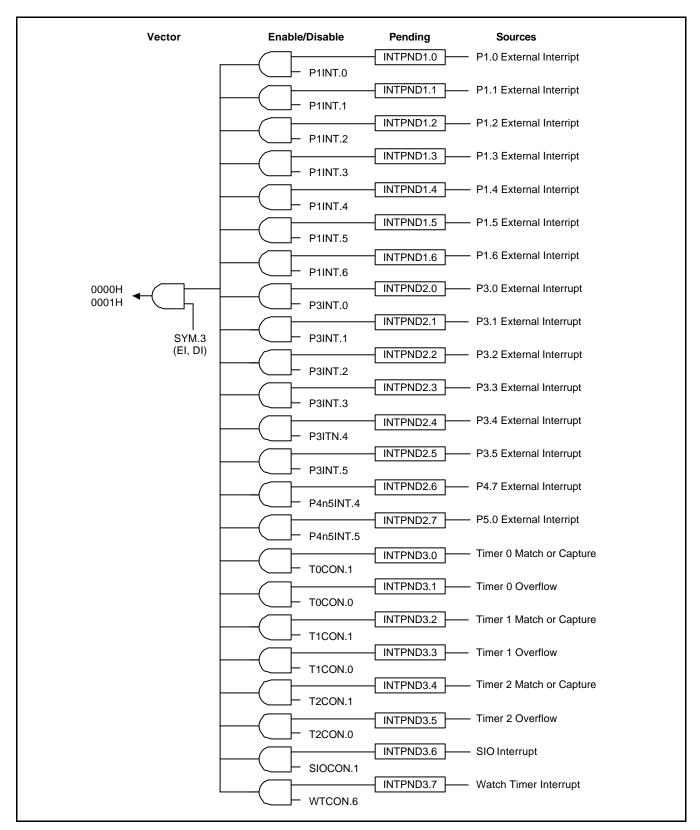

| 5-3              | S3C94A5/F94A5 Interrupt Structure                             | 5-5            |

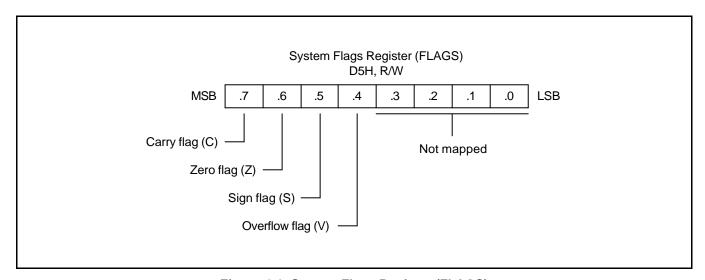

| 6-1              | System Flags Register (FLAGS)                                 | 6-4            |

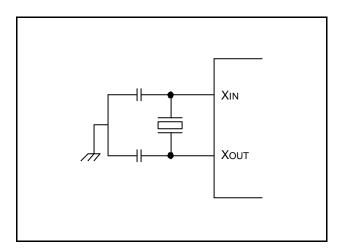

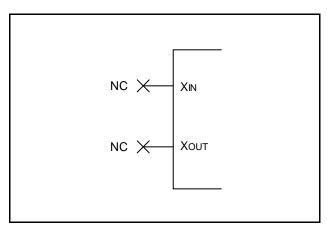

| 7-1              | Crystal/Ceramic Oscillator(fx)                                | 7-2            |

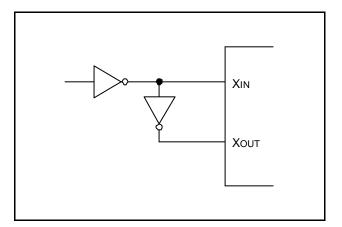

| 7-2              | External Oscillator(fx)                                       | 7-2            |

| 7-3              | RC Oscillator(fx)                                             | 7-2            |

| 7-4              | External RC Oscillator(fx)                                    | 7-2            |

| 7-5              | Internal RC Oscillator(fx)                                    | 7-2            |

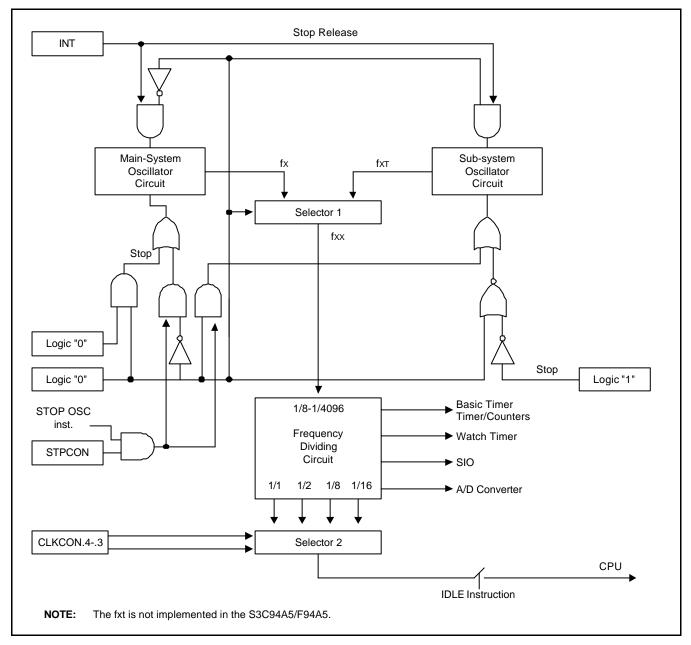

| 7-6              | System Clock Circuit Diagram                                  | 7-3            |

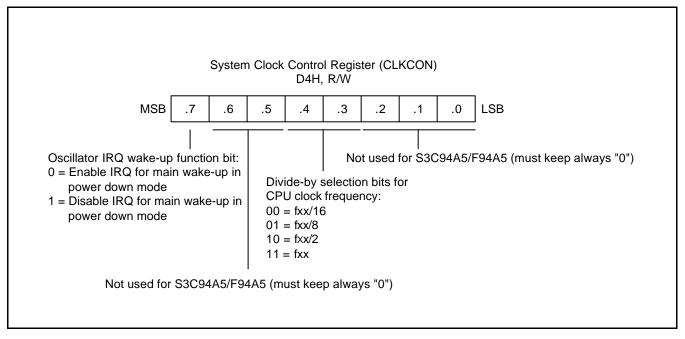

| 7-7              | System Clock Control Register (CLKCON)                        |                |

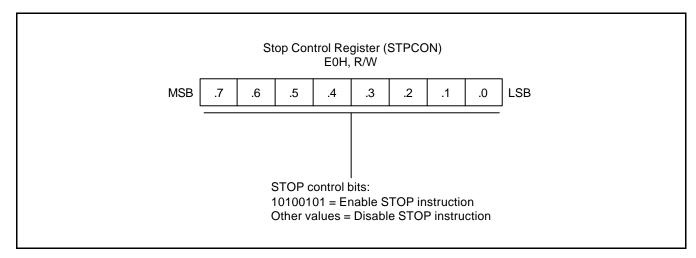

| 7-8              | STOP Control Register (STPCON)                                | 7-5            |

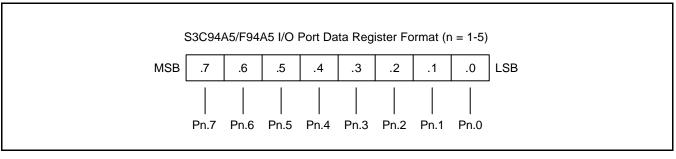

| 9-1              | S3C94A5/F94A5 I/O Port Data Register Format                   |                |

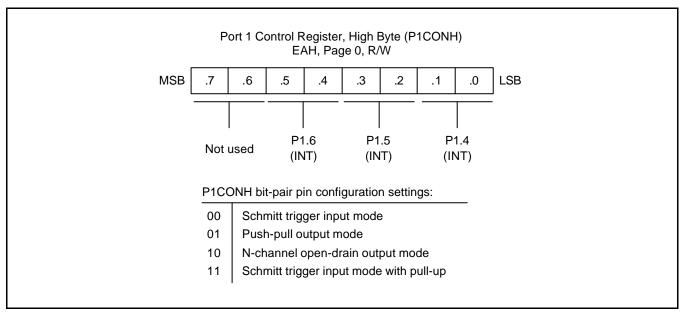

| 9-2              | Port 1 Control Register, High Byte (P1CONH)                   |                |

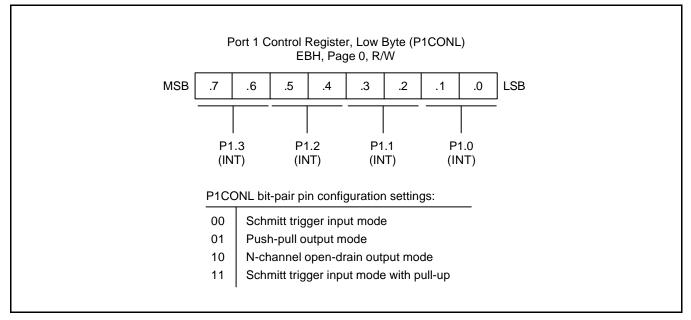

| 9-3              | Port 1 Control Register, Low Byte (P1CONL)                    | 9-4            |

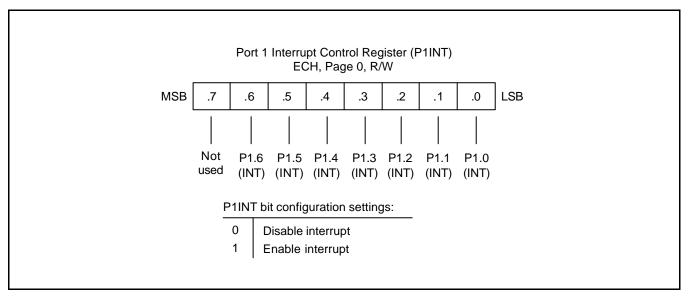

| 9-4              | Port 1 Interrupt Control Register (P1INT)                     | 9-5            |

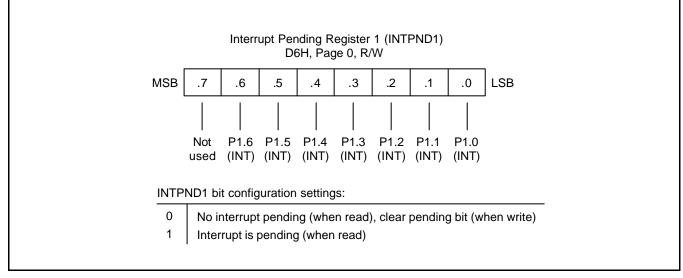

| 9-5              | Interrupt Pending Register 1 (INTPND1)                        | 9-5            |

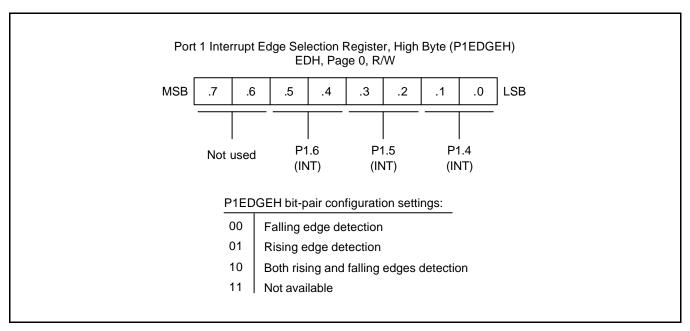

| 9-6              | Port 1 Interrupt Edge Selection Register, High Byte (P1EDGEH) | 9-6            |

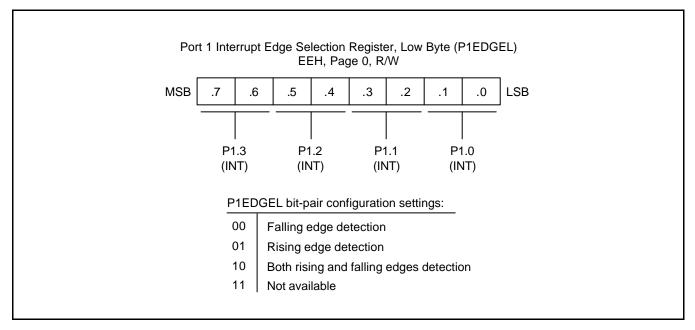

| 9-7              | Port 1 Interrupt Edge Selection Register, Low Byte (P1EDGEL)  | 9-6            |

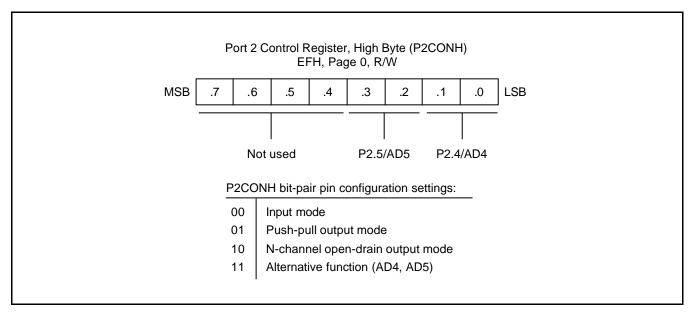

| 9-8              | Port 2 Control Register, High Byte (P2CONH)                   | 9-7            |

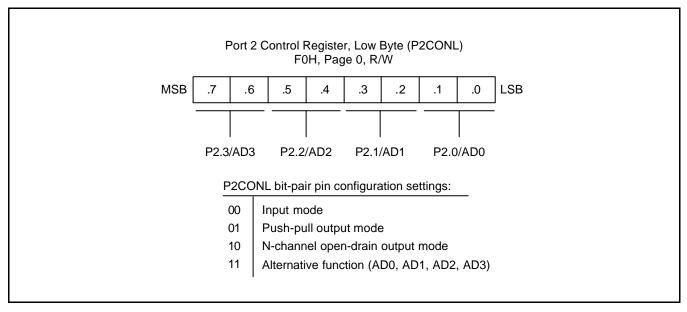

| 9-9              | Port 2 Control Register, Low Byte (P2CONL)                    | 9-8            |

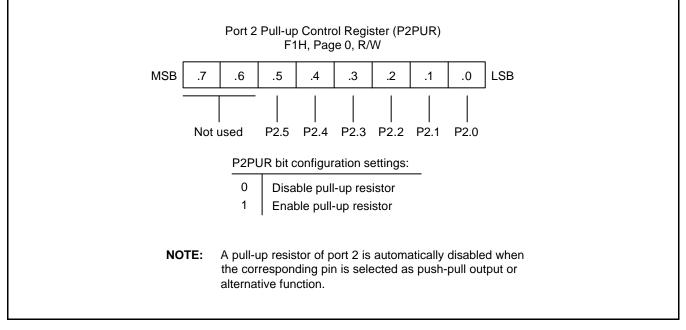

| 9-10             | Port 2 Pull-up Control Register (P2PUR)                       | 9-8            |

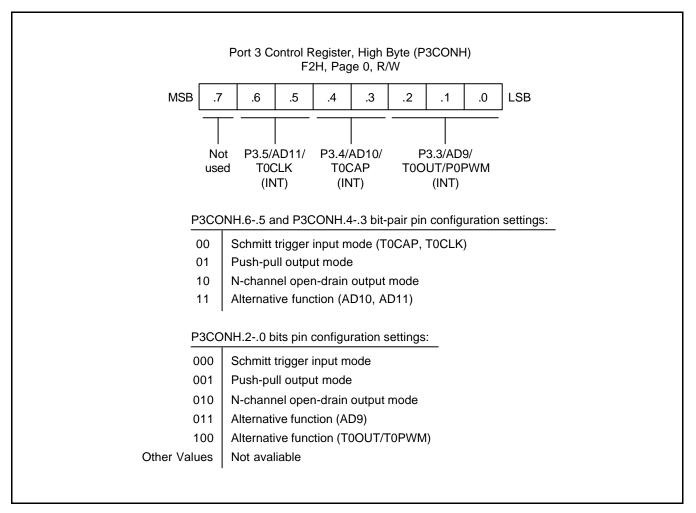

| 9-11             | Port 3 Control Register, High Byte (P3CONH)                   | 9-10           |

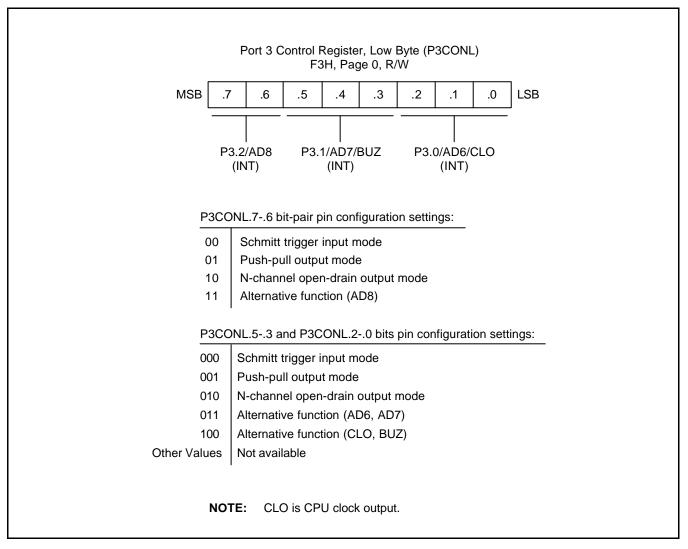

| 9-12             | Port 3 Control Register, Low Byte (P3CONL)                    | 9-11           |

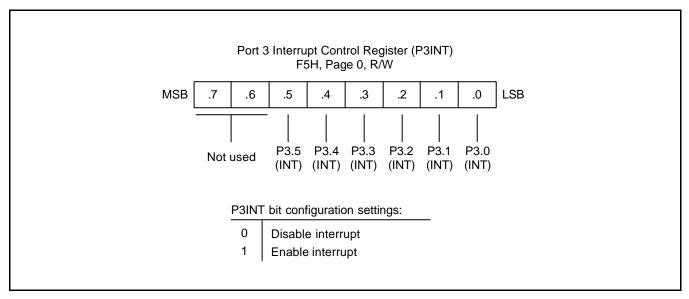

| 9-13             | Port 3 Interrupt Control Register (P3INT)                     | 9-12           |

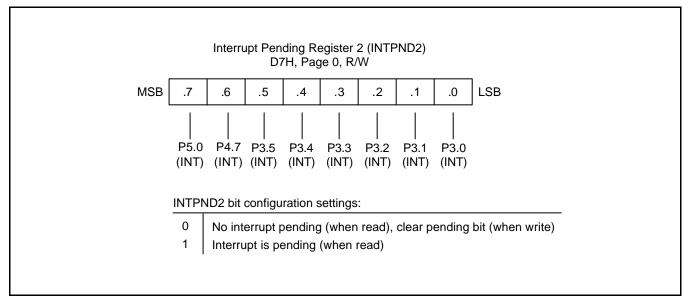

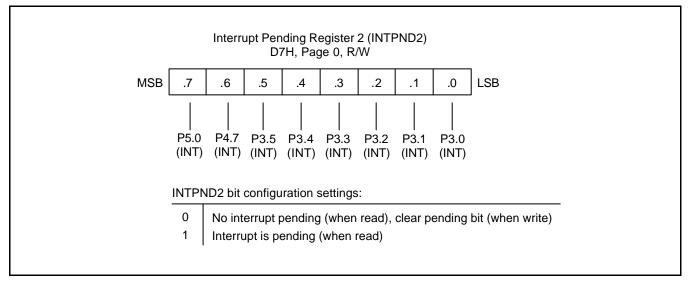

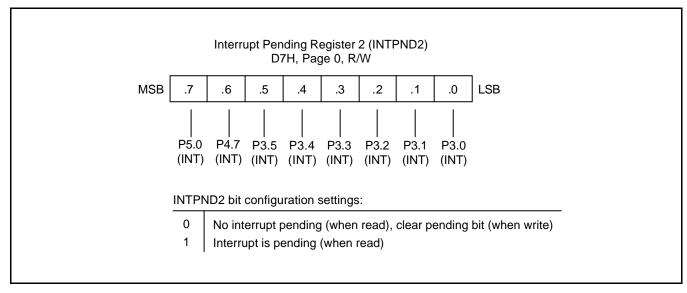

| 9-14             | Interrupt Pending Register 2 (INTPND2)                        | 9-12           |

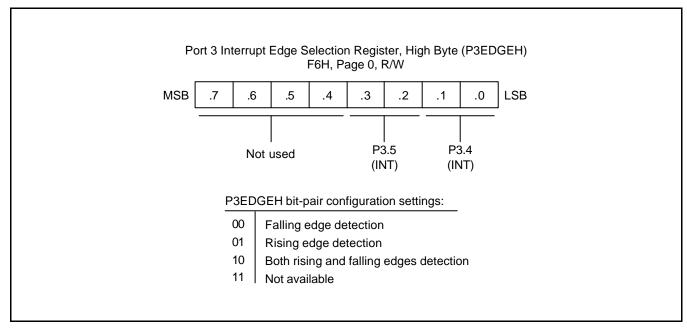

| 9-15             | Port 3 Interrupt Edge Selection Register, High Byte (P3EDGEH) | 9-13           |

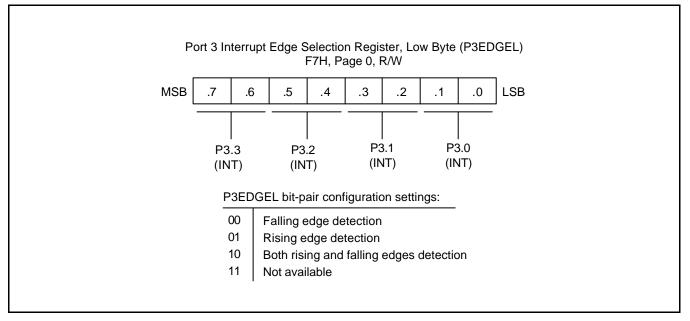

| 9-16             | Port 3 Interrupt Edge Selection Register, Low Byte (P3EDGEL)  | 9-13           |

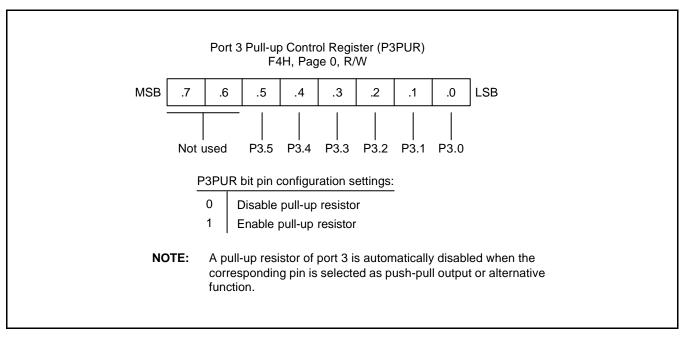

| 9-17             | Port 3 Pull-up Control Register (P3PUR)                       | 9-14           |

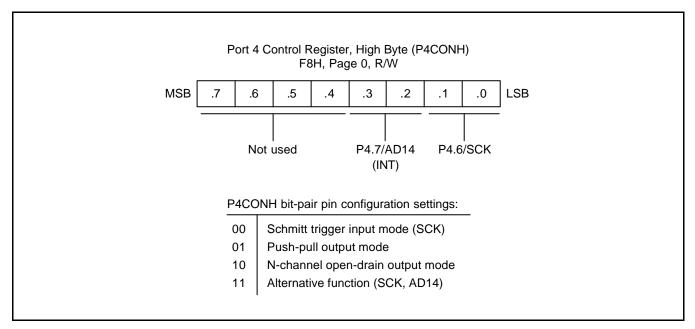

| 9-18             | Port 4 Control Register, High Byte (P4CONH)                   | 9-16           |

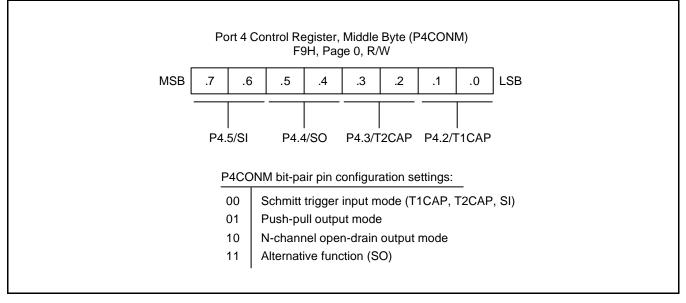

| 9-19             | Port 4 Control Register, Middle Byte (P4CONM)                 |                |

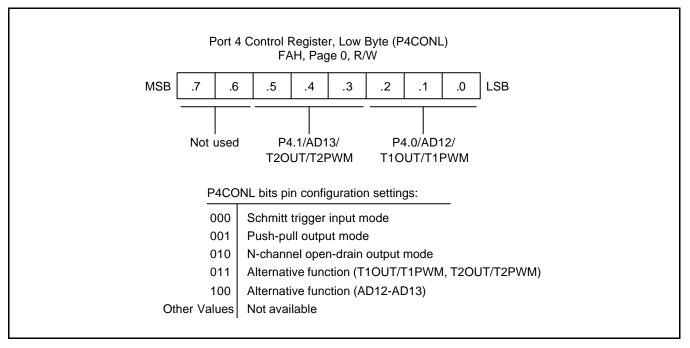

| 9-20             | Port 4 Control Register, Low Byte (P4CONL)                    |                |

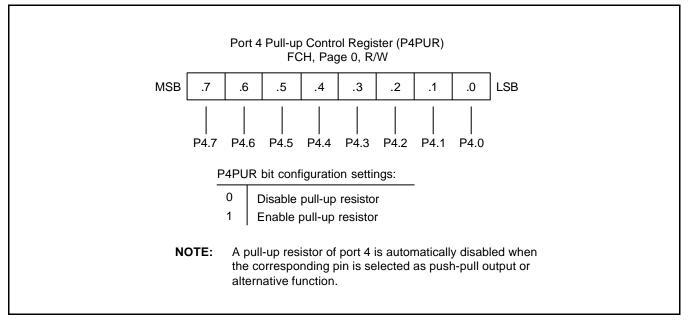

| 9-21             | Port 4 Pull-up Control Register (P4PUR)                       | 9-17           |

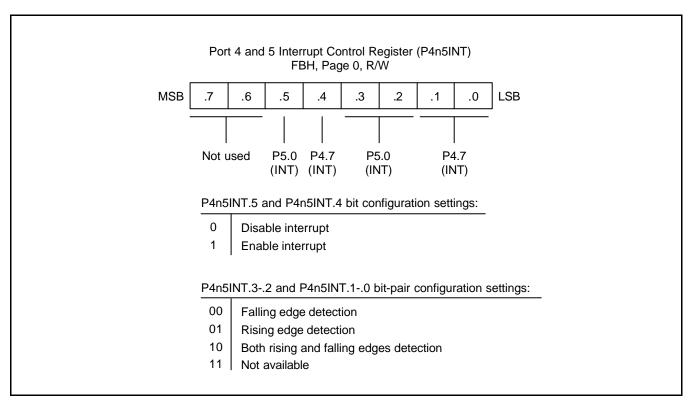

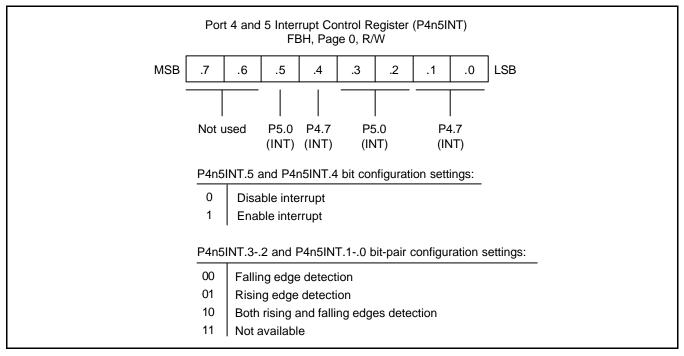

| 9-22             | Port 4 and 5 Interrupt Control Register (P4n5INT)             |                |

| 9-23             | Interrupt Pending Register 2 (INTPND2)                        |                |

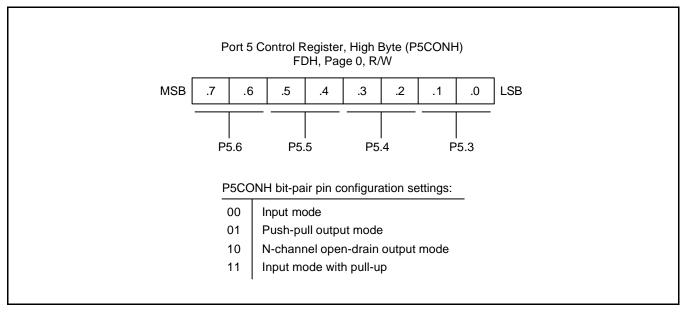

| 9-24             | Port 5 Control Register, High-Byte (P5CONH)                   |                |

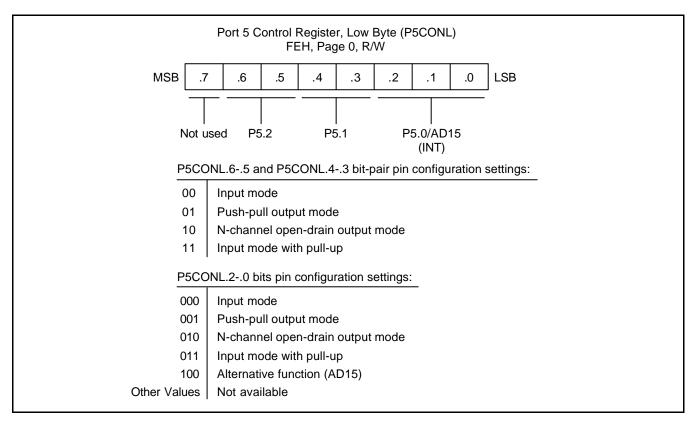

| 9-25             | Port 5 Control Register, Low-Byte (P5CONL)                    |                |

| 9-26             | Port 4 and 5 Interrupt Control Register (P4n5INT)             |                |

| 9-27             | Interrupt Pending Register 2 (INTPND2)                        |                |

## List of Figures (Continued)

| Figure<br>Number | Title                                                    | Page<br>Number |

|------------------|----------------------------------------------------------|----------------|

| 10-1             | Basic Timer Control Register (BTCON)                     | 10-2           |

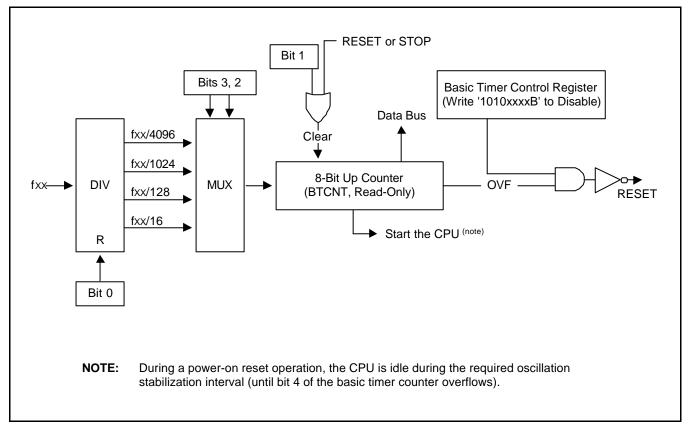

| 10-2             | Basic Timer Block Diagram                                | 10-4           |

| 11-1             | Timer 0 Control Register (T0CON)                         |                |

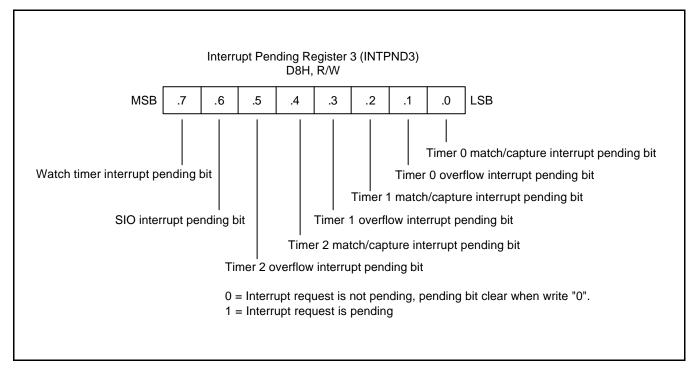

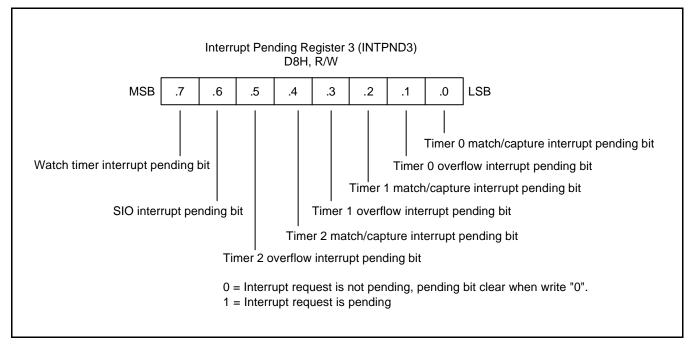

| 11-2             | Interrupt Pending Register 3 (INTPND3)                   |                |

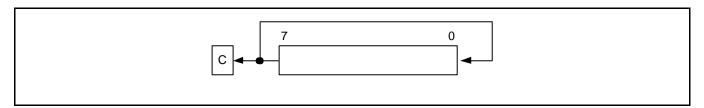

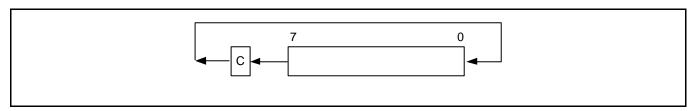

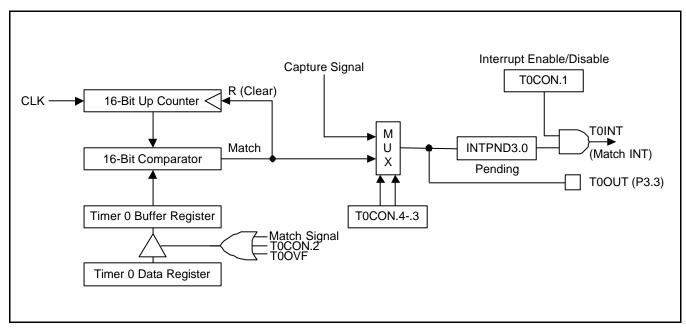

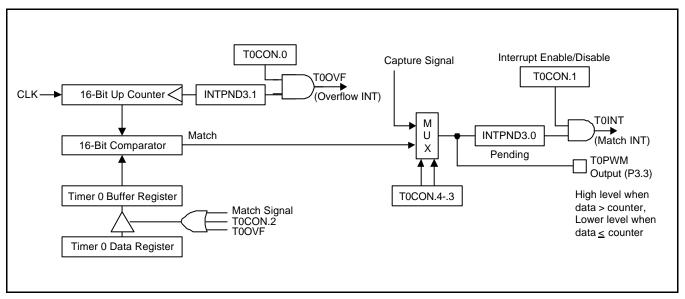

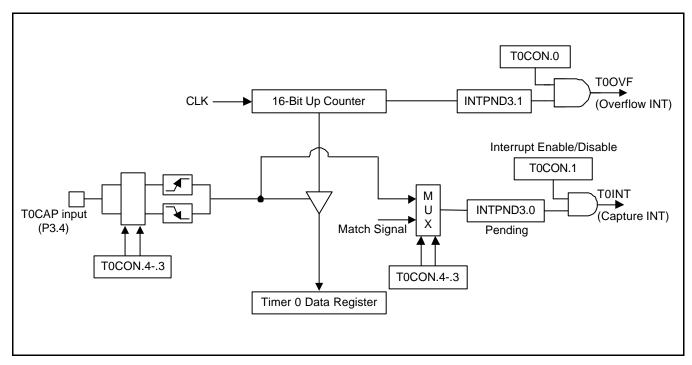

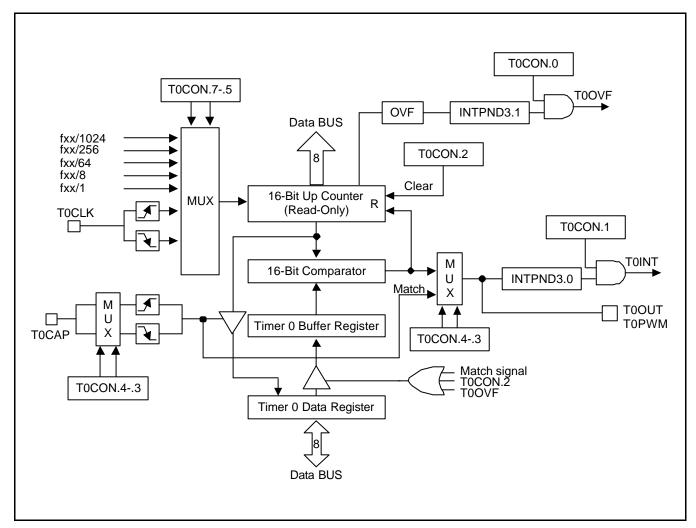

| 11-3             | Simplified Timer 0 Function Diagram: Interval Timer Mode |                |

| 11-4             | Simplified Timer 0 Function Diagram: PWM Mode            | 11-5           |

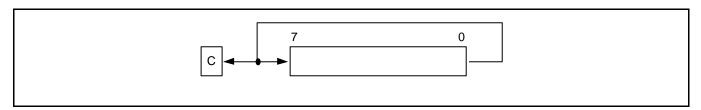

| 11-5             | Simplified Timer 0 Function Diagram: Capture Mode        |                |

| 11-6             | Timer 0 Block Diagram                                    | 11-7           |

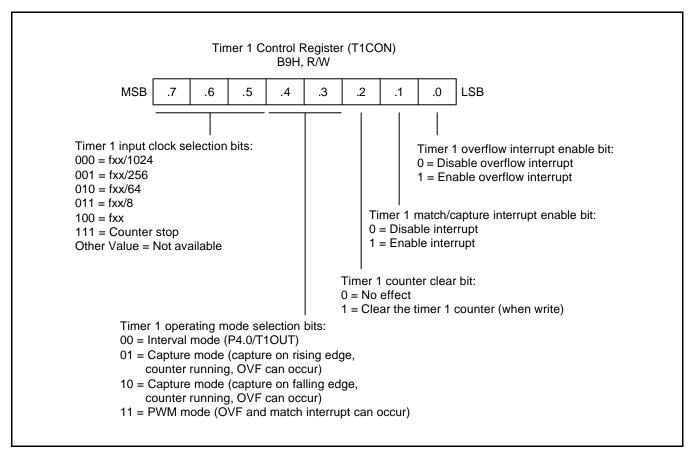

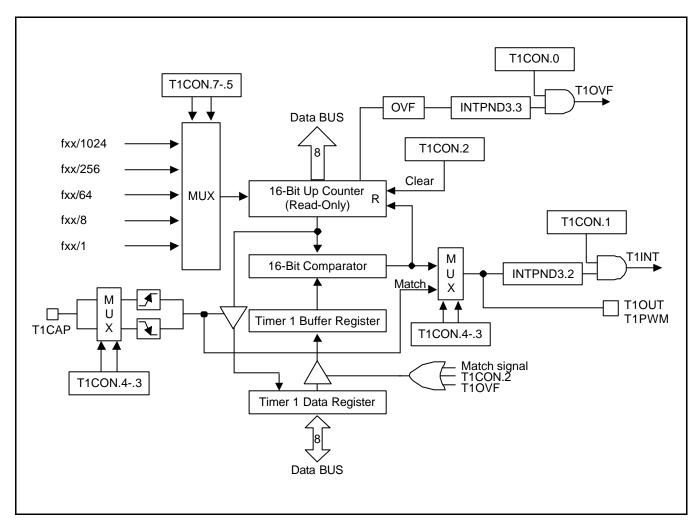

| 12-1             | Timer 1 Control Register (T1CON)                         | 12-2           |

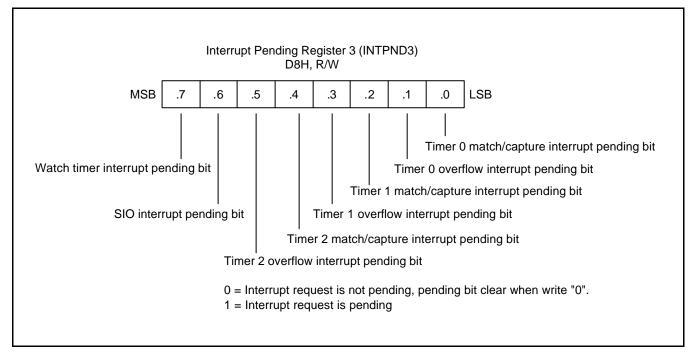

| 12-2             | Interrupt Pending Register 3 (INTPND3)                   | 12-3           |

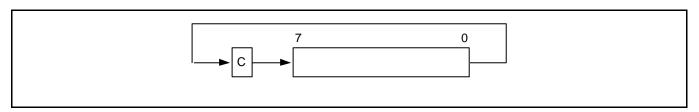

| 12-3             | Simplified Timer 1 Function Diagram: Interval Timer Mode | 12-4           |

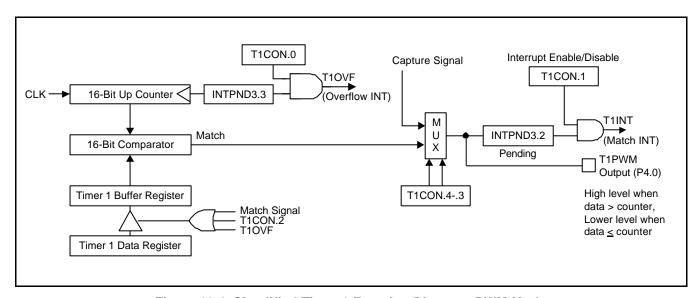

| 12-4             | Simplified Timer 1 Function Diagram: PWM Mode            | 12-5           |

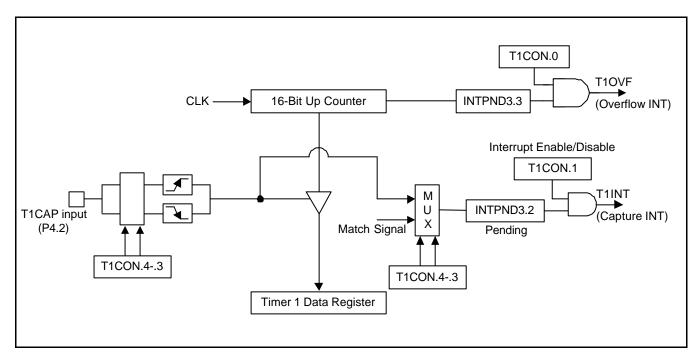

| 12-5             | Simplified Timer 1 Function Diagram: Capture Mode        | 12-6           |

| 12-6             | Timer 1 Block Diagram                                    | 12-7           |

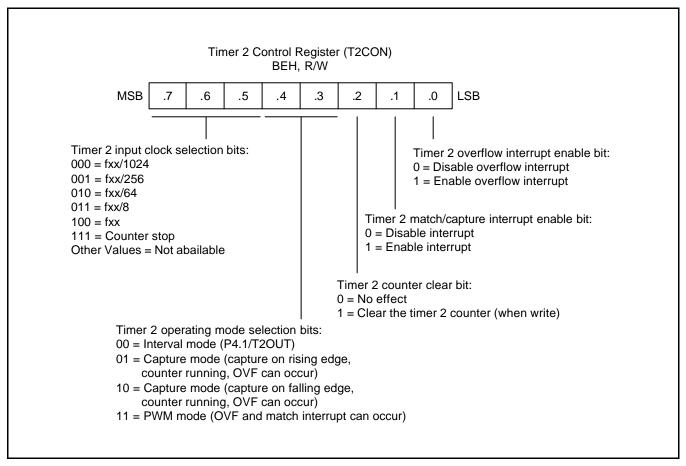

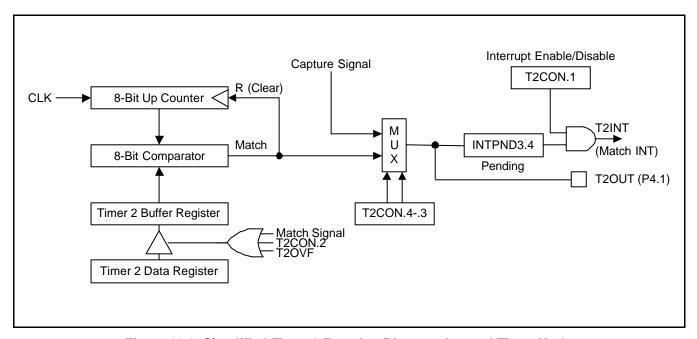

| 13-1             | Timer 2 Control Register (T2CON)                         | 13-2           |

| 13-2             | Interrupt Pending Register 3 (INTPND3)                   | 13-3           |

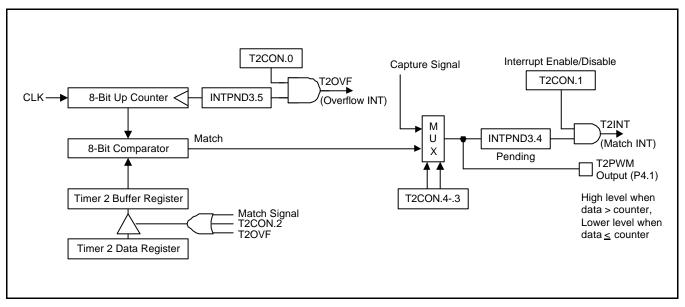

| 13-3             | Simplified Timer 2 Function Diagram: Interval Timer Mode | 13-4           |

| 13-4             | Simplified Timer 2 Function Diagram: PWM Mode            | 13-5           |

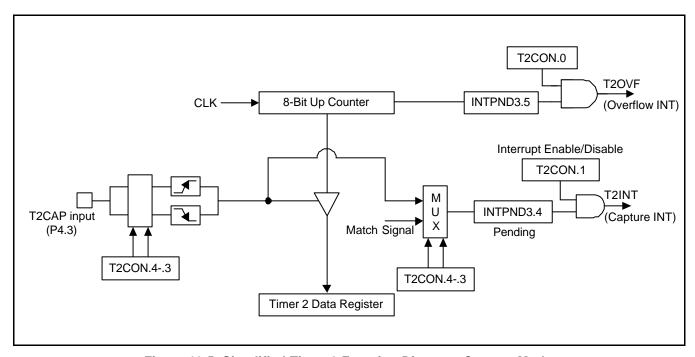

| 13-5             | Simplified Timer 2 Function Diagram: Capture Mode        | 13-6           |

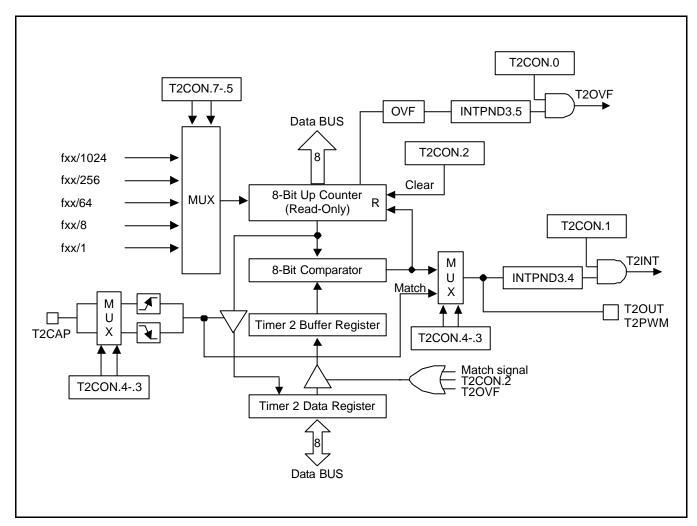

| 13-6             | Timer 2 Block Diagram                                    |                |

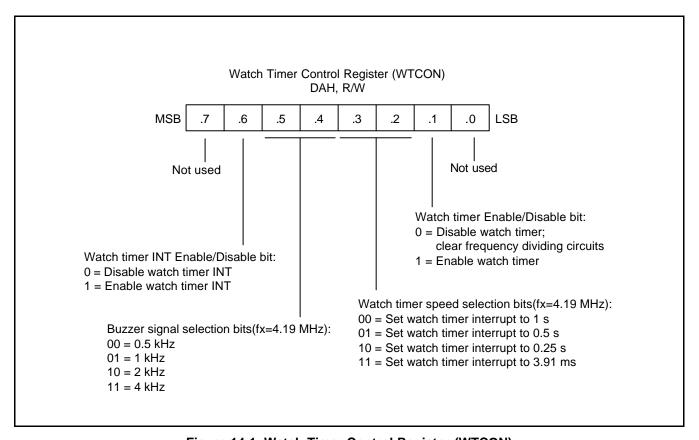

| 14-1             | Watch Timer Control Register (WTCON)                     | 14-2           |

| 14-2             | Watch Timer Circuit Diagram                              |                |

## List of Figures (Continued)

| Figure | Title                                                                    | Page   |

|--------|--------------------------------------------------------------------------|--------|

| Number |                                                                          | Number |

| 15-1   | A/D Converter Control Register (ADCON)                                   | 15-2   |

| 15-2   | A/D Converter Data Register (ADDATAH/ADDATAL)                            | 15-3   |

| 15-3   | A/D Converter Functional Block Diagram                                   | 15-4   |

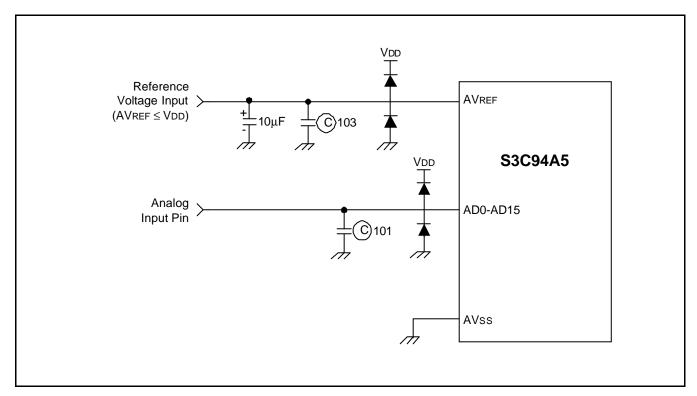

| 15-4   | Recommended A/D Converter Circuit for Highest Absolute Accuracy          | 15-5   |

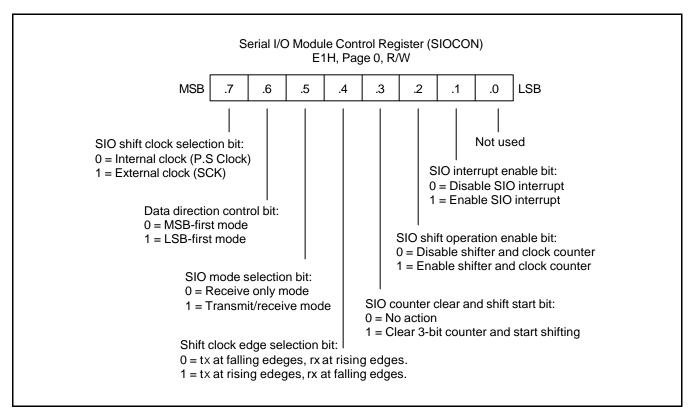

| 16-1   | Serial I/O Module Control Register (SIOCON)                              | 16-2   |

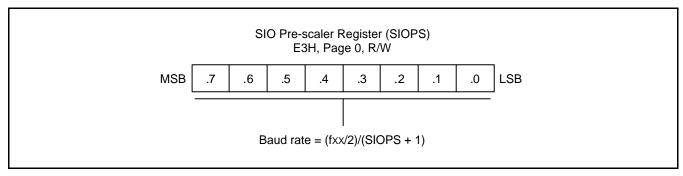

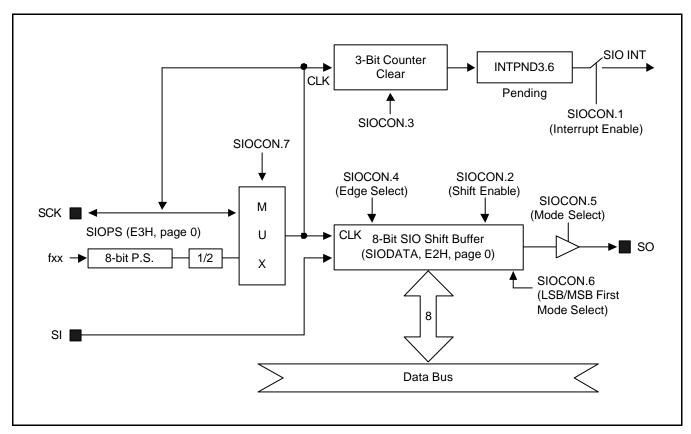

| 16-2   | SIO Prescaler Register (SIOPS)                                           | 16-3   |

| 16-3   | SIO Functional Block Diagram                                             |        |

| 16-4   | Serial I/O Timing in Transmit/Receive Mode (Tx at falling, SIOCON.4 = 0) | 16-4   |

| 16-5   | Serial I/O Timing in Transmit/Receive Mode (Tx at rising, SIOCON.4 = 1)  | 16-4   |

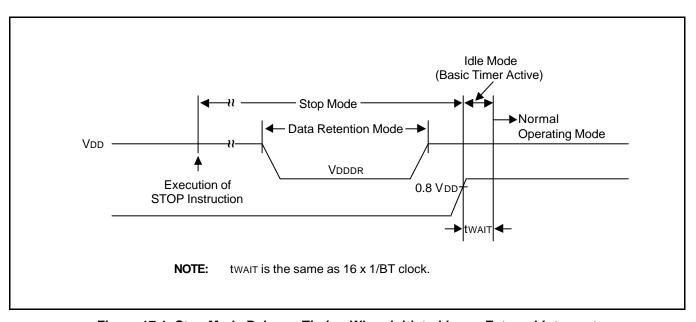

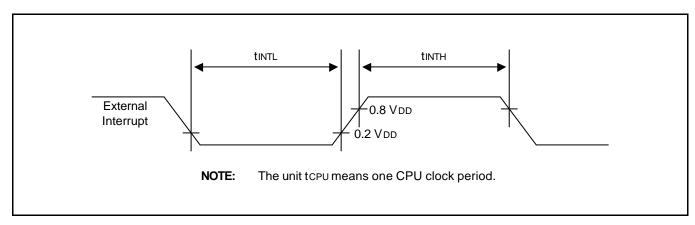

| 17-1   | Stop Mode Release Timing When Initiated by an External Interrupt         | 17-6   |

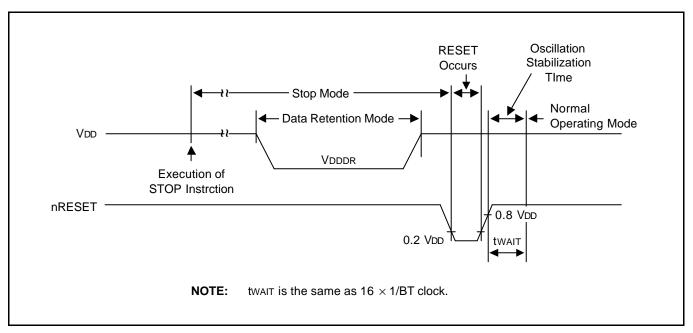

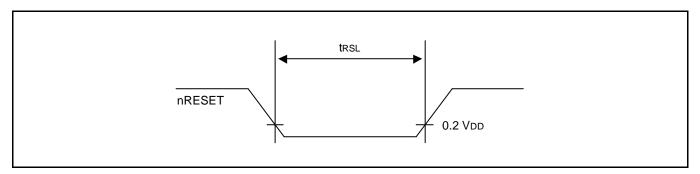

| 17-2   | Stop Mode Release Timing When Initiated by a RESET                       | 17-7   |

| 17-3   | Input Timing for External Interrupts                                     | 17-9   |

| 17-4   | Input Timing for nRESET                                                  | 17-10  |

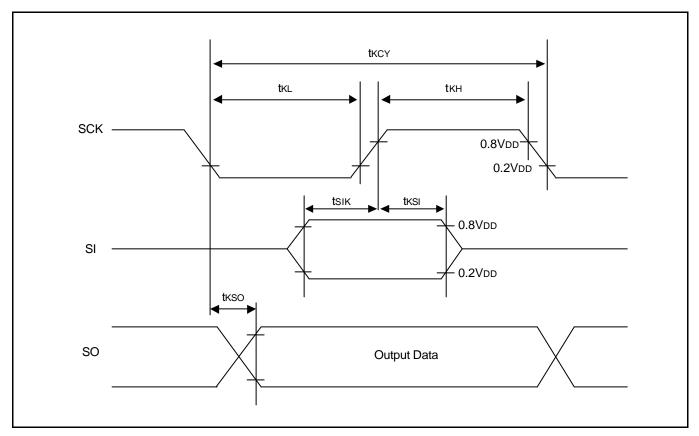

| 17-5   | Serial Data Transfer Timing                                              | 17-10  |

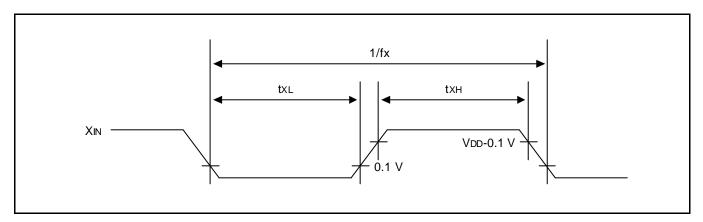

| 17-6   | Clock Timing Measurement at X <sub>N</sub>                               | 17-12  |

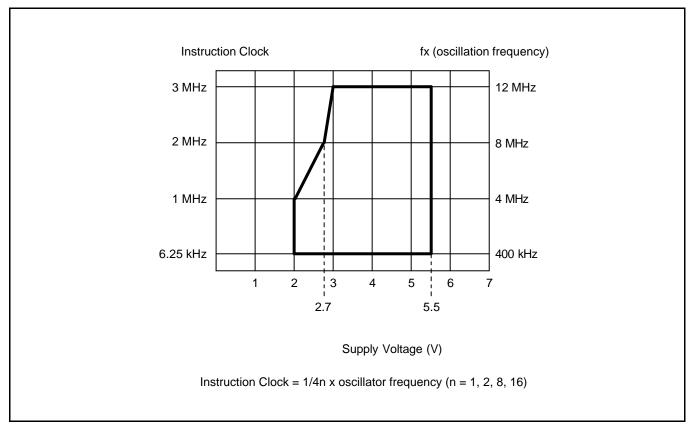

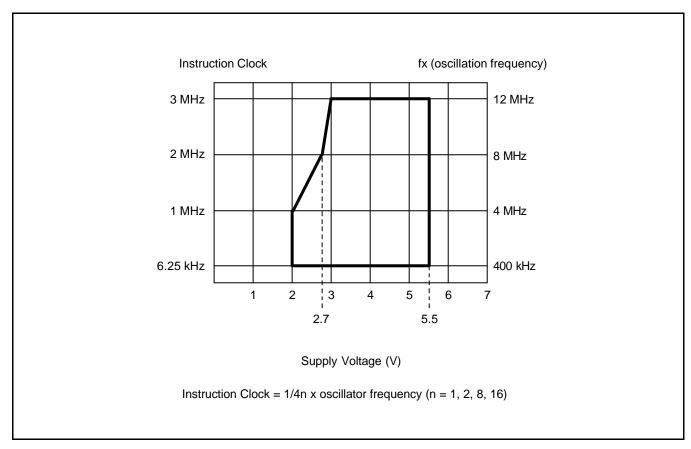

| 17-7   | Operating Voltage Range                                                  | 17-14  |

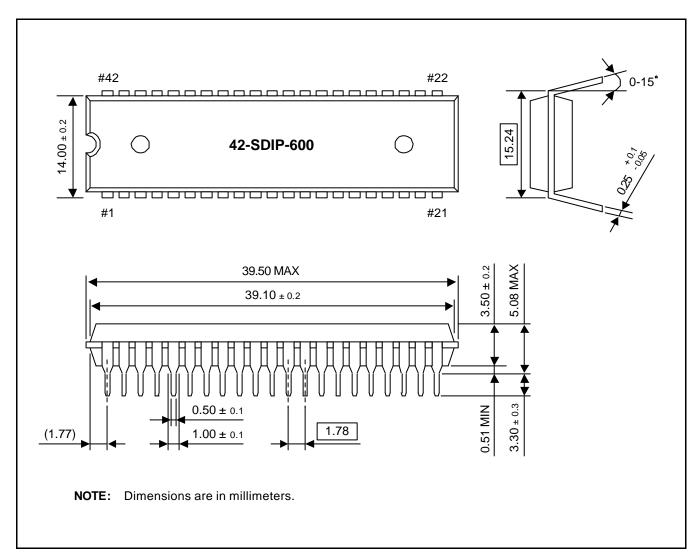

| 18-1   | 42-SDIP-600 Package Dimensions                                           | 18-1   |

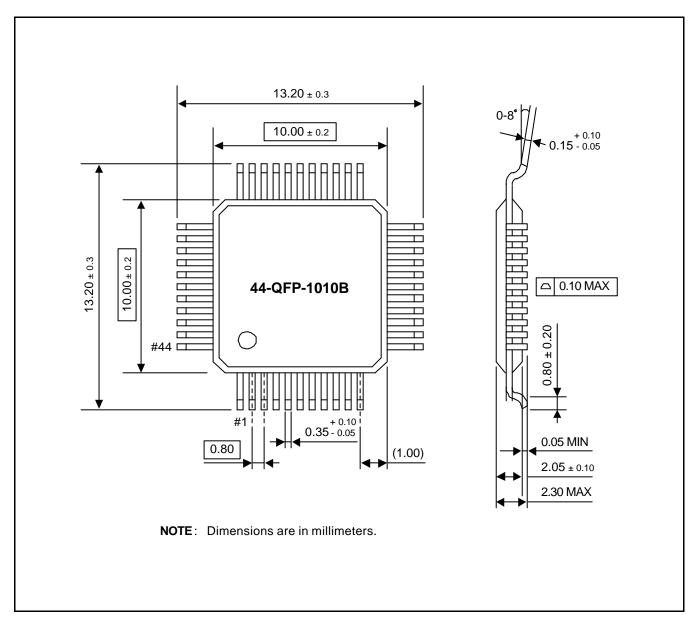

| 18-2   | 44-QFP-1010B Package Dimensions                                          | 18-2   |

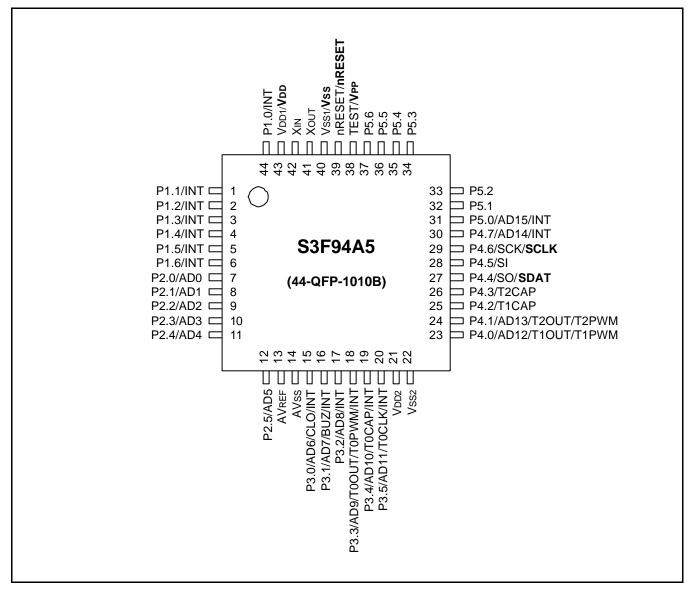

| 19-1   | S3F94A5 Pin Assignments (44-QFP-1010B)                                   | 19-2   |

| 19-2   | S3F94A5 Pin Assignments (42-SDIP-600)                                    | 19-3   |

| 19-3   | Operating Voltage Range                                                  | 19-7   |

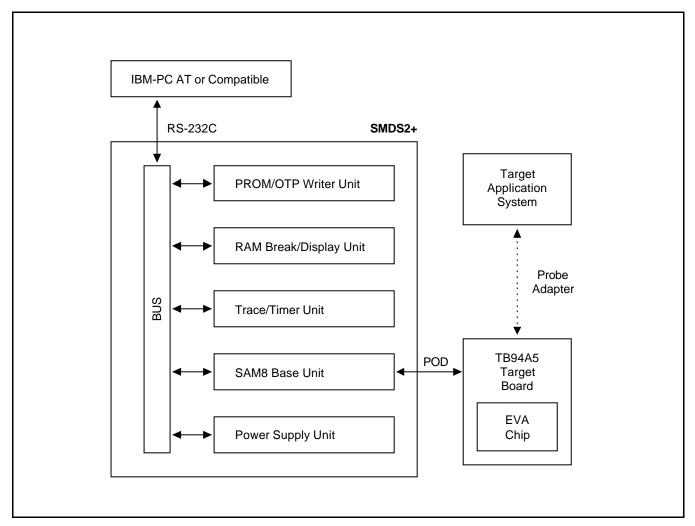

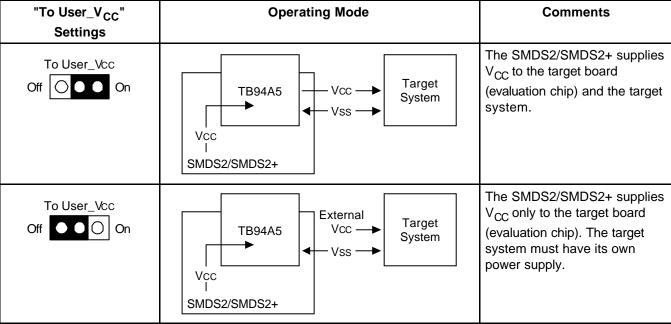

| 20-1   | SMDS Product Configuration (SMDS2+)                                      | 20-2   |

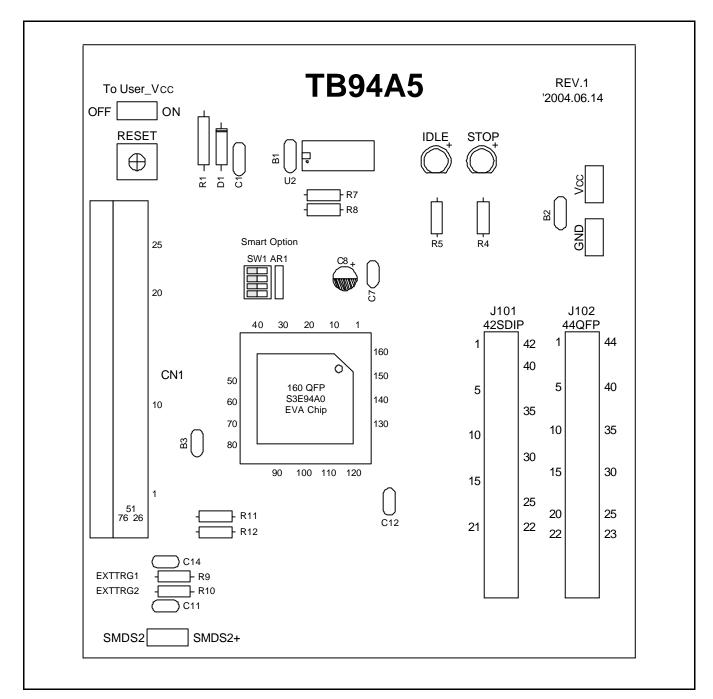

| 20-2   | TB94A5 Target Board Configuration                                        |        |

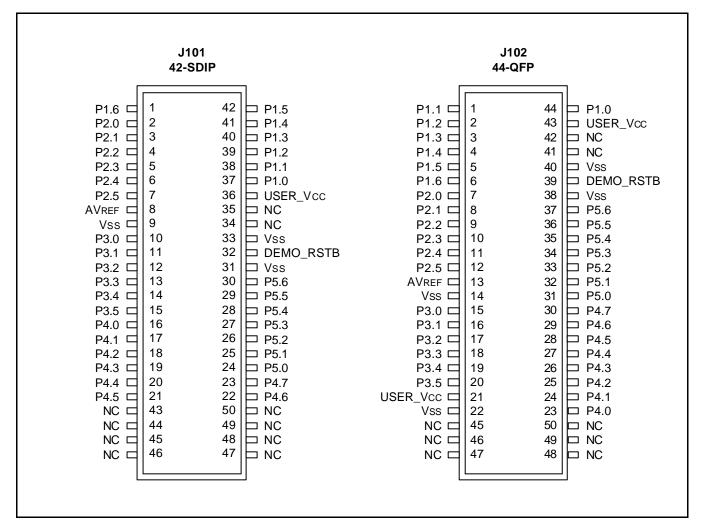

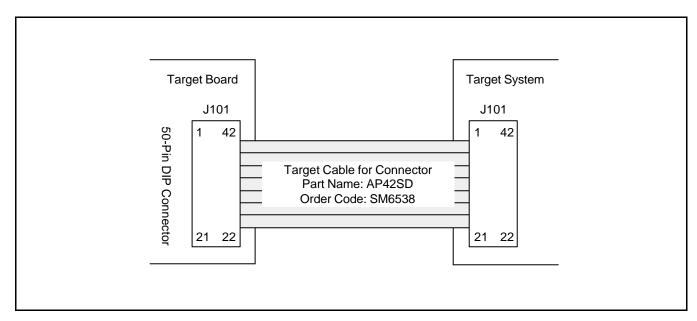

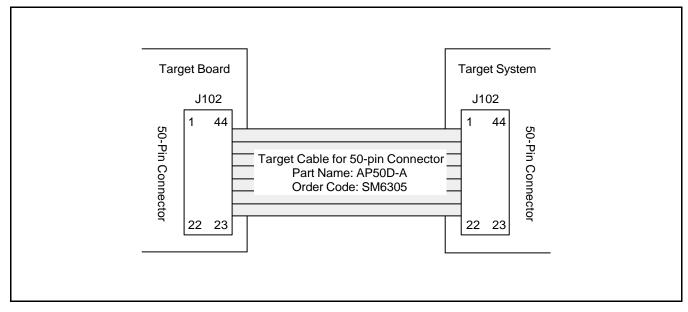

| 20-3   | Connectors (J101, J102) for TB94A5                                       | 20-6   |

| 20-4   | S3C94A5 Probe Adapter for 42-SDIP Package                                | 20-7   |

| 20-5   | S3C94A5 Probe Adapter for 44-QFP Package                                 | 20-7   |

## **List of Tables**

| Table<br>Number | Title                                                                   | Page<br>Numbe |  |

|-----------------|-------------------------------------------------------------------------|---------------|--|

| 1-1             | Pin Descriptions                                                        | 1-6           |  |

| 4-1             | System and Peripheral Control Registers                                 | 4-2           |  |

| 6-1             | Instruction Group Summary                                               |               |  |

| 6-2             | Flag Notation Conventions                                               |               |  |

| 6-3             | Instruction Set Symbols                                                 |               |  |

| 6-4             | Instruction Notation Conventions                                        |               |  |

| 6-5             | Opcode Quick Reference                                                  |               |  |

| 6-6             | Condition Codes                                                         | 6-9           |  |

| 8-1             | Register Values after RESET                                             | 8-4           |  |

| 9-1             | S3C94A5 Port Configuration Overview                                     | 9-1           |  |

| 9-2             | Port Data Register Summary                                              | 9-2           |  |

| 17-1            | Absolute Maximum Ratings                                                | 17-2          |  |

| 17-2            | D.C. Electrical Characteristics                                         | 17-3          |  |

| 17-3            | Data Retention Supply Voltage in Stop Mode                              | 17-6          |  |

| 17-4            | Input/Output Capacitance                                                | 17-7          |  |

| 17-5            | A.C. Electrical Characteristics                                         | 17-8          |  |

| 17-6            | A/D Converter Electrical Characteristics                                | 17-9          |  |

| 17-7            | Main Oscillation Characteristics                                        | 17-11         |  |

| 17-8            | Main Oscillator Stabilization Time                                      | 17-12         |  |

| 17-9            | External RC Oscillation (Mode 2) Characteristics                        | 17-13         |  |

| 17-10           | Internal RC Oscillation Characteristics                                 | 17-13         |  |

| 19-1            | Descriptions of Pins Used to Read/Write the Flash ROM                   | 19-4          |  |

| 19-2            | Comparison of S3F94A5 and S3C94A5 Features                              | 19-4          |  |

| 19-3            | Operating Mode Selection Criteria                                       | 19-5          |  |

| 19-4            | D.C. Electrical Characteristics                                         | 19-6          |  |

| 20-1            | Power Selection Settings for TB94A5                                     | 20-4          |  |

| 20-2            | Smart Option Switch Settings for TB94A5                                 |               |  |

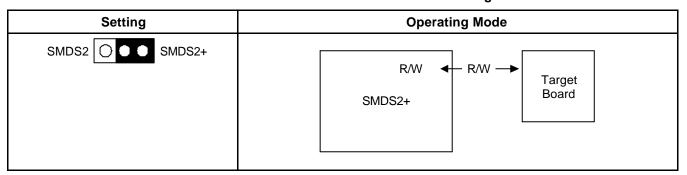

| 20-3            | The SMDS2+ Tool Selection Setting                                       |               |  |

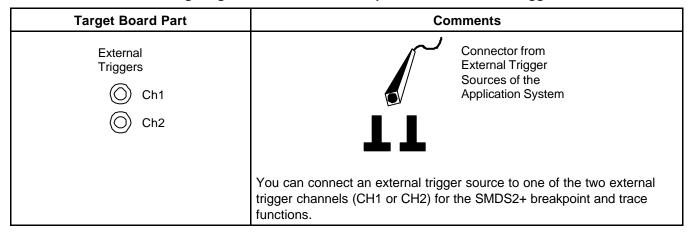

| 20-4            | Using Single Header Pins as the Input Path for External Trigger Sources |               |  |

## **List of Programming Tips**

| Description          |                                                                           | Page<br>Numbe |

|----------------------|---------------------------------------------------------------------------|---------------|

| Chapter 2:           | Address Spaces                                                            |               |

| Addressi<br>Standard | ing the Common Working Register Aread Stack Operations Using PUSH and POP | 2-6<br>2-8    |

| Chapter 5:           | Interrupt Structure                                                       |               |

| How to c             | clear an interrupt pending bit                                            | 5-6           |

| Chapter 7:           | Clock Circuits                                                            |               |

| How to U             | Jse Stop Instruction                                                      | 7-5           |

## **List of Register Descriptions**

| Register   | Full Register Name                                   | Page   |

|------------|------------------------------------------------------|--------|

| Identifier |                                                      | Number |

| ADCON      | A/D Converter Control Register                       | 4-5    |

| BTCON      | Basic Timer Control Register                         |        |

| CLKCON     | System Clock Control Register                        | 4-7    |

| FLAGS      | System Flags Register                                |        |

| INTPND1    | Interrupt Pending Register 1                         | 4-9    |

| INTPND2    | Interrupt Pending Register 2                         | 4-10   |

| INTPND3    | Interrupt Pending Register 3                         | 4-11   |

| P1CONH     | Port 1 Control Register (High Byte)                  | 4-12   |

| P1CONL     | Port 1 Control Register (Low Byte)                   | 4-13   |

| P1INT      | Port 1 Interrupt Control Register                    | 4-14   |

| P1EDGEH    | Port 1 Interrupt Edge Selection Register (High Byte) | 4-15   |

| P1EDGEL    | Port 1 Interrupt Edge Selection Register (Low Byte)  | 4-16   |

| P2CONH     | Port 2 Control Register (High Byte)                  | 4-17   |

| P2CONL     | Port 2 Control Register (Low Byte)                   | 4-18   |

| P2PUR      | Port 2 Pull-up Control Register                      | 4-19   |

| P3CONH     | Port 3 Control Register (High Byte)                  | 4-20   |

| P3CONL     | Port 3 Control Register (Low Byte)                   | 4-21   |

| P3INT      | Port 3 Interrupt Control Register                    | 4-22   |

| P3EDGEH    | Port 3 Interrupt Edge Selection Register (High Byte) | 4-23   |

| P3EDGEL    | Port 3 Interrupt Edge Selection Register (Low Byte)  |        |

| P3PUR      | Port 3 Pull-up Control Register                      | 4-25   |

| P4CONH     | Port 4 Control Register (High Byte)                  | 4-26   |

| P4CONM     | Port 4 Control Register (Middle Byte)                |        |

| P4CONL     | Port 4 Control Register (Low Byte)                   |        |

| P4n5INT    | Port 4 and 5 Interrupt Control Register              |        |

| P4PUR      | Port 4 Pull-up Control Register                      |        |

| P5CONH     | Port 5 Control Register (High Byte)                  |        |

| P5CONL     | Port 5 Control Register (Low Byte)                   |        |

| SIOCON     | SIO Control Register                                 |        |

| STPCON     | Stop Control Register                                |        |

| SYM        | System Mode Register                                 |        |

| T0CON      | Timer 0 Control Register                             |        |

| T1CON      | Timer 1 Control Register                             |        |

| T2CON      | Timer 2 Control Register                             |        |

| WTCON      | Watch Timer Control Register                         | 4-39   |

## **List of Instruction Descriptions**

| Instruction<br>Mnemonic | Full Instruction Name      | Page<br>Numbe |

|-------------------------|----------------------------|---------------|

| ADC                     | Add With Carry             | 6-11          |

| ADD                     | Add                        | 6-12          |

| AND                     | Logical AND                | 6-13          |

| CALL                    | Call Procedure             | 6-14          |

| CCF                     | Complement Carry Flag      | 6-15          |

| CLR                     | Clear                      | 6-16          |

| COM                     | Complement                 | 6-17          |

| CP                      | Compare                    | 6-18          |

| DEC                     | Decrement                  | 6-19          |

| DI                      | Disable Interrupts         | 6-20          |

| El                      | Enable Interrupts          | 6-21          |

| IDLE                    | Idle Operation             | 6-22          |

| INC                     | Increment                  | 6-23          |

| IRET                    | Interrupt Return           | 6-24          |

| JP                      | Jump                       | 6-25          |

| JR                      | Jump Relative              | 6-26          |

| LD                      | Load                       | 6-27          |

| LDC/LDE                 | Load Memory                | 6-29          |

| LDCD/LDED               | Load Memory and Decrement  | 6-31          |

| LDCI/LDEI               | Load Memory and Increment  | 6-32          |

| NOP                     | No Operation               | 6-33          |

| OR                      | Logical OR                 | 6-34          |

| POP                     | Pop From Stack             | 6-35          |

| PUSH                    | Push To Stack              | 6-36          |

| RCF                     | Reset Carry Flag           | 6-37          |

| RET                     | Return                     | 6-38          |

| RL                      | Rotate Left                | 6-39          |

| RLC                     | Rotate Left Through Carry  | 6-40          |

| RR                      | Rotate Right               | 6-41          |

| RRC                     | Rotate Right Through Carry | 6-42          |

| SBC                     | Subtract With Carry        | 6-43          |

| SCF                     | Set Carry Flag             | 6-44          |

| SRA                     | Shift Right Arithmetic     | 6-45          |

| STOP                    | Stop Operation             | 6-46          |

| SUB                     | Subtract                   | 6-47          |

| TCM                     | Test Complement Under Mask | 6-48          |

| TM                      | Test Under Mask            | 6-49          |

| XOR                     | Logical Exclusive OR       | 6-50          |

S3C94A5/F94A5 PRODUCT OVERVIEW

1

## **PRODUCT OVERVIEW**

#### SAM88RCRI PRODUCT FAMILY

Samsung's SAM88RCRI family of 8-bit single-chip CMOS microcontrollers offer fast and efficient CPU, a wide range of integrated peripherals, and supports Flash device.

A dual address/data bus architecture and bit- or nibble-configurable I/O ports provide a flexible programming environment for applications with varied memory and I/O requirements. Timer/counters with selectable operating modes are included to support real-time operations.

#### S3C94A5/F94A5 MICROCONTROLLER

The S3C94A5 can be used for dedicated control functions in a variety of applications, and is especially designed for application with printer or etc.

The S3C94A5/F94A5 single-chip 8-bit microcontroller is fabricated using an advanced CMOS process. It is built around the powerful SAM88RCRI CPU core.

Stop and Idle power-down modes were implemented to reduce power consumption. To increase on-chip register space, the size of the internal register file was logically expanded. The S3C94A5/F94A5 has 16K-byte of program ROM, and 368-byte of RAM (including 16-byte of working register).

Using the SAM88RCRI design approach, the following peripherals were integrated with the SAM88RCRI core:

- 5 configurable I/O ports including ports

- 15-bit programmable pins for external interrupts

- One 8-bit basic timer for oscillation stabilization and watch-dog functions

- Two 16-bit timer/counters and one 8-bit timer/counter with selectable operating modes

- Watch timer for real time

- 16 channel A/D converter

- 8-bit serial I/O interface

#### **FLASH**

The S3F94A5 microcontroller is available in Flash version. S3C94A5 microcontroller has an on-chip 16K-byte masked ROM. The S3F94A5 is comparable to S3C94A5, both in function and in pin configuration.

PRODUCT OVERVIEW S3C94A5/F94A5

#### **FEATURES**

#### **CPU**

SAM88RCRI CPU core

#### Memory

- 16k × 8 bits program memory (ROM)

- 368 × 8 bits data memory (RAM)

#### **Instruction Set**

- 41 instructions

- Idle and Stop instructions added for power-down modes

#### 34 I/O Pins

High sink current (20mA at 3.3V)

#### Interrupts

- 23 interrupt source and 1 vector

- One interrupt level

#### 8-Bit Basic Timer

- Watchdog timer function

- 4 kinds of clock source

#### 16-Bit Timer/Counter 0

- External event counter

- PWM and capture function

#### 16-Bit Timer/Counter 1

- Programmable 16-bit interval timer

- PWM and capture function

#### 8-Bit Timer/Counter 2

- Programmable 8-bit interval timer

- PWM and capture function

#### **Watch Timer**

- Interval time: 3.91mS, 0.25S, 0.5S, and 1S at 4.19 MHz

- 0.5/1/2/4 kHz Selectable buzzer output

#### 8-bit Serial I/O Interface

- 8-bit transmit/receive mode

- 8-bit receive mode

- LSB-first or MSB-first transmission selectable

- Internal or external clock source

#### A/D Converter

- 10-bit converter resolution

- 50us conversion speed at 1MHz f<sub>ADC</sub> clock

- 16-channel

#### **Two Power-Down Modes**

- · Idle mode: only CPU clock stops

- Stop mode: system clock and CPU clock stop

#### **Oscillation Sources**

- Crystal, ceramic, or RC for main clock (Internal or external RC oscillation)

- System clock frequency: 0.4 MHz 12 MHz

- CPU clock output

#### **Instruction Execution Times**

333nS at 12 MHz fx (minimum)

#### **Operating Voltage Range**

- 2.0 V to 5.5 V at 4.2 MHz

- 2.7 V to 5.5 V at 8 MHz

- 3.0 V to 5.5 V at 12 MHz

#### **Operating Temperature Range**

• −25 °C to +85 °C

#### **Package Type**

• 44-pin QFP, 42-pin SDIP

#### **Smart Option**

Oscillator type selectable by ROM option (ROM address 3FH)

S3C94A5/F94A5 PRODUCT OVERVIEW

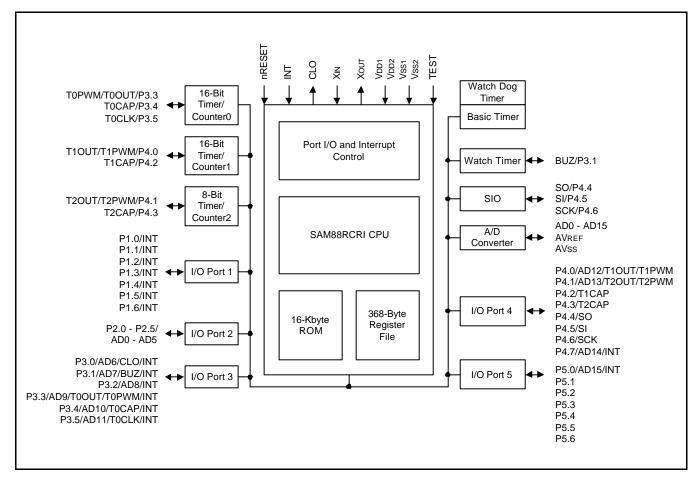

#### **BLOCK DIAGRAM**

Figure 1-1. Block Diagram

PRODUCT OVERVIEW S3C94A5/F94A5

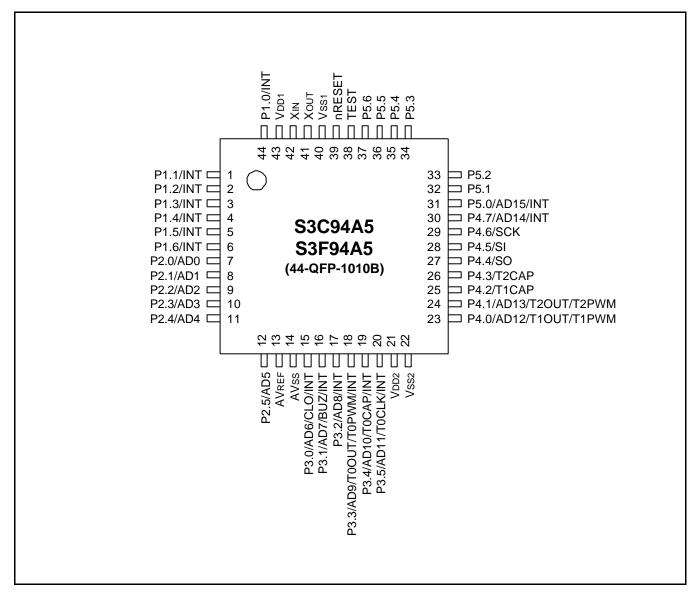

#### **PIN ASSIGNMENTS**

Figure 1-2. S3C94A5/F94A5 Pin Assignments (44-QFP-1010B)

S3C94A5/F94A5 PRODUCT OVERVIEW

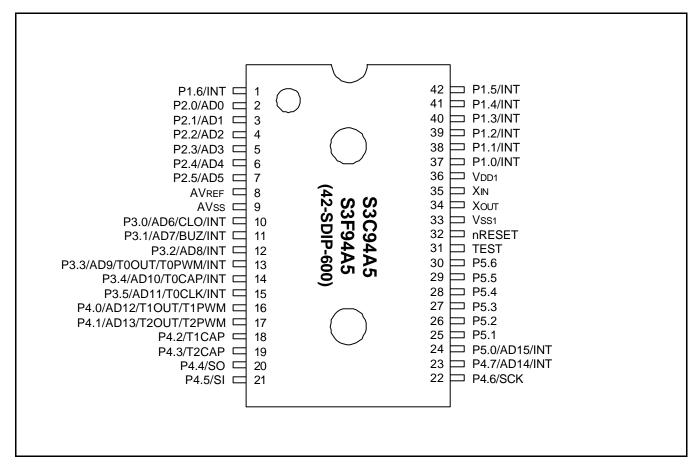

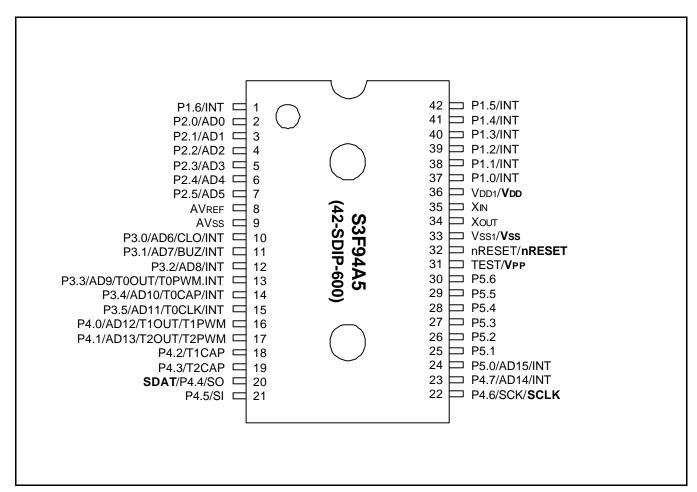

Figure 1-3. S3C94A5/F94A5 Pin Assignments (42-SDIP-600)

PRODUCT OVERVIEW S3C94A5/F94A5

#### **PIN DESCRIPTIONS**

**Table 1-1. Pin Descriptions**

| Pin Names | Pin<br>Type | Pin Description                                                         | Circuit<br>Number | Pin<br>Numbers | Share<br>Pins  |

|-----------|-------------|-------------------------------------------------------------------------|-------------------|----------------|----------------|

| P1.0      | I/O         | 1-bit programmable I/O port.                                            | E-4               | 44(37)         | INT            |

| P1.1      |             | Schmitt trigger input or push-pull, open-                               |                   | 1(38)          | INT            |

| P1.2      |             | drain output and software assignable pull-                              |                   | 2(39)          | INT            |

| P1.3      |             | ups.                                                                    |                   | 3(40)          | INT            |

| P1.4      |             |                                                                         |                   | 4(41)          | INT            |

| P1.5      |             |                                                                         |                   | 5(42)          | INT            |

| P1.6      |             |                                                                         |                   | 6(1)           | INT            |

| P2.0      | I/O         | 1-bit programmable I/O port.                                            | F-16              | 7(2)           | AD0            |

| P2.1      |             | Input or push-pull, open-drain output and                               |                   | 8(3)           | AD1            |

| P2.2      |             | software assignable pull-ups.                                           |                   | 9(4)           | AD2            |

| P2.3      |             |                                                                         |                   | 10(5)          | AD3            |

| P2.4      |             |                                                                         |                   | 11(6)          | AD4            |

| P2.5      |             |                                                                         |                   | 12(7)          | AD5            |

| P3.0      | I/O         | 1-bit programmable I/O port.                                            | F-16A             | 15(10)         | AD6/CLO/INT    |

| P3.1      |             | Schmitt trigger input or push-pull, open-                               |                   | 16(11)         | AD7/BUZ/INT    |

| P3.2      |             | drain output and software assignable pull-                              |                   | 17(12)         | AD8/INT        |

| P3.3      |             | ups.                                                                    |                   | 18(13)         | AD9/T0OUT/     |

|           |             |                                                                         |                   |                | T0PWM/INT      |

| P3.4      |             |                                                                         |                   | 19(14)         | AD10/T0CAP/INT |

| P3.5      |             |                                                                         |                   | 20(15)         | AD11/T0CLK/INT |

| P4.0      | I/O         | 1-bit programmable I/O port.                                            | F-16A             | 23(16)         | AD12/T1OUT/    |

|           |             | Schmitt trigger input or push-pull, open-                               |                   |                | T1PWM          |

| P4.1      |             | drain output and software assignable pull-                              | F-16A             | 24(17)         | AD13/T2OUT/    |

|           |             | ups.                                                                    |                   |                | T2PWM          |

| P4.2      |             |                                                                         | E-4               | 25(18)         | T1CAP          |

| P4.3      |             |                                                                         | E-4               | 26(19)         | T2CAP          |

| P4.4      |             |                                                                         | E-4               | 27(20)         | SO             |

| P4.5      |             |                                                                         | E-4               | 28(21)         | SI             |

| P4.6      |             |                                                                         | E-4               | 29(22)         | SCK            |

| P4.7      | 1/0         |                                                                         | F-16A             | 30(23)         | AD14/INT       |

| P5.0      | I/O         | 1-bit programmable I/O port.                                            | F-16              | 31(24)         | AD15/INT       |

| P5.1–P5.6 |             | Input or push-pull, open-drain output and software assignable pull-ups. | E-2               | 32-37(25-30)   | _              |

**NOTE:** Parentheses indicate pin number for 42-SDIP-600 package.

S3C94A5/F94A5 PRODUCT OVERVIEW

Table 1-1. Pin Descriptions (Continued)

| Pin Names                                                                  | Pin<br>Type | Pin Description                                                                | Circuit<br>Number              | Pin<br>Numbers                                      | Share<br>Pins                                        |

|----------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------|------------------------------------------------------|

| V <sub>DD1</sub> , V <sub>SS1</sub><br>V <sub>DD2</sub> , V <sub>SS2</sub> | -           | Power input pins for internal power block                                      | _                              | 43,40(36,33)<br>21,22(-)                            | -                                                    |

| X <sub>OUT</sub> , X <sub>IN</sub>                                         | _           | Oscillator pins for system clock                                               | _                              | 41,42(34,35)                                        | _                                                    |

| TEST                                                                       | _           | Chip test input pin Hold GND when the device is operating                      | _                              | 38(31)                                              | -                                                    |

| nRESET                                                                     | I           | nRESET signal input pin. Schmitt trigger input with internal pull-up resistor. | В                              | 39(32)                                              | _                                                    |

| INT                                                                        | I/O         | External interrupts input.                                                     | E-4                            | 44,1-6<br>(37-42,1)                                 | P1.0-P1.6                                            |

|                                                                            |             |                                                                                | F-16A<br>F-16A<br>F-16         | 15-20(10-15)<br>30(23)<br>31(24)                    | P3.0-P3.5<br>P4.7<br>P5.0                            |

| T0CLK                                                                      | I/O         | Timer 0 external clock input                                                   | F-16A                          | 20(15)                                              | P3.5                                                 |

| T0CAP                                                                      | I/O         | Timer 0 capture input                                                          | F-16A                          | 19(14)                                              | P3.4                                                 |

| T0OUT                                                                      | I/O         | Timer 0 clock output                                                           | F-16A                          | 18(13)                                              | P3.3                                                 |

| T0PWM                                                                      | I/O         | Timer 0 PWM output                                                             | F-16A                          | 18(13)                                              | P3.3                                                 |

| T1CAP                                                                      | I/O         | Timer 1 capture input                                                          | E-4                            | 25(18)                                              | P4.2                                                 |

| T1OUT                                                                      | I/O         | Timer 1 clock output                                                           | F-16A                          | 23(16)                                              | P4.0                                                 |

| T1PWM                                                                      | I/O         | Timer 1 PWM input                                                              | F-16A                          | 23(16)                                              | P4.0                                                 |

| T2CAP                                                                      | I/O         | Timer 2 capture input                                                          | E-4                            | 26(19)                                              | P4.3                                                 |

| T2OUT                                                                      | I/O         | Timer 2 clock output                                                           | F-16A                          | 24(17)                                              | P4.1                                                 |

| T2PWM                                                                      | I/O         | Timer 2 PWM output                                                             | F-16A                          | 24(17)                                              | P4.1                                                 |

| AD0-AD5<br>AD6-AD11<br>AD12,13,14<br>AD15                                  | I/O         | Analog input pins for A/D converts module                                      | F-16<br>F-16A<br>F-16A<br>F-16 | 7-12(2-7)<br>15-20(10-15)<br>23,24,30<br>(16,17,23) | P2.0-P2.5<br>P3.0-P3.5<br>P4.0,P4.1,<br>P4.7<br>P5.0 |

|                                                                            |             | A/D convertor reference valtage                                                | F-10                           | 31(24)                                              | P5.0                                                 |

| AV <sub>REF</sub>                                                          | _           | A/D converter reference voltage                                                | _                              | 13(8)                                               | _                                                    |

| AV <sub>SS</sub>                                                           | _           | A/D converter ground                                                           | _                              | 14(9)                                               | _                                                    |

| BUZ                                                                        | I/O         | Buzzer signal output                                                           | F-16A                          | 16(11)                                              | P3.1                                                 |

| CLO                                                                        | I/O         | CPU clock output                                                               | F-16A                          | 15(10)                                              | P3.0                                                 |

| SCK<br>SI<br>SO                                                            | I/O         | Serial clock, serial data input, serial data output                            | E-4                            | 29(22)<br>28(21)<br>27(20)                          | P4.6<br>P4.5<br>P4.4                                 |

**NOTE:** Parentheses indicate pin number for 42-SDIP-600 package.

PRODUCT OVERVIEW S3C94A5/F94A5

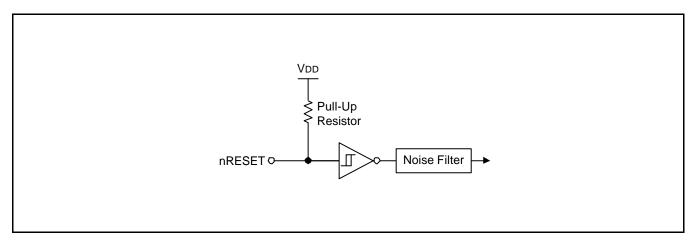

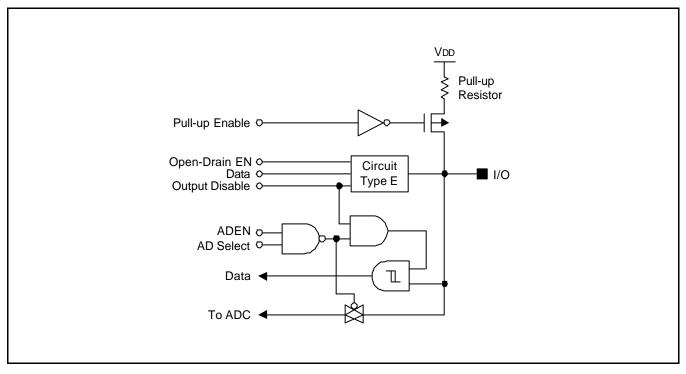

#### **PIN CIRCUIT DIAGRAMS**

Figure 1-4. Pin Circuit Type B (nRESET)

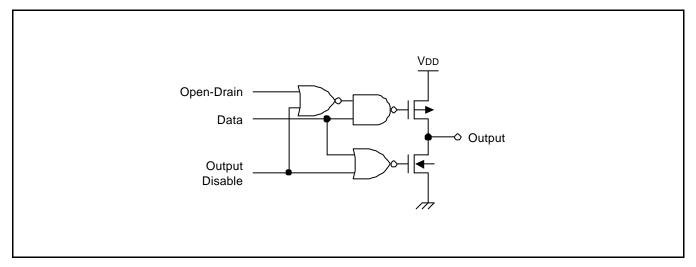

Figure 1-5. Pin Circuit Type E

S3C94A5/F94A5 PRODUCT OVERVIEW

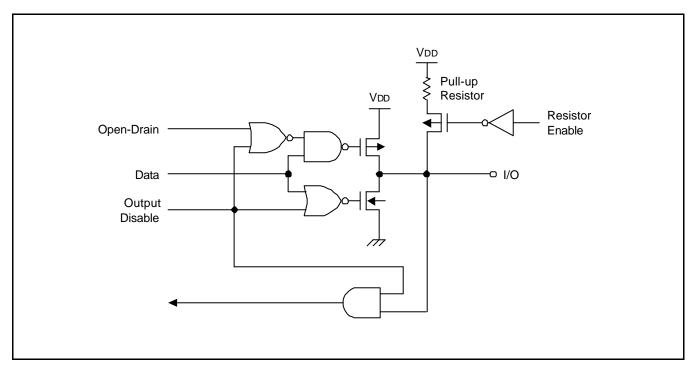

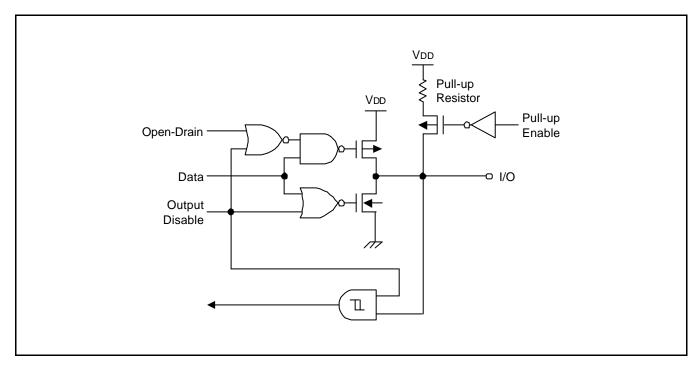

Figure 1-6. Pin Circuit Type E-2 (P5.1-P5.6)

Figure 1-7. Pin Circuit Type E-4 (P1, P4.2–P4.6)

PRODUCT OVERVIEW S3C94A5/F94A5

Figure 1-8. Pin Circuit Type F-16 (P2, P5.0)

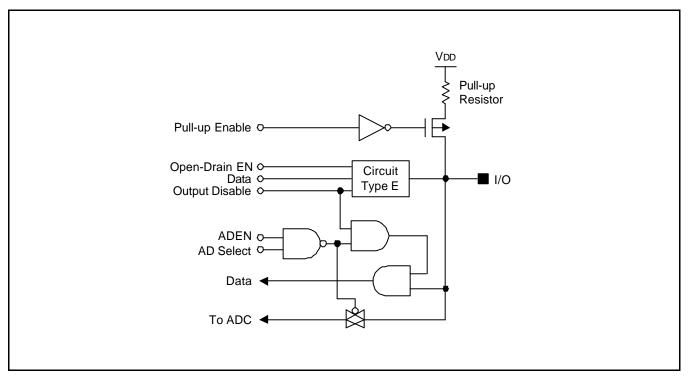

Figure 1-9. Pin Circuit Type F-16A (P3, P4.0, P4.1, P4.7)

S3C94A5/F94A5 ADDRESS SPACES

## 2 ADDRESS SPACES

#### **OVERVIEW**

The S3C94A5/F94A5 microcontroller has two kinds of address space:

- Program memory (ROM)

- Internal register file

A 16-bit address bus supports program memory operations. Special instructions and related internal logic determine when the 16-bit bus carries addresses for program memory. A separate 8-bit register bus carries addresses and data between the CPU and the internal register file.

The S3C94A5 has 16K bytes of mask-programmable program memory on-chip. The S3C94A5/F94A5 microcontroller has 368 bytes general-purpose registers in its internal register file 64 bytes in the register file are mapped for system and peripheral control functions.

ADDRESS SPACES S3C94A5/F94A5

#### PROGRAM MEMORY (ROM)

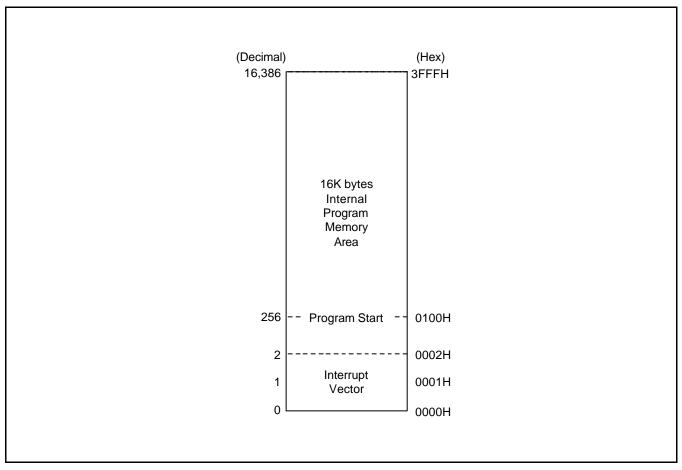

Program memory (ROM) stores program code or table data. The S3C94A5 has 16K bytes of mask-programable program memory. The program memory address range is therefore 0H-3FFFH. The first 2 bytes of the ROM (0000H–0001H) are an interrupt vector address. The program reset address in the ROM is 0100H.

Figure 2-1. S3C94A5/F94A5 Program Memory Address Space

S3C94A5/F94A5 ADDRESS SPACES

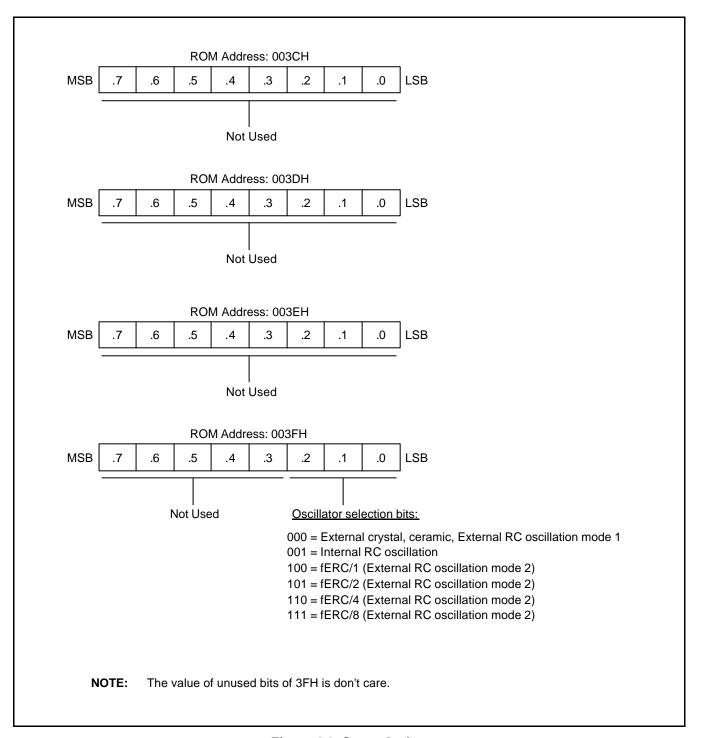

#### **SMART OPTION**

Smart option is the ROM option for starting condition of the chip. The ROM addresses used by smart option are from 003CH to 003FH. The S3C94A5 only use 003FH and ROM address 003CH, 003DH, 003EH is not used.

For example, if you program as below:

ORG 003FH

DB 01H ; Select internal RC oscillation

If you don't program any values in these option areas, then the default value is "1".

In these cases, the address 003CH, 003DH, 003EH would be the value of "FFH".

ADDRESS SPACES S3C94A5/F94A5

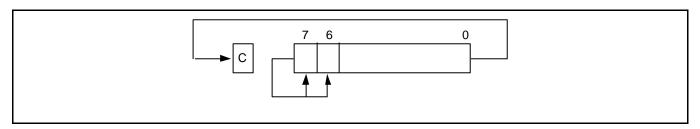

Figure 2-2. Smart Option

S3C94A5/F94A5 ADDRESS SPACES

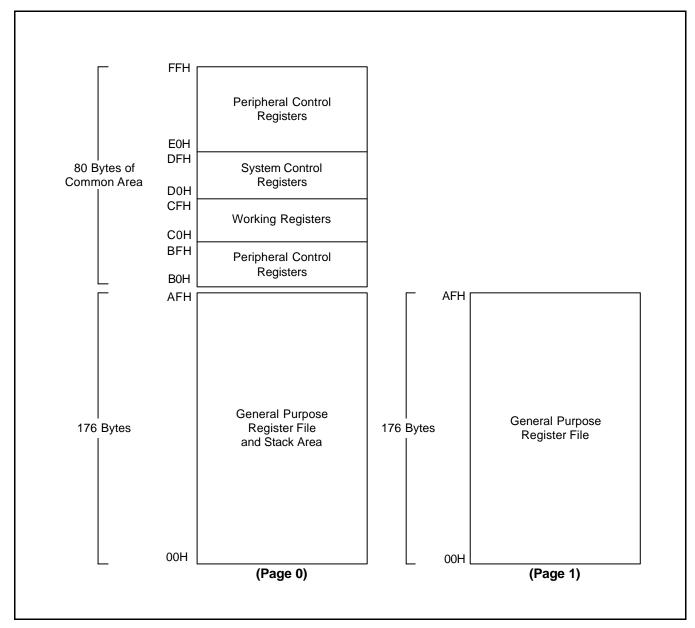

#### REGISTER ARCHITECTURE

The upper 80 bytes of the S3C94A5/F94A5's internal register file are addressed as working registers, system control registers and peripheral control registers. The lower 176 bytes of internal register file (00H–AFH) is called the general purpose register space.

For many SAM88RCRI microcontrollers, the addressable area of the internal register file is further expanded by the additional of one or more register pages at general purpose register space (00H–BFH). This register file expansion is implemented by page 1 in the S3C94A5/F94A5.

Figure 2-3. Internal Register File Organization

ADDRESS SPACES S3C94A5/F94A5

#### COMMON WORKING REGISTER AREA (C0H-CFH)

The SAM88RCRI register architecture provides an efficient method of working register addressing that takes full advantage of shorter instruction formats to reduce execution time.

This16-byte address range is called common area. That is, locations in this area can be used as working registers by operations that address any location on any page in the register file. Typically, these working registers serve as temporary buffers for data operations between different pages.

The Register (R) addressing mode can be used to access this area

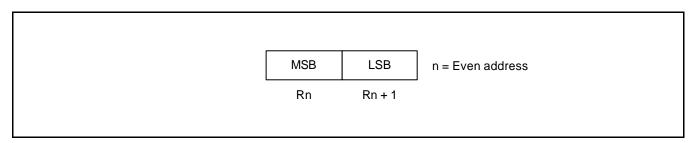

Registers are addressed either as a single 8-bit register or as a paired 16-bit register. In 16-bit register pairs, the address of the first 8-bit register is always an even number and the address of the next register is an odd number. The most significant byte of the 16-bit data is always stored in the even-numbered register; the least significant byte is always stored in the next (+ 1) odd-numbered register.

Figure 2-4. 16-Bit Register Pairs

#### PROGRAMMING TIP — Addressing the Common Working Register Area

As the following examples show, you should access working registers in the common area, locations C0H–CFH, using working register addressing mode only.

Examples: 1. LD 0C2H,40H ; Invalid addressing mode!

Use working register addressing instead:

LD R2,40H ; R2 (C2H)  $\leftarrow$  the value in location 40H

2. ADD 0C3H,#45H ; Invalid addressing mode!

Use working register addressing instead:

ADD R3,#45H ; R3 (C3H)  $\leftarrow$  R3 + 45H

S3C94A5/F94A5 ADDRESS SPACES

#### SYSTEM STACK

S3C9-series microcontrollers use the system stack for subroutine calls and returns and to store data. The PUSH and POP instructions are used to control system stack operations. The S3C94A5/F94A5 architecture supports stack operations in the internal register file.

#### STACK OPERATIONS

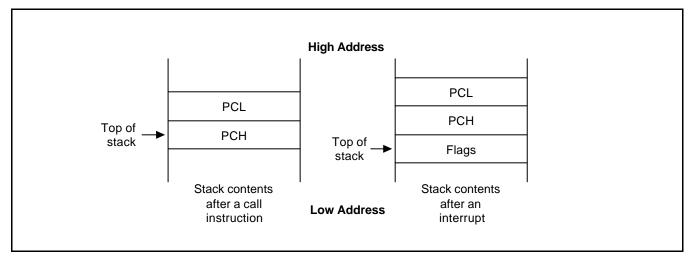

Return addresses for procedure calls and interrupts and data are stored on the stack. The contents of the PC are saved to stack by a CALL instruction and restored by the RET instruction. When an interrupt occurs, the contents of the PC and the FLAGS register are pushed to the stack. The IRET instruction then pops these values back to their original locations. The stack address is always decremented before a push operation and incremented after a pop operation. The stack pointer (SP) always points to the stack frame stored on the top of the stack, as shown in Figure 2-5.

Figure 2-5. Stack Operations

#### STACK POINTER (SP)

Register location D9H contains the 8-bit stack pointer (SP) that is used for system stack operations. After a reset, the SP value is undetermined.

Because only internal memory space is implemented in the S3C94A5/F94A5, the SP must be initialized to an 8-bit value in the range 00H–B7H.

#### **NOTE**

In case a Stack Pointer is initialized to 00H, it is decreased to FFH when stack operation starts. This means that a Stack Pointer access invalid stack area.

**ADDRESS SPACES** S3C94A5/F94A5

#### PROGRAMMING TIP — Standard Stack Operations Using PUSH and POP

The following example shows you how to perform stack operations in the internal register file using PUSH and POP instructions:

> ; SP  $\leftarrow$  B8H (Normally, the SP is set to 0B8H by the LD SP,#0B8H ; initialization routine) PUSH SYM ; Stack address 0B7H  $\leftarrow$  SYM ; Stack address 0B6H  $\leftarrow$  WTCON PUSH WTCON PUSH ; Stack address  $0B5H \leftarrow 20H$ 20H

> > Stack address 0B4H ← R3

PUSH R3

POP R3 ; R3 ← Stack address 0B4H 20H 20H ← Stack address 0B5H POP POP WTCON WTCON ← Stack address 0B6H ; SYM ← Stack address 0B7H POP SYM

S3C94A5/F94A5 ADDRESSING MODES

3

### **ADDRESSING MODES**

#### **OVERVIEW**

Instructions that are stored in program memory are fetched for execution using the program counter. Instructions indicate the operation to be performed and the data to be operated on. Addressing mode is the method used to determine the location of the data operand. The operands specified in SAM88RCRI instructions may be condition codes, immediate data, or a location in the register file, program memory, or data memory.

The SAM88RCRI instruction set supports six explicit addressing modes. Not all of these addressing modes are available for each instruction. The addressing modes and their symbols are as follows:

- Register (R)

- Indirect Register (IR)

- Indexed (X)

- Direct Address (DA)

- Relative Address (RA)

- Immediate (IM)

ADDRESSING MODES S3C94A5/F94A5

#### REGISTER ADDRESSING MODE (R)

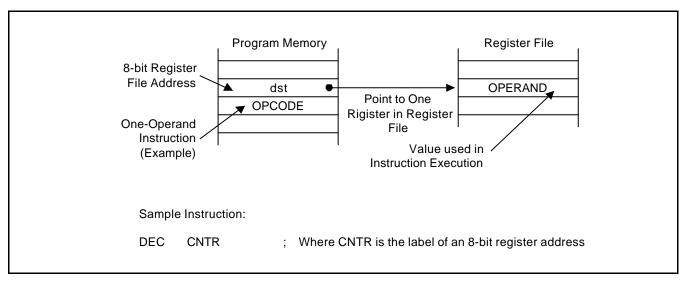

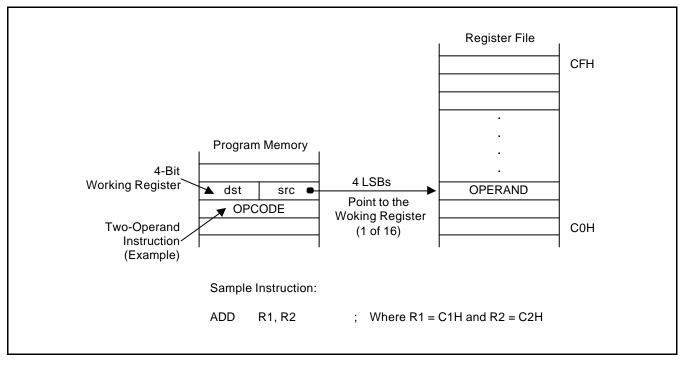

In Register addressing mode, the operand is the content of a specified register (see Figure 3-1). Working register addressing differs from Register addressing because it uses a 16-byte working register space in the register file and a 4-bit register within that space (see Figure 3-2).

Figure 3-1. Register Addressing

Figure 3-2. Working Register Addressing

S3C94A5/F94A5 ADDRESSING MODES

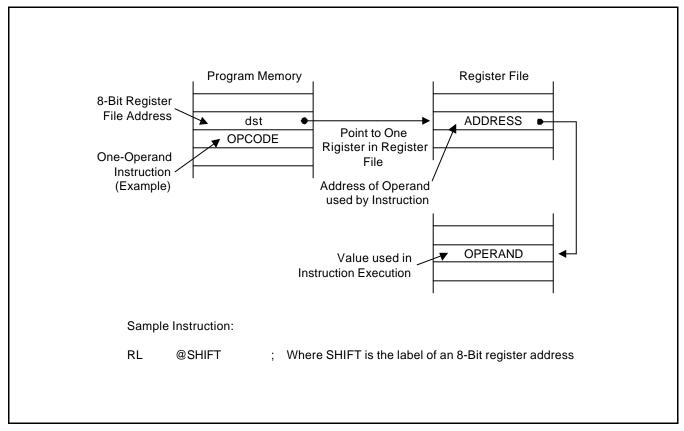

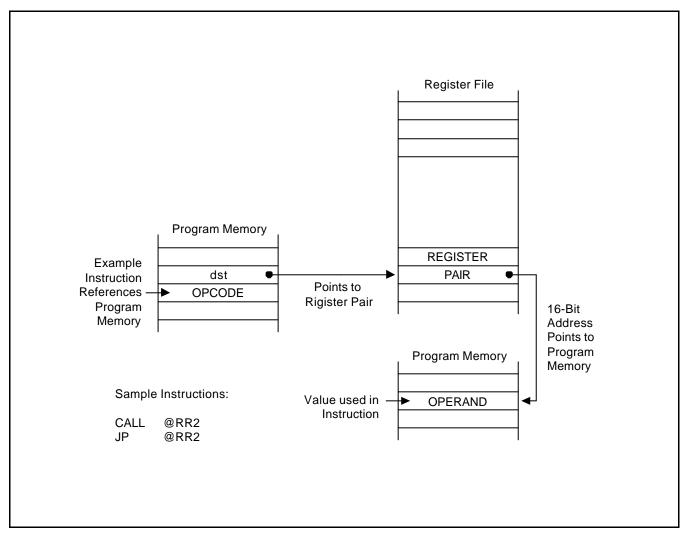

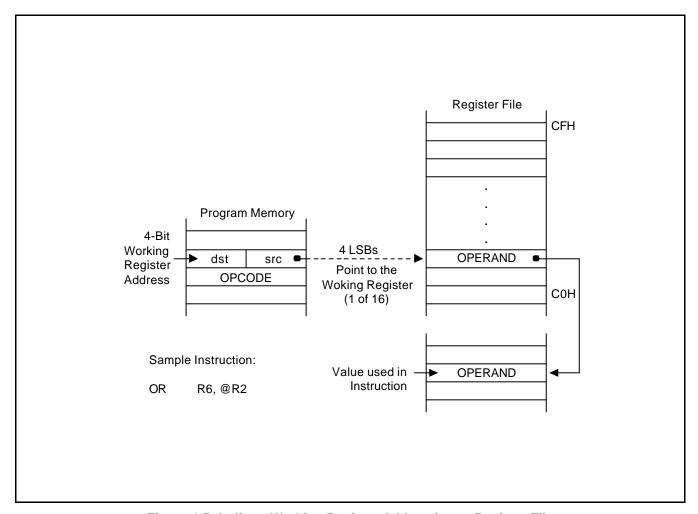

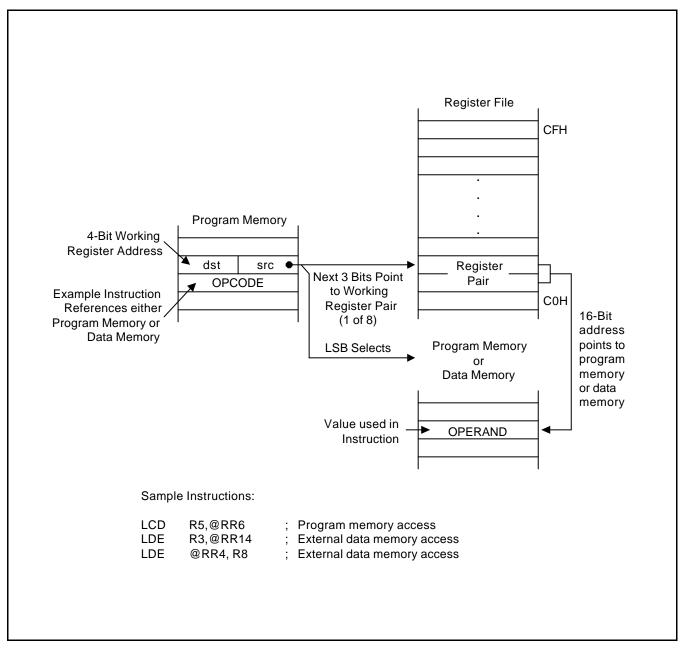

#### **INDIRECT REGISTER ADDRESSING MODE (IR)**

In Indirect Register (IR) addressing mode, the content of the specified register or register pair is the address of the operand. Depending on the instruction used, the actual address may point to a register in the register file, to program memory (ROM), or to an external memory space (see Figures 3-3 through 3-6).

You can use any 8-bit register to indirectly address another register. Any 16-bit register pair can be used to indirectly address another memory location.

Figure 3-3. Indirect Register Addressing to Register File

ADDRESSING MODES S3C94A5/F94A5

#### **INDIRECT REGISTER ADDRESSING MODE (Continued)**

Figure 3-4. Indirect Register Addressing to Program Memory

S3C94A5/F94A5 ADDRESSING MODES

#### **INDIRECT REGISTER ADDRESSING MODE (Continued)**

Figure 3-5. Indirect Working Register Addressing to Register File

ADDRESSING MODES S3C94A5/F94A5

#### **INDIRECT REGISTER ADDRESSING MODE (Concluded)**

Figure 3-6. Indirect Working Register Addressing to Program or Data Memory

S3C94A5/F94A5 ADDRESSING MODES

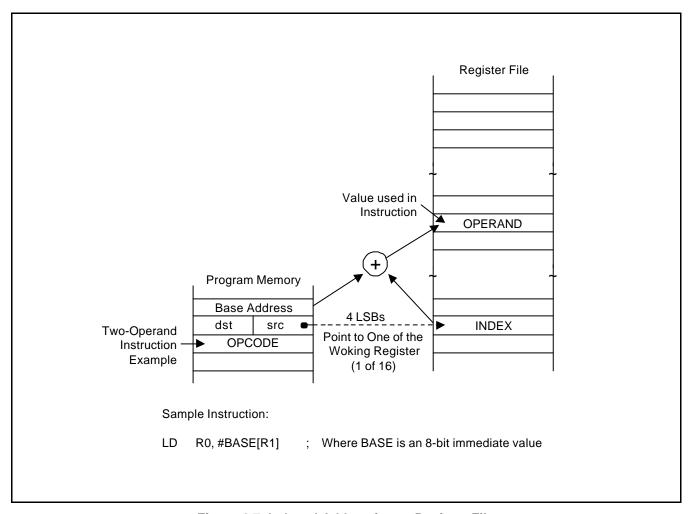

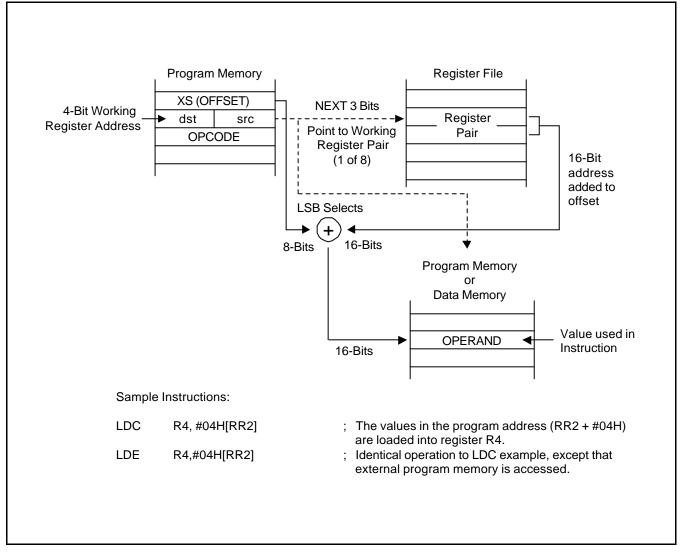

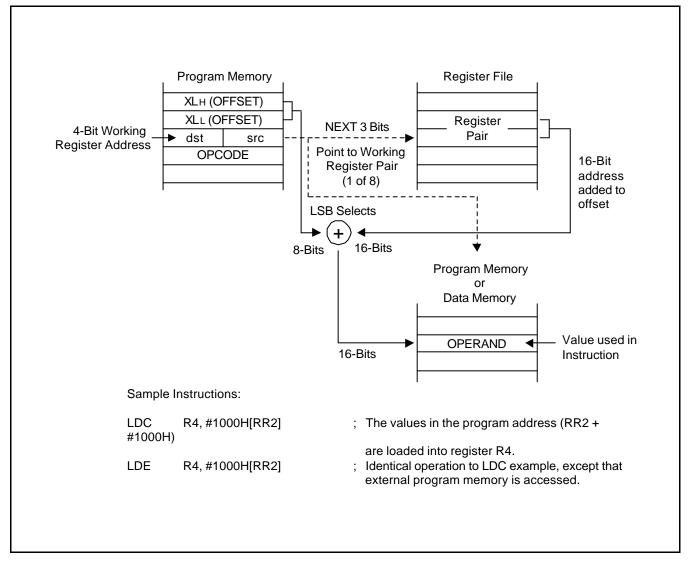

#### **INDEXED ADDRESSING MODE (X)**

Indexed (X) addressing mode adds an offset value to a base address during instruction execution in order to calculate the effective operand address (see Figure 3-7). You can use Indexed addressing mode to access locations in the internal register file or in external memory.

In short offset Indexed addressing mode, the 8-bit displacement is treated as a signed integer in the range of -128 to +127. This applies to external memory accesses only (see Figure 3-8).

For register file addressing, an 8-bit base address provided by the instruction is added to an 8-bit offset contained in a working register. For external memory accesses, the base address is stored in the working register pair designated in the instruction. The 8-bit or 16-bit offset given in the instruction is then added to the base address (see Figure 3-9).

The only instruction that supports Indexed addressing mode for the internal register file is the Load instruction (LD). The LDC and LDE instructions support Indexed addressing mode for internal program memory, external program memory, and for external data memory, when implemented.

Figure 3-7. Indexed Addressing to Register File

ADDRESSING MODES S3C94A5/F94A5

#### **INDEXED ADDRESSING MODE (Continued)**

Figure 3-8. Indexed Addressing to Program or Data Memory with Short Offset

S3C94A5/F94A5 ADDRESSING MODES

#### **INDEXED ADDRESSING MODE (Concluded)**

Figure 3-9. Indexed Addressing to Program or Data Memory with Long Offset

ADDRESSING MODES S3C94A5/F94A5

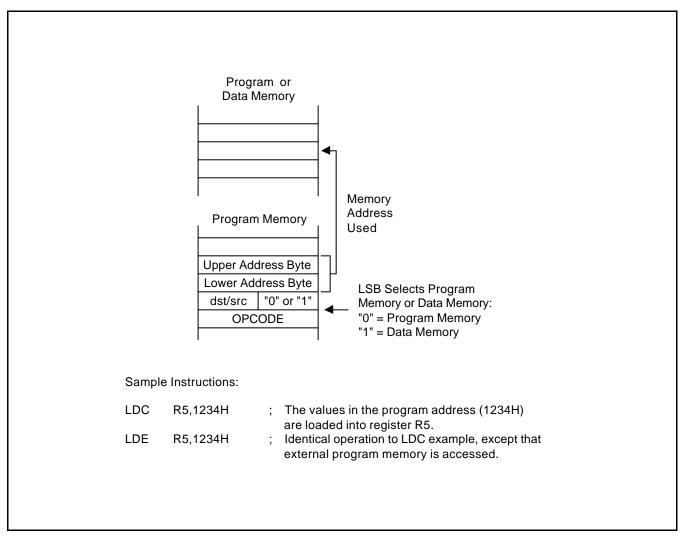

#### **DIRECT ADDRESS MODE (DA)**

In Direct Address (DA) mode, the instruction provides the operand's 16-bit memory address. Jump (JP) and Call (CALL) instructions use this addressing mode to specify the 16-bit destination address that is loaded into the PC whenever a JP or CALL instruction is executed.

The LDC and LDE instructions can use Direct Address mode to specify the source or destination address for Load operations to program memory (LDC) or to external data memory (LDE), if implemented.

Figure 3-10. Direct Addressing for Load Instructions

S3C94A5/F94A5 ADDRESSING MODES

#### **DIRECT ADDRESS MODE (Continued)**

Figure 3-11. Direct Addressing for Call and Jump Instructions

ADDRESSING MODES S3C94A5/F94A5

#### **RELATIVE ADDRESS MODE (RA)**

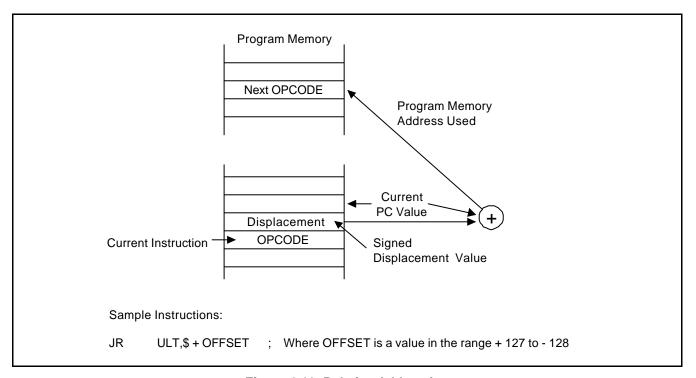

In Relative Address (RA) mode, a two's-complement signed displacement between - 128 and + 127 is specified in the instruction. The displacement value is then added to the current PC value. The result is the address of the next instruction to be executed. Before this addition occurs, the PC contains the address of the instruction immediately following the current instruction.

The instructions that support RA addressing is JR.

Figure 3-12. Relative Addressing

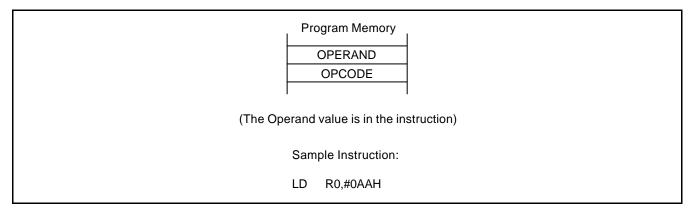

#### **IMMEDIATE MODE (IM)**

In Immediate (IM) addressing mode, the operand value used in the instruction is the value supplied in the operand field itself. Immediate addressing mode is useful for loading constant values into registers.

Figure 3-13. Immediate Addressing

## **CONTROL REGISTERS**

#### **OVERVIEW**

In this section, detailed descriptions of the S3C94A5/F94A5 control registers are presented in an easy-to-read format. These descriptions will help familiarize you with the mapped locations in the register file. You can also use them as a quick-reference source when writing application programs.

System and peripheral registers are summarized in Table 4-1. Figure 4-1 illustrates the important features of the standard register description format.

Control register descriptions are arranged in alphabetical order according to register mnemonic. More information about control registers is presented in the context of the various peripheral hardware descriptions in Part II of this manual.

Table 4-1. System and Peripheral Control Registers

| Register Name                           | Mnemonic              | Add        | lress | R/W |

|-----------------------------------------|-----------------------|------------|-------|-----|

|                                         |                       | Decimal    | Hex   | 1   |

| Loca                                    | tions B0H — B3H are   | not mapped | -     | -   |

| Timer 0 control register                | T0CON                 | 196        | В4Н   | R/W |

| Timer 0 data register (high byte)       | T0DATAH               | 197        | B5H   | R/W |

| Timer 0 data register (low byte)        | TODATAL               | 198        | В6Н   | R/W |

| Timer 0 counter (high byte)             | T0CNTH                | 199        | В7Н   | R   |

| Timer 0 counter (low byte)              | T0CNTL                | 200        | В8Н   | R   |

| Timer 1 control resistor                | T1CON                 | 201        | В9Н   | R/W |

| Timer 1 data register (high byte)       | T1DATAH               | 202        | BAH   | R/W |

| Timer 1 data register (low byte)        | T1DATAL               | 203        | BBH   | R/W |

| Timer 1 counter (high byte)             | T1CNTH                | 204        | BCH   | R   |

| Timer 1 counter (low byte)              | T1CNTL                | 205        | BDH   | R   |

| Timer 2 control register                | T2CON                 | 206        | BEH   | R/W |

| Timer 2 data register                   | T2DATA                | 207        | BFH   | R/W |

| Timer 2 counter                         | T2CNT                 | 208        | D0H   | R   |

| A/D converter control register          | ADCON                 | 209        | D1H   | R/W |

| A/D converter data register (high byte) | ADDATAH               | 210        | D2H   | R   |

| A/D converter data register (low byte)  | ADDATAL               | 211        | D3H   | R   |

| System clock control register           | CLKCON                | 212        | D4H   | R/W |