## RC288DPi and RC288DPL V.34 Data/V.17 Fax/Voice Modem Data Pumps

## INTRODUCTION

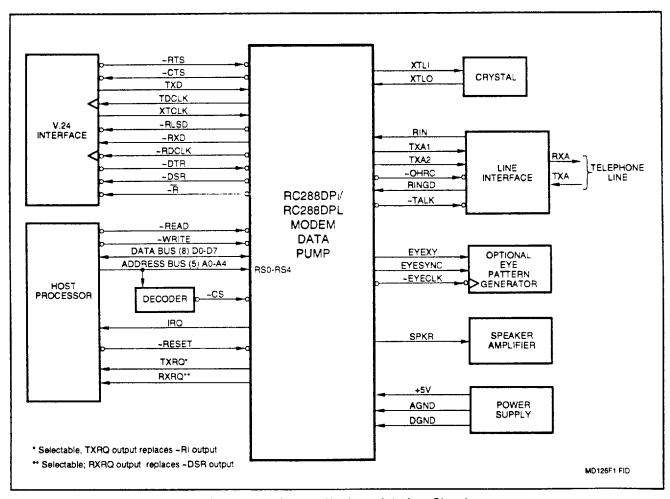

The Rockwell RC288DPi and RC288DPL are V.34 modem data pump families that support data rates up to 28800 bps, fax operation up to 14400 bps, and voice coding/decoding. The following models are available:

| Model                 | Data      | Fax       | Voice |

|-----------------------|-----------|-----------|-------|

| RC288DPi-D/RC288DPL-D | 28.8 kbps | None      | No    |

| RC288DPVRC288DPL      | 28.8 kbps | 14.4 kbps | No    |

| RCV288DPi/RCV288DPL   | 28.8 kbps | 14.4 kbps | Yes   |

As a data modem, the modem can operate in 2-wire, full-duplex, synchronous/asynchronous modes at rates up to 28800 bps. Using V.34 techniques to optimize modem configuration for line conditions, the modem can connect at the highest data rate that the channel can support from 28800 bps to 2400 bps with automatic fallback to V.Fast Class<sup>™</sup> (V.FC<sup>™</sup>) or V.32 bis. Automode operation in V.32 bis is provided per EIA/TIA-PN2330.

Internal HDLC support eliminates the need for an external serial input/output (SIO) device in the DTE for products incorporating error correction and T.30 protocols.

Facsimile models support Group 3 facsimile send and receive speeds up to 14400 bps.

Voice models include a voice pass-through mode which allows the host to transmit and receive uncompressed audio signals. These models also include an Adaptive Differential Pulse Code Modulation (ADPCM) voice coder and decoder (codec). The codec compresses and decompresses voice signals to allow efficient digital storage of voice messages. The codec operates at 28.8k, 21.6k, or 14.4k bps (4-bit, 3-bit, or 2-bit quantization, respectively) with a default 7.2 kHz programmable sample rate. Optional coder silence detection/deletion and decoder silence interpolation are included to achieve greater compression rates.

The modem operates over the public switched telephone network (PSTN) through the appropriate line termination.

The RC288DPL offers lower power consumption and small footprint, low profile PQFP and TQFP packages meeting PCMCIA Type II envelope requirements for PCMCIA PC Cards and battery-powered portable applications such as notebook and subnotebook computers.

Additional information is provided in the RC288DPi Modem Designer's Guide (Order No. 1026).

V.Fast Class and V.FC are trademarks of Rockwell International.

#### **FEATURES**

- · 2-wire full-duplex

- V.34, V.FC, V.32 bis, V.32, V.22 bis, V.22, V.23, and V.21

- Bell 212 and 103

- · 2-wire half-duplex

- V.17, V.33, V.29, V.27 ter, V.26 bis,

V.26 Alternative A, and V.21 channel 2

- Bell 208

- Short train option in V.17 and V.27 ter

- · Serial synchronous and asynchronous data

- · Parallel synchronous and asynchronous data

- · Parallel synchronous SDLC/HDLC support

- In-band secondary channel (V.FC and V.32 bis)

- · Automatic mode selection (AMS)

- Automatic rate adaption (ARA)

- · Digital near-end and far-end echo cancellation

- · Bulk delay for satellite transmission

- · Auto-dial and auto-answer

- · TTL and CMOS compatible DTE interface

- CCITT V.24 (EIA/TIA-232-E) (data/control)

- Microprocessor bus (data/configuration/control)

- Dynamic range: -43 dBm to -9 dBm

- · Voice pass-through mode

- ADPCM voice mode (optional)

- Adjustable speaker output to monitor received signal

- DMA support interrupt lines

- Two 16-byte FiFO data buffers for burst data transfer

- · NRZI encoding/decoding

- · 511 pattern generation/detection

- · Diagnostic capability

- V.8 signaling

- V.13 signaling

- · V.54 inter-DCE signaling

- V.54 local analog and remote digital loopback

- +5V operation

- Typical power consumption:

| Modem    | Normal Mode | Sleep Mode |

|----------|-------------|------------|

| RC288DPL | 620 mW      | 9 mW       |

| RC288DPi | 980 mW      | 200 mW     |

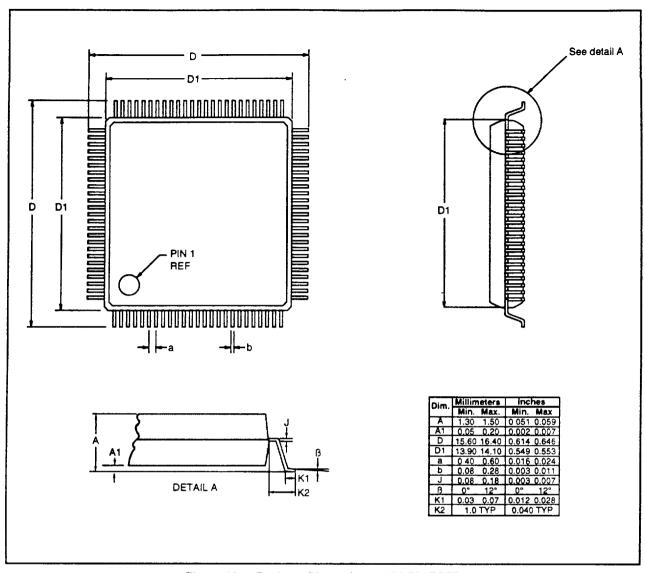

- · Flexible packaging options

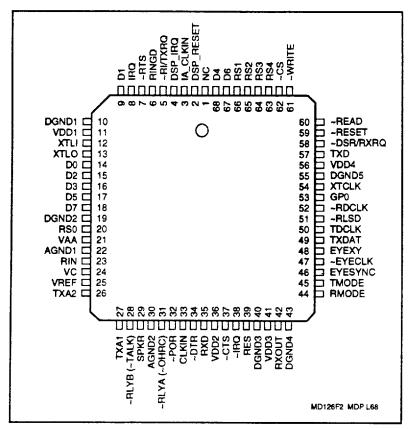

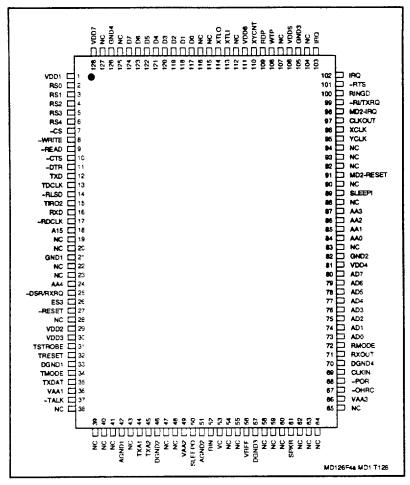

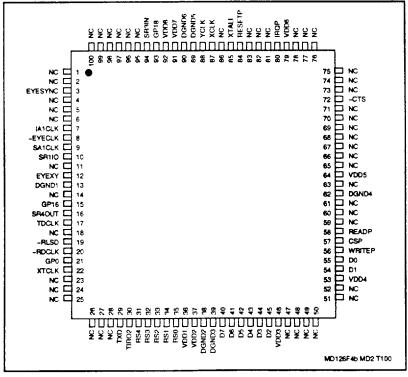

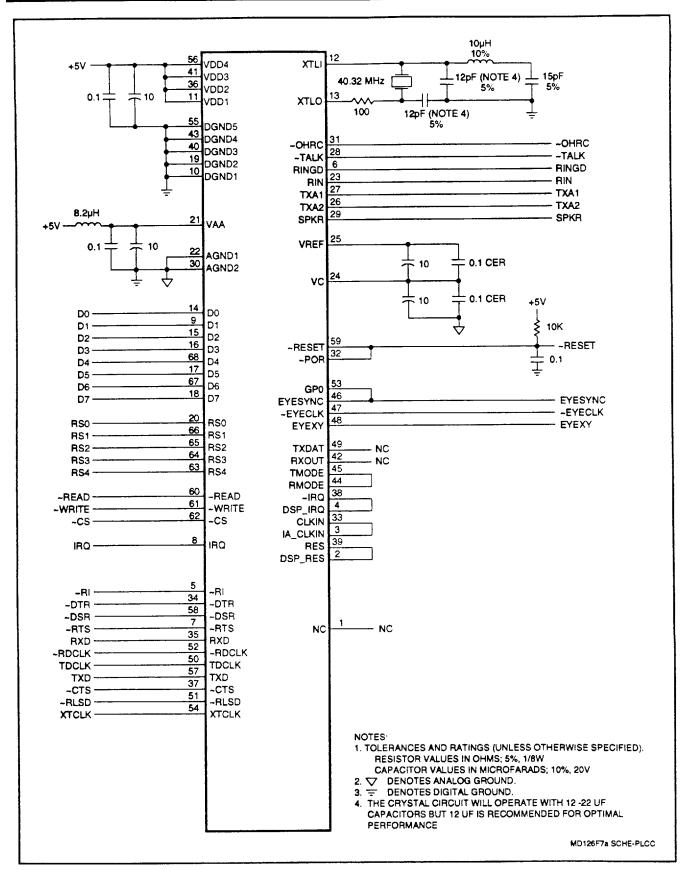

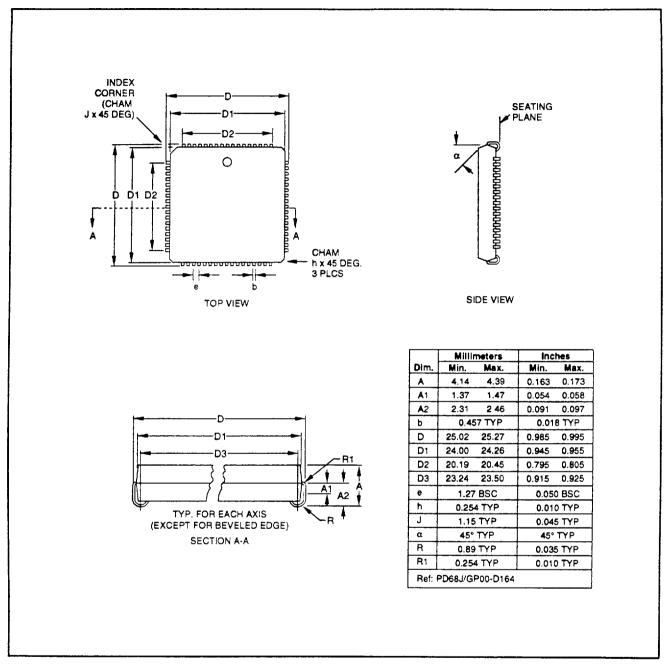

- One 68-pin PLCC package, or

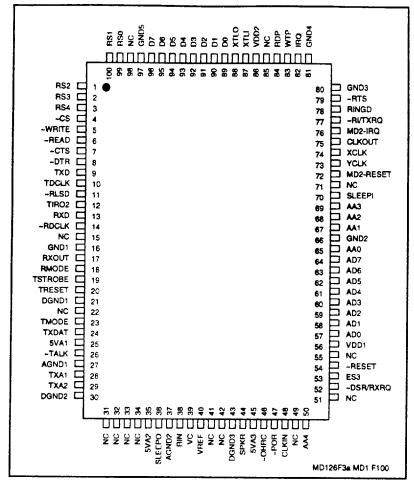

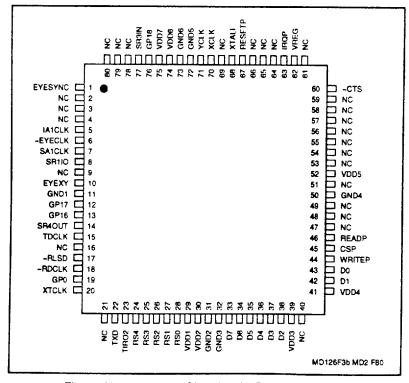

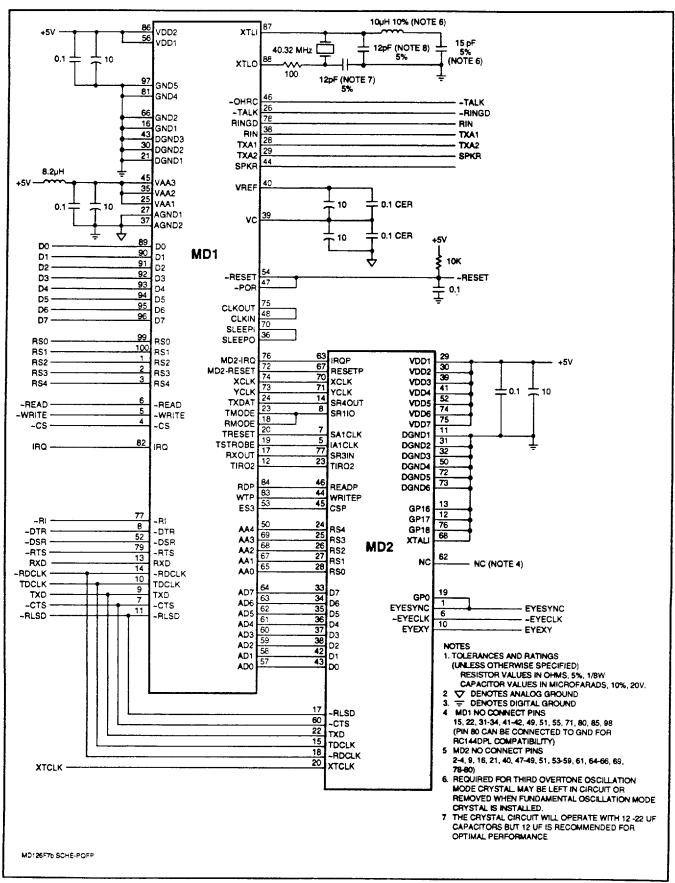

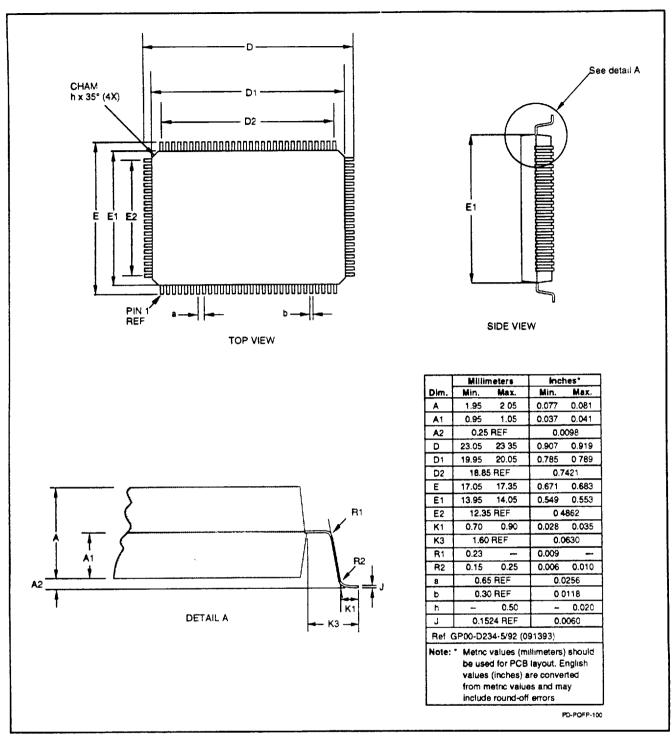

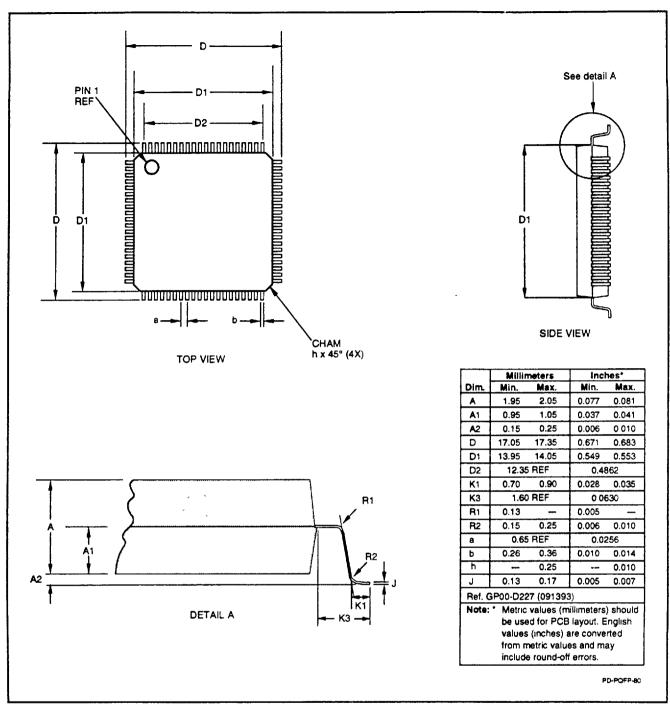

- One 100-pin PQFP and one 80-pin PQFP, or

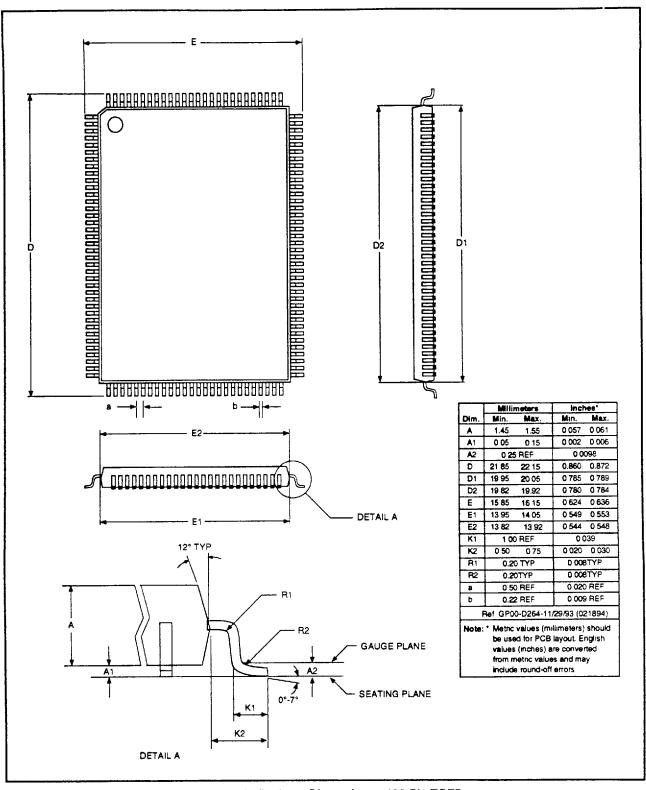

- One 128-pin TQFP and one 100-pin TQFP

Data Sheet (Preliminary)

Order No. MD126 Rev. 2, October 24, 1994 (Supersedes earlier issues)

## **TECHNICAL DESCRIPTION**

#### Configurations and Rates

The selectable modem configurations, signaling rates, and data rates are listed in Table 1.

#### **Automatic Mode Selection**

When automatic mode selection (AMS) is enabled, the modem configures itself to the highest compatible data rate supported by the remote modem (AUTO bit). Automode operation in V.32 bis, V.32 V.22 bis, V.22, V.21, V.23, Bell 212A, and Bell 103 modes is in accordance with EIA/TIA-PN2330.

**NOTE:** Bit names refer to data, control, and/or status bits in the modem interface memory (see Table 9).

## **Automatic Rate Adaption (ARA)**

In V.34, V.FC, and V.32 bis modes, automatic rate adaption (ARA) can be enabled to select the highest data rate possible based on the measured eye quality monitor (EQM) (EARC bit). This selection occurs during handshake/retrain and rate renegotiation.

#### **Tone Generation**

The modem can generate single or dual voice-band tones from 0 Hz to 3600 Hz with a resolution of 0.15 Hz and an accuracy of  $\pm$  0.01%. Tones over 3000 Hz are attenuated. DTMF tone generation allows the modem to operate as a programmable DTMF dialer.

## **Data Encoding**

The data encoding conforms to CCITT recommendations V.34, V.32 bis, V.32, V.17, V.33, V.29, V.27 ter, V.26 bis, V.26 Alternative A, V.22 bis, V.22, V.23, or V.21, and is compatible with V.FC, Bell 208, 212A, or 103, depending on the configuration.

#### Transmitted Data Spectrum

The transmitter spectrum is shaped by raised cosine filter functions as follows:

| Configuration                                   | Raised Cosine<br>Filter Function |

|-------------------------------------------------|----------------------------------|

| V.34, V.FC, V.32 bis, V.32, V.17,<br>V.33, V.29 | Square root of 12.5%             |

| V.27 ter, V.26, Bell 208                        | Square root of 50%               |

| V.22 bis/V.22, Bell 212A                        | Square root of 75%               |

#### RTS - CTS Response Time

The response times of CTS relative to a corresponding transition of RTS are listed in Table 2.

#### Transmit Level

The transmitter output level is selectable from 0 dBm to -15 dBm in 1 dB steps and is accurate to ±0.5 dB when used with an external hybrid. The output level can also be fine tuned by changing a gain constant in modem DSP RAM. The maximum V.34/V.FC/V.32 bis/V.32 transmit level for acceptable receive performance should not exceed -9 dBm.

**Note:** In V.34 and V.FC modes, the transmit level may be automatically changed during the handshake. This automatic adjustment of the transmit level may be disabled via a parameter in DSP RAM.

#### **Transmitter Timing**

Transmitter timing is selectable between internal (±0.01%), external, or slave.

#### Scrambler/Descrambler

A self-synchronizing scrambler/descrambler is used in accordance with the selected configuration.

#### **Answer Tone**

The modem generates a 2100 Hz answer tone for 3.6 seconds at the beginning of the answer handshake when the NV25 bit is a zero (V.8, V.FC, V.32 bis, V.32, V.22 bis, V.22, V.23, and V.21). The answer tone has 180° phase reversals every 0.45 second to disable network echo cancellers (V.8, V.FC, V.32 bis, V.32).

#### Receive Level

The modem satisfies performance requirements for received line signal levels from -9 dBm to -43 dBm measured at the Receiver Analog (RXA) (TIP and RING) input (-15 dBm at RIN).

Note: A 6 dB pad is required between TIP and RING and the RIN input.

#### Receiver Timing

The timing recovery circuit can track a frequency error in the associated transmit timing source of  $\pm 0.035\%$  (V.22 bis) or  $\pm 0.01\%$  (other configurations).

#### **Carrier Recovery**

The carrier recovery circuit can track a  $\pm 7$  Hz frequency offset in the received carrier.

#### Clamping

Received Data (RXD) is clamped to a constant mark whenever the Received Line Signal Detector (~RLSD) is off. ~RLSD can be clamped off (RLSDE bit).

#### **Echo Canceller**

A data echo canceller with near-end and far-end echo cancellation is included for 2-wire full-duplex V.34/V.FC/V.32 bis/V.32 operation. The combined echo span of near and far cancellers can be up to 40 ms. The proportion allotted to each end is automatically determined by the modem. The delay between near-end and far-end echoes can be up to 1.2 seconds.

#### **ADPCM Voice Mode**

**Transmit Voice.** 16-bit compressed transmit voice can be sent to the modern ADPCM codec for decompression then to the digital-to-analog converter (DAC) by the host.

Receive Voice. 16-bit received voice samples from the modem analog-to-digital converter (ADC) can be sent to the ADPCM codec for compression, and then be read by the host.

#### Voice Pass-Through Mode

**Transmit Voice.** 16-bit transmit voice samples can be sent to the modem DAC from the host.

**Receive Voice.** 16-bit received voice samples from the modern ADC can be read by the host.

2

Table 1. Configurations, Signaling Rates, and Data Rates

| Configuration   Modulation   (Hz) ±0.01%   ±0.01%   (Symbola/Sec.)   Data   TCM   Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |            | Carrier Frequency | Data Rate (bps) | Symbol Rate    | Bits/Symbol - | Bits/Symbol - | Constellation |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------|-------------------|-----------------|----------------|---------------|---------------|---------------|

| V.3.4 24000 TCM         TCM         Note 2         26400         Note 2                                                  | Configuration                    | Modulation | (Hz) ±0.01%       | ±0.01%          | (Symbols/Sec.) |               | TCM           | Points        |

| V.34 24000 TCM         TCM         Note 2         24000         Note 2         No                                        | V.34 28800 TCM                   | TCM        | Note 2            | <b>288</b> 00   | Note 2         | Note 2        | Note 2        | Note 2        |

| V.3.4 19200 TCM         TCM         Note 2         21650         Note 2         N                                        | V.34 26400 TCM                   | TCM        | Note 2            | 26400           | Note 2         | Note 2        | Note 2        | Note 2        |

| V.3.4 18000 TCM         TCM         Note 2         19200         Note 2         N                                        | V.34 24000 TCM                   | тсм        | Note 2            | 24000           | Note 2         | Note 2        | Note 2        | Note 2        |

| V.3.4 14400 TCM         TCM         Note 2         15800         Note 2         N                                        | V.34 21600 TCM                   | TCM        | Note 2            | 21600           | Note 2         | Note 2        | Note 2        | Note 2        |

| V3.4 14000 TCM         TCM         Note 2         14400         Note 2         No                                        | V.34 19200 TCM                   | TCM        | Note 2            | <b>19</b> 200   | Note 2         | Note 2        | Note 2        | Note 2        |

| V3.4 12000 TCM         TCM         Note 2         12000         Note 2         No                                        | V.34 16800 TCM                   | TCM        | Note 2            | 16800           | Note 2         | Note 2        | Note 2        | Note 2        |

| V3.4 BEOD TCM         TCM         Note 2         9600         Note 2         Note                                        | V.34 14400 TCM                   | TCM        | Note 2            | 14400           | Note 2         | Note 2        | Note 2        | Note 2        |

| V.3.4 7200 TCM         TCM         Note 2         Adep 2         Note 2         N                                        | V.34 12000 TCM                   | TCM        | Note 2            | 12000           | Note 2         | Note 2        | Note 2        | Note 2        |

| V.34 4200 TCM         TCM         Note 2         4500 Note 2         <                                    | V.34 9600 TCM                    | TCM        | Note 2            | <b>96</b> 00    | Note 2         | Note 2        | Note 2        |               |

| V.34 2200 TCM         TCM         Note 2         2400         Note 2         Note                                        | V.34 7200 TCM                    | TCM        | Note 2            | 7200            | Note 2         | Note 2        | Note 2        |               |

| V.F.C 28800 TCM         TCM         Note 2         28800         Note 2                                                  | V.34 4800 TCM                    | TCM        | Note 2            | 4800            | Note 2         | Note 2        | Note 2        | · ·           |

| V.F.C 24000 TCM         TCM         Note 2         28400         Note 2         N                                        | V.34 2400 TCM                    | TCM        | Note 2            | 2400            | Note 2         | Note 2        | Note 2        | Note 2        |

| V.F.C 24000 TCM         TCM         Note 2         24000         Note 2         N                                        | V.FC 28800 TCM                   | TCM        | Note 2            | 28800           | Note 2         | Note 2        | Note 2        |               |

| V.F.C 21800 TCM         TCM         Note 2         21600         Note 2                                                  | V.FC 26400 TCM                   | TCM        | Note 2            | 26400           | Note 2         | Note 2        | Note 2        | Note 2        |

| V.F.C 19820 TCM         TCM         Note 2         19200         Note 2         N                                        | V.FC 24000 TCM                   | TCM        | Note 2            | 24000           | Note 2         | Note 2        | Note 2        |               |

| V.F.C 18800 TOM         TCM         Note 2         18800         Note 2         N                                        | V.FC 21600 TCM                   | TCM        | Note 2            | 21600           | Note 2         | Note 2        | Note 2        |               |

| V.FC 14400 TOM         TCM         Note 2         14400         Note 2         Note 3         1         16         4           V.32 bis 4800         CAM         1800         9600         2400         4         1         32         16         16         16         16         16         14         12         32         16         16         16         16         16         18         16         16         18         16         16         18         16         16         18         16         16         18         18         18         18         18         18         18         18         18         18         18         18         18         18         18         18         18         18         18 <t< td=""><td>V.FC 19200 TCM</td><td>TCM</td><td>Note 2</td><td>19200</td><td>Note 2</td><td>Note 2</td><td>Note 2</td><td></td></t<> | V.FC 19200 TCM                   | TCM        | Note 2            | 19200           | Note 2         | Note 2        | Note 2        |               |

| V.32 bis 14400 TCM         TCM         1800         14400         2400         6         1         128           V.32 bis 1200 TCM         TCM         1800         12000         2400         5         1         64           V.32 bis 9600 TCM         TCM         1800         9600         2400         3         1         16           V.32 bis 7200 TCM         TCM         1800         7200         2400         3         1         16           V.32 bis 7200 TCM         TCM         1800         7200         2400         2         0         4           V.32 bis 8400         QAM         1800         9600         2400         4         1         32           V.32 9600 TCM         TCM         1800         9600         2400         4         0         16           V.32 9600 QAM         1800         9600         2400         2         0         4           V.32 6bis 2400         DPSK         1800         2400         1200         2         0         4           V.25 bis 1200         DPSK         1800         2400         1200         2         0         4           V.25 bis 2400         DPSK         1800                                                                                                                                                                                                    | V.FC 16800 TCM                   | I          | I .               |                 | Note 2         | 1             |               |               |

| V.32 bis 12000 TCM         TCM         1800         12000         2400         5         1         64           V.32 bis 9600 TCM         TCM         1800         9600         2400         4         1         32           V.32 bis 7200 TCM         TCM         1800         7200         2400         2         0         4           V.32 bis 4800         QAM         1800         9600         2400         2         0         4           V.32 9600 TCM         TCM         1800         9600         2400         4         1         32           V.32 9600 QAM         1800         9600         2400         4         1         32           V.32 9600 QAM         1800         4800         2400         2         0         4           V.32 4800 QAM         1800         4800         2400         1200         2         0         4           V.26 bis 1200         DPSK         1800         2400         1200         2         0         4           V.22 bis 1200         DPSK         1800         2400         1200         2         0         4           V.22 bis 1200         DPSK 1200/2400         1200         600                                                                                                                                                                                                      | V.FC 14400 TCM                   | TCM        | Note 2            | 14400           | Note 2         | Note 2        | Note 2        | Note 2        |

| V.32 bis 9600 TCM         TCM         1800         9600         2400         4         1         32           V.32 bis 8700 TCM         TCM         1800         7200         2400         2         0         4           V.32 9600 TCM         TCM         1800         4800         2400         2         0         4           V.32 9600 TCM         TCM         1800         9600         2400         4         1         32           V.32 9600 TCM         TCM         1800         9600         2400         4         1         32           V.32 9800 QAM         1800         9600         2400         2         0         4           V.32 4800 QAM         1800         2400         1200         2         0         4           V.26 bis 2400 DPSK         1800         1200         1200         2         0         4           V.25 bis 2400 DAM         1200/2400         2400         1200         2         0         4           V.22 bis 1200 DPSK         1200/2400         1200         600         2         0         4           V.22 bis 2400 DDPSK         1200/2400         1200         600         2         0         4                                                                                                                                                                                              |                                  |            | j.                | 1               |                |               | 1             |               |

| V.32 bis 7200 TCM         TCM         1800         7200         2400         3         1         16           V.32 bis 4800         QAM         1800         4800         2400         2         0         4           V.32 9800 TCM         TCM         1800         9800         2400         4         1         32           V.32 9800 QAM         QAM         1800         9800         2400         4         0         16           V.32 9800 QAM         QAM         1800         4800         2400         2         0         4           V.32 4800 QDPSK         1800         1200         1200         2         0         4           V.26 bis 2400 QDPSK         1800         1200         1200         1         0         4           V.26 A 2400 QAM         1200/2400 QAM         1200         2         0         4         0         16           V.22 bis 2400 QAM         1200/2400 QAM         2400 GOO         4         0         16         0         4         0         16           V.22 bis 2400 QBK         1200/2400 QAM         1200/2400 GOO         2         0         4         0         16         0         2         0                                                                                                                                                                                           |                                  |            | 1                 | ŧ .             |                |               | E .           |               |

| V.32 bis 4800         QAM         1800         4800         2400         2         0         4           V.32 9600 TCM         TCM         1800         9600         2400         4         1         32           V.32 9600 QAM         1800         9600         2400         4         0         16           V.32 4800 QAM         1800         4800         2400         2         0         4           V.26 bis 2400 DPSK         1800         2400         1200         1         0         4           V.26 bis 1200 DPSK         1800         2400         1200         1         0         4           V.26 bis 1200 DPSK         1800         2400         600         2         0         4           V.22 bis 1200 DPSK         1800         2400         600         2         0         4           V.22 bis 1200 DPSK         1200/2400         2400         600         2         0         4           V.22 1200 DPSK         1200/2400         1200         600         2         0         4           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21 FSK                                                                                                                                                                                                       |                                  |            |                   | 1               |                |               |               |               |

| V.32 9600 TCM         TCM         1800         9600         2400         4         1         32           V.32 9600         QAM         1800         9600         2400         2         0         4           V.32 4800         QAM         1800         9600         2400         2         0         4           V.32 4800         DPSK         1800         2400         1200         2         0         4           V.26 bis 2400         DPSK         1800         1200         1200         2         0         4           V.26 A 2400         DPSK         1800         2400         1200         2         0         4           V.26 A 2400         DPSK         1800         2400         600         4         0         16           V.26 A 2400         DPSK         1800/2400         1200         600         4         0         16           V.22 bis 2400         DPSK         1200/2400         1200         600         2         0         4           V.22 1800         DPSK         1200/2400         1200         600         2         0         4           V.22 1800         DPSK         1200/2400         1200 <td></td> <td></td> <td></td> <td>•</td> <td></td> <td></td> <td></td> <td></td>                                                                                                                           |                                  |            |                   | •               |                |               |               |               |

| V.32 9600         QAM         1800         9600         2400         4         0         16           V.32 4800         QAM         1800         4800         2400         2         0         4           V.26 bis 2400         DPSK         1800         2400         1200         2         0         4           V.26 bis 1200         DPSK         1800         2400         1200         2         0         4           V.22 bis 2400         DPSK         1800         2400         1200         2         0         4           V.22 bis 1200         DPSK         1200/2400         1200         600         4         0         16           V.22 bis 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 1200         DPSK         1200/2400         1200         600         2         0         4           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1080/1750 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                       |                                  |            |                   |                 |                |               |               |               |

| V.32 4800         QAM         1800         4800         2400         2         0         4           V.26 bis 2400         DPSK         1800         2400         1200         2         0         4           V.26 bis 1200         DPSK         1800         2400         1200         2         0         4           V.26 A 2400         DPSK         1800         2400         1200         2         0         4           V.22 bis 2400         QAM         1200/2400         2400         600         4         0         16           V.22 bis 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 1200         DPSK         1200/2400         1200         600         2         0         4           V.21 1         FSK         1700/420         1200/75         1200         1         0         -           V.21 1         FSK         1080/1750         0-300         300         1         0         -           Bell 208 4800         DPSK         1800         4                                                                                                                                                                                                        |                                  | 1          |                   |                 |                | 1             |               |               |

| V.26 bis 2400         DPSK         1800         2400         1200         2         0         4           V.26 bis 1200         DPSK         1800         1200         1200         1         0         4           V.26 A 2400         DPSK         1800         2400         1200         2         0         4           V.22 bis 2400         QAM         1200/2400         2400         600         4         0         16           V.22 bis 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 1200         DPSK         1200/2400         600         600         1         0         -           V.21 FSK         1700/420         1200/75         1200         1         0         -           V.21 FSK         1800         4800         1600         3         0         8           Bell 208 4800         DPSK         1800         4800         1600                                                                                                                                                                                                             | 1 1                              |            | 1                 |                 |                |               |               |               |

| V.26 bis 1200         DPSK         1800         1200         1200         1         0         4           V.26 A 2400         DPSK         1800         2400         1200         2         0         4           V.22 bis 2400         QAM         1200/2400         2400         600         4         0         16           V.25 bis 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 600         DPSK         1200/2400         600         600         1         0         4           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0            V.21         FSK         1080/1750         0-300         300         1         0            Bell 208 4800         DPSK         1800         4800         1600         3         0         8           Bell 103         FSK         1200/2400         1200         600         2         0         4           Bell 103         FSK         1700/420                                                                                                                                                                                                                                 |                                  |            |                   | <u></u>         |                |               |               |               |

| V.26 A 2400         DPSK         1800         2400         1200         2         0         4           V.22 bis 2400         QAM         1200/2400         2400         600         4         0         16           V.22 bis 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 1200         DPSK         1200/2400         600         600         2         0         4           V.22 600         DPSK         1200/2400         600         600         1         0         4           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0            V.21         FSK         1080/1750         0-300         300         1         0            V.21         FSK         1080/1750         4800         1600         3         0         8           Bell 208 4800         DPSK         1200/2400         1200         600         2         0         4           Bell 103         FSK         1700/2125         0-300         300         1         0            V.23 1200/75         FSK         1700/2125                                                                                                                                                                                                                                      |                                  |            |                   |                 | _              | ř.            |               |               |

| V.22 bis 2400         QAM         1200/2400         2400         600         4         0         16           V.22 bis 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 1200         DPSK         1200/2400         600         600         2         0         4           V.22 600         DPSK         1200/2400         600         600         1         0         4           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1700/420         1200         600         2         0         4           Bell 122A         DPSK         1200/2400         1200         600         2         0         4           Bell 103         FSK         1170/2125         0-300         300         1         0         -           V.23 1200/75         FSK         1170/2125         0-300         300         1         0         -           V.21         FSK         1700/420         12                                                                                                                                                                                                        |                                  |            | - ii              | <del></del>     |                |               |               |               |

| V.22 bis 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 600         DPSK         1200/2400         600         600         1         0         4           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0            V.21         FSK         1080/1750         0-300         300         1         0            Bell 208 4800         DPSK         1800         4800         1600         3         0         8           Bell 103         FSK         1200/2400         1200         600         2         0         4           Bell 103         FSK         1170/2125         0-300         300         1         0            V.23 1200/75         FSK         1700/420         1200/75         1200         1         0            V.21         FSK         1700/420         1200/75         1200         1         0            V.21         FSK         1700/420 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                         |                                  |            |                   |                 |                |               |               |               |

| V.22 1200         DPSK         1200/2400         1200         600         2         0         4           V.22 600         DPSK         1200/2400         600         600         1         0         4           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1080/1750         0-300         300         1         0         -           Bell 208 4800         DPSK         1800         4800         1600         3         0         8           Bell 212A         DPSK         1200/2400         1200         600         2         0         4           Bell 103         FSK         1170/2125         0-300         300         1         0         -           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1080/1750         0-300         300         1         0         -           V.17 14400 TCMV.333         TCM         1700 or 1800         14400         2400         6         1         128           V.17 1200 TCM3         TCM         1700 or                                                                                                                                                                                               |                                  |            | 1                 |                 |                |               | t             |               |

| V.22 600         DPSK         1200/2400         600         600         1         0         4           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1080/1750         0-300         300         1         0         -           Bell 208 4800         DPSK         1800         4800         1600         3         0         8           Bell 212A         DPSK         1200/2400         1200         600         2         0         4           Bell 103         FSK         1170/2125         0-300         300         1         0         -           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1080/1750         0-300         300         1         0         -           V.21         FSK         1080/1750         0-300         300         1         0         -           V.21 1 4400 TCMV.333         TCM         1700 or 1800         14400         2400         6         1         128           V.17 12000 TCMV.333         TCM         1700 o                                                                                                                                                                                               |                                  |            | <del></del>       |                 |                |               |               |               |

| V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1080/1750         0-300         300         1         0         -           Bell 208 4800         DPSK         1800         4800         1600         3         0         8           Bell 212A         DPSK         1200/2400         1200         600         2         0         4           Bell 103         FSK         1170/2125         0-300         300         1         0         -           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1700/420         1200/75         1200         1         0         -           V.17 14400 TCMV.33³         TCM         1700 or 1800                                                                                                                                                                                                          |                                  |            | L                 | 1               |                |               | i             |               |

| V.21         FSK         1080/1750         0-300         300         1         0         -           Bell 208 4800         DPSK         1800         4800         1600         3         0         8           Bell 212A         DPSK         1200/2400         1200         600         2         0         4           Bell 103         FSK         1170/2125         0-300         300         1         0         -           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1080/1750         0-300         300         1         0         -           V.21 f 14400 TCMV.33³         TCM         1700 or 1800         14400         2400         6         1         128           V.17 12000 TCMV.33³         TCM         1700 or 1800         12000         2400         5         1         64           V.17 9600 TCM³         TCM         1700 or 1800         9600         2400         4         1         32           V.17 7200 TCM³         TCM         1700 or 1800         7200         2400         3         1         16           V.29 9600³                                                                                                                                                                                               |                                  |            |                   | <del></del>     | <u> </u>       |               |               |               |

| Bell 208 4800         DPSK         1800         4800         1600         3         0         8           Bell 212A         DPSK         1200/2400         1200         600         2         0         4           Bell 103         FSK         1170/2125         0-300         300         1         0         -           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1080/1750         0-300         300         1         0         -           V.17 14400 TCMV.33³         TCM         1700 or 1800         14400         2400         6         1         128           V.17 12000 TCMV.33³         TCM         1700 or 1800         12000         2400         5         1         64           V.17 9600 TCM³         TCM         1700 or 1800         9600         2400         4         1         32           V.17 7200 TCM³         TCM         1700 or 1800         7200         2400         3         1         16           V.29 9600³         QAM         1700         9600         2400         4         0         16           V.29 4800³                                                                                                                                                                                               |                                  |            |                   |                 |                |               |               |               |

| Bell 122A         DPSK         1200/2400         1200         600         2         0         4           Bell 103         FSK         1170/2125         0-300         300         1         0         -           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1080/1750         0-300         300         1         0         -           V.17 14400 TCM/V.33³         TCM         1700 or 1800         14400         2400         6         1         128           V.17 12000 TCM/V.33³         TCM         1700 or 1800         12000         2400         5         1         64           V.17 9600 TCM³         TCM         1700 or 1800         9600         2400         4         1         32           V.17 7200 TCM³         TCM         1700 or 1800         7200         2400         3         1         16           V.29 9600³         QAM         1700         9600         2400         4         0         16           V.29 7200³         QAM         1700         7200         2400         3         0         8           V.29 4800³         QA                                                                                                                                                                                      | V.21                             | FSK        | 1080/1750         | 0-300           | <b>30</b> 0    | 1             | 0             | -             |

| Bell 103         FSK         1170/2125         0-300         300         1         0         -           V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1080/1750         0-300         300         1         0         -           V.17 14400 TCM/V.33³         TCM         1700 or 1800         14400         2400         6         1         128           V.17 12000 TCM/V.33³         TCM         1700 or 1800         12000         2400         5         1         64           V.17 9600 TCM³         TCM         1700 or 1800         9600         2400         4         1         32           V.17 7200 TCM³         TCM         1700 or 1800         7200         2400         3         1         16           V.29 9600³         QAM         1700         9600         2400         3         1         16           V.29 7200³         QAM         1700         7200         2400         3         0         8           V.29 4800³         QAM         1700         4800         2400         2         0         4           V.27 4800³         DPSK </td <td>Bell 208 4800</td> <td>DPSK</td> <td>1800</td> <td><b>48</b>00</td> <td>1<b>6</b>00</td> <td>3</td> <td>0</td> <td>8</td>                                                     | Bell 208 4800                    | DPSK       | 1800              | <b>48</b> 00    | 1 <b>6</b> 00  | 3             | 0             | 8             |

| V.23 1200/75         FSK         1700/420         1200/75         1200         1         0         -           V.21         FSK         1080/1750         0-300         300         1         0         -           V.17 14400 TCM/V.333         TCM         1700 or 1800         14400         2400         6         1         128           V.17 12000 TCM/V.333         TCM         1700 or 1800         12000         2400         5         1         64           V.17 9600 TCM3         TCM         1700 or 1800         9600         2400         4         1         32           V.17 7200 TCM3         TCM         1700 or 1800         7200         2400         3         1         16           V.29 96003         QAM         1700         9600         2400         4         0         16           V.29 72003         QAM         1700         7200         2400         3         0         8           V.29 48003         QAM         1700         4800         2400         2         0         4           V.27 48003         DPSK         1800         4800         1600         3         0         8           V.27 24003         DPSK <td>Bell 212A</td> <td>DPSK</td> <td>1200/2400</td> <td>1200</td> <td>600</td> <td>2</td> <td>0</td> <td>4</td>                                                                          | Bell 212A                        | DPSK       | 1200/2400         | 1200            | 600            | 2             | 0             | 4             |

| V.21         FSK         1080/1750         0-300         300         1         0         -           V.17 14400 TCMV.33³         TCM         1700 or 1800         14400         2400         6         1         128           V.17 12000 TCMV.33³         TCM         1700 or 1800         12000         2400         5         1         64           V.17 9600 TCM³         TCM         1700 or 1800         9600         2400         4         1         32           V.17 7200 TCM³         TCM         1700 or 1800         7200         2400         3         1         16           V.29 9600³         QAM         1700         9600         2400         4         0         16           V.29 7200³         QAM         1700         7200         2400         3         0         8           V.29 4800³         QAM         1700         4800         2400         3         0         8           V.27 4800³         DPSK         1800         4800         1600         3         0         8           V.27 2400³         DPSK         1800         2400         1200         2         0         4           V.21 Channel 2³         FSK                                                                                                                                                                                                | Bell 103                         | FSK        | 1170/2125         | 0-300           | 300            | 1             | 0             | -             |

| V.17 14400 TCMV.33 <sup>3</sup> TCM         1700 or 1800         14400         2400         6         1         128           V.17 12000 TCMV.33 <sup>3</sup> TCM         1700 or 1800         12000         2400         5         1         64           V.17 9600 TCM <sup>3</sup> TCM         1700 or 1800         9600         2400         4         1         32           V.17 7200 TCM <sup>3</sup> TCM         1700 or 1800         7200         2400         3         1         16           V.29 9600 <sup>3</sup> QAM         1700         9600         2400         4         0         16           V.29 7200 <sup>3</sup> QAM         1700         7200         2400         3         0         8           V.29 4800 <sup>3</sup> QAM         1700         4800         2400         2         0         4           V.27 4800 <sup>3</sup> DPSK         1800         4800         1600         3         0         8           V.27 2400 <sup>3</sup> DPSK         1800         2400         1200         2         0         4           V.21 Channel 2 <sup>3</sup> FSK         1750         300         300         1         0         -                                                                                                                                                                                          | V.23 1200/75                     | FSK        | 1700/420          | 1200/75         | 1200           | 1             | 0             | -             |

| V.17 14400 TCMV.33 <sup>3</sup> TCM         1700 or 1800         14400         2400         6         1         128           V.17 12000 TCMV.33 <sup>3</sup> TCM         1700 or 1800         12000         2400         5         1         64           V.17 9600 TCM <sup>3</sup> TCM         1700 or 1800         9600         2400         4         1         32           V.17 7200 TCM <sup>3</sup> TCM         1700 or 1800         7200         2400         3         1         16           V.29 9600 <sup>3</sup> QAM         1700         9600         2400         4         0         16           V.29 7200 <sup>3</sup> QAM         1700         7200         2400         3         0         8           V.29 4800 <sup>3</sup> QAM         1700         4800         2400         2         0         4           V.27 4800 <sup>3</sup> DPSK         1800         4800         1600         3         0         8           V.27 2400 <sup>3</sup> DPSK         1800         2400         1200         2         0         4           V.21 Channel 2 <sup>3</sup> FSK         1750         300         300         1         0         -                                                                                                                                                                                          | V.21                             | FSK        | 1080/1750         | <b>0–30</b> 0   | <b>3</b> 00    | 1             | С             | -             |

| V.17 12000 TCMV.33 <sup>3</sup> TCM         1700 or 1800         12000         2400         5         1         64           V.17 9600 TCM <sup>3</sup> TCM         1700 or 1800         9600         2400         4         1         32           V.17 7200 TCM <sup>3</sup> TCM         1700 or 1800         7200         2400         3         1         16           V.29 9600 <sup>3</sup> QAM         1700         9600         2400         4         0         16           V.29 7200 <sup>3</sup> QAM         1700         7200         2400         3         0         8           V.29 4800 <sup>3</sup> QAM         1700         4800         2400         2         0         4           V.27 4800 <sup>3</sup> DPSK         1800         4800         1600         3         0         8           V.27 2400 <sup>3</sup> DPSK         1800         2400         1200         2         0         4           V.21 Channel 2 <sup>3</sup> FSK         1750         300         300         1         0         -                                                                                                                                                                                                                                                                                                                        | V.17 14400 TCM/V 33 <sup>3</sup> |            |                   | 14400           | 2400           | 6             | 1             | 128           |

| V.17 9600 TCM3         TCM         1700 or 1800         9600         2400         4         1         32           V.17 7200 TCM3         TCM         1700 or 1800         7200         2400         3         1         16           V.29 96003         QAM         1700         9600         2400         4         0         16           V.29 72003         QAM         1700         7200         2400         3         0         8           V.29 48003         QAM         1700         4800         2400         2         0         4           V.27 48003         DPSK         1800         4800         1600         3         0         8           V.27 24003         DPSK         1800         2400         1200         2         0         4           V.21 Channel 23         FSK         1750         300         300         1         0         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |            | 1                 | ì               |                | l .           | i             |               |

| V.17 7200 TCM3         TCM         1700 or 1800         7200         2400         3         1         16           V.29 96003         QAM         1700         9600         2400         4         0         16           V.29 72003         QAM         1700         7200         2400         3         0         8           V.29 48003         QAM         1700         4800         2400         2         0         4           V.27 48003         DPSK         1800         4800         1600         3         0         8           V.27 24003         DPSK         1800         2400         1200         2         0         4           V.21 Channel 23         FSK         1750         300         300         1         0         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  | l          | 1                 |                 |                | l .           | · ·           | li .          |

| V.29 9600 <sup>3</sup> QAM       1700       9600       2400       4       0       16         V.29 7200 <sup>3</sup> QAM       1700       7200       2400       3       0       8         V.29 4800 <sup>3</sup> QAM       1700       4800       2400       2       0       4         V.27 4800 <sup>3</sup> DPSK       1800       4800       1600       3       0       8         V.27 2400 <sup>3</sup> DPSK       1800       2400       1200       2       0       4         V.21 Channel 2 <sup>3</sup> FSK       1750       300       300       1       0       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V 17 7200 TCM3                   |            |                   |                 |                | 1             | 1             |               |

| V.29 7200 <sup>3</sup> QAM         1700         7200         2400         3         0         8           V.29 4800 <sup>3</sup> QAM         1700         4800         2400         2         0         4           V.27 4800 <sup>3</sup> DPSK         1800         4800         1600         3         0         8           V.27 2400 <sup>3</sup> DPSK         1800         2400         1200         2         0         4           V.21 Channel 2 <sup>3</sup> FSK         1750         300         300         1         0         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |            |                   | <b>.</b>        |                |               | <u> </u>      |               |

| V.29 4800 <sup>3</sup> QAM         1700         4800         2400         2         0         4           V.27 4800 <sup>3</sup> DPSK         1800         4800         1600         3         0         8           V.27 2400 <sup>3</sup> DPSK         1800         2400         1200         2         0         4           V.21 Channel 2 <sup>3</sup> FSK         1750         300         300         1         0         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |            |                   |                 |                | 1             | -             |               |

| V.27 4800 <sup>3</sup> DPSK         1800         4800         1600         3         0         8           V.27 2400 <sup>3</sup> DPSK         1800         2400         1200         2         0         4           V.21 Channel 2 <sup>3</sup> FSK         1750         300         300         1         0         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |            |                   | 1               |                | 1             | •             | ] ·           |

| V.27 2400 <sup>3</sup> DPSK         1800         2400         1200         2         0         4           V.21 Channel 2 <sup>3</sup> FSK         1750         300         300         1         0         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                  | L          | 1                 | <del></del>     |                | 1             |               |               |

| V.21 Channel 2 <sup>3</sup> FSK 1750 300 300 1 0 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |            | 1                 | 3               |                | 1             | 1             | i .           |

| **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V.27 2400 <sup>3</sup>           | DPSK       | 1800              | 2400            | 1200           | 2             | 0             | 4             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V.21 Channel 2 <sup>3</sup>      | FSK        | 1750              | 300             | 300            | 1             | 0             | _             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Tone Transmit                    | -          | -                 | -               | -              | _             | -             | -             |

1. Modulation legend: TCM. Treflis-Coded Modulation QAM Quadrature Amplitude Modulation PSK. Frequency Shift Keying DPSK: Differential Phase Shift Keying

2. Adaptive; established during handshake

|                              | Carrier Frequency (Hz) |                  |                   |  |  |  |  |

|------------------------------|------------------------|------------------|-------------------|--|--|--|--|

| Symbol Rate (Baud)           | V.FC                   | V.34 Low Carrier | V.34 High Carrier |  |  |  |  |

| 2400                         | 1800                   | 1600             | 1800              |  |  |  |  |

| <b>280</b> 0                 | 1867                   | 1 <b>6</b> 80    | 1867              |  |  |  |  |

| <b>300</b> 0                 | 1875                   | 1800             | <b>200</b> 0      |  |  |  |  |

| <b>320</b> 0                 | 1920                   | 1829             | 1920              |  |  |  |  |

| <b>342</b> 9                 | 1 <b>9</b> 59          | 1959             | 1 <b>9</b> 59     |  |  |  |  |

| Models with fax support only |                        |                  |                   |  |  |  |  |

#### **Data Formats**

#### Serial Synchronous Data

Data rate: 28800, 26400, 24000, 21600, 19200, 16800,

14400, 12000, 9600, 7200, 4800, 2400,

1200, 600, or 300 bps ±0.01%.

Selectable clock: Internal, external, or slave.

#### Serial Asynchronous Data

Data rate: 28800, 26400, 24000, 21600, 19200, 16800,

14400, 12000, 9600, 7200, 4800, 2400, 1200

or 600 bps +1% (or +2.3%), -2.5%;

0-300 bps (V.21 and Bell 103);

1200/75 bps (V.23).

Bits per character: 7, 8, 9, 10, or 11.

#### Parallel Synchronous Data

Normal sync: 8-bit data for transmit and receive

Data rate: 28800, 26400, 24000, 21600, 19200, 16800,

14400, 12000, 9600, 7200, 4800, 2400,

1200, 600, or 300 bps ±0.01%.

## SDLC/HDLC support:

Transmitter: Flag generation, 0 bit stuffing.

CCITT CRC-16 or CRC-32 generation.

Receiver: Flag detection, 0 bit deletion,

CCITT CRC-16 or CRC-32 checking.

#### Parallel Asynchronous Data

Data rate: 28800, 26400, 24000, 21600, 19200, 16800,

14400, 12000, 9600, 7200, 4800, 2400, 1200

or 600 bps +1% (or 2.3%), -2.5%;

1200, 300, or 75 bps (FSK).

Data bits per character: 5, 6, 7, or 8.

Parity generation/checking: Odd, even, or 9th data bit.

#### Async/Sync and Sync/Async Conversion

An asynchronous-to-synchronous converter is provided in the transmitter and a synchronous-to-asynchronous converter is provided in the receiver. The converters operate in both serial and parallel modes. The asynchronous character format is 1 start bit, 5 to 8 data bits, an optional parity bit, and 1 or 2 stop bits. Valid character size, including all bits, is 7, 8, 9, 10, or 11 bits per character. Two ranges of signaling rates are provided:

- Basic range: +1% to -2.5%

- Extended overspeed range: +2.3% to -2.5%

When the transmitter's converter is operating at the basic signaling rate, no more than one stop bit will be deleted per 8 consecutive characters. When operating at the extended rate, no more than one stop bit will be deleted per 4 consecutive characters. Break handling is performed as described in V.14.

Asynchronous characters are accepted on the TXD serial input and are issued on the RXD serial output.

#### V.54 Inter-DCE Signaling

The modem supports V.54 inter-DCE signaling procedures in synchronous and asynchronous configurations. Transmission and detection of the preparatory, acknowledgment, and termination phases as defined in V.54 are provided. Three control bits in the transmitter allow the host to send the appropriate bit patterns (V54T, V54A, and V54P bits). Three control bits in the receiver are used to enable one of three bit pattern detectors (V54TE, V54AE, and V54PE bits). A status bit indicates when the selected pattern detector has found the corresponding bit pattern (V54DT bit).

## V.13 Remote RTS Signaling

The modem supports V.13 remote RTS signaling. Transmission and detection of signaling bit patterns in response to a change of state in the RTS bit or the ~RTS input signal are provided. The RRTSE bit enables V.13 signaling. The RTSDE bit enables detection of V.13 patterns. The RTSDT status bit indicates the state of the remote RTS signal. This feature may be used to clamp/unclamp the local ~RLSD and RXD signals in response to a change in the remote RTS signal in order to simulate controlled carrier operation in a constant carrier environment. The modem automatically clamps and unclamps ~RLSD.

Table 2. RTS-CTS Response Times

| , abie 2. The of office fillies |                     |                       |                                   |  |  |  |

|---------------------------------|---------------------|-----------------------|-----------------------------------|--|--|--|

|                                 | RTS-CTS             | Response <sup>1</sup> |                                   |  |  |  |

| Configuration                   | Constant<br>Carrier | Controlled<br>Carrier | Turn-Off<br>Sequence <sup>3</sup> |  |  |  |

| V.34, V.FC,<br>V.32 bis, V.32   | ± 2 ms              | N/A                   | N/A                               |  |  |  |

| V.33/V.17 Long                  | N/A                 | 1393 ms <sup>2</sup>  | 15 ms <sup>4</sup>                |  |  |  |

| V.33/V.17 Short                 | N/A                 | 142 ms <sup>2</sup>   | 15 ms <sup>4</sup>                |  |  |  |

| V.29                            | N/A                 | 253 ms <sup>2</sup>   | 12 ms                             |  |  |  |

| V.27 4800 Long                  | N/A                 | 708 ms <sup>2</sup>   | 7 ms <sup>4</sup>                 |  |  |  |

| V.27 4800 Short                 | N/A                 | 50 ms <sup>2</sup>    | 7 ms <sup>4</sup>                 |  |  |  |

| V.27 2400 Long                  | N/A                 | 943 ms <sup>2</sup>   | 10 ms <sup>4</sup>                |  |  |  |

| V.27 2400 Short                 | N/A                 | 67 ms <sup>2</sup>    | 10 ms <sup>4</sup>                |  |  |  |

| V.26                            | N/A                 | 60 ms                 | 10 ms                             |  |  |  |

| V.22 bis, V.22,<br>Bell 212A    | ± 2 ms              | 270 ms                | N/A                               |  |  |  |

| V.21                            | 500 ms              | 500 ms                | N/A                               |  |  |  |

| V.23, Bell 103                  | 210 ms              | 210 ms                | N/A                               |  |  |  |

#### Notes:

- Times listed are CTS turn-on. The CTS OFF-to-ON response time is host programmable in DSP RAM. (Full-duplex modes only.)

- Add echo protector tone duration plus 20 ms when echo protector tone is used during turn-on.

- Turn-off sequence consists of transmission of remaining data and scrambled ones for controlled carner operation. CTS turn-off is less than 2 ms for all configurations.

- Plus 20 ms of no transmitted energy.

- 5. N/A = not applicable.

#### Auto-Dialing and Auto-Answering Control

The host can perform auto-dialing and auto-answering. These functions include DTMF or pulse dialing, ringing detection, and a comprehensive supervisory tone detection scheme. The major parameters are host programmable.

#### **Supervisory Tone Detection**

Three parallel tone detectors (A, B, and C) are provided for supervisory tone detection. The signal path to these detectors is separate from the main received signal path.

Each tone detector consists of two cascaded second order IIR biquad filters. The coefficients are host programmable. Each fourth order filter is followed by a level detector which has host programmable turn-on and turn-off thresholds allowing hysteresis. Tone detector C is preceded by a prefilter and squarer. This circuit is useful for detecting a tone with frequency equal to the difference between two tones that may be simultaneously present on the line. The squarer may be disabled by the SQDIS bit causing tone detector C to be an eighth order filter. The tone detectors are disabled in data mode.

The tone detection sample rate is 9600 Hz in V.8, V.34, and V.FC modes and is 7200 Hz in non-V.34/V.FC modes. The default call progress filter coefficients are based on a 7200 Hz sampling rate and apply to non-V.34/V.FC modes only. The maximum detection bandwidth is equal to one-half the sample rate.

#### Supervisory Tone Detectors, Default Characteristics

The default bandwidths and thresholds of the tone detectors are as follows:

| Tone Detector | Bandwidth    | Turn-On<br>Threshold | Turn-Off<br>Threshold |