TRINAMIC Motion Control GmbH & Co. KG Sternstrasse 67 D – 20357 Hamburg GERMANY

WWW.TRINAMIC.COM

# TMC 423 – Datasheet Serial Triple Incremental Encoder Interface

### TMC<sub>423</sub> Main Features

The TMC423 is a triple incremental encoder input chip, which interfaces to any SPI<sup>™</sup> compatible controller. The TMC423 can especially be used in conjunction with the TMC428 triple stepper motor controller to provide position verification or stabilization using some additional software. It integrates 24 bit counters for each encoder to provide a high position resolution without CPU interaction. Further it allows dynamic resolution adaptation to allow direct comparison of encoder counters with motors using different micro step resolution. All encoder counters can be latched synchronously, or whenever a null channel event occurs, providing a position on strobe holding function. The TMC428 as an optional function. A multiplexer function is also integrated for the TMC428 reference switches. Furthermore control and drive of a LED and switch matrix is implemented. All functions can also be used in conjunction.

## Applications

- Stepper Motor Position Verification

- Position Maintenance

- Incremental Encoder Interface Readout

- Step / Direction conversion for TMC428 systems

- Control of LED 6 x 4 Matrix and Switch 6 x 4 Matrix

### Features

- Supports 2 and 3 channel incremental encoders with a wide range of resolutions

- Allows step / direction signal extraction from TMC428 output data stream

- Programmable pulse shaping for step / direction interface

- 24 bit integrated position resolution

- Programmable prescaler for Incremental Encoder Interface

- 4-times evaluation of encoder signals

- Fast 32 bit SPI<sup>™</sup> interface

- Can share SPI<sup>™</sup> interface with TMC428 and supplies separate interrupt output

- Integrates Reference Switch Multiplexers

- Package: TQ100

Note: SPI is Trademark of Motorola, Inc.

## **Revision History**

| Version         | Comment                                                                             | Date                                 | Name                 |

|-----------------|-------------------------------------------------------------------------------------|--------------------------------------|----------------------|

| Initial Version |                                                                                     | November 22, 2002                    | Technical Department |

| 0.4             | Corrected Array Switching Frequency                                                 | January 23, 2003                     | Technical Department |

| 0.5             | First Customer Release                                                              | January 24, 2003                     | Technical Department |

| 0.6             | Minor corrections                                                                   | March 11, 2003                       | Technical Department |

| 0.6             | Changes concerning new company TRINAMIC<br>Motion Control GmbH & Co. KG             | October 1 <sup>st</sup> , 2004       | Technical Department |

| 0.7             | Corrected Pinning: Position of CLK pin                                              | December, 15 <sup>th</sup> ,<br>2004 | Technical Department |

| 1.0             | Corrected Reset input in diagram, added<br>supply spec                              | March, 15 <sup>th</sup> , 2005       | Technical Department |

| 1.1             | Added Application Environment examples                                              | March, 9 <sup>th</sup> , 2007        | Technical Department |

| 1.1             | Added encoder timing                                                                | Apr, 4 <sup>th</sup> , 2007          | Dw                   |

| 1.2             | S/D Appl. corrected, added TMC428 SPI<br>datagram for S/D                           | June 6 <sup>th</sup> , 2007          | НС                   |

| 1.3             | Figure 4 and Figure 5: TMC423 clock input corrected; more detailed flag description | June 20 <sup>th</sup> , 2007         | HC, Dw               |

## **Table of Contents**

| 1  | Pinc   | put                                                      |    |

|----|--------|----------------------------------------------------------|----|

|    | 1.1    | Pin Description                                          | 6  |

|    | 1.2    | Recommended Operating Conditions                         |    |

|    | 1.3    | Electrical Characteristics                               | 7  |

| 2  | Bloc   | k Diagram                                                | 8  |

| 3  | Арр    | lication Environment                                     | 9  |

|    | 3.1    | Application Description                                  |    |

|    | 3.1.1  | - · · F L · · · · · · · · · · · · · · · ·                |    |

|    | 3.1.2  |                                                          | 9  |

|    | 3.2    | Application Examples                                     | 10 |

|    | 3.2.1  | Application with TMC236 Stepper Motor Driver             | 10 |

|    | 3.2.2  |                                                          |    |

| 4  | Dyn    | amic Resolution Adaptation                               | 11 |

| 5  | Seri   | al Peripheral Interface (SPI) with 32-bit Register       | 12 |

|    | 5.1    | Description and Specification                            | 12 |

|    | 5.2    | 32-bit SPI Datagram Structure                            | 13 |

|    | 5.3    | SPI 32-bit Datagram Specification                        |    |

|    | 5.3.1  |                                                          |    |

| 6  | Incr   | emental Encoder                                          | 14 |

| 7  | Con    | figuration Datagrams                                     |    |

|    | 7.1    | Encoder Interface Prescaler and Null Event Configuration | 15 |

|    | 7.2    | Encoder Interface Hold Register Operation                |    |

|    | 7.3    | Timer Logic Step Pulse Length and Delay                  |    |

|    | 7.4    | Control Register and Interrupt Control                   |    |

|    | 7.5    | Switch Matrix Read                                       |    |

|    | 7.6    | LED Matrix Write                                         |    |

| 8  | SPI-   | Protocol for Interface with 6-bit Register               |    |

|    | 8.1    | Step and Direction Pulse conversion                      |    |

| 9  | LED    | and Switch Matrix                                        | 19 |

| 1( | o Pack | age dimensions                                           | 20 |

## **List of Figures**

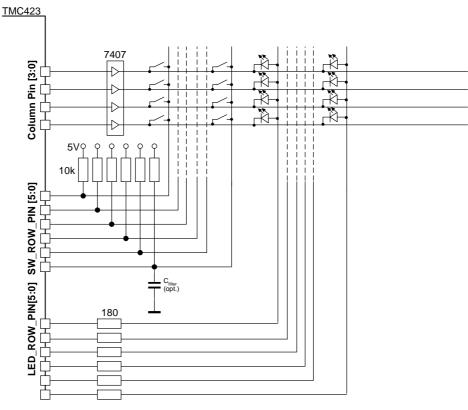

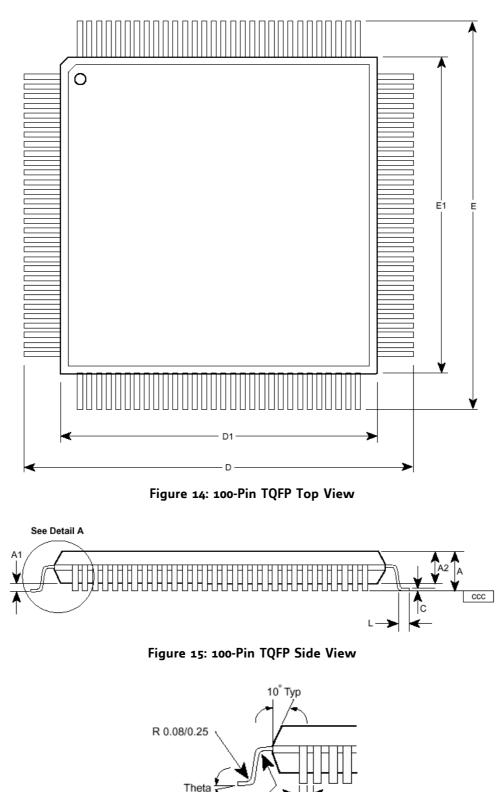

Figure 1: Pinout TMC4235 Figure 2: Block diagram of the TMC423 8 Figure 3: Application Environment Figure 4: Example for Application with TMC236 Stepper Motor Driver 10 Figure 5: Example for Application with Step / Direction Power Stage 10 Figure 6: TMC423 Application 11 Figure 7: Timing diagram of the Serial Interface 12 Figure 8: Structure 32-Bit Interface 13 Figure 9: Overview TMC423 Registers 13 Figure 10: Encoder Output and Evaluation 14 Figure 11: Crosstalk on Encoder Wire 14 Figure 12: Step Direction conversion 18 Figure 13: Connection to the matrix 19 Figure 14: 100-Pin TQFP Top View 20 Figure 15: 100-Pin TQFP Side View 20 Figure 16: 100-Pin TQFP Side View Detail A 20

## **List of Tables**

Table 1: TMC423 Pinout 7 Table 2: Operating Conditions 7 Table 3: Operating Conditions 7 Table 4: Prescaler factors for different motors and encoders 11 Table 5: Interrupt Flags 13

Table 6: SPI Datagram Prescaler 16

Table 7: SPI Datagram Hold Register 16 Table 8: SPI Datagram Step-/Dir logic 17 Table 9: SPI Datagram Control Register 17 Table 10: Switch Matrix Read 17 Table 11: LED Matrix Write 17 Table 12: SPI Datagram Step / Direction Converter 18 Table 13: Datagram example and RAM contents for three step-direction drivers 18 Table 14: TMC423 LED Matrix Pins 19 Table 15: TQFP Dimensions 21

# 1 Pinout

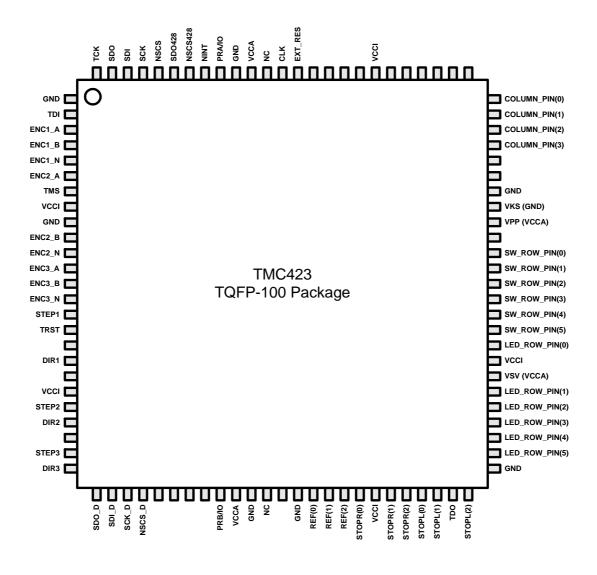

Figure 1: Pinout TMC423

# 1.1 Pin Description

| Pin                     | Location                        | Dir | Description                                         |

|-------------------------|---------------------------------|-----|-----------------------------------------------------|

| GND                     | 1, 9, 36, 39, 51, 68,<br>69, 91 | In  | Ground                                              |

| ENC1 A                  | 3                               | In  | Incremental Encoder Interface 1 Channel A           |

| ENC1 B                  | 4                               | In  | Incremental Encoder Interface 1 Channel B           |

| ENC1_N                  | 5                               | In  | Incremental Encoder Interface 1 Channel N           |

|                         | -                               |     | (Connect to +5V if not used)                        |

| ENC2_A                  | 6                               | In  | Incremental Encoder Interface 2 Channel A           |

| ENC2 B                  | 10                              | In  | Incremental Encoder Interface 2 Channel B           |

| ENC2_N                  | 11                              | In  | Incremental Encoder Interface 2 Channel N           |

| -                       |                                 |     | (Connect to +5V if not used)                        |

| ENC3_A                  | 12                              | In  | Incremental Encoder Interface 3 Channel A           |

| ENC3_B                  | 13                              | In  | Incremental Encoder Interface 3 Channel B           |

| ENC3_N                  | 14                              | In  | Incremental Encoder Interface 3 Channel N           |

|                         |                                 |     | (Connect to +5V if not used)                        |

| TDI                     | 2                               |     | Connect to Ground                                   |

| TMS                     | 7                               |     | Connect to 5 Volt via Pull-Up Resistor              |

| TRST                    | 16                              |     | Connect to 5 Volt via Pull-Up Resistor              |

| TDO                     | 49                              |     | To be left open                                     |

| ТСК                     | 100                             |     | Connect to Ground                                   |

| VCCI                    | 8, 20, 44, 58, 82               | In  | Positive Power Supply 5 Volt                        |

| VCCA                    | 35, 57, 67, 90                  | In  | Positive Power Supply 2.5 Volt                      |

| GND                     | 39                              | In  | Unused input: Connect to Ground                     |

| CLK                     | 88                              | In  | System Clock 16MHz                                  |

| EXT_RES                 | 87                              | In  | External Reset Low Active                           |

| NC                      | 37, 89                          | In  | Connect to Ground                                   |

| PRA / IO                | 92                              |     | To be left open                                     |

| PRB / IO                | 34                              |     | To be left open                                     |

| Step 1                  | 15                              | Out | Step/Direction Interface – Step Output Motor 1      |

| Dir 1                   | 18                              | Out | Step/Direction Interface – Direction Output Motor 1 |

| Step 2                  | 21                              | Out | Step/Direction Interface – Step Output Motor 2      |

| Dir 2                   | 22                              | Out | Step/Direction Interface – Direction Output Motor 2 |

| Step 3                  | 24                              | Out | Step/Direction Interface – Step Output Motor 3      |

| Dir 3                   | 25                              | Out | Step/Direction Interface – Direction Output Motor 3 |

| SDO_D                   | 26                              | Out | Step / Direction SPI MISO                           |

| SDI_D                   | 27                              | In  | Step / Direction SPI MOSI                           |

| SCK_D                   | 28                              | In  | Step / Direction SPI SCK                            |

| NSCS_D                  | 29                              | In  | Step / Direction SPI NSCS                           |

| REFo                    | 40                              | Out | Reference switch output 1                           |

| REF1                    | 41                              | Out | Reference switch output 2                           |

| REF2                    | 42                              | Out | Reference switch output 3                           |

| STOPRo                  | 43                              | In  | Right Stop Switch Motor 1                           |

| STOPR1                  | 45                              | In  | Right Stop Switch Motor 2                           |

| STOPR2                  | 46                              | In  | Right Stop Switch Motor 3                           |

| STOPLo                  | 47                              | In  | Left Stop Switch Motor 1                            |

| STOPL1                  | 48                              | In  | Left Stop Switch Motor 2                            |

| STOPL2                  | 50                              | In  | Left Stop Switch Motor 3                            |

| COLUMN_PINo             | 75                              | Out | Column Drive Pin o                                  |

| COLUMN_PIN1             | 74                              | Out | Column Drive Pin 1                                  |

| COLUMN_PIN2             | 73                              | Out | Column Drive Pin 2                                  |

| COLUMN_PIN3             | 72                              | Out | Column Drive Pin 3                                  |

| SW_ROW_PINo             | 65                              | In  | Switch Matrix Pin o                                 |

| SW_ROW_PIN1             | 64                              | In  | Switch Matrix Pin 1                                 |

| SW_ROW_PIN2             | 63                              | In  | Switch Matrix Pin 2                                 |

| SW_ROW_PIN <sub>3</sub> | 62                              | In  | Switch Matrix Pin 3                                 |

| SW ROW PIN4  | 61 | In  | Switch Matrix Pin 4           |

|--------------|----|-----|-------------------------------|

| SW_ROW_PIN5  | 60 | In  | Switch Matrix Pin 5           |

| LED_ROW_PINo | 59 | Out | LED Matrix Drive Pin o        |

| LED_ROW_PIN1 | 56 | Out | LED Matrix Drive Pin 1        |

| LED_ROW_PIN2 | 55 | Out | LED Matrix Drive Pin 2        |

| LED_ROW_PIN3 | 54 | Out | LED Matrix Drive Pin 3        |

| LED_ROW_PIN4 | 53 | Out | LED Matrix Drive Pin 4        |

| LED_ROW_PIN5 | 52 | Out | LED Matrix Drive Pin 5        |

| SDO          | 99 | Out | SPI MISO                      |

| SDI          | 98 | In  | SPI MOSI                      |

| SCK          | 97 | In  | SPI SCK                       |

| NSCS         | 96 | In  | SPI NSCS                      |

| SD0428       | 95 | In  | SPI MISO Pin of TMC428        |

| NSCS428      | 94 | In  | SPI NSCS Pin of TMC428        |

| NINT         | 93 | Out | Interrupt Output (low active) |

### Table 1: TMC423 Pinout

Note: Pins which are not marked in Figure 1: Pinout TMC423 on page 5 must be left open.

## 1.2 Recommended Operating Conditions

| Parameter           | Value     | Unit             |

|---------------------|-----------|------------------|

| Clock Frequency (1) | 16        | MHz              |

| Temperature         | 0 + 70    | °C               |

| 2.5 V Power Supply  | 2.25 2.75 | V <sub>CCA</sub> |

| 5.0 V Power Supply  | 4.50 5.50 | V <sub>CCI</sub> |

#### Table 2: Operating Conditions

slower frequencies are also supported. Please take care about the timing information in this datasheet, since they are based on 16MHz Clock Frequency.

# 1.3 Electrical Characteristics

| Parameter                  | Min                | Max              | Unit |

|----------------------------|--------------------|------------------|------|

| Supply Current 2.5V        |                    | 100              | mA   |

| Supply Current 5.0V        |                    | 10               | mA   |

| (Output current = o)       |                    |                  |      |

| LED driver current per pin |                    | 20               | mA   |

| Input voltage level Low    |                    | 0.8              | V    |

| Input voltage level High   | 2.4                |                  | V    |

| Encoder input pulse length | 2 t <sub>CLK</sub> |                  |      |

| Encoder count rate         |                    | f <sub>ськ</sub> |      |

| Table | 3: | Operating | Conditions |

|-------|----|-----------|------------|

|-------|----|-----------|------------|

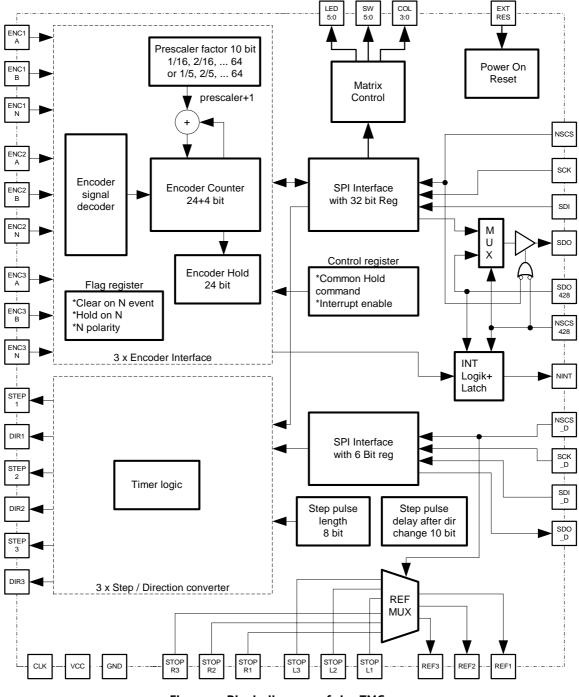

# 2 Block Diagram

Figure 2: Block diagram of the TMC423

# **3** Application Environment

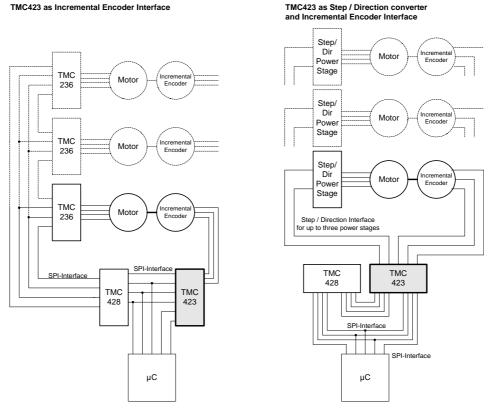

#### TMC423 as Incremental Encoder Interface

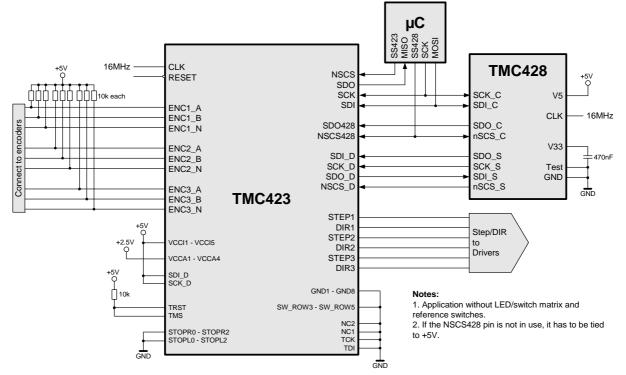

Figure 3: Application Environment

#### **Application Description** 3.1

#### Application with TMC236 Stepper Motor Driver 3.1.1

A complete close-loop motion control system consists of the TMC428 three-axis motion controller, the powerful TMC236 stepper motor driver and the TMC423 Encoder Interface. The system is controlled by an inexpensive microcontroller.

The main advantage of the system is that time critical communication to the TMC236 driver is performed by the TMC428. The main purpose of the inexpensive microcontroller is to parameterize the TMC428 and TMC423 and to send motion parameters like maximum speed or target position to the TMC428. Position validation is done by reading the actual position of the TMC428 and the TMC423.

#### Application with Step / Direction Power Stage 3.1.2

Another possibility to built a close loop motion control system is to use the TMC423 as encoder interface and also as a step direction converter. Thereto the TMC423 converts the SPI<sup>™</sup> datagrams sent by the TMC428 into parameterizeable step and direction pulses. For parameterizing both the TMC428 and TMC423 have to be connected via SPI<sup>™</sup> interface to an inexpensive microcontroller.

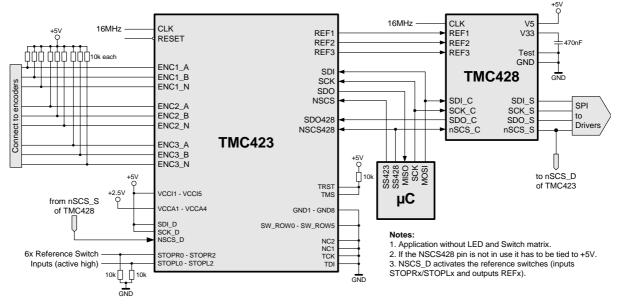

## 3.2.1 Application with TMC236 Stepper Motor Driver

This example illustrates the encoder connection and the use of reference switches with the TMC423 and additionally the SPI interface connections between TMC423, TMC428 and a microcontroller. The communication to the drivers (e.g. TMC236) is performed via SPI by the TMC428 motion control chip.

Figure 4: Example for Application with TMC236 Stepper Motor Driver

## 3.2.2 Application with Step / Direction Power Stage

Additionally to the previous example the use of the TMC423 as step/direction converter is shown. The reference switches can be used as above.

Figure 5: Example for Application with Step / Direction Power Stage

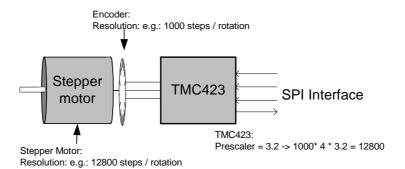

# **4** Dynamic Resolution Adaptation

The dynamic resolution adaptation is needed to link stepper motors and encoders with different resolutions. The characteristics of the connected hardware must provided to the TMC423 by sending the corresponding SPI telegram. (See 5.3.1 Overview on page 13 in this issue). The TMC423 multiplies the encoder counter by a user selectable value in the range 1..1024, and then divides it by 16. When using incremental encoders with N channel it is also possible to select between different behaviors when the N channel is triggered.

Figure 6: TMC423 Application

Table 4 shows a number of prescaler factors for possible combinations of micro step resolution and encoder resolution. Note: The given number of pulses have to be multiplied by four since 4-times encoder signal evaluation is used. (See Figure 10: Encoder Output and Evaluation on page 14).

| Microstep |        |      | Er     | ncoder R | esolution | [Pulses | Rotatio | n]   |    |    |

|-----------|--------|------|--------|----------|-----------|---------|---------|------|----|----|

| S         | 1024   | 1000 | 512    | 500      | 256       | 250     | 200     | 125  | 50 | 25 |

| 12800     | 3.125  | 3.2  | 6.25   | 6.4      | 12.5      | 12.8    | 16      | 25.6 | 64 |    |

| 6400      | 1.5625 | 1.6  | 3.125  | 3.2      | 6.25      | 6.4     | 8       | 12.8 | 32 | 64 |

| 3200      |        |      | 1.5625 | 1.6      | 3.125     | 3.2     | 4       | 6.4  | 16 | 32 |

| 1600      |        |      |        |          | 1.5625    | 1.6     | 2       | 3.2  | 8  | 16 |

| 800       |        |      |        |          |           |         | 1       | 1.6  | 4  | 8  |

| 400       |        |      |        |          |           |         |         |      | 2  | 4  |

Table 4: Prescaler factors for different motors and encoders

# 5 Serial Peripheral Interface (SPI) with 32-bit Register

## 5.1 Description and Specification

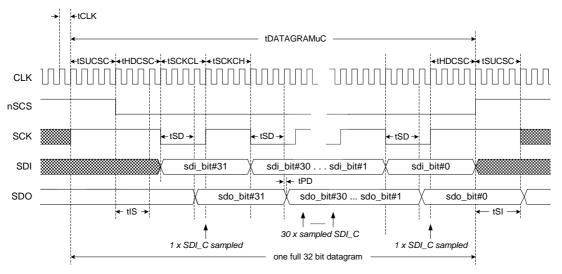

Four pins named nSCS, SCK, SDI and SDO form the serial peripheral interface from a microcontroller to the TMC423. The communication between the microcontroller and the TMC423 takes place via datagrams with a fixed length of 32 bit. The microcontroller acts always as master and the TMC423 as slave.

The SPI<sup>™</sup> of the TMC423 behaves like a simple 32-bit shift register. Incoming serial data at pin SDI is shifted with the rising edge of the clock signal SCK into the 32-bit register. The content of this register is copied after 32-bits with the rising edge of the selection signal nSCS into a buffer register of 32-bit length. The SPI<sup>™</sup> of the TMC423 sends back data read from registers immediately via the SDO signal. It processes serial data synchronously to the clock signal CLK.

Because of on-the-fly processing of the input data stream, the serial microcontroller interface of the TMC423 requires the serial data clock signal SCK to have a minimum low / high time of three clock cycles. The data signal SDI driven by the microcontroller has to be valid at the rising edge of the serial data clock input SCK. The maximum duration of the serial data clock period is unlimited.

A complete serial datagram frame has a fixed length of 32 bit. While the data transmission from the microcontroller to the TMC423 is idle, the low active serial chip select input nSCS and also the serial data clock signal SCK are set to high. The serial data input SDI of the TMC428 has to be driven by the microcontroller. Like other SPI compatible devices, the SDO signal of the TMC423 is high impedance 'Z' as long as nSCS is high.

The signal nSCS has to be high for at least three clock cycles before starting a datagram transmission. To initiate a transmission, the signal nSCS has to be set to low. Three clock cycles later the serial data clock may go low. The most significant bit (MSB) of a 32 bit wide datagram comes first and the least significant bit (LSB) is transmitted as the last one. A data transmission is finished by setting nSCS high for three or more CLK cycles after the last rising SCK slope. nSCS and SCK change in opposite order from low to high at the end of a transmission as these signals change from high to low at the beginning. The timing of the serial microcontroller interface is outlined in Figure 7: *Timing diagram of the Serial Interface*.

Figure 7: Timing diagram of the Serial Interface

# 5.2 32-bit SPI Datagram Structure

|        | Datagram from TMC423 send to $\mu$ C |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |   |   |   |   |   |   |   |   |   |   |

|--------|--------------------------------------|---|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---|---|---|---|---|---|---|---|---|---|

| 3<br>1 | 3                                    | 3 | 2<br>9 | 2<br>8 | 2<br>7 | 2<br>6 | 2<br>5 | 2<br>4 | 2<br>3 | 2<br>2 | 2<br>1 | 2<br>0 | 1<br>9 | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1<br>4 | 1<br>3 | 1<br>2 | 1<br>1 | 1<br>0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|        | I                                    | N | Г      |        | 0      | 0      | 0      | 0      |        | Data   |        |        |        |        |        |        |        |        |        |        |        |        |   |   |   |   |   |   |   |   |   |   |

| Datagram from µC to TMC423                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |  |  |  |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|--|--|--|--|--|--|--|--|--|

| 3         3         2         2         2         2         2         2         2         2         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 |      |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Address <sup>R</sup> <sub>W</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Data |  |  |  |  |  |  |  |  |  |  |  |  |  |

### Figure 8: Structure 32-Bit Interface

| Interrupt Flags [Bit] | Name     | Description                              |

|-----------------------|----------|------------------------------------------|

| 31                    | INT_ext  | external Interrupt, e.g. TMC428          |

| 30                    | INT_enc1 | N Signal of Encoder Interface 1 detected |

| 29                    | INT_enc2 | N Signal of Encoder Interface 2 detected |

| 28                    | INT_enc3 | N Signal of Encoder Interface 3 detected |

Table 5: Interrupt Flags

# 5.3 SPI 32-bit Datagram Specification

## 5.3.1 Overview

| Byte #    |    |    |    | By                    | te :   | 3  |    |                                 |          |                                   | E     | Зу   | te  | 2    |     |       |                       |                             |     |     | В    | yt | :e '     | 1      |        |         |           | Byte 0    |      |     |     |     |    |   |  |

|-----------|----|----|----|-----------------------|--------|----|----|---------------------------------|----------|-----------------------------------|-------|------|-----|------|-----|-------|-----------------------|-----------------------------|-----|-----|------|----|----------|--------|--------|---------|-----------|-----------|------|-----|-----|-----|----|---|--|

| Bit #     | 31 | 30 | 29 | 28                    | 27     | 26 | 25 | 24                              | 23       | 23 22 21 20 19 18 17 16 15        |       |      |     |      |     |       |                       | 14                          | 4 1 | 3   | 12   | 11 | 10       | 9      | 8      | 7       | 6         | 5         | 4    | 4   | 3   | 2   | 1  | 0 |  |

|           |    |    | Ac | ddre                  | SS     |    |    | R<br>V                          |          |                                   |       |      |     |      |     |       |                       |                             |     |     |      |    |          |        |        |         |           |           |      |     |     |     |    |   |  |

| Control   | 0  | 0  | 0  | 0                     | 0      | 0  | 0  | 1                               |          | Encoder 1 Presca                  |       |      |     |      |     |       |                       |                             |     |     |      |    | >        |        |        |         |           |           |      | F   | Res | erv | ed |   |  |

|           | 0  | 0  | 0  | 0                     | 0      | 0  | 1  | 1                               |          |                                   |       | Е    | ncc | oder | 2   | Pres  | ca                    | ler                         |     |     |      |    | Polarity | N Hold | Clear  | Trigger | ction     |           |      | F   | Res | erv | ed |   |  |

|           | 0  | 0  | 0  | 0                     | 0      | 1  | 0  | 1                               |          |                                   |       | Е    | ncc | oder | 3   | Pres  | ca                    | er                          |     |     |      |    | N Po     | Z      | 2<br>Z | I<br>Z  | Direction |           |      | F   | Res | erv | ed |   |  |

|           | 0  | 0  | 0  | 0                     | 0      | 1  | 1  | 1                               | Er       | ncoc                              | ler 1 | , 2, | 3 F | Pres | са  | ler - | se                    | t all                       | со  | mm  | nonl | у  |          |        |        |         |           | Reserved  |      |     |     |     |    |   |  |

| Data      | 0  | 0  | 0  | 0                     | 1<br>  | 0  | 0  | <br>                            |          |                                   |       |      |     |      |     |       |                       | Encoder 1 Position Register |     |     |      |    |          |        |        |         |           |           |      |     |     |     |    |   |  |

|           | 0  | 0  | 0  | 0                     | 1<br>1 | 0  | 1  |                                 |          |                                   |       |      |     |      |     |       |                       | Encoder 2 Position Register |     |     |      |    |          |        | ter    | -       | <br>      |           |      |     |     |     |    |   |  |

|           | 0  | 0  | 0  | 0                     | ,<br>1 | 1  | 0  |                                 |          |                                   |       |      |     |      |     |       |                       | Encoder 3 Position Register |     |     |      |    |          |        | ter    |         |           |           |      |     |     |     |    |   |  |

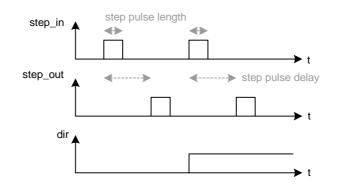

| Step /Dir | 0  | 0  | 0  | 0                     | 1      | 1  | 1  | 1                               |          | S                                 | Step  | Pul  | se  | Len  | gth | 1     |                       |                             |     |     | St   | ep | Pu       | se     | Dela   | ıy      |           | Reserved  |      |     |     |     |    |   |  |

| INT       | 0  | 0  | 0  | 1<br>1<br>1<br>1<br>1 |        | 0  | 0  | 1<br>1<br>1<br>1<br>1<br>1<br>1 | Reg Hold | Reg Hold<br>INT EN<br>Clear Flags |       |      |     |      |     |       |                       |                             |     |     |      |    | Re       | ser    | ved    |         |           |           |      |     |     |     |    |   |  |

| Matrix    | 0  | 0  | 0  | 1                     | 0      | 0  | 1  | 0                               |          | Switch Row 3                      |       |      |     |      |     |       | Switch Row 2 Switch R |                             |     |     |      |    |          | n Ro   | w 1    |         |           | 5         | Swit | tch | Row | / 0 |    |   |  |

|           | 0  | 0  | 0  | 1                     | 0      | 1  | 0  | 1                               |          | LED Row 3 LE                      |       |      |     |      |     |       |                       | ED F                        | Ro  | w 2 |      |    | LED Row  |        |        |         |           | LED Row 0 |      |     |     |     |    |   |  |

Figure 9: Overview TMC423 Registers

# 6 Incremental Encoder

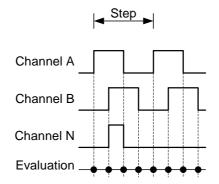

Incremental Encoders are translating the rotary motion of a shaft into a two-channel digital quadrature output. The light emitted from a LED is focused onto a reflective code wheel. As the shaft moves, the code wheel rotates, reflecting light from an alternating bright and dark pattern.

The TMC423 samples the incoming signals  $ENCx_a$  and  $ENCx_B$  from the incremental encoder. A internal algorithm block counts the amount of edges generated by the encoder. A prescaler value can be used to adapt the incremental encoder resolution to the stepper motor resolution.

For high resolution the TMC423 evaluates the encoder signals 4-times during each encoder step. This has to kept in mind when choosing the prescaler value.

Figure 10: Encoder Output and Evaluation

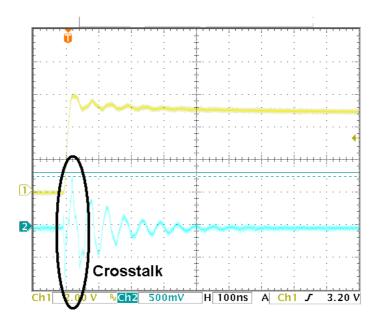

Note: It is possible that the encoder signals ENCx\_A, ENCx\_B and ENCx\_N are polluted with crosstalk noise. Crosstalk could influence the internal logic, to overcome this problem internal filters are applied to ensure correct functionality. Furthermore is saves the need for external analog filters. e.g.: Figure 11: Crosstalk on Encoder Wire shows crosstalk from channel A to channel B.

Figure 11: Crosstalk on Encoder Wire

# 7 Configuration Datagrams

# 7.1 Encoder Interface Prescaler and Null Event Configuration

The Encoder Interface Initialization datagram configures the parameterizeable encoder prescaler to adapt the TMC423 for different incremental encoders. Furthermore the TMC423 behavior concerning the N channel can be selected.

Example: A 1000 steps per rotation encoder is to connect at a stepper motor with 12800 microsteps per rotation. When the next event at the high active N channel is found, the position register must set to zero. Only Encoder Interface 1 is connected. The following datagram performs this task:

- Bits 31 down to 24 have to be set to  $O1_{HEX}$  to select encoder interface 1

- The prescaler value has to set to 12800 / (1000\*4) = 3.2. Therefore bits 23 down to 12 must set to 831<sub>HEX</sub>.

- The N channel is set up correctly when bits 11 down to 0 are set to  $Ao_{HEX}$ .

| Bit  | Encoder Interface Initialization                                                                                    |

|------|---------------------------------------------------------------------------------------------------------------------|

| 3128 | "oooo" Register Address                                                                                             |

| 2725 | Interface Selection                                                                                                 |

|      | 000 = Interface 1                                                                                                   |

|      | 001 = Interface 2                                                                                                   |

|      | 010 = Interface 3                                                                                                   |

|      | 011 = Interface 1, 2 and 3                                                                                          |

| 24   | '1'                                                                                                                 |

| 2312 | External Encoder Resolution and Corresponding Prescaler Factor                                                      |

|      | Bits 15 12: Fractional part of Factor. Unit: 1/16 (when bit 23 = 0) resp. 1/5 (bit 23 = 1)                          |

|      | Bits 22 16: Integer part of Factor                                                                                  |

|      | Bit 23: Switches Fractional part between 1/5 resolution or 1/16 resolution                                          |

|      | Default:                                                                                                            |

|      | (010), (prescaler 1) (default value after power on)                                                                 |

|      | Example settings:                                                                                                   |

|      | Encoder: 1024 lines (4096 steps per rotation)                                                                       |

|      | $(032)_h$ for 12800 micro steps per rotation (prescaler 3.125)<br>$(019)_h$ for 6400 micro steps (prescaler 1.5625) |

|      |                                                                                                                     |

|      | Encoder: 1000 lines                                                                                                 |

|      | (831) h for 12800 micro steps (prescaler 3.2)                                                                       |

|      | (813) <sub>h</sub> for 6400 micro steps (prescaler 1.6)                                                             |

|      | Encoder: 512 lines                                                                                                  |

|      | (064) <sub>h</sub> for 12800 micro steps (prescaler 6.25)                                                           |

|      | $(032)_h$ for 6400 micro steps (prescaler 3.125)<br>$(019)_h$ for 3200 micro steps (prescaler 1.5625)               |

|      |                                                                                                                     |

|      | Encoder: 500 lines                                                                                                  |

|      | (862) <sub>h</sub> for 12800 micro steps (prescaler 6.4)                                                            |

|      | (831) <sub>h</sub> for 6400 micro steps (prescaler 3.2)<br>(813) <sub>h</sub> for 3200 micro steps (prescaler 1.6)  |

|      |                                                                                                                     |

|      | Encoder: 256 lines                                                                                                  |

|      | $(oC8)_h$ for 12800 micro steps (prescaler 12.5)<br>$(o64)_h$ for 6400 micro steps (prescaler 6.25)                 |

|      | $(032)_h$ for 3200 micro steps (prescaler 3.125)                                                                    |

|      | (019) <sub>h</sub> for 1600 micro steps (prescaler 1.5625)                                                          |

|      | Encoder: 250 lines                                                                                                  |

|      | (8C4) <sub>h</sub> for 12800 micro steps (prescaler 12.8)                                                           |

|      | (862) <sub>h</sub> for 6400 micro steps (prescaler 6.4)                                                             |

|      | (831) <sub>h</sub> for 3200 micro steps (prescaler 3.2)<br>(813) <sub>h</sub> for 1600 micro steps (prescaler 1.6)  |

|      | Encoder: 200 lines                                                                                                  |

|      | (100) <sub>h</sub> for 12800 micro steps (prescaler 16)                                                             |

|      | (080) <sub>h</sub> for 6400 micro steps (prescaler 8)                                                               |

|      | (040) <sub>h</sub> for 3200 micro steps (prescaler 4)<br>(020) <sub>h</sub> for 1600 micro steps (prescaler 2)      |

| L    |                                                                                                                     |

| i.e. to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------------------------------------------------------------------------------|

| <ul> <li>(993), for 12800 micro steps (prescaler 22.6)</li> <li>(862b, for 2800 micro steps (prescaler 12.8)</li> <li>(862b, for 3200 micro steps (prescaler 3.2)</li> <li>(833), for 1600 micro steps (prescaler 3.2)</li> <li>(833), for 1600 micro steps (prescaler 3.2)</li> <li>(833), for 12800 micro steps (prescaler 3.2)</li> <li>(800), for 12800 micro steps (prescaler 4.4)</li> <li>(200), for 12800 micro steps (prescaler 3.2)</li> <li>(100), for 12800 micro steps (prescaler 3.2)</li> <li>(100), for 12800 micro steps (prescaler 3.2)</li> <li>(100), for 1600 micro steps (prescaler 4.4)</li> <li>(100), for 1600 micro steps (prescaler 4.4)</li> <li>(100), for 1600 micro steps (prescaler 2.1)</li> <li>(11 N Polarity for Selected Interface</li> <li>0 = active low (default)</li> <li>1 = active high</li> <li>When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.</li> <li>10 Hold on N for Selected Interface</li> <li>0 = no hold (default)</li> <li>1 = active: Encoder counter freezes during o channel event.</li> <li>9 Clear on N Event for Selected Interface</li> <li>0 = no clear (default)</li> <li>1 = active</li> <li>When switched to active, then it depends on bit 8, if a clear event is issued only once, or always when the N channel becomes active.</li> <li>8 N Trigger Selection</li> <li>0 = only at next N signal (default)</li> <li>1 = always at N signal</li> <li>The clear event last until the N signal goes inactive again. If earlier termination is desired, <i>i.e.</i> to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.</li> </ul>                                                                                                                                                                                                                       |    | (010) <sub>h</sub> for 800 micro steps (prescaler 1)                                            |

| <ul> <li>(862), for 6400 micro steps (prescaler 3.2)</li> <li>(862), for 3200 micro steps (prescaler 3.2)</li> <li>(833), for 800 micro steps (prescaler 3.2)</li> <li>(833), for 800 micro steps (prescaler 3.2)</li> <li>(833), for 800 micro steps (prescaler 4.6)</li> <li>(200), for 12800 micro steps (prescaler 3.2)</li> <li>(100), for 3200 micro steps (prescaler 3.2)</li> <li>(101), for 200 steps per rotation (prescaler 1.1)</li> <li>11 N Polarity for Selected Interface</li> <li>0 = active low (default)</li> <li>1 = active high</li> <li>When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.</li> <li>10 Hold on N for Selected Interface</li> <li>0 = no hold (default)</li> <li>1 = active: Encoder counter freezes during 0 channel event.</li> <li>9</li> <li>Clear on N Event for Selected Interface</li> <li>0 = no clear (default)</li> <li>1 = active</li> <li>When switched to active, then it depends on bit 8, if a clear event is issued only once, or always when the N channel becomes active.</li> <li>8</li> <li>N Trigger Selection</li> <li>0 = only at next N signal (default)</li> <li>1 = always at N signal</li> <li>The clear event lost until the N signal goes inactive again. If earlier termination is desired, i.e. to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.</li> </ul>                                                                                                                                                            |    | Encoder: 125 lines                                                                              |

| <ul> <li>(662), for 3200 micro steps (prescaler 3.2)</li> <li>(831), for 1600 micro steps (prescaler 3.2)</li> <li>(833), for 12800 micro steps (prescaler 1.6)</li> <li>Encoder: so lines (200 steps per rotation)</li> <li>(400), for 12800 micro steps (prescaler 3.2)</li> <li>(1200), for 12800 micro steps (prescaler 3.2)</li> <li>(1200), for 3200 micro steps (prescaler 3.2)</li> <li>(1200), for 1600 micro steps (prescaler 3.2)</li> <li>(1200), for 3200 micro steps (prescaler 1.2)</li> <li>(1200), for 400 micro steps (prescaler 1.2)</li> <li>(1200), for 200 steps per rotation (prescaler 1.2)</li> <li>(12</li></ul> |    | (993) <sub>h</sub> for 12800 micro steps (prescaler 25.6)                                       |

| <ul> <li>(83), for 1600 micro steps (prescaler 3.2)</li> <li>(83), for 800 micro steps (prescaler 1.6)</li> <li>Encoder: 50 lines (200 steps per rotation)</li> <li>(400), for 12800 micro steps (prescaler 32)</li> <li>(100), for 1200 micro steps (prescaler 32)</li> <li>(100), for 3200 micro steps (prescaler 16)</li> <li>(080), for 1600 micro steps (prescaler 1)</li> <li>11 N Polarity for Selected Interface</li> <li>0 = active low (default)</li> <li>1 = active high</li> <li>When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.</li> <li>10 Hold on N for Selected Interface</li> <li>0 = no hold (default)</li> <li>1 = active: Encoder counter freezes during 0 channel event.</li> <li>9 Clear on N Event for Selected Interface</li> <li>0 = no clear (default)</li> <li>1 = active</li> <li>When switched to active, then it depends on bit 8, if a clear event is issued only once, or always when the N channel becomes active.</li> <li>8 N Trigger Selection</li> <li>0 = only at next N signal (default)</li> <li>1 = always at N signal</li> <li>The clear event last until the N signal goes inactive again. If earlier termination is desired, i.e. to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | (8C4) <sub>h</sub> for 6400 micro steps (prescaler 12.8)                                        |

| <ul> <li>(813)<sup>h</sup> for 800 micro steps (prescaler 1.6)</li> <li>Encoder: so lines (200 steps per rotation) <ul> <li>(400)<sup>h</sup> for 12800 micro steps (prescaler 64)</li> <li>(200)<sup>h</sup> for 3200 micro steps (prescaler 76)</li> <li>(000)<sup>h</sup> for 300 micro steps (prescaler 16)</li> <li>(000)<sup>h</sup> for 300 micro steps (prescaler 2)</li> <li>(000)<sup>h</sup> for 200 micro steps (prescaler 1)</li> </ul> </li> <li>11 N Polarity for Selected Interface <ul> <li>0 = active low (default)</li> <li>1 = active high</li> <li>When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.</li> </ul> </li> <li>10 Hold on N for Selected Interface <ul> <li>0 = no hold (default)</li> <li>1 = active: Encoder counter freezes during o channel event.</li> </ul> </li> <li>9 Clear on N Event for Selected Interface <ul> <li>0 = no clear (default)</li> <li>1 = active</li> <li>When switched to active, then it depends on bit 8, if a clear event is issued only once, or always when the N channel becomes active.</li> </ul> </li> <li>8 N Trigger Selection <ul> <li>0 = only at next N signal (default)</li> <li>1 = always at N signal</li> <li>The clear event last until the N signal goes inactive again. If earlier termination is desired, i.e. to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |                                                                                                 |

| <ul> <li>Encoder: 50 lines (200 steps per rotation)<br/>(400), for 12800 micro steps (prescaler 64)<br/>(200), for 5200 micro steps (prescaler 32)<br/>(100), for 3200 micro steps (prescaler 32)<br/>(100), for 300 micro steps (prescaler 4)<br/>(020), for 300 micro steps (prescaler 2)<br/>(030), for 200 steps per rotation (prescaler 1)</li> <li>11 N Polarity for Selected Interface<br/>0 = active low (default)<br/>1 = active high<br/>When changing the polarity, please be aware that a single clear on N Event might be<br/>triggered, and thus should not be initiated in the same write access.</li> <li>10 Hold on N for Selected Interface<br/>0 = no hold (default)<br/>1 = active: Encoder counter freezes during 0 channel event.</li> <li>9 Clear on N Event for Selected Interface<br/>0 = no clear (default)<br/>1 = active</li> <li>9 Clear on N Event for Selected Interface</li> <li>8 N Trigger Selection<br/>0 = only at next N signal (default)<br/>1 = always at N signal<br/>The clear event last until the N signal goes inactive again. If earlier termination is desired,<br/>i.e. to preset the encoder counter to a different value, disable "Clear on N" prior to<br/>changing the position register.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |                                                                                                 |

| <ul> <li>(400), for 12800 micro steps (prescaler 32)</li> <li>(100), for 12800 micro steps (prescaler 32)</li> <li>(100), for 3200 micro steps (prescaler 32)</li> <li>(100), for 300 micro steps (prescaler 4)</li> <li>(020), for 400 micro steps (prescaler 2)</li> <li>(010), for 200 steps per rotation (prescaler 1)</li> <li>11 N Polarity for Selected Interface</li> <li>0 = active low (default)</li> <li>1 = active high</li> <li>When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.</li> <li>10 Hold on N for Selected Interface</li> <li>0 = no hold (default)</li> <li>1 = active: Encoder counter freezes during o channel event.</li> <li>9 Clear on N Event for Selected Interface</li> <li>0 = no clear (default)</li> <li>1 = active</li> <li>When switched to active, then it depends on bit 8, if a clear event is issued only once, or always when the N channel becomes active.</li> <li>8 N Trigger Selection</li> <li>0 = only at next N signal (default)</li> <li>1 = always at N signal</li> <li>The clear event last until the N signal goes inactive again. If earlier termination is desired, i.e. to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | (013) <sup>h</sup> for 800 millio steps (prescale) 1.0                                          |

| <ul> <li>(200), for 6400 micro steps (prescaler 32)</li> <li>(200), for 3200 micro steps (prescaler 16)</li> <li>(080), for 1600 micro steps (prescaler 8)</li> <li>(040), for 800 micro steps (prescaler 2)</li> <li>(020), for 200 steps per rotation (prescaler 1)</li> </ul> 11 N Polarity for Selected Interface <ul> <li>0 = active low (default)</li> <li>1 = active high</li> <li>When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.</li> </ul> 10 Hold on N for Selected Interface <ul> <li>0 = no hold (default)</li> <li>1 = active: Encoder counter freezes during 0 channel event.</li> </ul> 9 Clear on N Event for Selected Interface <ul> <li>0 = no clear (default)</li> <li>1 = active</li> <li>When switched to active, then it depends on bit 8, if a clear event is issued only once, or always when the N channel becomes active.</li> </ul> 8 N Trigger Selection <ul> <li>0 = only at next N signal (default)</li> <li>1 = always at N signal</li> <li>The clear event last until the N signal goes inactive again. If earlier termination is desired, i.e. to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |                                                                                                 |

| <ul> <li>(100)<sup>h</sup> for 3200 micro steps (prescaler 16)</li> <li>(080)<sub>h</sub> for 3000 micro steps (prescaler 4)</li> <li>(040)<sub>h</sub> for 800 micro steps (prescaler 2)</li> <li>(010)<sub>h</sub> for 200 steps per rotation (prescaler 1)</li> <li>11</li> <li>N Polarity for Selected Interface         <ul> <li>o = active low (default)</li> <li>1 = active high</li> <li>When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.</li> </ul> </li> <li>10</li> <li>Hold on N for Selected Interface         <ul> <li>o = no hold (default)</li> <li>1 = active: Encoder counter freezes during o channel event.</li> </ul> </li> <li>9</li> <li>Clear on N Event for Selected Interface         <ul> <li>o = no clear (default)</li> <li>1 = active</li> <li>when the N channel becomes active.</li> </ul> </li> <li>8</li> <li>N Trigger Selection         <ul> <li>o = only at next N signal</li> <li>o = only at next N signal</li> <li>The clear event last until the N signal goes inactive again. If earlier termination is desired, <i>i.e.</i> to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.</li> </ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |                                                                                                 |

| <ul> <li>(080)<sup>h</sup>/<sub>h</sub> for 1600 micro steps (prescaler 8)</li> <li>(040)<sup>h</sup>, for 800 micro steps (prescaler 2)</li> <li>(020)<sup>h</sup>, for 200 steps per rotation (prescaler 1)</li> <li>11 N Polarity for Selected Interface</li> <li>0 = active low (default)</li> <li>1 = active high</li> <li>When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.</li> <li>10 Hold on N for Selected Interface</li> <li>0 = no hold (default)</li> <li>1 = active: Encoder counter freezes during 0 channel event.</li> <li>9 Clear on N Event for Selected Interface</li> <li>0 = no clear (default)</li> <li>1 = active</li> <li>When switched to active, then it depends on bit 8, if a clear event is issued only once, or always when the N channel becomes active.</li> <li>8 N Trigger Selection</li> <li>0 = only at next N signal (default)</li> <li>1 = always at N signal</li> <li>The clear event last until the N signal goes inactive again. If earlier termination is desired, <i>i.e.</i> to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |                                                                                                 |

| <ul> <li>(a40)<sup>h</sup> for 800 micro steps (prescaler 4)<br/>(a20)<sub>h</sub> for 200 steps per rotation (prescaler 2)</li> <li>(a10)<sup>h</sup> for 200 steps per rotation (prescaler 1)</li> <li>11 N Polarity for Selected Interface <ul> <li>a = active low (default)</li> <li>1 = active high</li> <li>When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.</li> </ul> </li> <li>10 Hold on N for Selected Interface <ul> <li>o = no hold (default)</li> <li>1 = active: Encoder counter freezes during o channel event.</li> </ul> </li> <li>9 Clear on N Event for Selected Interface <ul> <li>o = no clear (default)</li> <li>1 = active</li> <li>When switched to active, then it depends on bit 8, if a clear event is issued only once, or always when the N channel becomes active.</li> </ul> </li> <li>8 N Trigger Selection <ul> <li>o = only at next N signal (default)</li> <li>1 = always at N signal</li> <li>The clear event last until the N signal goes inactive again. If earlier termination is desired, i.e. to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                                                                                                 |

| (020), for 400 micro steps (prescaler 2)<br>(010), for 200 steps per rotation (prescaler 1)         11       N Polarity for Selected Interface<br>0 = active low (default)<br>1 = active high<br>When changing the polarity, please be aware that a single clear on N Event might be<br>triggered, and thus should not be initiated in the same write access.         10       Hold on N for Selected Interface<br>0 = no hold (default)<br>1 = active: Encoder counter freezes during 0 channel event.         9       Clear on N Event for Selected Interface<br>0 = no clear (default)<br>1 = active<br>When switched to active, then it depends on bit 8, if a clear event is issued only once, or<br>always when the N channel becomes active.         8       N Trigger Selection<br>0 = only at next N signal (default)<br>1 = always at N signal<br>The clear event last until the N signal goes inactive again. If earlier termination is desired,<br>i.e. to preset the encoder counter to a different value, disable "Clear on N" prior to<br>changing the position register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |                                                                                                 |

| <ul> <li>(010)<sub>h</sub> for 200 steps per rotation (prescaler 1)</li> <li>N Polarity for Selected Interface         <ul> <li>active low (default)</li> <li>active high</li> <li>When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.</li> </ul> </li> <li>Hold on N for Selected Interface         <ul> <li>o = no hold (default)</li> <li>active: Encoder counter freezes during o channel event.</li> </ul> </li> <li>Clear on N Event for Selected Interface         <ul> <li>o = no clear (default)</li> <li>active</li> <li>When switched to active, then it depends on bit 8, if a clear event is issued only once, or always when the N channel becomes active.</li> </ul> </li> <li>N Trigger Selection         <ul> <li>o = only at next N signal (default)</li> <li>always at N signal</li> <li>The clear event last until the N signal goes inactive again. If earlier termination is desired, <i>i.e.</i> to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.</li> </ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |                                                                                                 |

| <ul> <li>o = active low (default)         <ol> <li>active high</li> <li>When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.</li> </ol> </li> <li>Hold on N for Selected Interface         <ol> <li>no hold (default)</li> <li>active: Encoder counter freezes during o channel event.</li> </ol> </li> <li>Clear on N Event for Selected Interface         <ol> <li>no clear (default)</li> <li>active</li> <li>when switched to active, then it depends on bit 8, if a clear event is issued only once, or always when the N channel becomes active.</li> </ol> </li> <li>N Trigger Selection         <ol> <li>o = only at next N signal (default)</li> <li>always at N signal</li> <li>The clear event last until the N signal goes inactive again. If earlier termination is desired, i.e. to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.</li> </ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | (010) <sub>h</sub> for 200 steps per rotation (prescaler 1)                                     |

| 1 = active high         When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.         10       Hold on N for Selected Interface         0 = no hold (default)         1 = active: Encoder counter freezes during o channel event.         9       Clear on N Event for Selected Interface         0 = no clear (default)         1 = active         When switched to active, then it depends on bit 8, if a clear event is issued only once, or always when the N channel becomes active.         8       N Trigger Selection         0 = only at next N signal (default)         1 = always at N signal         The clear event last until the N signal goes inactive again. If earlier termination is desired, i.e. to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 | ,                                                                                               |

| When changing the polarity, please be aware that a single clear on N Event might be triggered, and thus should not be initiated in the same write access.         10       Hold on N for Selected Interface         0 = no hold (default)       1 = active: Encoder counter freezes during o channel event.         9       Clear on N Event for Selected Interface         0 = no clear (default)       1 = active         1 = active       When switched to active, then it depends on bit 8, if a clear event is issued only once, or always when the N channel becomes active.         8       N Trigger Selection         0 = only at next N signal (default)         1 = always at N signal         The clear event last until the N signal goes inactive again. If earlier termination is desired, i.e. to preset the encoder counter to a different value, disable "Clear on N" prior to changing the position register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |                                                                                                 |