#### SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

#### **FEATURES**

**GENERAL FEATURES**

- Six independent 3/1.5Gbps SATA ports.

- Connects 2 host ports to 4 device ports.

- Supports 3/1.5Gbps rate detection/speed negotiation.

- Supports power down modes Active, partial, slumber and power down.

- Advanced features configurable through MDIO bus.

PORT MULTIPLIER/SELECTOR LOGIC FEATURES

- Low latency architecture.

- Supports OOB signaling for SATA applications. Internal OOB detectors for COMRESET/ COMINIT and COMWAKE.

#### **I/O FEATURES**

- High speed outputs with programmable preemphasis to drive long interconnects.

- Selectable high speed input equalization for optimum reception.

- Compliant with SATA Gen-2i & Gen-2m specification.

- Enables reliable data transmission over 1 meter or more of FR-4 and 4 meters or more of unequalized copper cable.

- Selectable spread spectrum clocking (SSC) to reduce EMI.

**PHYSICAL FEATURES**

- CMOS 0.13 Micron Technology

- Single 1.2 V Power Supply

- -40℃ to 85℃ Industrial Temperature Range

- No heatsink or airflow required

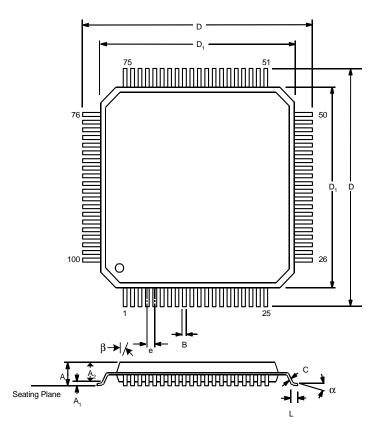

- 100-Pin LQFP Package

#### **1.0 INTRODUCTION**

The XRS10L240 provides the combined advantages of the Serial ATA II Port Selector and Port Multiplier implementations for Serial ATA II systems at 3.0 Gbps and 1.5 Gbps. Combining the capability to address four Serial ATA devices from one external link with support for a failover path from two independent hosts, the XRS10L240 offers a leading solution for propagation of high data rate Serial ATA products in a wide variety of applications. The integration of Serial ATA PHY links, a variety of digital logic capabilities, rate adjust FIFOs, integrated lowcost clock oscillator support, test and loopback features is achieved in a low cost and lower power implementation.

The port selector function is used when dual hosts, such as I/O controllers, must access single-port disk drives in high availability storage subsystems where redundancy and load sharing are important. The outputs from the I/O controllers are multiplexed to a Serial ATA drive through the port selector block of the Active/passive port selector XRS10L240. in XRS10L240 allows two different host ports to connect to the same target in order to create a redundant path to that target. In combination with RAID, the XRS10L240 allows system providers to build fully redundant solutions. This avoids the presence of a single point of failure, and enables a fail-over path in the case of host failure.

This port multiplier function is used when one active host has to communicate with multiple SATA drives. The XRS10L240 supports up to 4 SATA drives and utilizes the full bandwidth of the host connection.

The XRS10L240 includes enhanced features such as staggered HDD spin-up, power management control, hot plug capability and support for legacy software. The XRS10L240 acts as a retimer, maintaining independent signaling domains between the drives, hosts and the external interconnect.

The high-speed serial input feature: selectable equalization and the high-speed serial output feature: programmalbe pre-emphasis can be used to compensate for ISI (Inter-Symbol Interference) and increase maximum cabling distances.

XRS10L240 meets tight jitter budgets in SATA applications. Exar's serial I/O technology enables reliable data transmission over 1 meter or more of FR-4 and 4 meters or more of unequalized copper cable.

Host and drive port speeds can be mixed and matched, based upon inherent data rate negotiation present in the SATA II specifications.

The MDIO bus allows simple configuration of the XRS10L240 when needed. Receive equalization, transmit amplitude and pre-emphasis and SSC control are all configurable via the 2-wire MDIO interface.

#### SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

To summarize, the port multiplier functionality in the XRS10L240 allows the system designer to increase the number of serial ATA connections in an enclosure that does not have a sufficient number of serial ATA connections for all of the drives in the enclosure. The port selector functionality in the XRS10L240 allows replacement for expensive Fibre Channel drives with cost effective and high capacity SATA drives in enterprise class applications without compromising on redundancy or performance.

#### STANDARDS COMPLIANCE

The XRS10L240 is compliant with the following industry specifications:

- Serial ATA, Revision 1.0a

- Serial ATA II: Extensions to Serial ATA 1.0a, Revision 1.2

- Serial ATA II PHY Electrical Specifications, Revision 1.0

- Serial ATA II: Port Selector, Revision 1.0

- Serial ATA II: Port Multiplier, Revision 1.2

- Serial ATA II: Revision 2.6

#### **APPLICATIONS**

- Serial ATA Enclosures

- Other Serial ATA link replicator applications

- · Buffers for externally connected links

- High density storage boxes

- RAID Subsystems

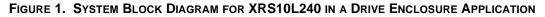

#### APPLICATION EXAMPLE

The XRS10L240 is ideally suited for use within an external drive enclosure as a means of providing redundant host access to ensure system availability and reliability, while enabling access to up to four target devices per XRS10L240. This application is shown in **Figure 1**. Other applications for the XRS10L240 include use in fixed-content or network attached storage systems, storage arrays, desktop applications or entry-level servers, RAID storage or disk-to-disk backup.

### SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

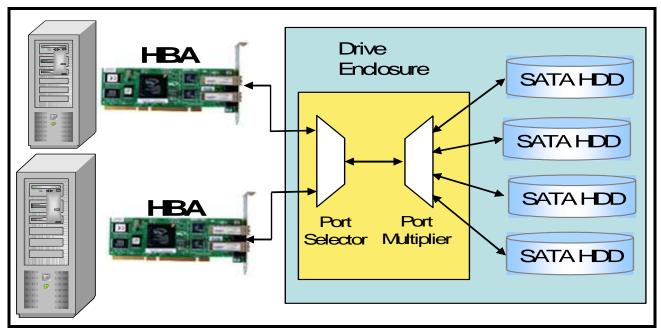

#### FIGURE 2. PINOUT OF THE XRS10L240

REV. 1.05

# SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

#### 2.0 PIN DESCRIPTIONS

| Pin Name              | Pin Number | I/O       |                      | DESCRIPTION                                                                                                                   |

|-----------------------|------------|-----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------|

|                       |            |           | DATA INT             | ERFACE                                                                                                                        |

| SOTP0/SOTN0           | 68, 69     |           | CML                  |                                                                                                                               |

| SOTP1/SOTN1           | 57, 56     | 0         | AC<br>Coupled        | Serial ATA Output Transmitters. These ports communicate                                                                       |

| SOTP2/SOTN2           | 8, 7       |           | Coupled              | from the XRS10L240 to downstream devices                                                                                      |

| SOTP3/SOTN3           | 19, 20     |           |                      |                                                                                                                               |

| SORP0/SORN0           | 65, 66     |           |                      |                                                                                                                               |

| SORP1/SORN1           | 60, 59     |           |                      | Serial ATA Input Receivers. These ports receive signals                                                                       |

| SORP2/SORN2           | 11, 10     |           |                      | from downstream devices                                                                                                       |

| SORP3/SORN3           | 16, 17     |           |                      |                                                                                                                               |

| SITP0/SITN0           | 93, 94     |           |                      | Serial ATA Output Transmitters. These ports communicate                                                                       |

| SITP1/SITN1           | 82, 81     | 0         |                      | from the XRS10L240 to upstream hosts.                                                                                         |

| SIRP0/SIRN0           | 90, 91     |           |                      | Serial ATA Input Receivers. These ports receive signals                                                                       |

| SIRP1/SIRN1           | 85, 84     | I         |                      | from upstream hosts.                                                                                                          |

|                       |            |           |                      | TERFACE                                                                                                                       |

| CMU_REFP/<br>CMU_REFN | 46,<br>47  | I         | CML<br>AC<br>Coupled | Reference clock input                                                                                                         |

| XOD                   | 43         | 0         | Analog               | Crystal oscillator output                                                                                                     |

| XOG                   | 44         | I         | Analog               | Crystal oscillator input, 1.26V max                                                                                           |

|                       |            |           |                      | ACE SIGNALS                                                                                                                   |

| MDC                   | 3          | Ι         | LVCMOS               | MDIO clock input, +3.3V LVCMOS                                                                                                |

| MDIO                  | 5          | I/O       | LVCMOS               | MDIO data port, +3.3V LVCMOS. Open drain                                                                                      |

|                       |            |           | JTAG Interfa         | ace Signals                                                                                                                   |

| ТСК                   | 96         | I         | LVCMOS               | JTAG test clock, +3.3V LVCMOS                                                                                                 |

| TDI                   | 100        | I         |                      | JTAG test data in, +3.3V LVCMOS                                                                                               |

| TDO                   | 99         | 0         |                      | JTAG test data out, +3.3V LVCMOS. Open drain. If used to daisy chain JTAG devices, pull up externally using 3.3KOhm resistor. |

| TMS                   | 97         | I         |                      | JTAG mode select, +3.3V LVCMOS                                                                                                |

| TRST                  | 1          | I         |                      | JTAG test reset, +3.3V LVCMOS. Pull low externally using 3.3KOhm resistor for normal operation of the device.                 |

|                       | Gene       | RAL CONTR | OL AND CONF          | IGURATION SIGNALS (CMOS)                                                                                                      |

| RBIAS                 | 49         | I         | Analog               | Connection point for calibration termination resistor.                                                                        |

| RESETB                | 75         | I         | LVCMOS               | Active low reset pin, +3.3V LVCMOS.                                                                                           |

#### TABLE 1: XRS10L240 PIN DESCRIPTIONS

# SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

#### TABLE 1: XRS10L240 PIN DESCRIPTIONS

| Pin Name          | Pin Number                                                                           | I/O |                      | DESCRIPTION                                                                                                                                                        |

|-------------------|--------------------------------------------------------------------------------------|-----|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWRDNB            | 52                                                                                   | Ι   | LVCMOS               | Active low power down signal for chip, +3.3V LVCMOS.                                                                                                               |

| DRACT[3:0]        | 71, 72, 73, 74                                                                       | 0   | LVCMOS               | Drive activity port for external LED. Active Low, 3.3V LVC-MOS, open drain                                                                                         |

| HBACT             | 76                                                                                   | 0   | LVCMOS               | 0 = Host 0 selected (status)<br>1 = No Host is selected (status)<br>0-1-0-1 Toggle (with 1 sec stay at each state) indicates<br>Host 1 is selected.<br>3.3V LVCMOS |

| PS_SIDEBAND_<br>B | 77                                                                                   | -   | LVCMOS               | +3.3V LVCMOS<br>Please refer to Table 2, "Host Port Selection," on<br>page 7                                                                                       |

| PORTSEL           | 2                                                                                    | I   | LVCMOS               | Port selector external input pin when this mode is set in<br>the register. Low selects host port 0, otherwise port 1.<br>+3.3V LVCMOS                              |

|                   |                                                                                      |     | TEST                 | Pin                                                                                                                                                                |

| ANTEST            | 51                                                                                   | 0   | Analog               | Analog test pin                                                                                                                                                    |

| CLKSTN/<br>CLKSTP | 24, 25                                                                               | 0   | CML<br>AC<br>Coupled | Output clock test pin                                                                                                                                              |

|                   |                                                                                      |     | RESERVE              | D PINS                                                                                                                                                             |

| NC                | 27, 28, 30, 31,<br>36, 37, 39, 40                                                    |     |                      | No Connect                                                                                                                                                         |

| SCANMODE          | 41                                                                                   | I   | LVCMOS               | For factory use only. connect to ground.                                                                                                                           |

|                   |                                                                                      | Po  | WER AND GRO          | DUND SIGNALS                                                                                                                                                       |

| VDD               | 9, 18, 23, 29,<br>38, 54, 58, 67,<br>79, 83, 92, 98                                  | I   |                      | 1.2V supply.                                                                                                                                                       |

| VDDA              | 14, 34, 45, 50,<br>62, 87                                                            | I   |                      | 1.2V Analog supply.                                                                                                                                                |

| VSS               | 4, 6, 12, 15, 21,<br>22, 26, 32, 35,<br>53, 55, 61, 64,<br>70, 78, 80, 86,<br>89, 95 | I   |                      | Ground.                                                                                                                                                            |

| VSSA              | 13, 33, 42, 48,<br>63, 88                                                            | Ι   |                      | Analog Ground.                                                                                                                                                     |

SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

| TABLE | 2: | Host | PORT | SELECTION |

|-------|----|------|------|-----------|

|-------|----|------|------|-----------|

| HARD                        | WARE PINS                                                | REGISTER S          | ETTINGS - REGIS      | STER 0.009A                                                       | Comments                                             |

|-----------------------------|----------------------------------------------------------|---------------------|----------------------|-------------------------------------------------------------------|------------------------------------------------------|

| PS_SIDEBAND_<br>B<br>Pin 77 | PORTSEL<br>Pin 2                                         | P_SEL_MTHD<br>BIT 0 | P_SIDE_MTHD<br>BIT 1 | P_HOST_SEL<br>BIT 2                                               | 3.3V LVCMOS                                          |

| 0                           | "Selects host port<br>0 = Host port 0<br>1 = Host port 1 | x                   | 0                    | x                                                                 | Host port is selected by hard-<br>ware PORTSEL pin   |

| x                           | "Selects host port<br>0 = Host port 0<br>1 = Host port 1 | 1                   | 0                    | x                                                                 | Host port is selected by hard-<br>ware PORTSEL pin   |

| 0                           | x                                                        | x                   | 1                    | "Selects host<br>port<br>0 = Host port<br>0<br>1 = Host port<br>1 | "Host port is selected by register<br>0x0.009A bit 2 |

| x                           | X                                                        | 1                   | 1                    | "Selects host<br>port<br>0 = Host port<br>0<br>1 = Host port<br>1 | "Host port is selected by register<br>0x0.009A bit 2 |

| 1                           | х                                                        | 0                   | х                    | x                                                                 | Host port is selected by protocol based selection    |

# 3.0 FUNCTIONAL DESCRIPTION

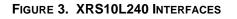

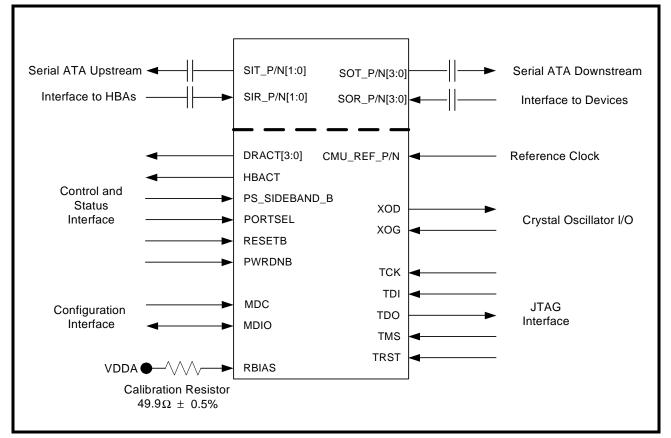

A top-level view of the XRS10L240 is shown in Figure 3 outlining the interfaces to the device and the required support components. The data path can be seen at the top of the device. This includes the two output transmit and input receive paths at the top left, providing the upstream interface to the host, and the four output transmit and input receive paths at the top right, providing the downstream interface to the target devices. The clocking, control, and configuration interfaces are shown below the dotted line.

The XRS10L240 incorporates identical instantiations of a dual-channel Serial ATA II 3 Gbps PHY macro. This common building block provides a uniform implementation with common characteristics and a common register map, but provides a functional implementation of independent PHY blocks. Digital logic implementations of Serial ATA link layer blocks along with port selector and port multiplier logic provide the remainder of the data path within the XRS10L240. In addition, management and control interfaces including an

#### REV. 1.05

#### SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

MDIO interface for register control, a JTAG interface for boundary scan purposes, and a resistor calibration circuit complete the device. A block diagram of the XRS10L240 is shown in Figure 4.

#### SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

# Powering Connectivity REV. 1.05

### 3.1 Out Of Band Feature

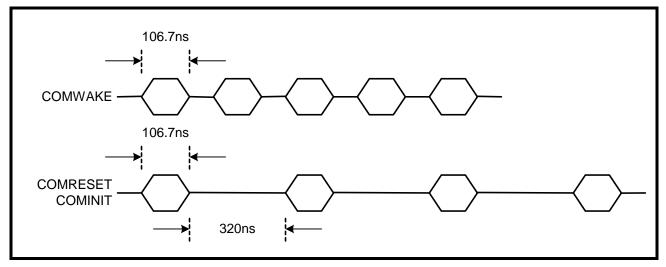

Each Serial ATA link provides full support for the three Out Of Band (OOB) signals supported by Serial ATA: COMRESET, COMINIT and COMWAKE. These sequences must be separated by idle periods as shown in **Figure 5**. The sequences are comprised of 106.7ns bursts of activity that are interleaved with varying length stretches of electrical idle. This alternating sequence must be repeated four times to be recognized.

#### FIGURE 5. COMWAKE AND COMRESET/COMINIT SEQUENCES

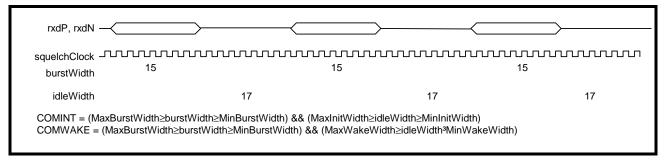

An example OOB sequence and the resulting burst and idle widths are shown in **Figure 6**. If the sequence of burstWidth and idleWidth counts falls within the range specified in the MDIO registers for four consecutive burst/idle sequences, then the link will assert COMINIT or COMWAKE. This OOB signal will remain asserted for as long as the corresponding sequence on the input pins continues.

#### FIGURE 6. EXAMPLE OOB SEQUENCE

REV. 1.05

# 3.2 Power Down Modes

The XRS10L240 features independent support for the 3 power modes, as follows:

- Active: All parts of the link are active. All power-down signals are de-asserted.

- Partial: In partial mode, the input and output pipelines are shut down, but the PLL and the OOB generation circuits are active.

- Slumber: In slumber mode, the PLL is also shut down, saving additional power but adding latency on exit.

The XRS10L240 transceiver components (transmitter, receive CDR, PLL, etc.) can be powered down through MDIO register settings. Please refer to Table 14, "Powerdown Registers (MDIO Devices 1, 2 & 3)," on page 29

Please refer to "XRS10L240/140 Errata Sheet" for details regarding Link Power Management.

# 3.3 Speed Negotiation

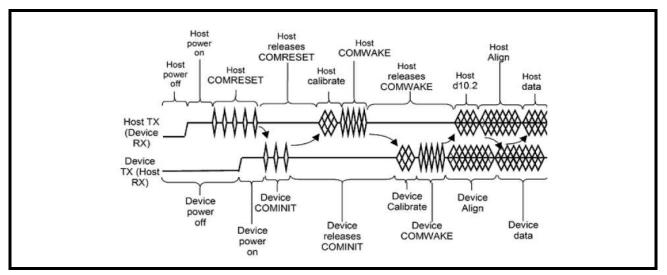

The XRS10L240 will automatically perform speed negotiation with the host and devices in order to verify whether the second generation Serial ATA 3.0 Gbps data rate is available or whether the system will need to fall back upon the first generation Serial ATA 1.5 Gbps data rate. Speed negotiation is performed on an independent basis by each of the dual-channel macros. Speed negotiation is done independently on all host and device ports by default. MDIO configuration can request a common negotiated speed on the host and device ports if such a speed exists. To perform speed negotiation with a downstream device, the XRS10L240 will first perform a COMRESET/COMINIT handshake with the device and then performs a calibrate/COMWAKE handshake. Following receipt of the device ALIGN primitive. Depending on the speed of the ALIGN primitive, the XRS10L240 will be able to determine the PHY generation of the device, and provide the appropriate 1.5 Gbps or 3.0 Gbps ALIGN primitive in return to the device, thus completing speed negotiation. This process is outlined in Figure 7.

#### FIGURE 7. SERIAL ATA SPEED NEGOTIATION

For speed negotiation with an upstream host, after the COMRESET/COMINIT and COMWAKE handshake is complete, the XRS10L240 will initially send out an ALIGN primitive at the 2nd generation 3.0 Gbps data rate. If no confirming 3.0 Gbps ALIGN primitive is received from the host, the XRS10L240 will then step down and attempt negotiation at the lower 1.5 Gbps data rate.

# 3.4 Port selector Implementation

#### SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

The XRS10L240 provides full support for the Serial ATA II Port Selector specification. A Serial ATA Port Selector is a mechanism that allows two different host ports to connect to the same device in order to create a redundant path to that device. Only one host connection to the device is active at a time.

The two host ports are responsible for coordination of access to the XRS10L240 by one of two separate means: protocol-based port selection or sideband port selection. Each method is described in detail in the next two sections.

#### 3.4.1 Protocol Based Port Selection

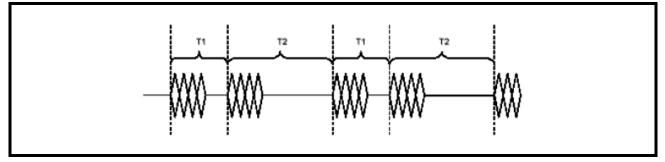

Protocol-based port selection makes use of a sequence of Serial ATA OOB signals to select the active host port. The port selection signal is based on a pattern of COMRESET OOB signals transmitted from the host to the XRS10L240. The port selection signal is composed of a series of COMRESET signals with the timing from one COMRESET signal to the next as shown in Table 3 and Figure 8. The XRS10L240 selects the port, if inactive, on the de-assertion of COMRESET after receiving two complete back-to-back sequences with this defined inter-burst spacing. This can also be identified as two sequences of two COMRESET intervals comprising a total of five COMRESET bursts with four inter-burst delays. Once a port is designated as active, reception of additional COMRESET signals is propagated directly to the device, even if the COMRESET signals.

Note that when protocol based selection mode has been enabled, following the initial hardware reset, a single COMRESET burst will select the active host port. After this initial host port selection, only COMRESET OOB observing the protocol timing given below will change the active host.

TABLE 3: PORT SELECTOR SIGNAL INTER-RESET TIMING REQUIREMENTS

|    | NOMINAL | Min. | ΜΑΧ | Units | Comments                                                               |

|----|---------|------|-----|-------|------------------------------------------------------------------------|

| T1 | 2.0     | 1.6  | 2.4 | ms    | Inter-reset assertion delay for first event of the selection sequence  |

| T2 | 8.0     | 7.6  | 8.4 | ms    | Inter-reset assertion delay for second event of the selection sequence |

FIGURE 8. PORT SELECTION SIGNAL - TRANSMITTED COMRESET SIGNALS

#### 3.4.2 Sideband Based Port Selection

The XRS10L240 also features support for a sideband port selection mechanism. This is implemented using a combination of the MDIO register settings and device pins including PS\_SIDEBAND\_B and PORTSEL. Refer to Table 2 for a sideband port selection settings.

#### 3.5 Port Multiplier Implementation

The XRS10L240 provides full support for the functionality outlined in the Serial ATA II Port Multiplier specification. This Port Multiplier functionality follows the Port Selector implementation, and only one link can be active at any time.

A Serial ATA II Port Multiplier is a mechanism for one active host connection to communicate with multiple devices. A Port Multiplier is conceptually a simple multiplexer in which one active host connection is multiplexed to multiple device connections.

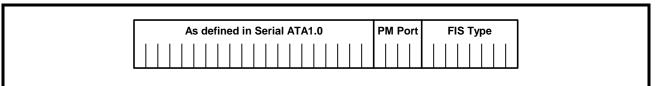

The XRS10L240 uses four bits, known as the PM Port field in all Serial ATA frame types, to route frames between the selected host and the appropriate device. PM ports 0 through 3 are valid device ports within the 4-output XRS10L240, while PM port 15 is designated for communication between the host and the XRS10L240 itself. For host-to-device transactions, the PM Port field is designated by the host in order to specify which device the frame is intended for. For device-to-host transactions, the XRS10L240 fills in the PM Port field with the port address of the device that is transmitting the frame.

The PM Port field is defined in the Serial ATA port multiplier specification to be the first 32-bit Dword in the Frame Information Structure (FIS) for all FIS types, as shown in Figure 9.

#### FIGURE 9. PORT SELECTION SIGNAL - TRANSMITTED COMRESET SIGNALS

#### 3.5.1 Transmission from a host to a device

A host indicates the target device for receipt of a transmitted frame by setting the PM Port field in the frame to the device's port address. When an XRS10L240 receives a frame as selected from one of the two available hosts by the port selector, it checks the PM Port field in the frame to determine which port address should be used. If the frame is set for transmission to the control port (15), the XRS10L240 receives the frame and performs the command or operation requested. If the frame is designated for a device port, the XRS10L240 obeys the following procedure:

- 1. The XRS10L240 first determines if the device port is valid. If the device port is not valid, the XRS10L240 will issue a SYNC primitive to the host and terminate reception of the frame.

- 2. The XRS10L240 determines if the X bit is set in the device port's PSCR[1] (SError) register. If the X bit is set, the XRS10L240 issues a SYNC primitive to the host and terminates reception of the frame.

- 3. The XRS10L240 determines if a collision has occurred. A collision occurs when a reception is already in progress from the device that the host wants to transmit to. If a collision has occurred, the XRS10L240 will finish receiving the frame from the host and will then issue an R\_ERR primitive to the host as the ending status. The XRS10L240 will then discard the frame, but will not return an R\_RDY primitive to the host until the frame from the affected device port has been transmitted to the host, thus indicating to the host when it can retry to send the frame. The transmission from the device will proceed as requested, as the device will always take collision precedence over the host.

- 4. The XRS10L240 initiates a transfer with the device by issuing an X\_RDY primitive to the device. A collision may occur as the XRS10L240 is issuing the X\_RDY to the device if the device has started transmitting an X\_RDY primitive to the XRS10L240, indicating a decision to start a transmission to the host. In this case, the XRS10L240 will finish receiving the frame from the host and then issue an R\_ERR primitive to the host to indicate an unsuccessful transmission. The transmission from the device will proceed as requested, as the device will always take collision precedence over the host.

- 5. After the device issues an R\_RDY primitive to the XRS10L240, the XRS10L240 will transmit the frame from the host to the device. The XRS10L240 will not send an R\_OK status primitive to the host until the device has issued an R\_OK primitive to indicate successful frame reception. In this way, the R\_OK status handshake is interlocked from the device to the host.

If an error is detected during any part of the frame transfer, the XRS10L240 will ensure that the error condition is propagated to the host and the device. If no error occurs during frame transfer, the XRS10L240 will not alter the contents of the frame, or modify the CRC in any way.

#### 3.5.2 Transmission from a device to a host

A device indicates a transmit to a host in the same way as would be done if the host and device were attached directly. This transaction obeys the following procedure:

- 1. After receiving an X\_RDY primitive from the device, the XRS10L240 will determine if the X bit is set in the device port's PSCR[1] (SError) register. The XRS10L240 will not issue an R\_RDY primitive to the device until this bit is cleared to zero.

- 2. The XRS10L240 will then receive the frame from the device. The XRS10L240 will fill in the PM Port field with the port address of the transmitting device. The XRS10L240 will then check the CRC received from the device, and if valid, it will recalculate the CRC based upon the new PM Port field. If the CRC calculated from the device is incorrect, the XRS10L240 will corrupt the CRC sent to the host to ensure propagation of the error condition

- **3.** The XRS10L240 will issue an X\_RDY primitive to the host to start the transmission of the frame to the host. After the host issues an R\_RDY primitive to the XRS10L240, the frame from the device, with the updated CRC, will then be transmitted to the host. The XRS10L240 will not send an R\_OK status primitive to the device until the host has issued an R\_OK primitive to indicate successful frame reception. In this way, the R\_OK status handshake will be interlocked from the device to the host.

If an error is detected during any part of the frame transfer, the XRS10L240 will ensure that the error condition is propagated to the host and the device.

#### 3.6 Clocking

The XRS10L240 allows the use of either an external reference clock or of a low cost crystal oscillator to act as a reference clock. Separate device inputs are available for each approach, with full rate reference clock inputs provided on pins CMU\_REFP and CMU\_REFN, and crystal oscillator inputs provided on pins XOD and XOG. Supported data rates and their appropriate PLL divide factors are outlined in Table 4.

| Mode        | Sysclk | /REF | /FB | DINCLK<br>RXCLK | SERIAL<br>CLOCK | Data<br>Rate |

|-------------|--------|------|-----|-----------------|-----------------|--------------|

| SATA Gen. 2 | 25MHz  | 1    | 60  | 300MHz          | 1.5GHz          | 3.0Gbps      |

| SATA Gen. 2 | 50MHz  | 1    | 30  | 300MHz          | 1.5GHz          | 3.0Gbps      |

| SATA Gen. 2 | 75MHz  | 1    | 20  | 300MHz          | 1.5GHz          | 3.0Gbps      |

| SATA Gen. 2 | 100MHz | 2    | 30  | 300MHz          | 1.5GHz          | 3.0Gbps      |

| SATA Gen. 2 | 150MHz | 1    | 10  | 300MHz          | 1.5GHz          | 3.0Gbps      |

#### TABLE 4: PLL DIVIDE FACTORS

**NOTE:** \* All link start with 3.0Gbps, then negotiate down to 1.5Gbps for SATA Generation 1 devices.

#### 3.6.1 Spread Spectrum Clocking

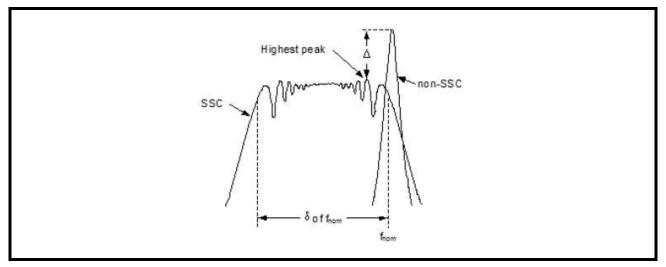

The XRS10L240 provides full support for receipt and generation of signals that have been configured for Spread Spectrum Clocking (SSC) support. The spread technique is implemented by down-spreading the data rate by 0.5% as a means of reducing EMI. Generation of the down-spread clock is performed within the XRS10L240. An example of the resultant spectral fundamental frequency before and after SSC can be seen in Figure 10.

# Powering Connectivity REV. 1.05

# 4.0 ELECTRICAL SPECIFICATIONS

This section contains the electrical specifications for the XRS10L240.

#### 4.1 Serial ATA Specifications

The XRS10L240 electrical transmit and receive specifications are outlined in this section. The XRS10L240 is fully compliant to the Serial ATA II specification for Gen2i, Gen2x, Gen2m, Gen1i, Gen1x and Gen1m variations at 3.0 and 1.5 Gbps.

#### 4.1.1 Serial ATA Transmitter

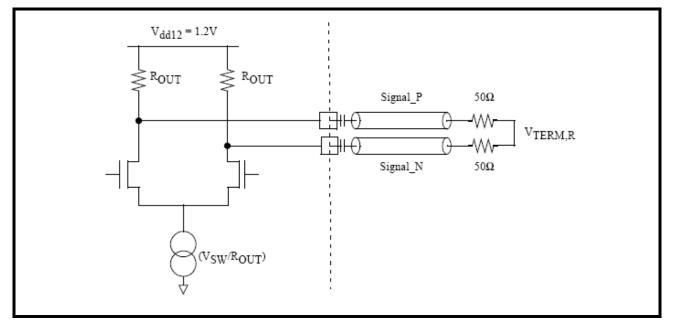

A simplified version of the output circuit and test fixture for each of the 6 Serial ATA transmit output pairs on the XRS10L240 is shown in Figure 11. The output differential pair is terminated to the supply VDD. The circuit is designed to be AC coupled.

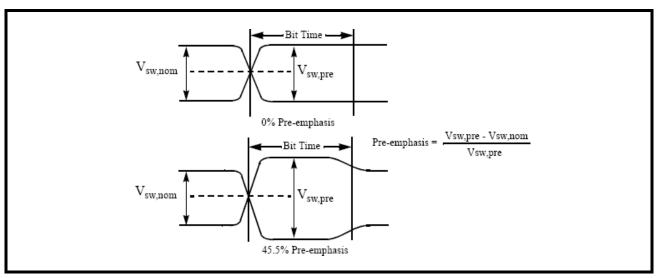

The XRS10L240 Serial ATA outputs include a simple one-tap equalizer, that is useful in driving longer printed circuit traces and is a required component in second generation Serial ATA PHYs. This equalizer preemphasizes the output signal whenever there is a data transition. The amount of pre-emphasis can vary between 0 and 45.5%, and is configured via MDIO register settings. Note that pre-emphasis doesn't increase the overall swing, but instead reduces the output amplitude when there is no transition.

# FIGURE 12. EFFECTS OF TRANSMIT PRE-EMPHASIS

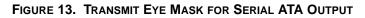

The overall swing level can also be modified via MDIO register settings. The XRS10L240 transmit mask is shown in Figure 13.

#### SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

#### 4.1.2 Serial ATA Receiver

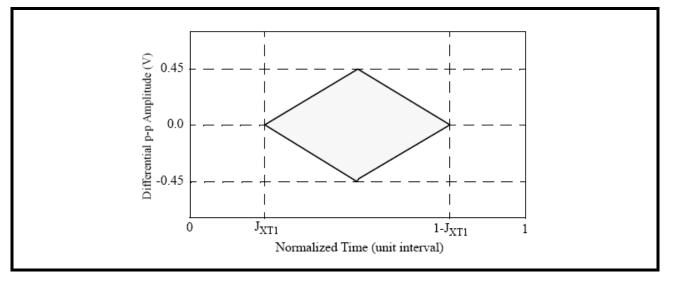

An equivalent circuit for the XRS10L240 Serial ATA inputs is shown in Figure 14. The device receiver mask is shown in Figure 15. This circuit is designed to be AC coupled. The termination resistors are not connected during power-up

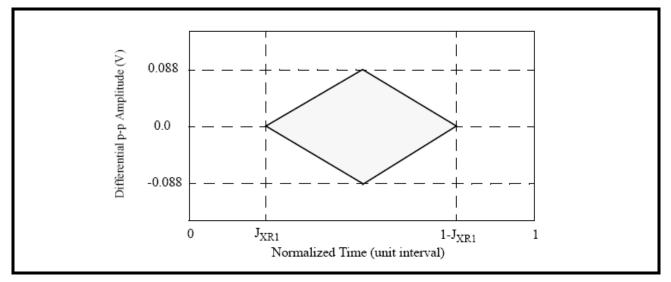

FIGURE 15. RECEIVE EYE MASK FOR SERIAL ATA INPUT

#### SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

#### TABLE 5: SERIAL ATA LINK SPECIFICATIONS

| ΝΑΜΕ                             | DESCRIPTION                                        | Min.  | Nom | Мах  | Units |

|----------------------------------|----------------------------------------------------|-------|-----|------|-------|

| t <sub>BIT,XS</sub>              | Bit Time                                           | 670   | -   | 333  | ps    |

| J <sub>XR1</sub>                 | Input Jitter Tolerance Mask at signal crossover    | 0.32  | -   | -    | UI    |

| J <sub>XR1,DJ</sub>              | Deterministic jitter tolerance at signal crossover | 0.18  | -   | -    | UI    |

| J <sub>XT1</sub>                 | Output jitter mask at signal crossover             | -     | -   | 0.15 | UI    |

| J <sub>XT1,DJ</sub>              | Deterministic output jitter at signal crossover    | -     | -   | 0.07 | UI    |

| t <sub>R</sub> /t <sub>F</sub>   | Input signal rise/fall times (20% - 80%)           | 0.2   | -   | 0.46 | UI    |

| t <sub>QR</sub> /t <sub>QF</sub> | Output signal rise/fall times (20% - 80%)          | 0.2   | -   | 0.41 | UI    |

| t <sub>TOL,RX</sub> 1            | RX to sysclock frequency offset tolerance          | -5350 | 0   | 350  | ppm   |

| V <sub>IN</sub>                  | Input swing, differential peak-peak                | 175   | -   | 1600 | mV    |

| V <sub>SW</sub> <sup>2</sup>     | Output swing, differential peak-peak               | 800   | -   | 1200 | mV    |

| V <sub>IN,IDLE</sub>             | No swing detection threshold                       | 65    | 120 | 155  | mV    |

| R <sub>IN,DIFF</sub>             | Differential mode input resistance                 | 85    | 100 | 115  | Ω     |

| R <sub>IN,CM</sub> <sup>3</sup>  | Common mode input resistance                       | 40    | 50  | 60   | Ω     |

| R <sub>IN,OFF</sub>              | Common mode input resistance, no power             | 200   | -   | -    | kΩ    |

| R <sub>IN,XS</sub>               | Output termination resistance                      | 40    | 50  | 60   | Ω     |

| S <sub>11,IN,DIFF</sub>          | Differential input return loss, 50MHz - 1.5GHz     | 12    | -   | -    | dB    |

| S <sub>11,IN,CM</sub>            | Common mode input return loss 50MHz-1.5GHz         | 6     | -   | -    | dB    |

| S <sub>22,OUT,DIFF</sub>         | Differential output return loss 50MHz-1.5GHz       | 12    | -   | -    | dB    |

| S <sub>22,OUT,CM</sub>           | Common mode output return loss 50MHz-1.5GHz        | 6     | -   | -    | dB    |

| t <sub>S,REG</sub>               | Setup time for register port                       | 1.5   | -   | -    | ns    |

| t <sub>H,REG</sub>               | Hold time for register port                        | 1.5   | -   | -    | ns    |

| t <sub>Q,REG</sub>               | Clock to Q time for register port                  | 0     | -   | 2    | ns    |

| t <sub>CYC,REG</sub>             | Register port clock cycle time                     | 10    | -   | -    | ns    |

| t <sub>HI,REG</sub>              | R register port clock high time                    | 4     | -   | -    | ns    |

| t <sub>LO,REG</sub>              | Register port clock low time                       | 4     | -   | -    | ns    |

| t <sub>RF,REG</sub>              | Register port input rise/fall time                 | -     | -   | 0.5  | ns    |

NOTES:

1. This value includes 0.5% downspread Spread Spectrum clocking, plus 350ppm tolerance around the center frequency.

2. This is measured at the package ball and does not include any board or connector loss.

3. This value can be as low as  $5\Omega$  during power on.

#### SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

#### 4.2 CMOS Interface

AC and DC specifications for the CMOS inputs and outputs are listed in Table 6. Since all these signals are asynchronous, there are no setup or hold times defined. The CMOS pins are defined in the General Control and Configuration portion of Table 1 in Section 3, "Pin Descriptions".

| NAME                                    | DESCRIPTION                                    | MIN  | Nом | ΜΑΧ | Units |

|-----------------------------------------|------------------------------------------------|------|-----|-----|-------|

| t <sub>DR</sub> /t <sub>DF,CMOS</sub>   | CMOS input signal rise/fall times (20% - 80%)  | 0.2  | -   | 5   | ns    |

| t <sub>QR</sub> /t <sub>QF,CMOS</sub> 1 | CMOS output signal rise/fall times (20% - 80%) | 0.2  | -   | 5   | ns    |

| V <sub>IL,CMOS</sub>                    | CMOS input low voltage                         | -0.3 | 0   | 0.8 | V     |

| V <sub>IH,CMOS</sub>                    | CMOS input high voltage                        | 1.7  | 3.3 | 3.6 | V     |

| V <sub>OL,CMOS</sub>                    | CMOS output low voltage                        | -0.3 | 0   | 0.4 | V     |

| V <sub>PULLUP</sub>                     | Open Drain Pull-up Voltage                     | 2.3  | -   | 3.6 | V     |

| I <sub>OL,CMOS</sub>                    | Output current for VOL = 0.4V                  | 10   | -   | 20  | mA    |

| dl <sub>OL</sub> /dt, <sub>CMOS</sub>   | Output current rate of change                  | -10  | -   | 10  | mA/ns |

| L <sub>I,CMOS</sub>                     | CMOS I/O inductance                            | -    | -   | 8   | nH    |

| C <sub>I,CMOS</sub>                     | CMOS I/O capacitance                           | -    | -   | 5   | pF    |

| I <sub>LEAKAGE</sub> 2                  | CMOS I/O Leakage Current                       |      |     | 150 | uA    |

#### TABLE 6: CMOS I/O SPECIFICATIONS

**Note:** .1. This value is measured driving a load of 20pF.

Note: .2. This values is measured at 2.5 VDC.

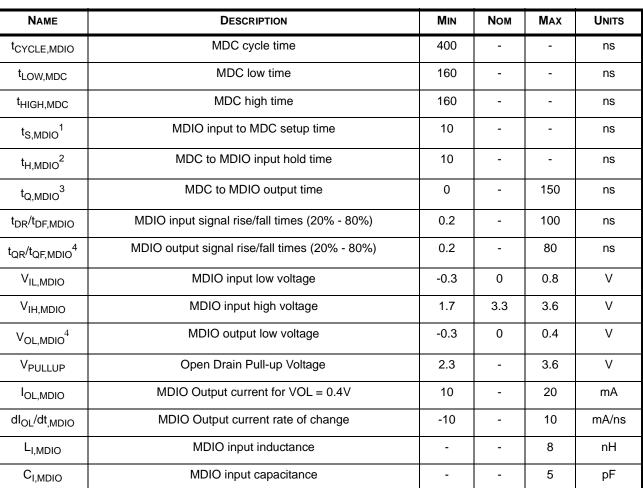

#### 4.3 MDIO Interface

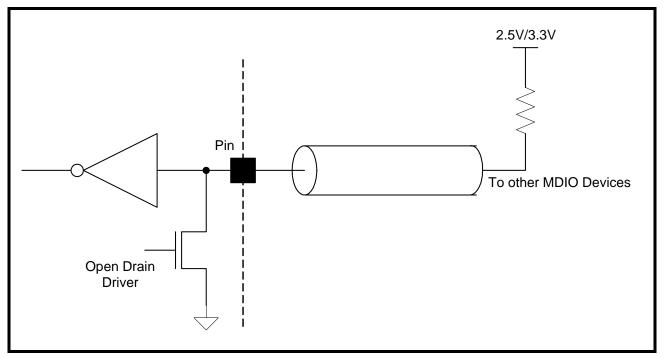

The Management Data Input/Output (MDIO) port complies with Clause 45 of the IEEE 802.3ae specification. A representative MDIO driver/receiver is shown in Figure 16. MDIO uses an open drain driver with a pull-up resistor.

#### FIGURE 16. REPRESENTATIVE MDIO CIRCUIT

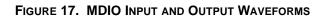

Representative MDIO Read and Write waveforms are shown in **Figure 17**. The XRS10L240 samples MDIO on the rising edge of MDC for input and drives MDIO after the rising edge of MDC for output. Note that setup, hold, and output timings are defined from the maximum VIL and minimum VIH levels.

Values for MDIO parameters are shown in Table 7

# EXSTOR - 1 XRS10L240 SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

#### TABLE 7: MDIO DC AND AC CHARACTERISTICS

REV. 1.05

Notes:

1. Measured from minimum MDIO VIH to maximum MDC VIL for MDIO rising edge.

Measured from maximum MDIO VIL to maximum MDC VIL for MDIO falling edge.

Measured from minimum MDC VIH to maximum MDIO VIL for MDIO rising edge.

Measured from minimum MDC VIH to minimum MDIO VIH for MDIO falling edge.

3. Measured from minimum MDC VIH to maximum MDIO VIL for MDIO rising edge and MDC rising edge. Measured from minimum MDC VIH to minimum MDIO VIH for MDIO falling edge and MDC rising edge. Measured from maximum MDC VIL to maximum MDIO VIL for MDIO rising edge and MDC falling edge. Measured from maximum MDC VIL to minimum MDIO VIH for MDIO falling edge and MDC falling edge.

4. Measured driving a load of 470pF.

| Name            | Description                    | Min  | Nom | Мах  | Units |

|-----------------|--------------------------------|------|-----|------|-------|

| T <sub>A</sub>  | Ambient temperature under bias | -40  | 25  | 85   | C     |

| V <sub>DD</sub> | Core power supply voltage      | 1.14 | 1.2 | 1.26 | V     |

| I <sub>DD</sub> | Core power supply current      | -    | 460 | 600  | mA    |

#### TABLE 8: OPERATING CONDITIONS

#### TABLE 8: OPERATING CONDITIONS

| Name              | Description                                                                                                                                          | Min   | Nom  | Мах  | Units            |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------------------|

| V <sub>ESD1</sub> | Electrostatic discharge tolerance, Human Body Model -<br>Any pin with respect to any other pin except VDDA pins<br>(pins 14, 34, 45, 50, 62, and 87) | -2000 |      | 2000 | V                |

| V <sub>ESD2</sub> | Electrostatic discharge tolerance, Human Body Model -<br>Any pin with respect to VDDA pins (pins 14, 34, 45, 50,<br>62, and 87)                      | -500  |      | 500  | V                |

| θJA               | Junction-to-ambient thermal resistance                                                                                                               |       | 38.5 |      | <sup>0</sup> C/W |

#### 5.0 REGISTERS DESCRIPTION

The XRS10L240 provides a variety of registers for the purpose of device configuration, testing and monitoring. These registers are accessed through the MDIO interface, outlined in "Section 4.3, MDIO Interface" on page 20. Operational registers available to the customer are given below. Note that all other address space should be left unmodified in order to ensure proper behavior of the device.

#### 5.1 Register Overview

The XRS10L240 port address is hardwired to 0; this field should be set to 0 in all packets. The XRS10L240 contains three identical instantiations of a dual Serial ATA PHY macro. A common set of registers exists within each of these macros, and are outlined in "Section 5.2, Macro Registers" on page 25. MDIO device designations 1-3 are used for each of these three macros as shown in Table 9. Registers relating to the XRS10L240 as a whole are outlined in "Section 5.3, XRS10L240 Device Generic Registers" on page 30 and make use of MDIO device 0.

| MDIO DEVICE DESIGNATION | Macro                              | RELEVANT PINS |

|-------------------------|------------------------------------|---------------|

| 0                       | XRS10L240 Device Generic Registers | N/A           |

| 1                       | Serial ATA Input Macro             | SI0, SI1      |

| 2                       | Serial ATA Output Macro 0          | SO0, SO1      |

| 3                       | Serial ATA Output Macro 1          | SO2, SO3      |

#### TABLE 9: MDIO DEVICE DESIGNATIONS

The XRS10L240 registers are arranged as 8-bit fields with 8-bit addresses. These are mapped into the 16-bit MDIO address and data fields by setting the most significant byte of each to 0x00. An example mapping from a macro address/data combination to an MDIO address & data combination is shown in Table 10.

#### TABLE 10: MDIO ADDRESSING

| MACRO ADDRESS | ΜΑCRO DΑΤΑ | MDIO ADDRESS | ΜΟΙΟ ΟΑΤΑ        |

|---------------|------------|--------------|------------------|

| 0x40          | abcde      | 0x0040       | 00000000000abcde |

**NOTE:** The unused upper 3 bits in FBDIV are also set to 0 during MDIO writes and are undefined during MDIO reads.

In the description of each register field, there is an entry describing its read/write status. This may fall into one of the following categories:

- RW- register field is read/write

- RO register field is read only

- LL Latching Low Used with bits that monitor some state internal to the XRS10L240. When the condition for the bit to go low is reached, the bit stays low until the next time it is read. Once it is read, its value reverts to the cur-rent state of the condition it monitors.

- LH Latching High When the condition for the bit to go high is reached, the bit stays high until the next time it is read. Once it is read, its value reverts to the current state of the condition it monitors.

- SC When an SC bit is set, some action is initiated; once the action is complete, the bit is cleared.

REV. 1.05

#### 5.2 Macro Registers

The registers outlined in this section are common to each of the three Serial ATA dual PHY macros as described in the previous section. As such, each listed register is present in each of the 1, 2, and 3 MDIO register spaces, and will perform the stated function on the specified Serial ATA lane.

The registers within each dual PHY macro are split into the following sections:

| Transmit/Receive lane 0 registers: | Address range 000***** |

|------------------------------------|------------------------|

| Transmit/Receive lane 1 registers: | Address range 001***** |

| PLL registers:                     | Address range 010***** |

| Bias generator registers:          | Address range 011***** |

#### TABLE 11: TRANSMIT/RECEIVE LANE REGISTERS (MDIO DEVICE 1, 2, 3)

| Address<br>Hex | Bit(s) | NAME                                   | RW | DEFAULT | DESCRPTION                                                                                                                                                                                                                                                                                                         |

|----------------|--------|----------------------------------------|----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N.0000         | 7      | Reserved                               | RW | 0       | DO NOT MODIFY                                                                                                                                                                                                                                                                                                      |

| N.0020         | 6      | SATAPCIEXB_G1                          | RW | 0       | Tx output swing booster bit (Gen 1)<br>0 = boost swing by 15%<br>1 = nominal swing                                                                                                                                                                                                                                 |

|                | 5:1    | Reserved                               | RW | 0001    | DO NOT MODIFY                                                                                                                                                                                                                                                                                                      |

|                | 0      | SATAPCIEXB_G2                          | RW | 0       | Tx output swing booster bit (Gen 2)<br>0 = boost swing by 15%<br>1 = nominal swing                                                                                                                                                                                                                                 |

| N.0001         | 7:3    | Reserved                               | RW | 00000   | DO NOT MODIFY                                                                                                                                                                                                                                                                                                      |

| N.0021         | 2:0    | Transmit_Eq0[2:0]<br>Transmit_Eq1[2:0] | RW | 011     | Transmit preemphasis control<br>000 = 0% transmit preemphasis<br>001 = 6.5% transmit preemphasis<br>010 = 13% transmit preemphasis<br>011 = 19.5% transmit preemphasis<br>100 = 26% transmit preemphasis<br>101 = 32.5% transmit preemphasis<br>110 = 39% transmit preemphasis<br>111 = 45.5% transmit preemphasis |

# SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

| Address<br>Hex   | Bıt(s)     | NAME                                         | RW | DEFAULT | DESCRPTION                                                                                                                                                                                                                                                                                                                                                             |

|------------------|------------|----------------------------------------------|----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N.0002<br>N.0022 | 7:6<br>7:6 | mscProg0[1:0]<br>mscProg1[1:0]               | RW | 10      | Receive equalization control – boost at 1.5GHz<br>*(Note mscProg = '10' default for device Revision<br>E, mscProg = '01' default for device Revision D)                                                                                                                                                                                                                |

|                  | 5:3<br>5:3 | Beacon_Swing0[2:0]<br>Beacon_Swing1[2:0]     | RW | 100     | Transmit swing size for OOB Signals<br>000 = 800mV<br>001 = 700mV<br>010 = 600mV<br>011 = 500mV<br>100 = 400mV<br>101 = 300mV<br>110 = 200mV<br>111 = 0mV                                                                                                                                                                                                              |

|                  | 2:0<br>2:0 | Output_Swing0[2:0]<br>Output_Swing1[2:0]     | RW | 100     | Transmit swing size in normal operation<br>000 = 800mV<br>001 = 700mV<br>010 = 600mV<br>011 = 500mV<br>100 = 400mV<br>101 = 300mV<br>110 = 200mV<br>111 = 0mV                                                                                                                                                                                                          |

| N.0003<br>N.0023 | 7          | enEqB                                        | RW | 0       | Enable receive equalization<br>0 = enable equalization<br>1 = disable equalization                                                                                                                                                                                                                                                                                     |

|                  | 6:0        | Reserved:0]                                  | RW | 0010000 | DO NOT MODIFY                                                                                                                                                                                                                                                                                                                                                          |

| N.0015           | 7          | Reserved                                     | RO | -       | Reserved                                                                                                                                                                                                                                                                                                                                                               |

| N.0035           | 6:4        | sysclk25divsel0[2:0]<br>sysclk25divsel1[2:0] | RW | 000     | Divider selection for sysclk-> sysclk25<br>000 = divide by 1 (sysclk is 25MHz)<br>001 = divide by 2 (sysclk is 50MHz)<br>010 = divide by 3 (sysclk is 75MHz)<br>011 = divide by 4 (sysclk is 100MHz)<br>100 = divide by 5 (sysclk is 125MHz)<br>101 = divide by 6 (sysclk is 150MHz)<br>110 = divide by 10 (sysclk is 250MHz)<br>111 = divide by 12 (sysclk is 300MHz) |

|                  | 3:0        | Reserved                                     | RW | 0101    | DO NOT MODIFY                                                                                                                                                                                                                                                                                                                                                          |

REV. 1.05

# SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

# TABLE 11: TRANSMIT/RECEIVE LANE REGISTERS (MDIO DEVICE 1, 2, 3)

| Address<br>Hex | Bit(s) | NAME                                         | RW | DEFAULT | DESCRPTION                                                                                                                                                 |

|----------------|--------|----------------------------------------------|----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N.0018         | 7:3    | Reserved                                     | RW | 00100   | DO NOT MODIFY                                                                                                                                              |

| N.0038         | 2:0    | txbiasbuffsela0[2:0]<br>txbiasbuffsela1[2:0] | RW | 100     | Tx Predriver swing size in normal operation<br>000 = 800 mV<br>001 = 700 mV<br>010 = 600 mV<br>011 = 500 mV<br>100 = 400 mV (sata default)<br>101 = 300 mV |

# SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

| Address<br>Hex | Bıт(s) | Nаме        | Түре | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                              |

|----------------|--------|-------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N.0040         | 7:6    | Reserved    | RO   | -       | Reserved                                                                                                                                                                                                                                                                                                                                                 |

|                | 5:0    | FBDIV[5:0]  | RW   | 101101  | Divide value for feedback clock<br>110000 = divide by 5<br>100000 = divide by 10<br>100001 = divide by 15<br>100010 = divide by 20<br>100011 = divide by 25<br>100101 = divide by 30<br>100111 = divide by 50<br>101101 = divide by 60 (default for 25MHz Ref))<br>Other - reserved                                                                      |

| N.0041         | 7:6    | Reserved    | RO   | -       | Reserved                                                                                                                                                                                                                                                                                                                                                 |

|                | 5:0    | REFDIV[5:0] | RW   | 010000  | Divide values for system clock<br>010000 = divide by 1 (default for 25MHz Ref))<br>000000 = divide by 2<br>000001 = divide by 3<br>000010 = divide by 4<br>000011 = divide by 5<br>000101 = divide by 6<br>000110 = divide by 8<br>000111 = divide by 10<br>001101 = divide by 12<br>001110 = divide by 16<br>001111 = divide by 20<br>Others - reserved |

| N.0044         | 7:6    | Reserved    | RO   | -       | Reserved                                                                                                                                                                                                                                                                                                                                                 |

|                | 5:0    | SSCMax      | RW   | 00000   | Maximum value for spread (set to 45, [0x2D] when SSCBypass is set to "0")                                                                                                                                                                                                                                                                                |

| N.0045         | 7:5    | Reserved    | RO   | -       | Reserved                                                                                                                                                                                                                                                                                                                                                 |

| NOTE 1         | 4      | SSCmode     | RW   | 0       | Selects position of spreading interpolator<br>0 = Interpolator in feedback path<br>1 = Interpolator in feedforward path<br>Set to '1' when SSCBypass = '0'                                                                                                                                                                                               |

|                | 3      | Reserved    | RW   | 0       | DO NOT MODIFY                                                                                                                                                                                                                                                                                                                                            |

|                | 2      | SSCInvert   | RW   | 0       | Spread up instead of down                                                                                                                                                                                                                                                                                                                                |

|                | 1      | Reserved    | RW   | 0       | DO NOT MODIFY                                                                                                                                                                                                                                                                                                                                            |

|                | 0      | SSCBypass   | RW   | 1       | Bypass the saw generator and pulse density modu-<br>lator and get increment from SSCMax (set SSCMax<br>to 45, 0x2D when SSCBypass is set to 0)                                                                                                                                                                                                           |

**Note:** 1) In order to enable SSC generation, set register N.0044 to 0x2D, N.0045 to 0x14 and then reset the PLL by writing register 0.0004 to 0x0 then 0xF.

| Address<br>Hex | Bıт(s) | NAME            | Түре | RESET VALUE | DESCRIPTION                                                                                                                      |

|----------------|--------|-----------------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------|

| N.0064         | 7:4    | pr100Tx[3:0]    | RW   | 0x0         | Transmit pre-driver current bias<br>1010=50uA<br>0010=75uA<br>0000=100uA<br>0001=125uA<br>1100=150uA<br>0111=175uA<br>1111=200uA |

|                | 3:0    | Reserved[3:0]   | RW   | 0x0         | DO NOT MODIFY                                                                                                                    |

| N.0065         | 7:4    | Reserved        | RW   | 0x0         | DO NOT MODIFY                                                                                                                    |

|                | 3:0    | prcal100Tx[3:0] | RW   | 0x0         | Transmit driver current bias<br>1010=50uA<br>0010=75uA<br>0000=100uA<br>0001=125uA<br>1100=150uA<br>0111=175uA<br>1111=200uA     |

#### TABLE 13: BIAS GENERATOR CONFIGURATION (MDIO DEVICE 1, 2, 3)

#### TABLE 14: POWERDOWN REGISTERS (MDIO DEVICES 1, 2 & 3)

| Address<br>Hex             | Bıт(s) | ΝΑΜΕ                                                               | Түре | RESET VALUE | DESCRIPTION                                                                                    |

|----------------------------|--------|--------------------------------------------------------------------|------|-------------|------------------------------------------------------------------------------------------------|

| 1.0080<br>2.0080<br>3.0080 | 7:6    | SIpwrdnDetB[1:0]<br>SO01pwrdnDetB[1:0]<br>SO23pwrdnDetB[1:0]       | RW   | 11          | Powers down the signal detector and COM*<br>circuits<br>1 = normal operation<br>0 = power down |

|                            | 5:4    | SlpwrdnRxB[1:0]<br>SO01pwrdnRxB[1:0]<br>SO23pwrdnRxB[1:0]          | RW   | 11          | Powers down the receivers and CDR<br>1 = normal operation<br>0 = power down                    |

|                            | 3:2    | SlpwrdnTxDrvB[1:0]<br>SO01pwrdnTxDrvB[1:0]<br>SO23pwrdnTxDrvB[1:0] | RW   | 11          | Powers down the transmitter<br>1 = normal operation<br>0 = power down                          |

|                            | 1:0    | SIpwrdnTxB[1:0]<br>SO01pwrdnTxB[1:0]<br>SO23pwrdnTxB[1:0]          | RW   | 11          | Powers down the transmit pipes and clock<br>1 = normal operation<br>0 = power down             |

# SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

#### TABLE 14: POWERDOWN REGISTERS (MDIO DEVICES 1, 2 & 3)

| Address<br>Hex   | BIT(S) | Nаме                                                   | Түре | RESET VALUE | DESCRIPTION                                                        |

|------------------|--------|--------------------------------------------------------|------|-------------|--------------------------------------------------------------------|

| 1.0081           | 7:2    | Reserved                                               | RO   | -           | Reserved                                                           |

| 2.0081<br>3.0081 | 1      | SlpwrdnBiasGen<br>SO01pwrdnBiasGen<br>SO23pwrdnBiasGen | RW   | 0           | Powers down the bandgap.<br>1 = power down<br>0 = normal operation |

|                  | 0      | SIpwrdnPLLB<br>SO01pwrdnPLLB<br>SO23pwrdnPLLB          | RW   | 1           | Powers down the PLL<br>1 = normal operation<br>0 = power down      |

#### 5.3 XRS10L240 Device Generic Registers

This section outlines generic registers relating to the XRS10L240 as a whole. These registers are accessed through MDIO device 0.

| Address<br>Hex | BIT(S) | Nаме             | Түре | RESET VALUE | DESCRIPTION                  |

|----------------|--------|------------------|------|-------------|------------------------------|

| 0.0030         | 7:0    | revision_id[7:0] | R/O  | 05H         | *(Note 1) Device Revision ID |

| 0.0031         | 7:0    | device_id [15:8] | R/O  | 83H         | Device ID MSB                |

| 0.0032         | 7:0    | device_id [7:0   | R/O  | 06H         | Device ID LSB                |

#### TABLE 15: RESET CONTROL SIGNALS

**NOTE:** 1) Revision ID 05H is for device Revision E. Revision ID 03H is for device Revision D.

#### TABLE 16: SATA PORT SELECTOR REGISTERS

| Address<br>Hex | Bıт(s) | NAME        | Түре | RESET VALUE | DESCRIPTION                                                                                                 |

|----------------|--------|-------------|------|-------------|-------------------------------------------------------------------------------------------------------------|

| 0.009A         | 7:3    | Reserved    | RW   | 00100       | DO NOT MODIFY                                                                                               |

|                | 2      | p_host_sel  | RW   | 0           | Side band port selection<br>1 = Select Host port 1<br>0 = Select Host port 0                                |

|                | 1      | p_side_mthd | RW   | 0           | <ul><li>1 = p_host_sel based sideband selection</li><li>0 = external pin based sideband selection</li></ul> |

|                | 0      | p_sel_mthd  | RW   | 0           | Please refer to Table 2, "Host Port<br>Selection," on page 7                                                |

SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

| Address<br>Hex | Вıт(s) | NAME        | Түре | RESET VALUE | DESCRIPTION                                                 |

|----------------|--------|-------------|------|-------------|-------------------------------------------------------------|

| 0.0001         | 7:3    | Reserved    | RO   | -           | Reserved                                                    |

|                | 2      | refClkSel   | RW   | 0           | 1 = select CMU_REF<br>0 = select on chip crystal oscillator |

|                | 1      | pwrdnRefClk | RW   | 0           | Powers down reference clock                                 |

|                | 0      | Reserved    | RO   | -           | Reserved                                                    |

#### TABLE 17: CLOCK CONFIGURATION REGISTER

TABLE 18: PORT MULTIPLIER SATA STANDARD REGISTERS

| REGISTER                | Bit(s)  | NAME                  | Түре | DEFAULT<br>VALUE | DESCRIPTION                                                                         |

|-------------------------|---------|-----------------------|------|------------------|-------------------------------------------------------------------------------------|

| GSCR(0)                 | 31 - 16 | Device ID             | R/O  | 0x8306           | Device ID allocated by the vendor.                                                  |

| Product<br>Identifier   | 15 - 0  | Vendor ID             | R/O  | 0x13A8           | Vendor ID allocated by the PCI-SIG of the vendor that produced the Port Multiplier. |

| GSCR(1)                 | 31 - 16 | Reserved              | R/O  | 0x0000           | 31-16 Reserved                                                                      |

| Revision<br>Information | 15 - 8  | REV_LEV               | R/O  | 0x03             | 15-8 Revision level of the Port Multiplier.                                         |

|                         | 7:4     | Reserved              | R/O  | 0x0              | 7-4 Reserved                                                                        |

|                         | 3       | PM_1,2                | R/O  | 1                | 1=Supports Port Multiplier specification 1.2.                                       |

|                         | 2       | PM_1.1                | R/O  | 1                | 1=Supports Port Multiplier specification 1.1.                                       |

|                         | 1       | PM_1.0                | R/O  | 1                | 1=Supports Port Multiplier specification 1.0.                                       |

|                         | 0       | Reserved              | R/O  | 0                | Reserved                                                                            |

| GSCR(2)                 | 7:4     | Reserved              | R/O  | 0x0              | Reserved                                                                            |

| Port<br>Information     | 3 - 0   | DEV_FAN_OUT_<br>PORTS | R/O  | 0x4              | Number of exposed device fan-out ports.                                             |

# SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR

| REGISTER                                         | Вıт(s)  | NAME                   | Түре | DEFAULT<br>VALUE | DESCRIPTION                                       |

|--------------------------------------------------|---------|------------------------|------|------------------|---------------------------------------------------|

| GSCR(32)                                         | 31 - 15 | Reserved               | R/O  | 0x0              |                                                   |

| Error<br>Information                             | 14      | Reserved               | R/O  | 0                | Unused                                            |

|                                                  | 13      | Reserved               | R/O  | 0                | Unused                                            |

|                                                  | 12      | Reserved               | R/O  | 0                | Unused                                            |

|                                                  | 11      | Reserved               | R/O  | 0                | Unused                                            |

|                                                  | 10      | Reserved               | R/O  | 0                | Unused                                            |

|                                                  | 9       | Reserved               | R/O  | 0                | Unused                                            |

|                                                  | 8       | Reserved               | R/O  | 0                | Unused                                            |

|                                                  | 7       | Reserved               | R/O  | 0                | Unused                                            |

|                                                  | 6       | Reserved               | R/O  | 0                | Unused                                            |

|                                                  | 5       | Reserved               | R/O  | 0                | Unused                                            |

|                                                  | 4       | Reserved               | R/O  | 0                | Unused                                            |

|                                                  | 3       | OR_PORT-3              | R/O  | 0                | OR of selectable bits in Port 3 PSCR[1] (SError)  |

|                                                  | 2       | OR_PORT-2              | R/O  | 0                | OR of selectable bits in Port 2 PSCR[1] (SError)  |

|                                                  | 1       | OR_PORT-1              | R/O  | 0                | OR of selectable bits in Port 1 PSCR[1] (SError)  |

|                                                  | 0       | OR_PORT-0              | R/O  | 0                | OR of selectable bits in Port 0 PSCR[1] (SError)  |

| GSCR(33)<br>Error Infor-<br>mation Bit<br>Enable | 31 - 0  | ERR_INFO_EN            | R/O  | 0x400FFFF        | If set, bit is enabled for use in GSCR[32]        |

| GSCR(64)                                         | 31 - 5  | Reserved               | R/O  | 0x0              | Reserved                                          |

| Port Multi-<br>plier Revi-                       | 4       | PHY_EVENT              | R/O  | 0                | 1 = Supports Phy event counters                   |

| sion 1.X<br>Features                             | 3       | ASYNC                  | R/O  | 1                | 1 = Supports asynchronous notification            |

| Support                                          | 2       | SSC                    | R/O  | 0                | 1 = Supports dynamic SSC transmit enable          |

|                                                  | 1       | PMREQ <sub>P</sub>     | R/O  | 1                | 1 = Supports issuing PMREQ <sub>P</sub> to host   |

|                                                  | 0       | BIST                   | R/O  | 0                | 1 = Supports BIST                                 |

| GSCR(96)                                         | 31 - 4  | Reserved               | R/O  | 0x0              | Reserved                                          |

| Port Multi-<br>plier Revi-                       | 3       | ASYNC_EN               | RW   | 0                | 1 = Asynchronous notification enabled             |

| sion 1.X<br>Features                             | 2       | SSC_EN                 | RW   | 0                | 1 = Dynamic SSC transmit is enabled               |

| Enable                                           | 1       | PMREQ <sub>P</sub> _EN | RW   | 0                | 1 = Issuing PMREQ <sub>P</sub> to host is enabled |

|                                                  | 0       | BIST_EN                | RW   | 0                | 1 = BIST support is enabled                       |

#### TABLE 18: PORT MULTIPLIER SATA STANDARD REGISTERS

# SERIAL ATA II: PORT MULTIPLIER / PORT SELECTOR