# SANYO Semiconductors DATA SHEET

# LV23200T — For Home Stereo System 1-chip Tuner IC Incorporating PLL

#### Overview

The LV23200T is a one-chip tuner IC incorporating PLL for home stereo system.

#### **Functions**

• AM tuner Changeover of the constant in RFAMP, MIX, OSC, IF AMP, DET, AGC, SD, OSC BUFF, IF BUFF, and

AGC modes.

• FM tuner 1stIFAMP, IF limiter AMP, DET (COIL type), S-METER, SD, AFC, IF BUFF.

• MPX PLL STEREO DECODER, forced MONO, AUDIO MUTE, function to prevent interference from a

neighboring station, PILOT canceling function.

• PLL frequency synthesizer.

#### **Features**

• Tuner IC and PLL IC integrated into one chip.

• MPX-VCO incorporated and without need of adjustment.

• FM/AM output level independent setting possible.

• MOS transistor for active LPF incorporated.

#### **Specitications**

**Maximum Ratings** at Ta = 25 °C

| Parameter              | Symbol              | Conditions      | Ratings     | Unit |

|------------------------|---------------------|-----------------|-------------|------|

| Maximum supply voltage | V <sub>CC</sub> max | Vcc             | 7.0         | V    |

|                        | V <sub>DD</sub> max | V <sub>DD</sub> | 6.0         | V    |

| Operating temperature  | Topr                |                 | -20 to +80  | °C   |

| Storage temperature    | Tstg                |                 | -40 to +125 | °C   |

- Any and all SANYO Semiconductor products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO Semiconductor representative nearest you before using any SANYO Semiconductor products described or contained herein in such applications.

- SANYO Semiconductor assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor products described or contained herein.

#### **Operating Condition** at Ta = 25 °C

| Parameter                      | Symbol              | Conditions                 | Ratings    | Unit |

|--------------------------------|---------------------|----------------------------|------------|------|

| Recommended supply voltage     | Vcc                 |                            | 5.0        | V    |

|                                | $V_{DD}$            |                            | 3.0        | V    |

| Operating supply voltage range | V <sub>CC</sub> op  |                            | 4.5 to 6.0 | V    |

|                                | V <sub>DD</sub> op1 | X'tal oscillation = 4.5MHz | 2.7 to 3.3 | V    |

<sup>\*</sup> Handle pin 34 with care because its electrostatic voltage at C = 200 pF and  $R = 0\Omega$  is 110 V.

# Operating Characteristics at Ta = 25°C, $V_{CC} = 5.0V$ , $V_{DD} = 3.0V$

| Parameter                         | Symbol             | Conditions                                                                      |                      | Ratings            |      |           |  |

|-----------------------------------|--------------------|---------------------------------------------------------------------------------|----------------------|--------------------|------|-----------|--|

| Farameter                         | Symbol             | Conditions                                                                      | min                  | typ                | max  | Unit      |  |

| [Current dissipation]             |                    |                                                                                 |                      |                    |      |           |  |

| FM tuner block                    | I <sub>CC</sub> FM | No input in FM mode                                                             | 25                   | 35                 | 45   | mA        |  |

| AM tuner block                    | I <sub>CC</sub> AM | No input in AM mode                                                             | 14                   | 24                 | 34   | mA        |  |

| PLL block                         | I <sub>DD</sub> FM | X'tal = 4.5MHz, No input at tuner                                               | 2.0                  | 3.0                | 4.0  | mA        |  |

| [FM-FE characteristics (MPX)] :   | FM-IF (5PIN) inpu  | t, fc = 10.7MHz, fm = 1kHz, 75kHzdev (L+R = 90)                                 | 0%, Pilot = 10%)     |                    |      |           |  |

| Demodulation output               | Vo                 | $V_{IN} = 100 dB\mu V$                                                          | 450                  | 550                | 650  | mVrms     |  |

| 3dB sensitivity 1                 | LS1                | V <sub>IN</sub> = 70dBμV reference, input at -3dB<br>*at input of FIFA (pin 1)  |                      | 28                 | 33   | dBμV      |  |

| 3dB sensitivity 2                 | LS2                | V <sub>IN</sub> = 100dBμV reference, input at -3dB<br>*at input of FMFA (pin 5) |                      | 35                 | 40   | dΒμV      |  |

| Total harmonic distortion         | THD1               | $V_{IN} = 100 dB\mu V$ , MONO                                                   |                      | 0.4                | 1.5  | %         |  |

| Signal-to-noise ratio             | S/N                | V <sub>IN</sub> = 100dBμV                                                       | 70                   | 76                 |      | dB        |  |

| AM suppression ratio              | AMR                | V <sub>IN</sub> = 100dBμV, AM = 30%                                             | 36                   | 40                 |      | dB        |  |

| SD sensitivity                    | SD-1               | 0%mod, SD sensitivity mode 1                                                    | 43                   | 50                 | 57   | dBμV      |  |

| Total harmonic distortion         | THD2               | V <sub>IN</sub> = 100dBμV, MAIN-MOD                                             |                      | 0.5                | 1.5  | %         |  |

| Separation                        | SEP                | $V_{IN} = 100 dB\mu V$ , L output/R output                                      | 30                   | 45                 |      | dB        |  |

| ST sensitivity                    | VL                 | $V_{IN} = 100dB\mu V$ , (L+R)+Pilot                                             |                      | 3.0                | 5.5  | %         |  |

| Mute attenuation                  | MUTE               | V <sub>IN</sub> = 100dBμV, L output                                             |                      | 60                 |      | dB        |  |

| Carrier leakage                   | CL                 | $V_{IN} = 100dB\mu V$ , (L+R)+Pilot                                             | 30                   | 40                 |      | dB        |  |

| [AM characteristics] : fc = 999kh | Hz, fm = 1kHz, 30% | 6mod                                                                            |                      |                    |      |           |  |

| Demodulation output 1             | V <sub>O</sub> 1   | $V_{IN} = 23 dB\mu V$ , 30%mod, fm = 1kHz                                       | 50                   | 80                 | 130  | mVrms     |  |

| Demodulation output 2             | V <sub>O</sub> 2   | $V_{IN} = 80 dB\mu V$ , 30%mod, fm = 1kHz                                       | 170                  | 240                | 310  | mVrms     |  |

| Signal-to-noise ratio 1           | S/N1               | $V_{IN} = 23dB\mu V$                                                            | 15                   | 20                 |      | dB        |  |

| Signal-to-noise ratio 2           | S/N2               | $V_{IN} = 80 dB\mu V$                                                           | 48                   | 54                 |      | dB        |  |

| Total harmonic distortion         | THD                | $V_{IN} = 80 dB \mu V$                                                          |                      | 0.4                | 1.3  | %         |  |

| SD sensitivity                    | SD-ON              | 0%mod (Internally fixed sensitivity)                                            | 14                   | 24                 | 34   | dBμV      |  |

| [PLL characteristics]             |                    |                                                                                 |                      |                    |      |           |  |

| Internal return resistance        | Rf                 | XIN                                                                             |                      | 8                  |      | $M\Omega$ |  |

| Built-in output resistance        | Rd                 | XOUT                                                                            |                      | 250                |      | kΩ        |  |

| Hysteresis width                  | VHIS               | CE, CL, DI                                                                      |                      | 0.1V <sub>DD</sub> |      | V         |  |

| Output high level voltage         | VOH                | PD ; I <sub>O</sub> = -1mA                                                      | V <sub>DD</sub> -1.0 |                    |      | V         |  |

| Output low level voltage          | V <sub>OL</sub> 1  | PD ; I <sub>O</sub> = 1mA                                                       |                      |                    | 1.0  | V         |  |

|                                   | V <sub>OL</sub> 2  | BO ; I <sub>O</sub> = 1mA                                                       |                      |                    | 0.25 | V         |  |

|                                   |                    | BO ; I <sub>O</sub> = 5mA                                                       |                      |                    | 1.25 | V         |  |

|                                   | V <sub>OL</sub> 3  | DO ; I <sub>O</sub> = 1mA                                                       |                      |                    | 0.25 | V         |  |

|                                   | V <sub>OL</sub> 4  | AOUT ; I <sub>O</sub> = 1mA, AIN = 2.0V                                         |                      |                    | 0.5  | V         |  |

| Output high level voltage         | I <sub>IH</sub> 1  | CE, CL, DI ; VI = 6.0V                                                          |                      |                    | 5.0  | μΑ        |  |

|                                   | I <sub>IH</sub> 2  | $XIN$ ; $VI = V_{DD}$                                                           | 0.16                 |                    | 0.9  | μΑ        |  |

|                                   | I <sub>IH</sub> 3  | AIN ; VI = 6.0V                                                                 |                      |                    | 200  | nA        |  |

| Input high level current          | I <sub>IL</sub> 1  | CE, CL, DI; VI = 0V                                                             |                      |                    | 5.0  | μΑ        |  |

|                                   | I <sub>IL</sub> 2  | XIN; VI = 0V                                                                    | 0.16                 |                    | 0.9  | μΑ        |  |

|                                   | I <sub>IL</sub> 3  | AIN; VI = 0V                                                                    |                      |                    | 200  | nA        |  |

Continued from preceding page.

| Parameter                          | Cumbal             | Conditions                      |     | Unit |     |       |

|------------------------------------|--------------------|---------------------------------|-----|------|-----|-------|

| Parameter                          | Symbol             | Conditions                      | min | typ  | max | Offic |

| Output off-leak current            | I <sub>OFF</sub> 1 | BO, AOUT ; V <sub>O</sub> = 10V |     |      | 5.0 | μΑ    |

|                                    | I <sub>OFF</sub> 2 | DO ; V <sub>O</sub> = 6.0V      |     |      | 5.0 | μΑ    |

| "H" level 3-state off-leak current | IOFFH              | PD ; V <sub>O</sub> = 6.0V      |     | 0.01 | 200 | nA    |

| "L" level 3-state off-leak current | IOFFL              | PD ; V <sub>O</sub> = 0V        |     | 0.01 | 200 | nA    |

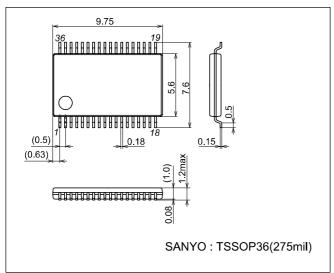

# **Package Dimensions**

unit : mm 3253B

#### **Description of Pin Functions**

| No. | Functions            | Voltage (V) | Internal Equivalent Circuit | Remarks                                                       |

|-----|----------------------|-------------|-----------------------------|---------------------------------------------------------------|

| 1   | FM 1stIF-AMP input   | 1.6V        | 1<br>Rin                    | Input impedance ri (Rin). Rin = 330Ω                          |

| 2   | REG                  | 2.2V        | 2                           | Reference voltage of AM/FM IF/MPX block. Vreg = 2.2V          |

| 3   | FM 1st IF-AMP output | 3.0V        | Rout                        | Output impedance ro (Rout).<br>Rout = $300\Omega$             |

| 4   | AM MIX output        | Vcc         | 4                           | MIX coil used between pins 4 and 8 (V <sub>CC</sub> voltage). |

| 5   | FM IF input          | Vreg        | 5 Rin                       | Input impedance ri (Rin). Rin = 330Ω                          |

| 6   | GND                  | 0V          |                             | AM/FM IF/MPX block GND                                        |

| 7   | AM IF input          | 2.2V        | 7 Rin                       | Input impedance ri (Rin). Rin = 2kΩ                           |

| 8   | Vcc                  | 5.0V        |                             | AM/FM IF/MPX block V <sub>CC</sub>                            |

#### Continued from preceding page.

| No.      | Functions               | Voltage (V)           | Internal Equivalent Circuit | Remarks                                                                                                        |

|----------|-------------------------|-----------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------|

| 9        | FM DET                  | Vcc                   |                             | Recommended detection coil.<br>600BCAS-10790Z                                                                  |

| 10       | Phase comparator filter | V <sub>CC</sub> -1.0V | 10<br>R                     | R = 10kΩ                                                                                                       |

| 11       | Pilot filter            | V <sub>CC</sub> -1.0V | 11) R                       | R = 10kΩ                                                                                                       |

| 12<br>13 | L output<br>R output    | 2.5V                  | Rout (13)                   | Output impedance ro (Rout).<br>Rout = $7.7k\Omega$                                                             |

| 15       | CE                      | -                     | (15) S                      | Chip enable pin At changeover from "L" to "H": Address latching. At changeover from "H" to "L": Data latching. |

| 16       | DI                      | -                     | (16) S                      | Serial data input pin Sets data in synchronization with rise of data clock.                                    |

| 17       | CL                      | -                     | (17) S                      | Data clock input pin.                                                                                          |

| 18       | DO                      | _                     | 18                          | Data output pin Outputs various data in synchronization with fall of data clock in the OUT mode.               |

#### Continued from preceding page.

| No.      | Functions              | Voltage (V)            | Internal Equivalent Circuit | Remarks                                                                                                                                      |

|----------|------------------------|------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 19<br>20 | X IN<br>X OUT          | -                      |                             | Clock for internal reference<br>Connect a 4.5 MHz crystal oscillator.                                                                        |

|          |                        |                        | 19 (20)                     |                                                                                                                                              |

| 21       | V <sub>DD</sub>        | 3.0V                   |                             | AM/FM IF/MPX block V <sub>DD</sub>                                                                                                           |

| 22       | Pilot canceling output | Vreg                   | 22                          | Output impedance ro (Rout). Rout = $30k\Omega$                                                                                               |

|          |                        |                        | Rout                        |                                                                                                                                              |

| 23       | AM detection output    | 0.8V (FM)<br>Vreg (AM) | Rout 23                     | Output impedance ro (Rout). Rout = $10k\Omega$                                                                                               |

| 24       | MPX input              | Vreg                   | RNF<br>W                    | MPX inverse input pin. RNF = 20kΩ                                                                                                            |

| 25       | PLL input              | Vreg                   | Rin S                       | Input impedance $$ ri (Rin). $$ Rin = $20 k\Omega$                                                                                           |

| 26       | FM detection output    | Vreg+0.7V              | Rout                        | Output impedance ro (Rout).<br>Rout = $3.3 k\Omega$<br>Adjusts separation using the capacitance value of a section between this pin and GND. |

#### Continued from preceding page.

| No.      | Functions                    | Voltage (V)            | Internal Equivalent Circuit | Remarks                                                                                                                              |

|----------|------------------------------|------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 27       | SD monitor                   | VDD                    | V <sub>DD</sub> (27)        | Active "L" Open collector.                                                                                                           |

| 28       | FMS meter and AM AGC outputs | 0.2V (FM)<br>0.8V (AM) | 28<br>R                     | Internal load resistance $R=13.9k\Omega$ Determines the SD response speed during SEEK by a capacitor externally connected to pin 28. |

| 29       | PD                           | -                      | 29                          | PLL charge pump output pin.                                                                                                          |

| 30<br>31 | AIN<br>AOUT                  | -                      | 30                          | Nch MOS transistor for PLL active low pass filter.                                                                                   |

| 32       | AM OSC                       | Vcc                    | 32                          | OSC coil used between pins 32 and 8 (V <sub>CC</sub> voltage).                                                                       |

| 33       | AFC                          | Vreg                   | 33)                         | Enables adjustment of the FM SD band width by external resistor between pins 33 and 2 (Vreg voltage).                                |

#### Continued from preceding page.

| No. | Functions    | Voltage (V) | Internal Equivalent Circuit | Remarks                                                                           |

|-----|--------------|-------------|-----------------------------|-----------------------------------------------------------------------------------|

| 34  | AM RF input  | Vreg        | 34 • 34                     | Use pin 34 with the same potential as for pin 32 (AFC voltage).                   |

| 35  | FM OSC input | Vcc         | 35 VCC                      | Use pin 35 through pull-up to pin 8 (V <sub>CC</sub> voltage) by resistance load. |

| 36  | ВО           | -           | 36                          | Pin dedicated for output.                                                         |

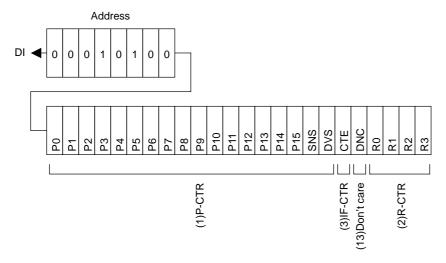

#### Composition of DI control data (serial data input)

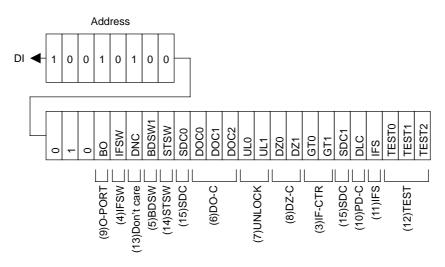

#### (1) IN1 mode

#### (2) IN2 mode

#### **Description of DI control Data**

| No. | Control block data |         |                                                                               |            |           | Descri              | ption   |                               |       | Related data |  |  |

|-----|--------------------|---------|-------------------------------------------------------------------------------|------------|-----------|---------------------|---------|-------------------------------|-------|--------------|--|--|

| (1) | Programmable       | • Data  | Data to set the dividing number of programmable divider                       |            |           |                     |         |                               |       |              |  |  |

|     | divider data       | Binary  | Binary value with P15 assumed to be MSB. LSB varies according to DVS and SNS. |            |           |                     |         |                               |       |              |  |  |

|     |                    |         | (* : Don't care)                                                              |            |           |                     |         |                               |       |              |  |  |

|     | P0 to P15          |         | DVS                                                                           | SNS        | LSB       | set dividing num    | ber (N) | Actual dividing               |       |              |  |  |

|     | DVS, SNS           |         | 1                                                                             | *          | P0        | 272 to 6553         | 35      | Twice the set value           |       |              |  |  |

|     |                    |         | 0                                                                             | 1          | P0        | 272 to 6553         | 35      | Set value                     |       |              |  |  |

|     |                    |         | 0                                                                             | 0          | P4        | 4 to 4095           |         | Set value                     |       |              |  |  |

|     |                    | * P0 to | P3 invali                                                                     | id when    | LSB : P4  | 1                   |         |                               |       |              |  |  |

|     |                    | • To se | lect the                                                                      | signal inp | out (FMII | N, AMIN) to the pro | gramma  | ble divider and to change the | input |              |  |  |

|     |                    | freque  | ency ran                                                                      | ge.        |           |                     |         |                               |       |              |  |  |

|     |                    |         |                                                                               |            |           |                     |         | (*: Don't care)               |       |              |  |  |

|     |                    |         | DVS                                                                           | SNS        |           | Input               | Ор      | eration frequency range       |       |              |  |  |

|     |                    |         | 1                                                                             | *          |           | FMIN                |         | 10 to 160MHz                  |       |              |  |  |

|     |                    |         | 0                                                                             | 1          |           | AMIN                |         | 2 to 40MHz                    |       |              |  |  |

|     |                    |         | 0                                                                             | 0          |           | AMIN                |         | 0.5 to 10MHz                  |       |              |  |  |

#### Continued from preceding page.

| No. | Control block data |          |             |             |            |            | Descr     | iption                                                 |     | Related data |

|-----|--------------------|----------|-------------|-------------|------------|------------|-----------|--------------------------------------------------------|-----|--------------|

| (2) | Reference          | • Refere | ence fre    | quency (    | fref) sele | ection dat | а         |                                                        |     |              |

|     | divider data       |          | R3          | R2          | R2 R1 R0   |            |           | Reference frequency                                    |     |              |

|     | D0 to D2           |          | 0           | 0           | 0          | 0          |           | 25kHz                                                  |     |              |

|     | R0 to R3           |          | 0           | 0           | 0          | 1          |           | 25kHz                                                  |     |              |

|     |                    |          | 0           | 0           | 1          | 0          |           | 25kHz                                                  |     |              |

|     |                    |          | 0           | 0           | 1          | 1          |           | 25kHz                                                  |     |              |

|     |                    |          | 0           | 1           | 0          | 0          |           | 12.5kHz                                                |     |              |

|     |                    |          | 0           | 1           | 0          | 1          |           | 6.25kHz                                                |     |              |

|     |                    |          | 0           | 1           | 1          | 0          |           | 3.125kHz                                               |     |              |

|     |                    |          | 0           | 1           | 1          | 1          |           | 3.125kHz                                               |     |              |

|     |                    |          | 1           | 0           | 0          | 0          |           | 5kHz                                                   |     |              |

|     |                    |          | 1           | 0           | 0          | 1          |           | 5kHz                                                   |     |              |

|     |                    |          | 1           | 0           | 1          | 0          |           | 5kHz                                                   |     |              |

|     |                    |          | 1           | 0           | 1          | 1          |           | 1kHz                                                   |     |              |

|     |                    |          | 1           | 1           | 0          | 0          |           | 3kHz                                                   |     |              |

|     |                    |          | 1           | 1           | 0          | 1          |           | 15kHz                                                  |     |              |

|     |                    |          | 1           | 1           | 1          | 0          |           | PLL INHIBIT+X'tal OSC                                  |     |              |

|     |                    |          | 1           | 1           | 1          | 1          |           | PLL INHIBIT                                            |     |              |

|     |                    | -        | rogramn     |             |            |            |           | vith FMIN, AMIN, HCTR and<br>ump has the high impedand | · - |              |

| (3) | IF counter         | • IF cou | ınter cou   | inting sta  | art data   |            |           |                                                        |     | IFS          |

|     | control data       |          |             | unting st   |            |            |           |                                                        |     |              |

|     |                    |          |             | unting st   |            |            |           |                                                        |     |              |

|     | CTE                | Deterr   | mines th    | e countii   | ng time o  | of univers | al counte | r                                                      |     |              |

|     | GT0, GT1           |          | GT1         | GT0         | Co         | ounting ti | me        | Wait time                                              |     |              |

|     |                    |          | 0           | 0           |            | 4ms        |           | 3 to 4ms                                               |     |              |

|     |                    |          | 0           | 1           |            | 8ms        |           | 3 to 4ms                                               |     |              |

|     |                    |          | 1           | 0           |            | 16ms       |           | 3 to 4ms                                               |     |              |

|     |                    |          | 1           | 1           |            | 32ms       |           | 3 to 4ms                                               |     |              |

| (4) | MUTE               | Data to  | o determ    | ine the o   | utput of o | utput por  | IFSW, co  | entrolling the MUTE function.                          |     |              |

|     | control data       | "Data    | a" = 0 : a  | t receivi   | ng         |            |           |                                                        |     |              |

|     |                    |          | 1:1         | <b>IUTE</b> |            |            |           |                                                        |     |              |

|     | IFSW               |          |             |             |            |            |           |                                                        |     |              |

| (5) | FM/AM BAND         | Data to  | o determ    | ine the o   | utput of o | utput por  | BDSW, o   | controlling selection of BAND.                         |     |              |

|     | selection          | "Data    | a'' = 0 : A | M           |            |            |           |                                                        |     |              |

|     | control data       |          | 1 : F       | M           |            |            |           |                                                        |     |              |

|     | BDSW               | 1        |             |             |            |            |           |                                                        |     |              |

#### Continued from preceding page.

| No.      | Control block data |             |                                  | Related data                                                          |              |                   |                                                                     |                 |          |

|----------|--------------------|-------------|----------------------------------|-----------------------------------------------------------------------|--------------|-------------------|---------------------------------------------------------------------|-----------------|----------|

| (6)      | DO pin             | • Data t    | o control                        | DO pin ou                                                             | tput         | <u> </u>          |                                                                     |                 | UL0, UL1 |

|          | control data       |             | DOC2                             | DOC1                                                                  | DOC0         |                   | DO pin condition                                                    |                 | CTE      |

|          | DOC0               |             | 0                                | 0                                                                     | 0            | Open              |                                                                     |                 |          |

|          | DOC1               |             | 0                                | 0                                                                     | 1            | Low when unlo     | ock is detected.                                                    |                 |          |

|          | DOC2               |             | 0                                | 1                                                                     | 0            | end-UC (See t     | he item with asterisk below)                                        |                 |          |

|          |                    |             | 0                                | 1                                                                     | 1            | Open              |                                                                     |                 |          |

|          |                    |             | 1                                | 0                                                                     | 0            | Open              |                                                                     |                 |          |

|          |                    |             | 1                                | 0                                                                     | 1            | Low when SD0      |                                                                     |                 |          |

|          |                    |             | 1                                | 1                                                                     | 0            | Low when ster     | eo                                                                  |                 |          |

|          |                    |             | 1                                | 1                                                                     | 1            | Open              |                                                                     |                 |          |

|          |                    |             | -                                |                                                                       | •            | ower ON/reset.    |                                                                     |                 |          |

|          |                    | * IF cou    | inter cour                       | nting end o                                                           | heck         |                   |                                                                     |                 |          |

|          |                    |             | DO pin                           |                                                                       | 1            | —                 | ¬. 1                                                                |                 |          |

|          |                    |             | БО ріп                           |                                                                       | <b>'</b>     |                   | ₩                                                                   |                 |          |

|          |                    |             |                                  | ① Co                                                                  | ounting star | rt ② Co           | ounting end ③ CE : HI                                               |                 |          |

|          |                    |             |                                  |                                                                       |              |                   | ), DO pin opens automatically.                                      |                 |          |

|          |                    |             |                                  | _                                                                     |              |                   | W and check on counting end                                         | can be made.    |          |

|          |                    | 1           | -                                |                                                                       |              | ntered/output (CE |                                                                     | during OF . Hi  |          |

|          |                    |             |                                  | -                                                                     |              | _                 | data input (IN1 and IN2 modes,<br>2). In the DO pin condition durir | -               |          |

|          |                    |             | ,                                |                                                                       | •            | •                 | O serial data is output in synchr                                   | •               |          |

|          |                    |             |                                  |                                                                       | •            | control data (DO  |                                                                     |                 |          |

| (7)      | Unlock detection   |             |                                  |                                                                       |              |                   | ge if PLL is locked.                                                |                 | DOC0     |

|          | data               | Phase       | e error ex                       | ceeding th                                                            | e detection  | n width is judged | to mean that PLL is locked                                          |                 | DOC1     |

|          |                    |             |                                  |                                                                       |              |                   | (* : don't care)                                                    |                 | DOC2     |

|          | UL0, UL1           |             | UL1                              | UL0                                                                   |              |                   |                                                                     |                 |          |

|          |                    |             | 0                                | 0                                                                     | ;            | Stop              | Open                                                                |                 |          |

|          |                    |             | 0                                | 1                                                                     |              | 0                 | Direct output of φE                                                 |                 |          |

|          |                    |             | 1                                |                                                                       |              | i.67μs            | φE extended by 1 to 2 ms                                            |                 |          |

| (0)      | Di                 |             |                                  | . Serial da                                                           | •            |                   |                                                                     |                 |          |

| (8)      | Phase comparator   | • Data t    | o control                        | the dead 2                                                            | zone or pna  | ase comparator    | 1                                                                   |                 |          |

|          | control data       |             | DZ1                              | DZ0                                                                   | Dead z       | one mode          |                                                                     |                 |          |

|          |                    |             | 0                                | 0                                                                     |              | DZA               |                                                                     |                 |          |

|          | DZ0, DZ1           |             | 0                                | 1                                                                     |              | DZB               |                                                                     |                 |          |

|          |                    |             | 1                                | 0                                                                     |              | DZC<br>DZD        |                                                                     |                 |          |

|          |                    | Dead        |                                  | th : DZA <i< td=""><td></td><td></td><td></td><td></td><td></td></i<> |              |                   |                                                                     |                 |          |

| (9)      | Output port data   |             |                                  |                                                                       |              | ports BO1 and B0  | D2                                                                  |                 |          |

|          |                    |             | a" = 0 : O                       | -                                                                     | •            |                   |                                                                     |                 |          |

|          | ВО                 |             | 1 : Lo                           | ow                                                                    |              |                   |                                                                     |                 |          |

| (10)     | Charge pump        | • Data t    | o enforce                        | e control of                                                          | charge pu    | mp output         |                                                                     |                 |          |

|          | control data       |             | DLC                              |                                                                       | pump outp    | ut                |                                                                     |                 |          |

|          | DLC                |             | 0                                |                                                                       | ormal        |                   |                                                                     |                 |          |

|          |                    | * 1         | 1                                |                                                                       | d to LOW     | 2 : !!!-/:        |                                                                     | 0.4             |          |

|          |                    |             |                                  |                                                                       |              |                   | when the VCO control voltage (<br>ump output to LOW and V tune      |                 |          |

|          |                    |             | lear circu                       |                                                                       | OUR DY SEL   | ung une change p  | amp output to LOVV and V tune                                       | 10 A.C.C. (Dean |          |

| (11)     | IFS                |             |                                  |                                                                       | Setting Dat  | a = 0 causes the  | input sensitivity worsening mod                                     | e and the       |          |

| <u> </u> |                    |             | -                                | eases by a                                                            | about 10 to  | 30mVrms.          |                                                                     |                 |          |

| (12)     | LSI test data      | • LSI te    |                                  |                                                                       |              |                   |                                                                     |                 |          |

|          | TECT0 +- 0         |             | ST0                              | ΛII +~ h -                                                            | not to "O"   |                   |                                                                     |                 |          |

|          | TEST0 to 2         |             | TEST1 All to be set to "0" TEST2 |                                                                       |              |                   |                                                                     |                 |          |

|          |                    |             |                                  | power ON                                                              | /reset       |                   |                                                                     |                 |          |

| (13)     | DNC                | • Set da    |                                  |                                                                       |              |                   |                                                                     |                 |          |

|          |                    | <del></del> |                                  |                                                                       |              |                   |                                                                     |                 |          |

#### Continued from preceding page.

| No.  | Control block data           | Description                                                                                                                                                                                                                                                 | Related data |

|------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| (14) | Forced monaural control data | Data to determine the output of output port STSW, controlling the forced stereo functions.  "Data" = 0 : MONO  1 : STEREO                                                                                                                                   |              |

|      | STSW                         |                                                                                                                                                                                                                                                             |              |

| (15) | SD sensitivity control data  | Data to determine the output of output ports SDC, controlling the SD sensitivity  "Data" = SDC0 : 0, SDC1 : 0 → SD sensitivity 1 = 50dBμV (Typ)  SDC0 : 0, SDC1 : 1 → SD sensitivity 2 = 52dBμV (Typ)  SDC0 : 1, SDC1 : 0 → SD sensitivity 3 = 57dBμV (Typ) |              |

|      |                              | SDC0 : 1, SDC1 : 1 $\rightarrow$ SD sensitivity 4 = 62dB $\mu$ V (Typ)  * Above data values indicate the difference of SD sensitivity levels and are reference values.                                                                                      |              |

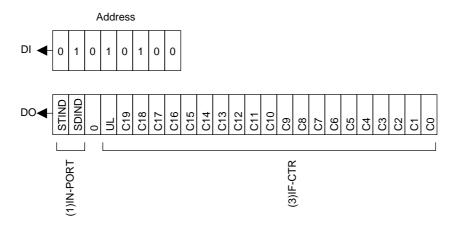

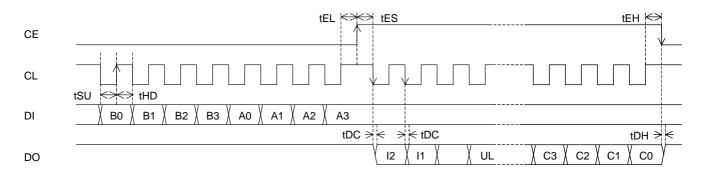

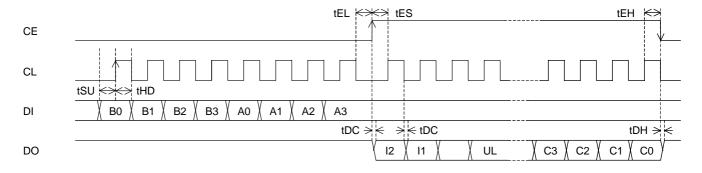

# DO control data (serial data output) composition

#### (1) OUT mode

### **Description of DO output data**

| No. | Control block data | Description                                                     |     |  |  |

|-----|--------------------|-----------------------------------------------------------------|-----|--|--|

| (1) | Stereo and SD      | Data latching stereo and SD indicator conditions.               |     |  |  |

|     | indicators         | Latching made in the data output (OUT) mode.                    |     |  |  |

|     | control data       | SDIND←Stereo indicator condition 0 : ST ON, 1 : ST OFF          |     |  |  |

|     |                    | STIND←SD indicator condition 0 : SD ON, 1 : SD OFF              |     |  |  |

|     | STIND, SDIND       |                                                                 |     |  |  |

| (2) | PLL unlock data    | Data latching the content of unlock detection circuit           |     |  |  |

|     |                    | UL←0 : At unlock                                                | UL1 |  |  |

|     | UL                 | 1 : At lock or in the detection stop mode                       |     |  |  |

| (3) | IF counter,        | Data latching the content of IF counter (20-bit binary counter) | CTE |  |  |

|     | binary counter     | C19←MSB of binary counter                                       | GT0 |  |  |

|     |                    | C0 ←LSB of binary counter                                       | GT1 |  |  |

|     | C19 to C0          |                                                                 |     |  |  |

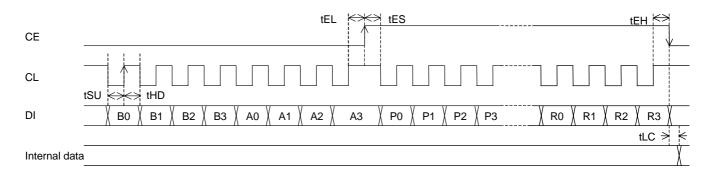

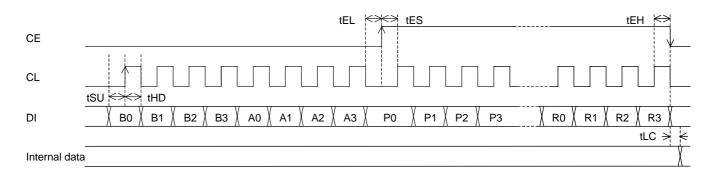

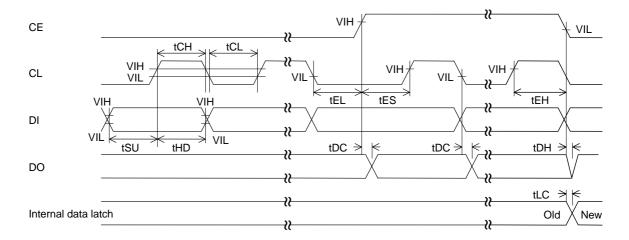

Serial data input (IN1/IN2) tSU, tHD, tEL, tES, tEH≥0.75µs tLC<0.75µs

CL: Normally Hi

CL: Normally Low

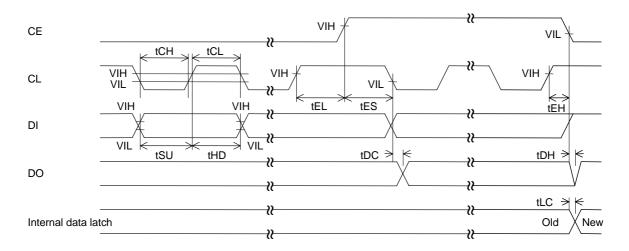

**Serial data output** (OUT) tSU, tHD, tEL, tES, tEH≥0.75µs tDC, tDH<0.35µs

CL: Normally Hi

CL: Normally Hi

(Note) DO pin is an Nch open drain pin, so that the data varying time (tDC and tDH) differs depending on the pull-up resistance and substrate capacity.

#### Serial data timing

<< When CL stops at the "L" level >>

<< When CL stops at the "H" level >>

| Parameter              | Symbol | Pin    | Conditions                                  | Min  | Тур | Max  | Unit |

|------------------------|--------|--------|---------------------------------------------|------|-----|------|------|

| Data setup time        | tSU    | DI, CL |                                             | 0.75 |     |      | μs   |

| Data hold time         | tHD    | DI, CL |                                             | 0.75 |     |      | μs   |

| Clock "L" level time   | tCL    | CL     |                                             | 0.75 |     |      | μs   |

| Clock "H" level time   | tCH    | CL     |                                             | 0.75 |     |      | μs   |

| CE wait time           | tEL    | CE, CL |                                             | 0.75 |     |      | μs   |

| CE setup time          | tES    | CE, CL |                                             | 0.75 |     |      | μs   |

| CE hold time           | tEH    | CE, CL |                                             | 0.75 |     |      | μs   |

| Data latch change time | tLC    |        |                                             |      |     | 0.75 | μs   |

| Data output time       | tDC    | DO, CL | Differs depending on the pull-up resistance |      |     | 0.35 | μs   |

|                        | tDH    | DO, CE | and substrate capacity                      |      |     |      |      |

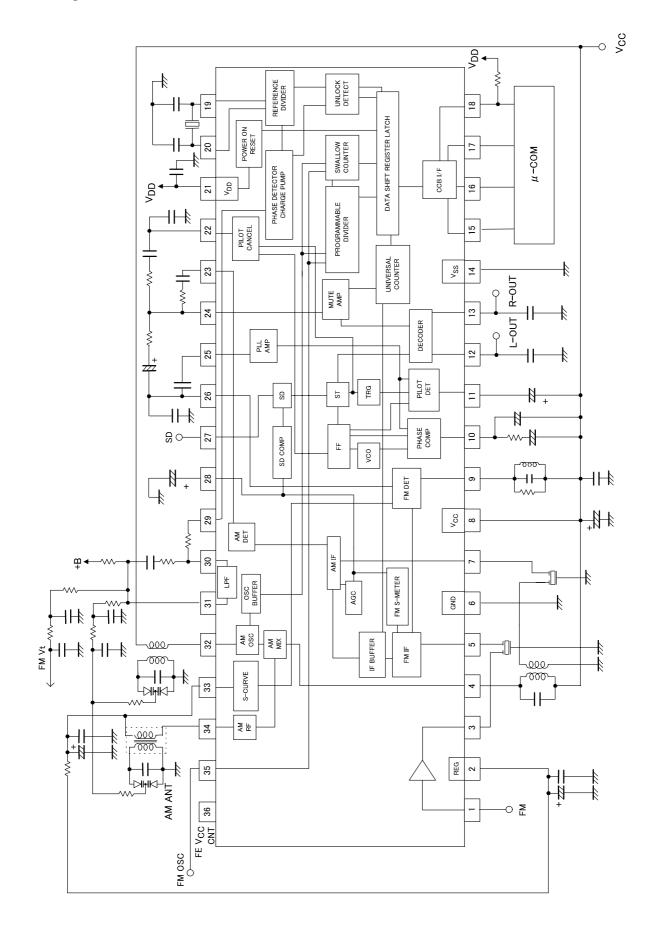

#### **Block Diagram**

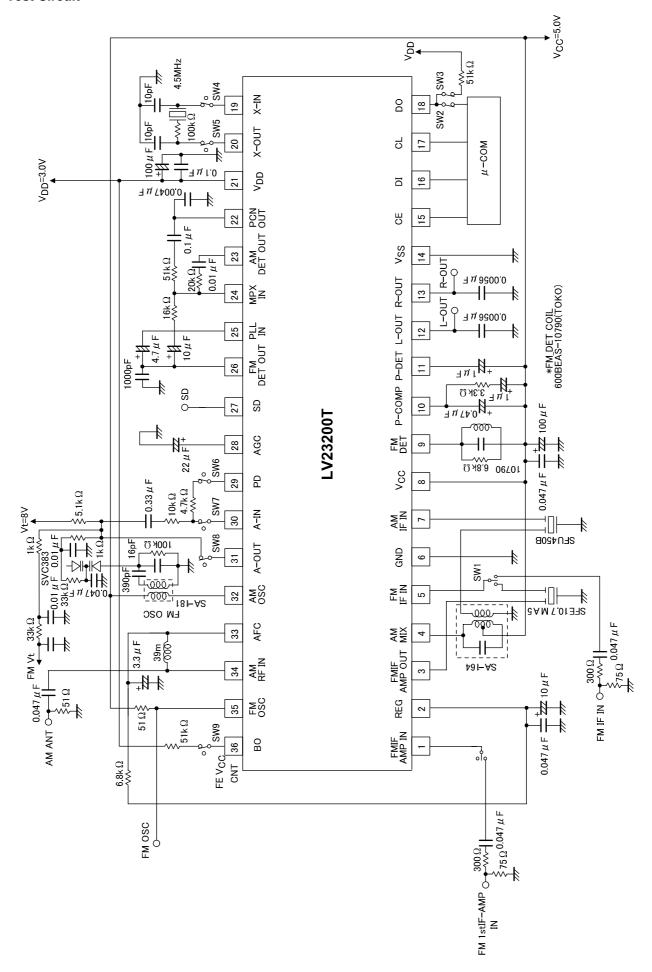

#### **Test Circuit**

- Specifications of any and all SANYO Semiconductor products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Semiconductor Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Semiconductor Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO Semiconductor believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of July, 2005. Specifications and information herein are subject to change without notice.