# **Getting Started with the KXPS5**

## Introduction

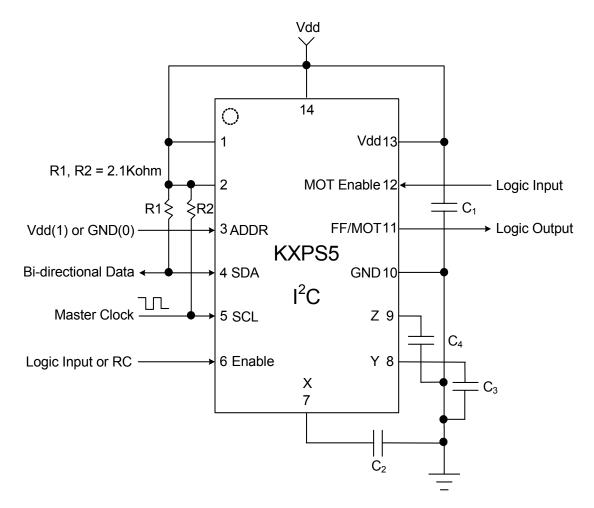

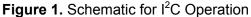

This application note will help users quickly implement proof-of-concept designs using the I<sup>2</sup>C or SPI digital interfaces of the KXPS5 tri-axis accelerometer. Please refer to the KXPS5 Data Sheet for additional implementation guidelines.

#### **Circuit Schematics**

This section shows recommended wiring schematics for the KXPS5 when operating in both  $I^2C$  and SPI modes. It also describes an RC method for enabling the KXPS5 upon power up. Please refer to the KXPS5 Data Sheet for all pin descriptions.

Note: these schematics are recommendations based on proven KXPS5 operation. Your specific application may require modifications from these recommendations.

## I<sup>2</sup>C Schematic

36 Thornwood Dr. – Ithaca, NY 14850 tel: 607-257-1080 – fax: 607-257-1146 www.kionix.com - <u>info@kionix.com</u> © 2006 Kionix, Inc. 9 March 2006 Page 1 of 6

## AN 009

Figure 2. Schematic for SPI Operation

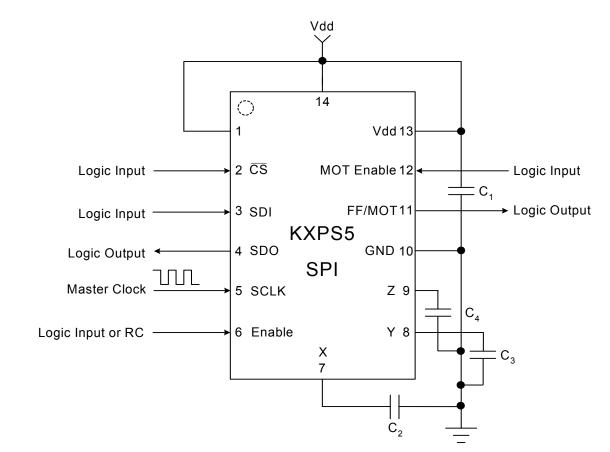

## RC Enable

A good design practice is to control the KXPS5 Enable pin (6) with a microprocessor, but it is also possible to enable the KXPS5 using the RC circuit shown in Figure 3. This circuit will transition the Enable pin high at power on, properly enabling the accelerometer after power has been supplied. Note that the RC values are just recommendations, therefore the final schematic may differ based on application needs.

Figure 3. Schematic for RC Enable

#### Filter Cap Recommendations

To be effective in many applications, such as HDD protection, the KXPS5 needs to respond to changes in acceleration as quickly as possible. The accelerometer's bandwidth, and in turn its response time, is largely determined by the external filter capacitance. Therefore, the filter capacitance should be as small as the application will allow. Table 1 shows several commonly used bandwidths and the associated capacitor values for  $C_2$ ,  $C_3$ , and  $C_4$  in the circuits shown above. For most applications, 500Hz (0.01uF) should be a good starting point. Also, the KXPS5 has an internal 1000Hz 1<sup>st</sup> order low pass filter that allows for operation without any external capacitors.

| Bandwidth<br>(Hz) | Capacitance<br>(uF) |  |  |

|-------------------|---------------------|--|--|

| 50                | 0.10                |  |  |

| 250               | 0.02                |  |  |

| 500               | 0.01                |  |  |

Table 1. Bandwidth (Hz) and Capacitance (uF)

## **Quick Start Implementation**

The KXPS5 offers the user a powerful range of operating options and features, mostly controlled by setting appropriate values in registers. This section is not a comprehensive guide to all of the options and features. Rather it is intended to guide the user to an implementation of the KXPS5 that will get the device up and running as quickly as possible. Once up and running, the user should experiment with different setting and options to reach the optimum performance for their specific application.

The registers shown in Table 2 need to be set to get the KXPS5 up and running:

|                      | Add  | lress     | Recommended Value |           |  |

|----------------------|------|-----------|-------------------|-----------|--|

| <b>Register Name</b> | Hex  | Binary    | Hex               | Binary    |  |

| CTRL_REGB            | 0x0D | 0000 1101 | 0x42              | 0100 0010 |  |

| CTRL_REGC            | 0x0C | 0000 1100 | 0x00              | 0000 0000 |  |

| FF_INT               | 0x08 | 0000 1000 | 0x0E              | 0000 1110 |  |

| FF_DELAY             | 0x09 | 0000 1001 | 0x14              | 0001 0100 |  |

| MOT_INT              | 0x0A | 0000 1010 | 0x55              | 0101 0101 |  |

| MOT_DELAY            | 0x0B | 0000 1011 | 0x14              | 0001 0100 |  |

#### Table 2. KXPS5 Registers

For each register, a set of initial recommended values is provided that will ensure the KXPS5 is configured to a known operational state. Note that these conditions just provide a starting point, and the values should vary as users refine their application requirements.

#### **Register Recommendations**

### CTRL\_REGB

| CLKhld | ENABLE | ST | Х | Х | Х | FFlen | XI |

|--------|--------|----|---|---|---|-------|----|

| 0      | 1      | 0  | 0 | 0 | 0 | 1     | 0  |

Figure 4. Operational Starting Point for CTRL\_REGB

**CLKhId = 0:** The KXPS5 will not hold the  $I^2C$  clock during A/D conversions. **ENABLE = 1:** The KXPS5 is enabled/operational.

**ST = 0:** The KXPS5 self-test function is not enabled/operational.

FFIen = 1: Free-fall detection interrupt is enabled/operational.

#### CTRL\_REGC

| Х | Х | Х | FFLatch | MOTLatch | Х | IntSpd1 | IntSpd0 |

|---|---|---|---------|----------|---|---------|---------|

| 0 | 0 | 0 | 0       | 0        | 0 | 0       | 0       |

Figure 5. Operational Starting Point for CTRL\_REGC

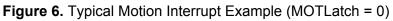

**FFLatch = 0:** The free-fall interrupt output will go high whenever the criterion for free-fall detection is met. The output will return low when the criterion is not met.

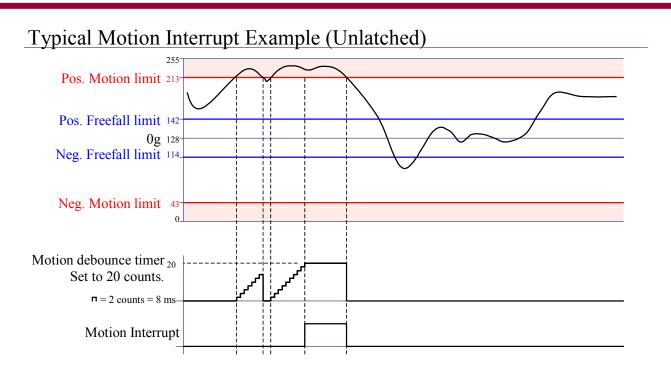

**MOTLatch = 0:** The motion interrupt output will go high whenever the criterion for motion detection is met. The output will return low when the criterion is not met.

**IntSpd1 and IntSpd0 = 0:** The interrupt sampling frequency is 250 samples/second. Therefore, the interrupt delay times can be calculated using Equation 1.

Free-fall Delay (sec) = FF\_Delay (# of samples) / 250 (samples/sec) High-g Motion Delay (sec) = MOT\_Delay (# of samples) / 250 (samples/sec)

Equation 1. Free-fall and Motion Delay Calculations

#### **Thresholds and Delays**

The following are some suggested acceleration thresholds and delay (or dwell) times appropriate for many HDD protection applications. For each suggested parameter the appropriate register value is provided in binary and hexadecimal.

#### Free fall

Detection Threshold = 0.4g FF\_INT = (0000 1110 or 0x0E)

Delay Time = 80mS FF\_DELAY = (0001 0100 or 0x14)

#### High-g Motion

Detection Threshold = 2.5g MOT\_INT = (0101 0101 or 0x55)

## AN 009

Delay Time = 80mS MOT\_DELAY = (0001 0100 or 0x14)

#### **Expected Results**

When the registers are loaded with the recommended values and the MOT Enable pin (12) is pulled high, the KXPS5 becomes armed for HDD protection. This means that the FF/MOT interrupt will be triggered if the accelerometer experiences an event that exceeds any of the above described thresholds and delays. In this case, FF/MOT will go high if all accelerometer axis (X, Y, and Z) simultaneously drop below 0.4g for more than 80mS or if any accelerometer axis (X, Y, or Z) go rise above 2.5g for more than 80mS. Figures 6 and 7 show how the KXPS5 interrupts will react to a typical event.

By monitoring the interrupt pin (11), or repeatedly reading the status register, CTRL\_REGA (0x0C), the user will be notified of a harmful event and must park/unload the HDD head for protection. Note that the interrupts are selected to be unlatched, so they will return low after the event has concluded. For additional information, please refer to the KXPS5 Data Sheet.

## AN 009

Figure 7. Typical Free-fall Interrupt Example (FFLatch = 0)