#### 3.5W/CH STEREO CLASS-D AUDIO POWER AMPLIFIER

#### **GENERAL DESCRIPTION**

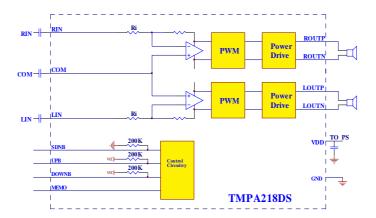

The TMPA218DS is a stereo class-D audio power amplifier IC with digital volume control. With BTL (Bridge-Tied-Load) configuration, it delivers up to 3.5W/ch (7W in all) into a 2 ohm load. Up and down volume control signals provide -60dB attenuation form maximum voltage gain. No external heat-sink is required.

For multiple-input applications, independent gain control and corner frequency can be implemented by summing the input sources through resistor ratio and input capacitor values. Automatic output power control makes the best use of battery.

Analog input signal is converted into digital output which drives directly to the speaker. High power efficiency is achieved due to digital output at the load. The audio information is embedded in PWM(Pulse Width Modulation).

#### **APPLICATIONS**

Multimedia application includes Cellular Phones, PDAs, DVD/CD players, TFT LCD TVs/Monitors, 2.1 channel audio systems, USB audio. It is also ideal for other portable devices like Wireless Radios.

#### **FEATURES**

- ♦ 2.5V to 6V Single Supply

- ♦ Up to 3.5W / Ch at 5.5V, 2 ohms

- ♦ Up to 88% Power Efficiency

- ◆ Automatic output power control (APC)

- ♦ Memory of voltage gain at shutdown

- ♦ 0dB to -60dB attenuation from max. voltage gain

- ◆ 2.2mA / Ch Quiescent Current at 5V

- ♦ Less Than 0.2uA / Ch Shutdown Current

- ◆ Pop-less Power-Up, Shutdown and Recovery

- ◆ Differential 250 KHz PWM Allows Bridge-Tied Load to increase Output Power and Eliminates LC Output Filter

- ♦ Thermal Shutoff and Automatic Recovery

- **♦** Compatible with earphone application

- Output Pin Short-Circuit Protection (Short to Other Outputs, Short to VCC, Short to Ground)

- ♦ Differential Signal Processing Improves CMRR

#### **Package**

TSSOP20 Available, pb free [RoHS]

For best performance, please refer to http://www.taimec.com.tw/English/EVM.htm http://www.class-d.com.tw/English/EVM.htm

for PCB layout.

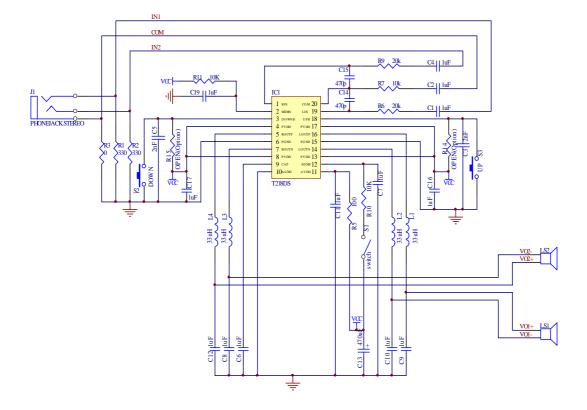

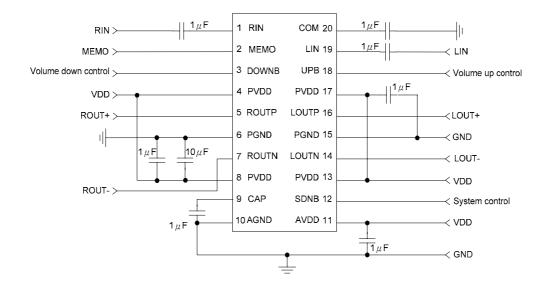

## REFERENCE CIRCUIT (Please refer to TMPA002.APP for application)

# (Please email david@taimec.com.tw for complete datasheet.)

Tai-1 Microelectronics reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers are responsible for their products and applications using Tai-1 Microelectronics components.

Note that the external components or PCB layout should be designed not to generate abnormal voltages to the chip to prevent from latch up which may cause damage to the device.

## **Typical Application**

www.taimec.com.tw / www.class-d.com.tw

TMPA218DS

Rev.1.0 December 24, 2007

#### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range unless otherwise noted(1)

| Supply veltage Van AVan            | In normal mode                  | -0.3V to 6V | V |

|------------------------------------|---------------------------------|-------------|---|

| Supply voltage, VDD, AVDD          | In shutdown mode                | -0.3V to 7V | V |

| Input voltage, Vı                  | -0.3V to VDD+0.3V               |             |   |

| Continuous total power dissipation | See package dissipation ratings |             |   |

| Operating free-air temperature, TA | -20 to 85                       | °C          |   |

| Operating junction temperature, TJ | -20 to 150                      |             |   |

| Storage temperature, Tstg          | -40 to 150                      | °C          |   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions in not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITONS

| PARAMETE                           | TEST CONDITIONS    | MIN            | NOM     | MAX | UNIT    |    |

|------------------------------------|--------------------|----------------|---------|-----|---------|----|

| Supply voltage                     | Vdd, AVdd          |                | 2.5     |     | 6       |    |

| High-level input voltage, VIH1     | VIH for SDNB       |                | 2       |     | VDD     |    |

| Low-level input voltage, Vı∟1      | VIL for SDNB       |                | 0       |     | 0.8     |    |

| High-level input voltage, Vıн2     | VIH for MEMO       | \/ A\/ 5\/     | 70%xVpp |     | VDD     | V  |

| Low-level input voltage, VıL2      | VIL for MEMO       | VDD= AVDD = 5V | 0       | ;   | 30%xVdd |    |

| High-level input voltage, Vıн3     | VIH for UPB, DOWNB |                | 70%xVpp |     | VDD     |    |

| Low-level input voltage, Vı∟3      | VIL for UPB, DOWNB |                | 0       | ;   | 30%xVdd |    |

| Operating free-air temperature, TA |                    |                | -20     |     | 85      | °C |

## **PACKAGE DISSIPATION RATINGS**

| PACKAGE | DERATING    | Ta≤25 °C     | TA = 70 °C   | TA = 85 ℃    |

|---------|-------------|--------------|--------------|--------------|

|         | FACTOR      | POWER RATING | POWER RATING | POWER RATING |

| TSSOP20 | 8.73 mW/ °C | 1.09W        | 698mW        | 567mW        |

#### **ELECTRICAL CHARACTERISTICS**

$T_A$ =25 °C (unless otherwise noted)

|      | PARAMETER                                       | TEST CONDITIONS                                                          | MIN | TYP | MAX | UNIT |

|------|-------------------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| Vos  | Output offset voltage (measured differentially) | V <sub>I</sub> =0V,Av=2, V <sub>DD</sub> =AV <sub>DD</sub> =2.5V to 5.5V |     | 25  |     | mV   |

| PSRR | Power supply rejection ratio                    | $V_{DD}$ =AV $_{DD}$ =2.5V to 5.5V                                       |     | -75 | -55 | dB   |

| CMRR | Common mode rejection ratio                     | $V_{DD}$ =AV $_{DD}$ =2.5V to 5.5V,<br>VIC=1Vpp, RL=8 $\Omega$           |     | -55 | -50 | dB   |

| IIH1 | High-level input current                        | V <sub>DD</sub> =AV <sub>DD</sub> =5.5V,<br>V <sub>I</sub> =5.8V (SDNB)  |     | 30  |     | μΑ   |

| IIL1 | Low-level input current                         | V <sub>DD</sub> =AV <sub>DD</sub> =5.5V,<br>V <sub>I</sub> =-0.3V (SDNB) |     |     | 1   | μΑ   |

| IIH2 | High-level input current                        | V <sub>DD</sub> =AV <sub>DD</sub> =5.5V,<br>VI=5.8V (MEMO)               |     |     | 1   | μΑ   |

| IIL2 | Low-level input current                         | V <sub>DD</sub> =AV <sub>DD</sub> =5.5V,<br>V <sub>I</sub> =-0.3V (MEMO) |     |     | 1   | μΑ   |

TMPA218DS

Rev.1.0 December 24, 2007

www.taimec.com.tw / www.class-d.com.tw

| IIH3                | High-level input current           | V <sub>DD</sub> =AV <sub>DD</sub> =5.5V,<br>VI=5.8V (UPB, DOWNB)               |     |     | 1   | μΑ  |

|---------------------|------------------------------------|--------------------------------------------------------------------------------|-----|-----|-----|-----|

| IIL3                | Low-level input current            | V <sub>DD</sub> =AV <sub>DD</sub> =5.5V,<br>V <sub>I=-</sub> 0.3V (UPB, DOWNB) |     | 30  |     | μΑ  |

| IQ (SD)             | Shutdown current / Ch              | V( SDN )=0.8V, V <sub>DD</sub> =AV <sub>DD</sub> =2.5V to 5.5V                 |     | 0.2 | 0.5 | μA  |

| r <sub>DS(on)</sub> | Static output resistance           | V <sub>DD</sub> =AV <sub>DD</sub> =5.5V                                        |     | 790 |     | mΩ  |

| f(sw)               | Switching frequency                | V <sub>DD</sub> =AV <sub>DD</sub> =2.5V to 5.5V                                | 200 | 250 | 300 | kHz |

| Avmax               | Max. BTL Gain                      | $V_{DD}$ =AV $_{DD}$ =2.5V to 5.5V, RL=8 $\Omega$                              | 21  |     | 25  | db  |

| Rsdn                | Resistance from SDNB to GND        | V(SDNB)= 5V                                                                    |     | 200 |     | kΩ  |

| Rud                 | Resistance from UpB / DownB to VDD | V(UPB)= V(DOWNB)=5V                                                            |     | 200 |     | kΩ  |

| Zı                  | Input impedance                    | RIN,LIN                                                                        |     | 30  |     | kΩ  |

## **OPERATING CHARACTERISTICS**

$T_A \text{=} 25~^{\circ}\text{C},~\text{RL=}8\Omega$  speaker (unless otherwise noted)

| PARAMETER                                            |                                      | TEST CON                                       | MIN TYP                                | MAX | UNIT |    |  |

|------------------------------------------------------|--------------------------------------|------------------------------------------------|----------------------------------------|-----|------|----|--|

|                                                      |                                      | RL=8Ω                                          |                                        | 1.5 |      | w  |  |

| Po                                                   | Output power / Ch                    | RL=4Ω                                          | V <sub>DD</sub> =AV <sub>DD</sub> =5V. | 2.3 |      |    |  |

| Po THD+N=10%,f=1kHz.  (Limited by thermal condition) | ,                                    | RL=3Ω                                          |                                        |     |      | VV |  |

|                                                      |                                      | RL=2Ω                                          | $V_{DD}$ =A $V_{DD}$ =5.5 $V$ .        | 3.5 |      |    |  |

|                                                      |                                      | V <sub>DD</sub> =AV <sub>DD</sub> =5V, Po=1W,  | 0.2                                    |     |      |    |  |

| THD+N                                                | Total harmonic distortion plus noise | V <sub>DD</sub> =AV <sub>DD</sub> =5V, Po=1.5V | 0.2                                    |     | %    |    |  |

|                                                      |                                      | V <sub>DD</sub> =AV <sub>DD</sub> =5V, Po=1.8V | 0.25                                   |     |      |    |  |

| SNR                                                  | Signal-to-noise ratio                | V <sub>DD</sub> =AV <sub>DD</sub> =5V, Po=1W,  | 95                                     |     | dB   |    |  |

| Crosstalk                                            | Crosstalk between outputs            | V <sub>DD</sub> =AV <sub>DD</sub> =5V, Po=1W   | -68                                    |     | dB   |    |  |

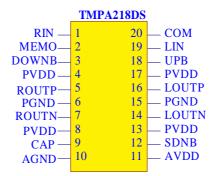

## **TERMINAL FUNCTIONS**

| TERMINAL |        | I/O | DESCRIPTION                                                |  |  |  |

|----------|--------|-----|------------------------------------------------------------|--|--|--|

| NAME     | PIN NO | 1/0 | DESCRIPTION                                                |  |  |  |

| AGND     | 10     | -   | Analog ground                                              |  |  |  |

| AVDD     | 11     | -   | Analog power supply                                        |  |  |  |

| CAP      | 9      | I   | Capacitance for power up delay and UPB/DOWNB reaction time |  |  |  |

| DOWNB    | 3      | I   | Volume down                                                |  |  |  |

| PGND     | 6,15   | -   | Digital ground                                             |  |  |  |

| COM      | 20     | I   | Common ground                                              |  |  |  |

| LIN      | 19     | I   | Left channel input                                         |  |  |  |

| LOUTN    | 14     | 0   | Negative output of left channel                            |  |  |  |

| LOUTP    | 16     | 0   | Positive output of left channel                            |  |  |  |

| RIN      | 1      | I   | Right channel input                                        |  |  |  |

| MEMO     | 2      | I   | Memory                                                     |  |  |  |

| ROUTN    | 7      | 0   | Negative output of right channel                           |  |  |  |

| ROUTP    | 5      | 0   | Positive output of right channel                           |  |  |  |

| SDNB     | 12     | I   | Shutdown terminal (active low logic)                       |  |  |  |

TMPA218DS Rev.1.0 December 24,

www.taimec.com.tw / www.class-d.com.tw

| UPB  | 18        | I | Volume up            |

|------|-----------|---|----------------------|

| PVDD | 4,8,13,17 | - | Digital Power supply |

#### TYPICAL CHARACTERISTICS

- Note 1. Input coupling 1µF capacitors are used for all measurements.

- 2. Differential inputs are applied and BTL outputs are measured.

- 3. Balanced LC filter is used for THD+N measurement and power efficiency measurement.

- 4. Characteristic frequency of the LC filter is set 41 KHz unless otherwise specified.

# Volume Step and Attenuation at Vdd=5v

| Step | Attenuation(dB) | Overall<br>AV(dB) | Step        | Attenuation(dB) | Overall<br>AV(dB) | Step | Attenuation(dB) | Overall<br>AV(dB) |

|------|-----------------|-------------------|-------------|-----------------|-------------------|------|-----------------|-------------------|

| 0    | 0               | 23                | 11          | 12              | 11                | 22   | 36              | -13               |

| 1    | 1               | 22                | <b>※</b> 12 | 14              | 9                 | 23   | 39              | -16               |

| 2    | 2               | 21                | 13          | 16              | 7                 | 24   | 42              | -19               |

| 3    | 3               | 20                | 14          | 18              | 5                 | 25   | 45              | -22               |

| 4    | 4               | 19                | 15          | 20              | 3                 | 26   | 48              | -25               |

| 5    | 5               | 18                | 16          | 22              | 1                 | 27   | 51              | -28               |

| 6    | 6               | 17                | 17          | 24              | -1                | 28   | 54              | -31               |

| 7    | 7               | 16                | 18          | 26              | -3                | 29   | 57              | -34               |

| 8    | 8               | 15                | 19          | 28              | -5                | 30   | 60              | -37               |

| 9    | 9               | 14                | 20          | 30              | -7                | 31   | ∞               | -∞                |

| 10   | 10              | 13                | 21          | 33              | -10               |      |                 |                   |

« Overall gain is preset at 5db at power up.

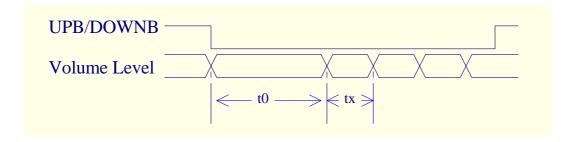

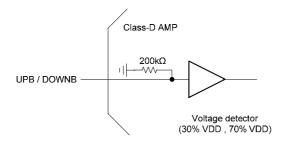

#### Volume UP/DOWN Control

- Volume up and down control is executed by UPB and DOWNB digital input signals.

- · UPB and DOWNB are "low" active.

- · Continuous "low" at UPB or DOWNB will make volume to change continuously.

- · A "low" at DOWNB overwrites a "low" at UPB.

- Timing diagram(capacitance at CAP pin has to be 1uF for following timing relationship)

- 1. First volume change is set at falling edge of UPB/DOWNB input.

- 2. Second volume change is set at ~0.5s(t0) after falling edge of UPB/DOWNB input.

- 3. Following volume changes are set at  $\sim 0.1$ s(tx) from previous change.

Note that the capacitance at pin CAP=1uF for t0=0.5s & t1=0.1s. The delay time t0 & t1 change linearly with capacitance at CAP pin, i.e. t0=1s & t1=0.2s if CAP=2uF.

#### **APPLICATION INFORMATION**

#### **DETAILED DESCRIPTION**

## **Efficiency**

The output transistors of a class D amplifier act as switches. The power loss is mainly due to the turn on resistance of the output transistors when driving current to the load. As the turn on resistance is so small that the power loss is small and the power efficiency is high. With 8 ohm load the power efficiency can be up to 88%.

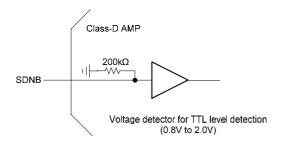

#### Shutdown

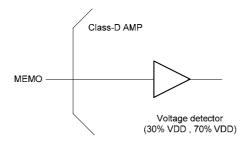

The shutdown mode reduces power consumption. A LOW at shutdown pin forces the device in shutdown mode and a HIGH forces the device in normal operating mode. Shutdown mode is useful for power saving when not in use. This function is useful when other devices like earphone amplifier on the same PCB are used but class D amplifier is not necessary. Internal circuit for shutdown is shown below.

Note that shutdown pin or SDNB is also used for volume control. Please refer to Voltage Gain section for details

## **Pop-less**

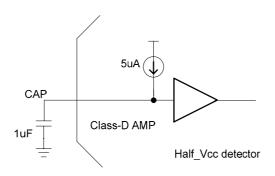

A soft start capacitor can be added to the CAP pin. This capacitor introduces delay for the internal circuit to be stable before driving the load. The pop or click noise when power up/down or switching in between shutdown mode can be thus eliminated. The delay time is proportional to the value of the capacitance. It is about 500ms for a capacitor of 1uF at 5v.

#### **CAP**

Cap provides a way of soft startup delay. A 5uA current source and a half\_Vcc detector are integrated in the chip. The charged capacitor is externally hooked up. For C=1uF the half\_Vcc delay is

$$T = CV/I = (1uF \times 2.5V)/5uA = 0.5$$

seconds

## Voltage gain

The voltage gain is preset, at power up, to 5db typical with 8 ohms load. The voltage gain can be increased by applying a LOW at UPB or decreased by applying a LOW at DOWNB. The maximum gain it can reach is 23db and the minimum gain is -55db. Beyond -55db is a MUTE.

## Memory of voltage gain

The voltage gain is preset to 5db at power up. The voltage gain can be changed to higher or lower value by applying a LOW at UPB or DOWNB. The changed voltage gain can be memorized during shutdown if MEMO=Vcc. In other words the voltage gain is the same before and after shutdown operation with MEMO=Vcc. Note that a RC delay is necessary between Vcc & MEMO at power up to ensure proper operation of the memory.

# tai'mec

## **Preliminary**

TMPA218DS Rev.1.0 December 24,

www.taimec.com.tw / www.class-d.com.tw

During shutdown mode, memory of voltage gain is still in effect even battery is removed for some time. The time period in which the voltage gain is still memorized during battery removed depends on the Vcc-GND capacitance and Vcc voltage.

Example 1. Four-battery power supply with Vcc-GND capacitance equals 1000uF.

If the voltage of each exhausted battery to be replaced is 1.0v on average then the voltage on the 1000uF capacitor is 4.0v. Since the chip can keep memory for down to 0.5v, the voltage allowed to drop is 4.0v-0.5v=3.5v. The voltage drop is caused by the small leakage of the chip, typical 0.2uA, during shutdown. So the time to survive is

$CV/I = 1000uF \times 3.5v/ 0.2uA = 17500 sec = 4.8 hrs$

Example 2. Two-battery power supply with Vcc-GND capacitance equals 1000uF.

If the voltage of each exhausted battery to be replaced is 1.0v on average then the voltage on the 1000uF capacitor is 2.0v. The voltage allowed to drop is 2.0v-0.5v=1.5v. With typical leakage current of 0.2uA the time to survive is

$CV/I = 1000 uF \times 1.5 v / 0.2 uA = 7500 sec = 2.08 hrs$

## **Automatic output Power Control (APC)**

The voltage gain is self adjusted in the chip over voltage range. This means that, regardless supply voltage change, the output power keeps about the same for a given input level from V<sub>DD</sub>=5.5v to 2.5v. It allows the best use of the battery.

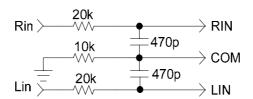

#### Input filter

Input filter is not required for most of the applications. However in some designs if it is necessary to reduce overall voltage gain, one can add an external input resistor as a voltage divider. It is advantageous to add a capacitor in between positive input and negative input to form an input filter.

An example to reduce voltage gain to 60%, as shown in the schematic on page 2, is also shown below. Note that the layout of input traces has to be symmetric.

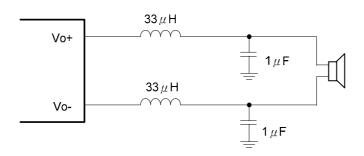

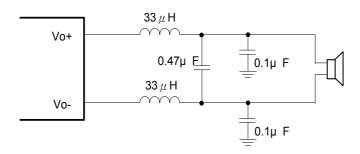

## **Output filter**

Ferrite bead filter can be used for EMI purpose. The ferrite filter reduces EMI around 1 MHz and higher ( FCC and CE only test radiated emissions greater than 30 MHz ) . When selecting a ferrite bead, choose one with high impedance at high frequencies, but low impedance at low frequencies.

Use an LC output filter if there are low frequency ( < 1 MHz) EMI sensitive circuits and/or there are long wires from the amplifier to the speaker. EMI is also affected by PCB layout and the placement of the surrounding components.

The suggested LC values for different speaker impendence are showed in following figures for reference.

Typical LC Output Filter (1)

www.taimec.com.tw / www.class-d.com.tw

TMPA218DS Rev.1.0 December 24,

#### Typical LC Output Filter (2)

## Over temperature protection

A temperature sensor is built in the device to detect the temperature inside the device. When a high temperature around 145°C and above is detected the switching output signals are disabled to protect the device from over temperature. Automatic recovery circuit enables the device to come back to normal operation when the internal temperature of the device is below around 120°C.

## Over current protection

A current detection circuit is built in the device to detect the switching current of the output stages of the device. It disables the device when the current is beyond about 3.5amps. It protects the device when there is an accident short between outputs or between output and power/gnd pins. It also protects the device when an abnormal low impedance is tied to the output. High current beyond the specification may potentially causes electron migration and permanently damage the device. Shutdown or power down is necessary to resolve the protection situation. There is no automatic recovery from over current protection.

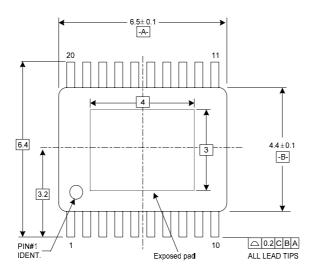

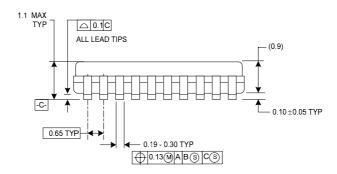

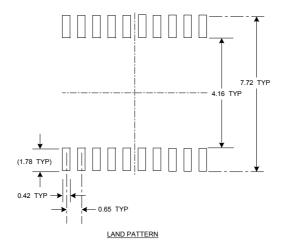

# Physical Dimensions (IN MILLIMETERS)

TSSOP20

tai'mec

## **Preliminary**

www.taimec.com.tw / www.class-d.com.tw

TMPA218DS Rev.1.0 December 24,

**IMPORTANT NOTICE**

Tai-1 Microelectronics Corp. reserves the right to make changes to its products and services and to

discontinue any product or service without notice. Customers should obtain the latest relevant information for

reference. Testing and quality control techniques are used to screen the parameters. Testing of all parameters

of each product is not necessarily performed.

Tai-1 Microelectronics Corp. assumes no liability for applications assistance or customer product design. To

minimize the risks associated with customer products and applications, customers should provide adequate

design and operating safeguards.

Reproduction of information in data sheets or related documentation is permissible only if reproduction is

without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Tai-1

Microelectronics Corp. is not responsible or liable for such altered documentation.

Resale of Tai-1 Microelectronics Corp. products or services with statements different from the parameters

stated by Tai-1 Microelectronics Corp. for that product or service voids all express and any implied warranties.

Tai-1 Microelectronics Corp. is not responsible or liable for any such statements.

Copyright ©2005, Tai-1 Microelectronics Corp.

13