## **PRELIMINARY**

# XRT86VL32

#### DUAL T1/E1/J1 FRAMER/LIU COMBO - E1 REGISTER DESCRIPTION

JULY 2005 REV. P1.0.5

#### **GENERAL DESCRIPTION**

The XRT86VL32 is a two-channel 1.544 Mbit/s or 2.048 Mbit/s DS1/E1/J1 framer and LIU integrated solution featuring R<sup>3</sup> technology (Relayless, Reconfigurable, Redundancy). The physical interface is optimized with internal impedance, and with the patented pad structure, the XRT86VL32 provides protection from power failures and hot swapping.

The XRT86VL32 contains an integrated DS1/E1/J1 framer and LIU which provide DS1/E1/J1 framing and error accumulation in accordance with ANSI/ITU\_T specifications. Each framer has its own framing synchronizer and transmit-receive slip buffers. The slip buffers can be independently enabled or disabled as required and can be configured to frame to the common DS1/E1/J1 signal formats.

Each Framer block contains its own Transmit and Receive T1/E1/J1 Framing function. There are 3 Transmit HDLC controllers per channel which encapsulate contents of the Transmit HDLC buffers into LAPD Message frames. There are 3 Receive HDLC controllers per channel which extract the

payload content of Receive LAPD Message frames from the incoming T1/E1/J1 data stream and write the contents into the Receive HDLC buffers. Each framer also contains a Transmit and Overhead Data Input port, which permits Data Link Terminal Equipment direct access to the outbound T1/E1/J1 frames. Likewise, a Receive Overhead output data port permits Data Link Terminal Equipment direct access to the Data Link bits of the inbound T1/E1/J1 frames.

The XRT86VL32 fully meets all of the latest T1/E1/J1 specifications: ANSI T1/E1.107-1988, ANSI T1/E1.403-1995, ANSI T1/E1.231-1993, ANSI T1/E1.408-1990, AT&T TR 62411 (12-90) TR54016, and ITU G-703, G.704, G706 and G.733, AT&T Pub. 43801, and ETS 300 011, 300 233, JT G.703, JT G.704, JT G706, I.431. Extensive test and diagnostic functions include Loop-backs, Boundary scan, Pseudo Random bit sequence (PRBS) test pattern generation, Performance Monitor, Bit Error Rate (BER) meter, forced error insertion, and LAPD unchannelized data payload processing according to ITU-T standard Q.921.

#### **APPLICATIONS AND FEATURES (NEXT PAGE)**

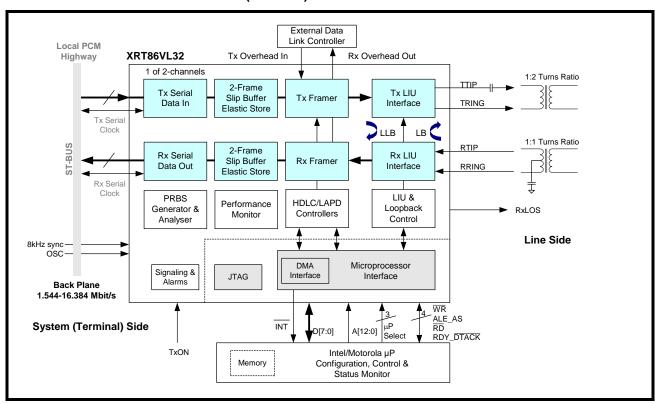

FIGURE 1. XRT86VL32 2-CHANNEL DS1 (T1/E1/J1) FRAMER/LIU COMBO

#### **APPLICATIONS**

- High-Density T1/E1/J1 interfaces for Multiplexers, Switches, LAN Routers and Digital Modems

- SONET/SDH terminal or Add/Drop multiplexers (ADMs)

- T1/E1/J1 add/drop multiplexers (MUX)

- Channel Service Units (CSUs): T1/E1/J1 and Fractional T1/E1/J1

- Digital Access Cross-connect System (DACs)

- Digital Cross-connect Systems (DCS)

- Frame Relay Switches and Access Devices (FRADS)

- ISDN Primary Rate Interfaces (PRA)

- PBXs and PCM channel bank

- T3 channelized access concentrators and M13 MUX

- Wireless base stations

- ATM equipment with integrated DS1 interfaces

- Multichannel DS1 Test Equipment

- T1/E1/J1 Performance Monitoring

- Voice over packet gateways

- Routers

#### **FEATURES**

- Two independent, full duplex DS1 Tx and Rx Framer/LIUs

- Two 512-bit (two-frame) elastic store, PCM frame slip buffers (FIFO) on TX and Rx provide up to 8.192 MHz asynchronous back plane connections with jitter and wander attenuation

- Supports input PCM and signaling data at 1.544, 2.048, 4.096 and 8.192 Mbits. Also supports 2-channel multiplexed 12.352/16.384 (HMVIP/H.100) Mbit/s on the back plane bus

- Programmable output clocks for Fractional T1/E1/J1

- Supports Channel Associated Signaling (CAS)

- Supports Common Channel Signalling (CCS)

- Supports ISDN Primary Rate Interface (ISDN PRI) signaling

- Extracts and inserts robbed bit signaling (RBS)

- 3 Integrated HDLC controllers per channel for transmit and receive, each controller having two 96-byte buffers (buffer 0 / buffer 1)

- HDLC Controllers Support SS7

- Timeslot assignable HDLC

- V5.1 or V5.2 Interface

- Automatic Performance Report Generation (PMON Status) can be inserted into the transmit LAPD interface every 1 second or for a single transmission

- Alarm Indication Signal with Customer Installation signature (AIS-CI)

- Remote Alarm Indication with Customer Installation (RAI-CI)

- Gapped Clock interface mode for Transmit and Receive.

- Intel/Motorola and Power PC interfaces for configuration, control and status monitoring

- Parallel search algorithm for fast frame synchronization

- Wide choice of T1 framing structures: SF/D4, ESF, SLC®96, T1DM and N-Frame (non-signaling)

- Direct access to D and E channels for fast transmission of data link information

#### **PRELIMINARY**

XRT86VL32

#### **DUAL T1/E1/J1 FRAMER/LIU COMBO - E1 REGISTER DESCRIPTION**

- PRBS, QRSS, and Network Loop Code generation and detection

- Programmable Interrupt output pin

- Supports programmed I/O and DMA modes of Read-Write access

- Each framer block encodes and decodes the T1/E1/J1 Frame serial data

- Detects and forces Red (SAI), Yellow (RAI) and Blue (AIS) Alarms

- Detects OOF, LOF, LOS errors and COFA conditions

- Loopbacks: Local (LLB) and Line remote (LB)

- Facilitates Inverse Multiplexing for ATM

- Performance monitor with one second polling

- Boundary scan (IEEE 1149.1) JTAG test port

- Accepts external 8kHz Sync reference

- 1.8V Inner Core

- 3.3V CMOS operation with 5V tolerant inputs

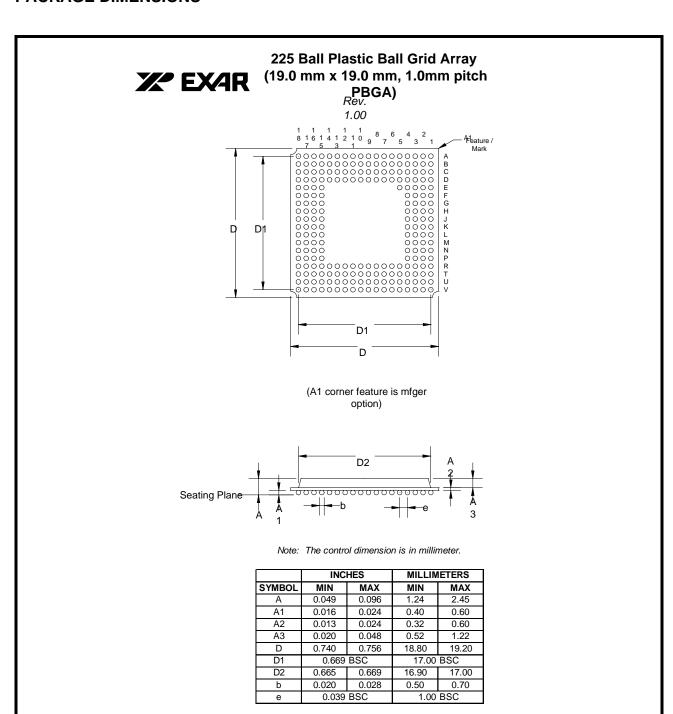

- 225-pin PBGA package with -40°C to +85°C operation

#### ORDERING INFORMATION

| Part Number | PACKAGE                     | OPERATING TEMPERATURE RANGE |

|-------------|-----------------------------|-----------------------------|

| XRT86VL32IB | 225 Plastic Ball Grid Array | -40°C to +85°C              |

## **LIST OF PARAGRAPHS**

| 1.0 REGISTER DESCRIPTION | NS - E1 MODE |                  | <br>9   |

|--------------------------|--------------|------------------|---------|

| 2.0 LINE INTERFACE UNIT  | LIU SECTION) | <b>REGISTERS</b> | <br>143 |

## LIST OF FIGURES

| Figure 1.: XRT86VL32 2-channel DS1 (T1 | E1/J1) Framer/LIU C | Combo | 1 |

|----------------------------------------|---------------------|-------|---|

|----------------------------------------|---------------------|-------|---|

## LIST OF TABLES

| TABLE 1: I | REGISTER SUMMARY                                          |                     | 4  |

|------------|-----------------------------------------------------------|---------------------|----|

| TABLE 2: ( | CLOCK SELECT REGISTER (CSR)                               | HEX ADDRESS: 0XN100 | 9  |

| TABLE 3: I | LINE INTERFACE CONTROL REGISTER (LICR)                    | HEX ADDRESS: 0XN101 | 11 |

| TABLE 4: I | Framing Select Register (FSR)                             | HEX ADDRESS: 0XN107 | 13 |

| TABLE 5: A | ALARM GENERATION REGISTER (AGR)                           | HEX ADDRESS: 0XN108 | 17 |

| TABLE 6: S | SYNCHRONIZATION MUX REGISTER (SMR)                        | HEX ADDRESS: 0XN109 | 19 |

| TABLE 7:   | Transmit Signaling and Data Link Select Register (TSDLSR) | HEX ADDRESS:0XN10A  | 21 |

| TABLE 8: 1 | FRAMING CONTROL REGISTER (FCR)                            | HEX ADDRESS: 0XN10B | 24 |

| TABLE 9: I | RECEIVE SIGNALING & DATA LINK SELECT REGISTER (RSDLSR)    | HEX ADDRESS: 0XN10C | 26 |

| TABLE 10:  | RECEIVE SIGNALING CHANGE REGISTER 0 (RSCR 0)              | HEX ADDRESS: 0XN10D | 28 |

| TABLE 11:  | RECEIVE SIGNALING CHANGE REGISTER 1 (RSCR 1)              | HEX ADDRESS: 0XN10E | 28 |

| TABLE 12:  | RECEIVE SIGNALING CHANGE REGISTER 2 (RSCR 2)              | HEX ADDRESS: 0XN10F | 28 |

| TABLE 13:  | RECEIVE SIGNALING CHANGE REGISTER 3 (RSCR 3)              | HEX ADDRESS: 0XN110 | 29 |

| TABLE 14:  | RECEIVE NATIONAL BITS REGISTER (RNBR)                     | HEX ADDRESS: 0XN111 | 30 |

| TABLE 15:  | RECEIVE EXTRA BITS REGISTER (REBR)                        | HEX ADDRESS: 0XN112 | 31 |

| TABLE 16:  | DATA LINK CONTROL REGISTER (DLCR1)                        | HEX ADDRESS: 0XN113 | 33 |

| TABLE 17:  | TRANSMIT DATA LINK BYTE COUNT REGISTER (TDLBCR1)          | HEX ADDRESS: 0XN114 | 35 |

| TABLE 18:  | RECEIVE DATA LINK BYTE COUNT REGISTER (RDLBCR1)           | HEX ADDRESS: 0XN115 | 36 |

| TABLE 19:  | SLIP BUFFER CONTROL REGISTER (SBCR)                       | HEX ADDRESS: 0XN116 | 37 |

| TABLE 20:  | FIFO LATENCY REGISTER (FFOLR)                             | HEX ADDRESS: 0XN117 | 38 |

| TABLE 21:  | DMA 0 (WRITE) CONFIGURATION REGISTER (DOWCR)              | HEX ADDRESS: 0XN118 | 39 |

| TABLE 22:  | DMA 1 (READ) CONFIGURATION REGISTER (D1RCR)               | HEX ADDRESS: 0xn119 | 40 |

| TABLE 23:  | INTERRUPT CONTROL REGISTER (ICR)                          | HEX ADDRESS: 0XN11A | 41 |

| TABLE 24:  | LAPD SELECT REGISTER (LAPDSR)                             | HEX ADDRESS: 0XN11B | 42 |

| TABLE 25:  | PERFORMANCE REPORT CONTROL REGISTER (PRCR)                | HEX ADDRESS: 0XN11D | 42 |

| TABLE 26:  | GAPPED CLOCK CONTROL REGISTER (GCCR)                      | HEX ADDRESS: 0XN11E | 43 |

| TABLE 27:  | TRANSMIT INTERFACE CONTROL REGISTER (TICR)                | HEX ADDRESS:0XN120  | 44 |

| TABLE 28:  | TRANSMIT INTERFACE SPEED WHEN MULTIPLEXED MODE IS DISABLE | .ED (TXMUXEN = 0)   | 46 |

|            | TRANSMIT INTERFACE SPEED WHEN MULTIPLEXED MODE IS ENABLI  |                     |    |

|            | PRBS CONTROL AND STATUS REGISTER 0 (PRBSCSR0)             | HEX ADDRESS: 0xn121 |    |

|            | RECEIVE INTERFACE CONTROL REGISTER (RICR)                 | HEX ADDRESS: 0XN122 |    |

|            | RECEIVE INTERFACE SPEED WHEN MULTIPLEXED MODE IS DISABLE  | ED (TXMUXEN = 0)    | 52 |

|            | RECEIVE INTERFACE SPEED WHEN MULTIPLEXED MODE IS ENABLED  |                     |    |

|            | PRBS CONTROL AND STATUS REGISTER 1 (PRBSCSR1)             | HEX ADDRESS: 0XN123 |    |

| TABLE 35:  | LOOPBACK CODE CONTROL REGISTER (LCCR)                     | HEX ADDRESS: 0XN124 | 56 |

|            | TRANSMIT LOOPBACK CODER REGISTER (TLCR)                   | HEX ADDRESS: 0XN125 |    |

|            | RECEIVE LOOPBACK ACTIVATION CODE REGISTER (RLACR)         | HEX ADDRESS: 0XN126 | 56 |

|            | RECEIVE LOOPBACK DEACTIVATION CODE REGISTER (RLDCR)       | HEX ADDRESS: 0XN127 |    |

|            | DEFECT DETECTION ENABLE REGISTER (DDER)                   | HEX ADDRESS: 0XN129 | 56 |

| TABLE 40:  | TRANSMIT SA SELECT REGISTER (TSASR)                       | HEX ADDRESS: 0XN130 | 57 |

|            | TRANSMIT SA AUTO CONTROL REGISTER 1 (TSACR1)              | HEX ADDRESS: 0XN131 |    |

| TABLE 42:  | CONDITIONS ON RECEIVE SIDE WHEN TSACR1 BITS ARE ENABLED   |                     |    |

|            | TRANSMIT SA AUTO CONTROL REGISTER 2 (TSACR2)              | HEX ADDRESS: 0XN132 |    |

|            | CONDITIONS ON RECEIVE SIDE WHEN TSACR2 BITS ENABLED       |                     | 62 |

|            | TRANSMIT SA4 REGISTER (TSA4R)                             | HEX ADDRESS: 0XN133 |    |

|            | TRANSMIT SA5 REGISTER (TSA5R)                             | HEX ADDRESS: 0XN134 | 63 |

|            | TRANSMIT SA6 REGISTER (TSA6R)                             | HEX ADDRESS: 0XN135 | 63 |

|            | TRANSMIT SAT REGISTER (TSATR)                             | HEX ADDRESS: 0XN136 |    |

|            | TRANSMIT SA8 REGISTER (TSA8R)                             | HEX ADDRESS: 0XN137 |    |

|            | RECEIVE SA4 REGISTER (RSA4R)                              | HEX ADDRESS: 0XN13B |    |

|            | RECEIVE SA5 REGISTER (RSA5R)                              | HEX ADDRESS: 0XN13C | 65 |

|            | RECEIVE SA6 REGISTER (RSA6R)                              | HEX ADDRESS: 0xn13D |    |

|            | RECEIVE SAT REGISTER (RSATR)                              | HEX ADDRESS: 0xn13E |    |

|            | RECEIVE SA8 REGISTER (RSA8R)                              | HEX ADDRESS: 0XN13F |    |

|            | DATA LINK CONTROL REGISTER (DLCR2)                        | HEX ADDRESS: 0xN143 |    |

|            | TRANSMIT DATA LINK BYTE COUNT REGISTER (TDLBCR2)          | HEX ADDRESS: 0XN144 |    |

|            | RECEIVE DATA LINK BYTE COUNT REGISTER (RDLBCR2)           | HEX ADDRESS: 0XN145 |    |

|            | DATA LINK CONTROL REGISTER (DLCR3)                        | HEX ADDRESS: 0XN153 |    |

|            | TRANSMIT DATA LINK BYTE COUNT REGISTER (TDLBCR3)          | HEX ADDRESS: 0XN154 |    |

|            | RECEIVE DATA LINK BYTE COUNT REGISTER (RDLBCR3)           | HEX ADDRESS: 0XN155 |    |

|            | DEVICE ID REGISTER (DEVID)                                | HEX ADDRESS: 0XN1FE |    |

|            | REVISION ID REGISTER (REVID)                              | HEX ADDRESS: 0XN1FF |    |

|            |                                                           |                     |    |

## DUAL T1/E1/J1 FRAMER/LIU COMBO - E1 REGISTER DESCRIPTION

| TABLE 63: TRANSMIT CHANNEL CONTROL REGISTER 0-31 (TCCR 0-31)       | HEX ADDRESS: 0XN300 TO 0XN31F76       |

|--------------------------------------------------------------------|---------------------------------------|

| TABLE 64: TRANSMIT USER CODE REGISTER 0 - 31 (TUCR 0-31)           | HEX ADDRESS: 0XN320 TO 0XN33F 78      |

| TABLE 65: TRANSMIT SIGNALING CONTROL REGISTER 0-31 (TSCR 0-31)     | HEX ADDRESS: 0XN340 TO 0XN35F 79      |

| TABLE 66: RECEIVE CHANNEL CONTROL REGISTER X (RCCR 0-31)           | HEX ADDRESS: 0XN360 TO 0XN37F82       |

| TABLE 67: RECEIVE USER CODE REGISTER 0-31 (RUCR 0-31)              | HEX ADDRESS: 0XN380 TO 0XN39F 84      |

| TABLE 68: RECEIVE SIGNALING CONTROL REGISTER 0-31 (RSCR 0-31)      | HEX ADDRESS: 0XN3A0 TO 0XN3BF85       |

| TABLE 69: RECEIVE SUBSTITUTION SIGNALING REGISTER 0-31 (RSSR 0-31) | HEX ADDRESS 0XN3C0 TO 0XN3DF87        |

| TABLE 70: RECEIVE SIGNALING ARRAY REGISTER 0 - 31 (RSAR 0-31)      | HEX ADDRESS: 0XN500 TO 0XN51F88       |

| TABLE 71: LAPD BUFFER 0 CONTROL REGISTER (LAPDBCR0)                | HEX ADDRESS: 0XN600 TO 0XN66089       |

| TABLE 72: LAPD BUFFER 1 CONTROL REGISTER (LAPDBCR1)                | HEX ADDRESS: 0XN700 TO 0XN76089       |

| TABLE 73: PMON RECEIVE LINE CODE VIOLATION COUNTER MSB (RLCVC)     | J) HEX ADDRESS: 0XN900 90             |

| TABLE 74: PMON RECEIVE LINE CODE VIOLATION COUNTER LSB (RLCVCL     |                                       |

| TABLE 75: PMON RECEIVE FRAMING ALIGNMENT BIT ERROR COUNTER MSE     |                                       |

| TABLE 76: PMON RECEIVE FRAMING ALIGNMENT BIT ERROR COUNTER LSB     | · · · · · · · · · · · · · · · · · · · |

| TABLE 77: PMON RECEIVE SEVERELY ERRORED FRAME COUNTER (RSEFC)      |                                       |

| TABLE 78: PMON RECEIVE CRC-4 BIT ERROR COUNTER - MSB (RSBBECO      |                                       |

| TABLE 79: PMON RECEIVE CRC-4 BLOCK ERROR COUNTER - LSB (RSBBE      |                                       |

| TABLE 80: PMON RECEIVE FAR-END BLOCK ERROR COUNTER - MSB (RFE      | •                                     |

| TABLE 81: PMON RECEIVE FAR END BLOCK ERROR COUNTER -LSB (RFEB      | ,                                     |

| TABLE 82: PMON RECEIVE SLIP COUNTER (RSC)                          | HEX ADDRESS: 0XN909                   |

| TABLE 83: PMON RECEIVE LOSS OF FRAME COUNTER (RLFC)                | HEX ADDRESS: 0XN90A                   |

| TABLE 84: PMON RECEIVE CHANGE OF FRAME ALIGNMENT COUNTER (RCF.     |                                       |

| TABLE 85: PMON LAPD FRAME CHECK SEQUENCE ERROR COUNTER ( ICF)      | •                                     |

| TABLE 86: PMON PRBS BIT ERROR COUNTER MSB (PBECU)                  | HEX ADDRESS: 0XN900                   |

| , ,                                                                | HEX ADDRESS: 0XN90E                   |

| TABLE 87: PMON PRBS BIT ERROR COUNTER LSB (PBECL)                  |                                       |

| TABLE 88: PMON TRANSMIT SLIP COUNTER (TSC)                         | HEX ADDRESS: 0XN90F                   |

| TABLE 89: PMON EXCESSIVE ZERO VIOLATION COUNTER MSB (EZVCU)        | HEX ADDRESS: 0XN910                   |

| TABLE 90: PMON Excessive Zero Violation Counter LSB (EZVCL)        | HEX ADDRESS: 0xN911                   |

| TABLE 91: PMON FRAME CHECK SEQUENCE ERROR COUNTER 2 (LFCSEC        |                                       |

| TABLE 92: PMON FRAME CHECK SEQUENCE ERROR COUNTER 3 (LFCSEC        |                                       |

| TABLE 93: BLOCK INTERRUPT STATUS REGISTER (BISR)                   | HEX ADDRESS: 0XNB00                   |

| TABLE 94: BLOCK INTERRUPT ENABLE REGISTER (BIER)                   | HEX ADDRESS: 0xNB01 100               |

| TABLE 95: ALARM & ERROR INTERRUPT STATUS REGISTER (AEISR)          | HEX ADDRESS: 0XNB02 102               |

| TABLE 96: ALARM & ERROR INTERRUPT ENABLE REGISTER (AEIER)          | HEX ADDRESS: 0XNB03 105               |

| TABLE 97: FRAMER INTERRUPT STATUS REGISTER (FISR)                  | HEX ADDRESS: 0XNB04 107               |

| TABLE 98: FRAMER INTERRUPT ENABLE REGISTER (FIER)                  | HEX ADDRESS: 0XNB05110                |

| TABLE 99: DATA LINK STATUS REGISTER 1 (DLSR1)                      | HEX ADDRESS: 0XNB06 112               |

| TABLE 100: DATA LINK INTERRUPT ENABLE REGISTER 1 (DLIER1)          | HEX ADDRESS: 0xnB07 114               |

| TABLE 101: SLIP BUFFER INTERRUPT STATUS REGISTER (SBISR)           | HEX ADDRESS: 0XNB08 116               |

| TABLE 102: SLIP BUFFER INTERRUPT ENABLE REGISTER (SBIER)           | HEX ADDRESS: 0XNB09 119               |

| TABLE 103: RECEIVE LOOPBACK CODE INTERRUPT AND STATUS REGISTER (F  | ,                                     |

| TABLE 104: RECEIVE LOOPBACK CODE INTERRUPT ENABLE REGISTER (RLCI   | ,                                     |

| TABLE 105: RECEIVE SA INTERRUPT STATUS REGISTER (RSAISR)           | HEX ADDRESS: 0XNB0C124                |

| TABLE 106: RECEIVE SA INTERRUPT ENABLE REGISTER (RSAIER)           | HEX ADDRESS: 0XNB0D127                |

| TABLE 107: EXCESSIVE ZERO STATUS REGISTER (EXZSR)                  | HEX ADDRESS: 0XNB0E130                |

| TABLE 108: EXCESSIVE ZERO ENABLE REGISTER (EXZER)                  | HEX ADDRESS: 0XNB0F131                |

| TABLE 109: RXLOS/CRC INTERRUPT STATUS REGISTER (RLCISR)            | HEX ADDRESS: 0XNB12 132               |

| TABLE 110: RXLOS/CRC INTERRUPT ENABLE REGISTER (RLCIER)            | HEX ADDRESS: 0XNB13134                |

| TABLE 111: DATA LINK STATUS REGISTER 2 (DLSR2)                     | HEX ADDRESS: 0XNB16135                |

| TABLE 112: DATA LINK INTERRUPT ENABLE REGISTER 2 (DLIER2)          | HEX ADDRESS: 0XNB17 137               |

| TABLE 113: DATA LINK STATUS REGISTER 3 (DLSR3)                     | HEX ADDRESS: 0XNB26139                |

| TABLE 114: DATA LINK INTERRUPT ENABLE REGISTER 3 (DLIER3)          | HEX ADDRESS: 0XNB27 141               |

| TABLE 115: LIU CHANNEL CONTROL REGISTER 0 (LIUCCR0)                | HEX ADDRESS: 0x0Fn0 143               |

| TABLE 116: EQUALIZER CONTROL AND TRANSMIT LINE BUILD OUT           |                                       |

| TABLE 117: LIU CHANNEL CONTROL REGISTER 1 (LIUCCR1)                | HEX ADDRESS: 0x0Fn1146                |

| TABLE 118: LIU CHANNEL CONTROL REGISTER 2 (LIUCCR2)                | HEX ADDRESS: 0x0Fn2148                |

| TABLE 119: LIU CHANNEL CONTROL REGISTER 3 (LIUCCR3)                | HEX ADDRESS: 0x0Fn3                   |

| TABLE 120: LIU CHANNEL CONTROL INTERRUPT ENABLE REGISTER (LIUCCI   |                                       |

| TABLE 121: LIU CHANNEL CONTROL STATUS REGISTER (LIUCCSR)           | HEX ADDRESS: 0x0Fn5                   |

| TABLE 122: LIU CHANNEL CONTROL INTERRUPT STATUS REGISTER (LIUCCI   |                                       |

| TABLE 123: LIU CHANNEL CONTROL CABLE LOSS REGISTER (LIUCCCCR)      | HEX ADDRESS: 0x0Fn7                   |

| TABLE 124: LIU CHANNEL CONTROL ARBITRARY REGISTER 1 (LIUCCAR1)     | HEX ADDRESS: 0x0Fn8                   |

| TABLE 125: LIU CHANNEL CONTROL ARBITRARY REGISTER 2 (LIUCCAR2)     | HEX ADDRESS: 0X0FN9                   |

| TABLE 126: LIU CHANNEL CONTROL ARBITRARY REGISTER 3 (LIUCCAR3)     | HEX ADDRESS: 0X0FNA                   |

| TABLE 127: LIU CHANNEL CONTROL ARBITRARY REGISTER 4 (LIUCCAR4)     | HEX ADDRESS: 0x0FnB                   |

| TABLE 128: LIU CHANNEL CONTROL ARBITRARY REGISTER 5 (LIUCCAR5)     | HEX ADDRESS: 0X0FNC                   |

| : -: -: -: -: -: -: -: -: -: -: -: -:                              |                                       |

## **PRELIMINARY**

### XRT86VL32 REV. P1.0.5

### DUAL T1/E1/J1 FRAMER/LIU COMBO - E1 REGISTER DESCRIPTION

| TABLE 129: | LIU CHANNEL CONTROL ARBITRARY REGISTER 6 (LIUCCAR6) | HEX ADDRESS: 0x0FnD 16 | <i>30</i>  |

|------------|-----------------------------------------------------|------------------------|------------|

| TABLE 130: | LIU CHANNEL CONTROL ARBITRARY REGISTER 7 (LIUCCAR7) | HEX ADDRESS: 0x0FnE16  | <i>30</i>  |

| TABLE 131: | LIU CHANNEL CONTROL ARBITRARY REGISTER 8 (LIUCCAR8) | HEX ADDRESS: 0x0FnF 16 | <i>30</i>  |

| TABLE 132: | LIU GLOBAL CONTROL REGISTER 0 (LIUGCR0)             | HEX ADDRESS: 0x0FE0 16 | 31         |

| TABLE 133: | LIU GLOBAL CONTROL REGISTER 1 (LIUGCR1)             | HEX ADDRESS: 0x0FE1 16 | <i>5</i> 2 |

| TABLE 134: | LIU GLOBAL CONTROL REGISTER 2 (LIUGCR2)             | HEX ADDRESS: 0x0FE2 16 | 53         |

| TABLE 135: | LIU GLOBAL CONTROL REGISTER 3 (LIUGCR3)             | HEX ADDRESS: 0x0FE4 16 | <b>34</b>  |

| TABLE 136: | LIU GLOBAL CONTROL REGISTER 4 (LIUGCR4)             | HEX ADDRESS: 0x0FE9 16 | 35         |

| TABLE 137: | LIU GLOBAL CONTROL REGISTER 5 (LIUGCR5)             | HEX ADDRESS: 0x0FEA 16 | 36         |

### DESCRIPTION OF THE CONTROL REGISTERS - E1 MODE

All address on this register description is shown in HEX format, where n indicates channels 0 and 2 in the 2- channel device.

TABLE 1: REGISTER SUMMARY

| Function                                         | SYMBOL   | HEX             |

|--------------------------------------------------|----------|-----------------|

| Control Registers (0xn100 - 0xn1FF)              |          |                 |

| Clock and Select Register                        | CSR      | 0xn100          |

| Line Interface Control Register                  | LICR     | 0xn101          |

| Reserved                                         | -        | 0xn102 - 0xn106 |

| Framing Select Register                          | FSR      | 0xn107          |

| Alarm Generation Register                        | AGR      | 0xn108          |

| Synchronization MUX Register                     | SMR      | 0xn109          |

| Transmit Signaling and Data Link Select Register | TSDLSR   | 0xn10A          |

| Framing Control Register                         | FCR      | 0xn10B          |

| Receive Signaling & Data Link Select Register    | RSDLSR   | 0xn10C          |

| Receive Signaling Change Register 0              | RSCR0    | 0xn10D          |

| Receive Signaling Change Register 1              | RSCR1    | 0xn10E          |

| Receive Signaling Change Register 2              | RSCR2    | 0xn10F          |

| Receive Signaling Change Register 3              | RSCR3    | 0xn110          |

| Receive National Bits Register                   | RNBR     | 0xn111          |

| Receive Extra Bits Register                      | REBR     | 0xn112          |

| Data Link Control Register 1                     | DLCR1    | 0xn113          |

| Transmit Data Link Byte Count Register 1         | TDLBCR1  | 0xn114          |

| Receive Data Link Byte Count Register 1          | RDLBCR1  | 0xn115          |

| Slip Buffer Control Register                     | SBCR     | 0xn116          |

| FIFO Latency Register                            | FIFOLR   | 0xn117          |

| DMA 0 (Write) Configuration Register             | D0WCR    | 0xn118          |

| DMA 1 (Read) Configuration Register              | D1RCR    | 0xn119          |

| Interrupt Control Register                       | ICR      | 0xn11A          |

| LAPD Select Register                             | LAPDSR   | 0xn11B          |

| Reserved - T1 mode only                          | -        | 0xn11C          |

| Performance Report Control Register              | PRCR     | 0xn11D          |

| Gapped Clock Control Register                    | GCCR     | 0xn11E          |

| Transmit Interface Control Register              | TICR     | 0xn120          |

| PRBS Control & Status Register 0                 | PRBSCSR0 | 0xn121          |

TABLE 1: REGISTER SUMMARY

| Function                                      | SYMBOL    | HEX                |

|-----------------------------------------------|-----------|--------------------|

| Receive Interface Control Register            | RICR      | 0xn122             |

| PRBS Control & Status Register 1              | PRBSCSR1  | 0xn123             |

| For T1 mode only                              | -         | 0xn124 - 0xn127    |

| Defect Detection Enable Register              | DDER      | 0xn129             |

| Transmit Sa Select Register                   | TSASR     | 0xn130             |

| Transmit Sa Auto Control Register 1           | TSACR1    | 0xn131             |

| Transmit Sa Auto Control Register 2           | TSACR2    | 0xn132             |

| Transmit Sa4 Register                         | TSA4R     | 0xn133             |

| Transmit Sa5 Register                         | TSA5R     | 0xn134             |

| Transmit Sa6 Register                         | TSA6R     | 0xn135             |

| Transmit Sa7 Register                         | TSA7R     | 0xn136             |

| Transmit Sa8 Register                         | TSA8R     | 0xn137             |

| Receive Sa4 Register                          | RSA4R     | 0xn13B             |

| Receive Sa5 Register                          | RSA5R     | 0xn13C             |

| Receive Sa6 Register                          | RSA6R     | 0xn13D             |

| Receive Sa7 Register                          | RSA7R     | 0xn13E             |

| Receive Sa8 Register                          | RSA8R     | 0xn13F             |

| Reserved - T1 mode only                       | -         | 0xn142             |

| Data Link Control Register 2                  | DLCR2     | 0xn143             |

| Transmit Data Link Byte Count Register 2      | TDLBCR2   | 0xn144             |

| Receive Data Link Byte Count Register 2       | RDLBCR2   | 0xn145             |

| Data Link Control Register 3                  | DLCR3     | 0xn153             |

| Transmit Data Link Byte Count Register 3      | TDLBCR3   | 0xn154             |

| Receive Data Link Byte Count Register 3       | RDLBCR3   | 0xn155             |

| Device ID Register                            | DEVID     | 0xn1FE             |

| Revision Number Register                      | REVID     | 0xn1FF             |

| Time Slot (payload) Control (0xn300 - 0xn3FF) |           |                    |

| Transmit Channel Control Register 0-31        | TCCR 0-31 | 0xn300 -<br>0xn31F |

| User Code Register 0-31                       | TUCR 0-31 | 0xn320 -<br>0xn33F |

| Transmit Signaling Control Register 0 -31     | TSCR 0-31 | 0xn340 -<br>0xn35F |

#### TABLE 1: REGISTER SUMMARY

| Function                                                                     | SYMBOL    | HEX                |

|------------------------------------------------------------------------------|-----------|--------------------|

| Receive Channel Control Register 0-31                                        | RCCR 0-31 | 0xn360 -<br>0xn37F |

| Receive User Code Register 0-31                                              | RUCR 0-31 | 0xn380 -<br>0xn39F |

| Receive Signaling Control Register 0-31                                      | RSCR 0-31 | 0xn3A0 -<br>0xn3BF |

| Receive Substitution Signaling Register 0-31                                 | RSSR 0-31 | 0xn3C0 -<br>0xn3DF |

| Receive Signaling Array (0xn500 - 0xn51F)                                    | 1         |                    |

| Receive Signaling Array Register 0                                           | RSAR0-31  | 0xn500 -<br>0xn51F |

| LAPDn Buffer 0                                                               |           |                    |

| LAPD Buffer 0 Control Register                                               | LAPDBCR0  | 0xn600 -<br>0xn660 |

| LAPDn Buffer 1                                                               |           |                    |

| LAPD Buffer 1 Control Register                                               | LAPDBCR1  | 0xn700 -<br>0xn760 |

| Performance Monitor                                                          | 1         | 1                  |

| Receive Line Code Violation Counter: MSB                                     | RLCVCU    | 0xn900             |

| Receive Line Code Violation Counter: LSB                                     | RLCVCL    | 0xn901             |

| Receive Frame Alignment Error Counter: MSB                                   | RFAECU    | 0xn902             |

| Receive Frame Alignment Error Counter: LSB                                   | RFAECL    | 0xn903             |

| Receive Severely Errored Frame Counter                                       | RSEFC     | 0xn904             |

| Receive Synchronization Bit (CRC-6 (T1) CRC-4 (E1) Block) Error Counter: MSB | RSBBECU   | 0xn905             |

| Receive Synchronization Bit (CRC-6 (T1) CRC-4 (E1) Block) Error Counter: LSB | RSBBECL   | 0xn906             |

| Receive Far-End Block Error Counter: MSB                                     | RFEBECU   | 0xn907             |

| Receive Far-End Block Error Counter: LSB                                     | RFEBECL   | 0xn908             |

| Receive Slip Counter                                                         | RSC       | 0xn909             |

| Receive Loss of Frame Counter                                                | RLFC      | 0xn90A             |

| Receive Change of Frame Alignment Counter                                    | RCFAC     | 0xn90B             |

| LAPD Frame Check Sequence Error counter 1                                    | LFCSEC1   | 0xn90C             |

| PRBS bit Error Counter: MSB                                                  | PBECU     | 0xn90D             |

| PRBS bit Error Counter: LSB                                                  | 0xn90E    |                    |

| Transmit Slip Counter                                                        | TSC       | 0xn90F             |

#### TABLE 1: REGISTER SUMMARY

| Function                                                        | SYMBOL          | HEX             |  |

|-----------------------------------------------------------------|-----------------|-----------------|--|

| Excessive Zero Violation Counter: MSB                           | EZVCU           | 0xn910          |  |

| Excessive Zero Violation Counter: LSB                           | EZVCL           | 0xn911          |  |

| LAPD Frame Check Sequence Error counter 2                       | LFCSEC2         | 0xn91C          |  |

| LAPD Frame Check Sequence Error counter 3                       | LFCSEC3         | 0xn92C          |  |

| Interrupt Generation/Enable Register Address Map (0xnB00 - 0xnB | 41)             |                 |  |

| Block Interrupt Status Register                                 | BISR            | 0xnB00          |  |

| Block Interrupt Enable Register                                 | BIER            | 0xnB01          |  |

| Alarm & Error Interrupt Status Register                         | AEISR           | 0xnB02          |  |

| Alarm & Error Interrupt Enable Register                         | AEIER           | 0xnB03          |  |

| Framer Interrupt Status Register                                | FISR            | 0xnB04          |  |

| Framer Interrupt Enable Register                                | FIER            | 0xnB05          |  |

| Data Link Status Register 1                                     | DLSR1           | 0xnB06          |  |

| Data Link Interrupt Enable Register 1                           | DLIER1          | 0xnB07          |  |

| Slip Buffer Interrupt Status Register                           | SBISR           | 0xnB08          |  |

| Slip Buffer Interrupt Enable Register                           | SBIER           | 0xnB09          |  |

| Receive Loopback code Interrupt and Status Register             | RLCISR          | 0xnB0A          |  |

| Receive Loopback code Interrupt Enable Register                 | RLCIER          | 0xnB0B          |  |

| Receive SA (Sa6) Interrupt Status Register                      | RSAISR          | 0xnB0C          |  |

| Receive SA (Sa6) Interrupt Enable Register                      | RSAIER          | 0xnB0D          |  |

| Excessive Zero Status Register                                  | EXZSR           | 0xnB0E          |  |

| Excessive Zero Enable Register                                  | EXZER           | 0xnB0F          |  |

| Reserved - T1 mode only                                         | -               | 0xnB10 - 0xnB11 |  |

| RxLOS/CRC Interrupt Status Register                             | RLCISR          | 0xnB12          |  |

| RxLOS/CRC Interrupt Enable Register                             | RLCIER          | 0xnB13          |  |

| Data Link Status Register 2                                     | DLSR2           | 0xnB16          |  |

| Data Link Interrupt Enable Register 2                           | DLIER2          | 0xnB17          |  |

| Reserved - T1 mode only                                         | -               | 0xnB18 - 0xnB19 |  |

| Data Link Status Register 3                                     | DLSR3           | 0xnB26          |  |

| Data Link Interrupt Enable Register 3                           | DLIER3          | 0xnB27          |  |

| Reserved - T1 mode only                                         | 0xnB28 - 0xnB29 |                 |  |

| Reserved - T1 mode only                                         | CIAIER          | 0xnB40 - 0xnB41 |  |

| LIU Register Summary - Channel Control Registers                |                 |                 |  |

| LIU Channel Control Register 0                                  | LIUCCR0         | 0x0Fn0          |  |

#### TABLE 1: REGISTER SUMMARY

| Function                                        | SYMBOL   | HEX                |

|-------------------------------------------------|----------|--------------------|

| LIU Channel Control Register 1                  | LIUCCR1  | 0x0Fn1             |

| LIU Channel Control Register 2                  | LIUCCR2  | 0x0Fn2             |

| LIU Channel Control Register 3                  | LIUCCR3  | 0x0Fn3             |

| LIU Channel Control Interrupt Enable Register   | LIUCCIER | 0x0Fn4             |

| LIU Channel Control Status Register             | LIUCCSR  | 0x0Fn5             |

| LIU Channel Control Interrupt Status Register   | LIUCCISR | 0x0Fn6             |

| LIU Channel Control Cable Loss Register         | LIUCCCCR | 0x0Fn7             |

| LIU Channel Control Arbitrary Register 1        | LIUCCAR1 | 0x0Fn8             |

| LIU Channel Control Arbitrary Register 2        | LIUCCAR2 | 0x0Fn9             |

| LIU Channel Control Arbitrary Register 3        | LIUCCAR3 | 0x0FnA             |

| LIU Channel Control Arbitrary Register 4        | LIUCCAR4 | 0x0FnB             |

| LIU Channel Control Arbitrary Register 5        | LIUCCAR5 | 0x0FnC             |

| LIU Channel Control Arbitrary Register 6        | LIUCCAR6 | 0x0FnD             |

| LIU Channel Control Arbitrary Register 7        | LIUCCAR7 | 0x0FnE             |

| LIU Channel Control Arbitrary Register 8        | LIUCCAR8 | 0x0FnF             |

| Reserved                                        | -        | 0x0F80 -<br>0x0FDF |

| LIU Register Summary - Global Control Registers | •        |                    |

| LIU Global Control Register 0                   | LIUGCR0  | 0x0FE0             |

| LIU Global Control Register 1                   | LIUGCR1  | 0x0FE1             |

| LIU Global Control Register 2                   | LIUGCR2  | 0x0FE2             |

| LIU Global Control Register 3                   | LIUGCR3  | 0x0FE4             |

| LIU Global Control Register 4                   | LIUGCR4  | 0x0FE9             |

| LIU Global Control Register 5                   | LIUGCR5  | 0x0FEA             |

| Reserved                                        |          | 0x0FEB -<br>0x0FFF |

#### 1.0 REGISTER DESCRIPTIONS - E1 MODE

All address on this register description is shown in HEX format, where n indicates channels 0 and 2 in the 2-channel device.

TABLE 2: CLOCK SELECT REGISTER (CSR)

| Віт | Function                      | Түре | DEFAULT | DESCRIPTION-OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------------------------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | LCV Insert                    | R/W  | 0       | Line Code Violation Insertion This bit is used to force a Line Code Violation (LCV) on the transmit output of TTIP/TRING. A "0" to "1" transition on this bit will cause a single LCV to be inserted on the transmit output of TTIP/TRING.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6   | Set T1 Mode                   | R/W  | 0       | T1/E1 Mode select This bit is used to program the individual channel to operate in either T1 or E1 mode.  0 = Configures the selected channel to operate in E1 mode.  1 = Configures the selected channel to operate in T1 mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5   | Sync All Transmitters to 8kHz | R/W  | 0       | Sync All Transmit Framers to 8kHz  This bit permits the user to configure each of the two (2) Transmit E1 Framer blocks to synchronize their "transmit output" frame alignment with the 8kHz signal that is derived from the MCLK PLL, as described below.  0 - Disables the "Sync all Transmit Framers to 8kHz" feature for all 2 channels.  1 - Enables the "Sync all Transmit Framers to 8kHz" feature for all 2 channels.  Note: Writing to this bit in register 0x0100 will enable this feature for all 2 channels.  Note: This bit is only active if the MCLK PLL is used as the "Timing Source" for the Transmit E1 Framer" blocks. CSS[1:0] of this register allows users to select the transmit source of the framer. |

| 4   | Clock Loss Detect             | R/W  | 1       | Clock Loss Detect Enable/Disable Select  This bit enables a clock loss protection feature for the Framer whenever the recovered line clock is used as the timing source for the transmit section. If the LIU loses clock recovery, the Clock Distribution Block will detect this occurrence and automatically begin to use the internal clock derived from MCLK PLL as the Transmit source, until the LIU is able to regain clock recovery.  0 = Disables the clock loss protection feature.  1 = Enables the clock loss protection feature.  Note: This bit needs to be enabled in order to detect the clock loss detection interrupt status (address: 0xnB00, bit 5)                                                         |

| 3:2 | Reserved                      | R/W  | 00      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## TABLE 2: CLOCK SELECT REGISTER (CSR)

| Віт | Function | Түре | DEFAULT |                                                                                                                                                                                                                                                              | DESCRIPTION-OPERATION                                                                                                    |                       |  |

|-----|----------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| 1:0 | CSS[1:0] | R/W  | 01      | Clock Source Select These bits select the timing source for the Transmit E1 Framer block. These bits can also determine the direction of TxSERCLK, TxSYNC, and TxMSYNC in base rate operation mode (2.048MHz Clock mode) In Base Rate (2.048MHz Clock Mode): |                                                                                                                          |                       |  |

|     |          |      |         | CSS[1:0]                                                                                                                                                                                                                                                     | TRANSMIT SOURCE FOR THE TRANSMIT E1 FRAMER BLOCK                                                                         | DIRECTION OF TXSERCLK |  |

|     |          |      |         | 00/11                                                                                                                                                                                                                                                        | Loop Timing Mode The recovered line clock is chosen as the timing source.                                                | Output                |  |

|     |          |      |         | 01                                                                                                                                                                                                                                                           | External Timing Mode The Transmit Serial Input Clock from the TxSERCLK_n input pin is chosen as the timing source.       | Input                 |  |

|     |          |      |         | 10                                                                                                                                                                                                                                                           | Internal Timing Mode The MCLK PLL is chosen as the timing source.                                                        | Output                |  |

|     |          |      |         | depending or                                                                                                                                                                                                                                                 | (NC/TxMSYNC can be programmed and the setting of SYNC INV bit in Regis see Register Description for the Syndr - 0xn109). | ter Address 0xn109,   |  |

|     |          |      |         |                                                                                                                                                                                                                                                              | gh-Speed or multiplexed modes, TxS<br>NC are all configured as INPUTS only                                               |                       |  |

## REV. P1.0.5

## TABLE 3: LINE INTERFACE CONTROL REGISTER (LICR)

| Віт | Function  | Түре | DEFAULT | DESCRIPTION-OPERATION                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-----|-----------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7   | FORCE_LOS | R/W  | 0       | Force Transmit LOS (To the Line Side) This bit permits the user to configure the transmit direction circuitry (within the channel) to transmit the LOS pattern to the remote terminal equipment, as described below.  0 - Configures the transmit direction circuitry to transmit "normal" traffic.  1 - Configures the transmit direction circuitry to transmit the LOS Pattern. |  |  |

| 6   | Reserved  | R/W  | 0       | Please set to '0' for normal operation                                                                                                                                                                                                                                                                                                                                            |  |  |

| 5:4 | LB[1:0]   | R/W  | 00      | Framer Loopback Selection These bits are used to select any of the following loop-back modes for the framer section. For LIU loopback modes, see the LIU configuration registers.                                                                                                                                                                                                 |  |  |

|     |           |      |         | LB[1:0] TYPES OF LOOPBACK SELECTED                                                                                                                                                                                                                                                                                                                                                |  |  |

|     |           |      |         | 00 Normal Mode (No LoopBack)                                                                                                                                                                                                                                                                                                                                                      |  |  |

|     |           |      |         | O1 Framer Local LoopBack:  When framer local loopback is enabled, the transmit PCM input data is looped back to the receive PCM output data. The receive input data at RTIP/RRING is ignored while an All Ones Signal is transmitted out to the line interface.                                                                                                                   |  |  |

|     |           |      |         | 10 Framer Far-End (Remote) Line LoopBack: When framer remote loopback is enabled, the digital data enters the framer interface, however does not enter the framing blocks. The receive digital data from the LIU is allowed to pass through the LIU Decoder/ Encoder circuitry before returning to the line interface.                                                            |  |  |

|     |           |      |         | 11 Framer Payload LoopBack: When framer payload loopback is enabled, the raw data within the receive time slots are looped back to the transmit framer block where the data is re-framed according to the transmit timing.                                                                                                                                                        |  |  |

| 3   | TCI       | R/W  | 0       | Transmit Clock Inversion This bit inverts the transmit clock input to the LIU.  0 = Configures the device to transmit data at the positive edge of the transmit clock  1 = Configures the device to transmit data at the negative edge of the transmit clock                                                                                                                      |  |  |

| 2   | RCI       | R/W  | 0       | Receive Clock Inversion This bit inverts the receive clock output from the LIU.  0 = Configures the device to receive data at the positive edge of the receive clock  1 = Configures the device to receive data at the negative edge of the receive clock                                                                                                                         |  |  |

## TABLE 3: LINE INTERFACE CONTROL REGISTER (LICR)

| Віт | Function        | ТҮРЕ | DEFAULT | DESCRIPTION-OPERATION                                                                                                                                                                                                                            |

|-----|-----------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Encode B8ZS     | R/W  | 0       | Encode AMI or B8ZS/HDB3 Line Code Select This bit enables or disables the B8ZS/HDB3 encoder on the transmit path.  0 = Enables the B8ZS encoder.  1 = Disables the B8ZS encoder.  Note: When B8ZS encoder is disabled, AMI line code is used.    |

| 0   | Decode AMI/B8ZS | R/W  | 0       | Decode AMI or B8ZS/HDB3 Line Code Select This bit enables or disables the B8ZS/HDB3 decoder on the receive path.  0 = Enables the B8ZS decoder.  1 = Disables the B8ZS decoder.  Note: When B8ZS decoder is disabled, AMI line code is received. |

## DUAL T1/E1/J1 FRAMER/LIU COMBO - E1 REGISTER DESCRIPTION

XRT86VL32

HEX ADDRESS: 0xn107

BEVL:

## TABLE 4: FRAMING SELECT REGISTER (FSR)

| Віт | FUNCTION                                       | Түре | DEFAULT | DESCRIPTION-OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------------------------------------------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | G.706 Annex B<br>CRC-4 Calcula-<br>tion Enable | R/W  | 0       | G.706 Annex B CRC-4 Calculation Enable This bit configures the E1 Receive Framer Block to be compliant with ITU-T G.706 Annex B for CRC-to-non-CRC interworking detection. If Annex B is enabled, G.706 Annex B CRC-4 multiframe alignment algorithm is implemented. If CRC-4 alignment is enabled and not achieved in 400msec while the basic frame alignment signal is present, it is assumed that the remote end is a non CRC-4 equipment. A CRC-to-Non-CRC interworking interrupt will be generated. The CRC-to-Non-CRC interworking interrupt Status can be read from Register Address 0xnB0A.  0 - Configures the Receive E1 Framer block to NOT support the "G.706 Annex B" CRC-4 Multiframe Alignment algorithm.  1 - Configures the Receive E1 Framer block to support the "G.706 Annex B" CRC-4 Multiframe Alignment algorithm. |

| 6   | Transmit CRC-4<br>Error                        | R/W  | 0       | Transmit CRC-4 Error This bit is used to force a continuous errored CRC pattern in the outbound CRC multiframe to be sent on the transmission line. The Transmit E1 Framer Block will implement this error by inverting the value of CRC bit (C1).  0 = Disables the Transmit E1 Framer Block to transmit errored CRC bit.  1 = Forces the Transmit E1 Framer Block to transmit continuous errored CRC bit.  Note: This bit is ignored if CRC multi-Framing is disabled.                                                                                                                                                                                                                                                                                                                                                                  |

### TABLE 4: FRAMING SELECT REGISTER (FSR)

| Віт | Function                 | Түре | DEFAULT |                             | DESCRIPTION-OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|--------------------------|------|---------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-4 | CAS MF Align<br>Sel[1:0] | R/W  | 00      | These bits allow            | ne Alignment Declaration Algorithm Select[1:0]  w the user to select which CAS Multiframe Alignment Declanate the Receive E1 Framer block will employ, according to the                                                                                                                                                                                                                                                                                                                                                      |

|     |                          |      |         | CAS MF<br>ALIGN<br>SEL[1:0] | CAS MULTIFRAME ALIGNMENT DECLARATION ALGORITHM SELECTED                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |                          |      |         | 00/11                       | CAS Multiframe Alignment is Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |                          |      |         | 01                          | The "16-Frame" Algorithm  If this alignment algorithm is selected, then the Receive E1 Framer block will monitor the 16th timeslot of each incoming E1 frame and will declare CAS Multiframe alignment (e.g., clear the Loss of CAS Multiframe" defect) condition; anytime that it detects 15 consecutive E1 frames in which bits 1 - 4 (of timeslot 16) do not contain the "CAS Multiframe Alignment" pattern; which is immediately followed by an E1 frame that DOES contain the "CAS Multiframe Alignment" pattern.       |

|     |                          |      |         | 10                          | The "2-Frame" (ITU-T G.732) Algorithm  If this alignment algorithm is selected, then the Receive E1 Framer block will monitor the 16th timeslot of each incoming E1 frame and will declare CAS Multiframe alignment (e.g., clear the Loss of CAS Multiframe" defect) condition; anytime that it detects a single E1 frame in which bits 1 - 4 (of timeslot 16) do not contain the "CAS Multiframe Alignment" pattern; which is immediately followed by an E1 frame that DOES contain the "CAS Multiframe Alignment" pattern. |

|     |                          |      |         | uses in order to            | rmation on the criteria that the Receive E1 Framer block of declare the "Loss of CAS Multiframe" defect condition, ister description for the Framing Control Register (FCR - B)                                                                                                                                                                                                                                                                                                                                              |

## TABLE 4: FRAMING SELECT REGISTER (FSR)

| Віт | Function                                  | Түре | DEFAULT | DESCRIPTION-OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-----|-------------------------------------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 3-2 | CRC MF Align<br>Sel[1:0]                  | R/W  | 00      | CRC Multiframe Alignment Declaration Criteria Select [1:0] These two bits allow the user to select which CRC-Multiframe Alignment Declaration criteria the Receive E1 Framer block will employ. The Receive E1 Framer block will check for CRC Multiframe Alignment by checking the incoming E1 data-stream and determining whether the international bits (bit 1 of timeslot 0) of non-FAS frames match the CRC multiframe alignment pattern (0,0,1,0,1,1,E1,E2). The table below provides more details on the three different CRC Multiframe Alignment Declaration Criteria. |                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|     |                                           |      |         | CRC MF<br>ALIGN SEL<br>[1:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CRC MULTIFRAME ALIGNMENT DECLARATION CRITERIA SELECTED                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|     |                                           |      |         | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CRC Multiframe Alignment is Disabled                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|     |                                           |      |         | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CRC Multiframe Alignment is Enabled. Alignment is declared if at least 1 valid CRC multiframe alignment signal (0,0,1,0,1,1,E1,E2) is observed within 8ms.                                                                                                                                                                                                                                                  |  |  |  |

|     |                                           |      |         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CRC Multiframe Alignment is Enabled. Alignment is declared if at least 2 valid CRC multiframe alignment signals (0,0,1,0,1,1,E1,E2) are observed within 8ms.                                                                                                                                                                                                                                                |  |  |  |

|     |                                           |      |         | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CRC Multiframe Alignment is Enabled. Alignment is declared if at least 3 valid CRC multiframe alignment signals (0,0,1,0,1,1,E1,E2) are observed within 8ms.                                                                                                                                                                                                                                                |  |  |  |

|     |                                           |      |         | uses to declare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | mation on the criteria that the Receive E1 Framer block<br>the "Loss of CRC Multiframe Alignment" defect condition,<br>ter description for the Framing Control Register (FCR -                                                                                                                                                                                                                              |  |  |  |

| 1   | Additional Frame<br>Check Enable -<br>FAS | R/W  | 0       | This bit permits t<br>form some "addi<br>ing "FAS Frame<br>Receive E1 Fran<br>E1 frames, prior<br>0 - Disables this                                                                                                                                                                                                                                                                                                                                                                                                                                                            | he Check Enable - FAS Frame Alignment Declaration he user to configure the Receive E1 Framer block to per- tional FAS frame synchronization checking" prior to declar- Alignment". If the user implements this feature, then the ner block will perform some more testing on two additional to declaring the "FAS Frame Alignment" condition. additional FAS frame checking. additional FAS frame checking. |  |  |  |

### TABLE 4: FRAMING SELECT REGISTER (FSR)

| Віт | Function        | Түре  | DEFAULT | DESCRIPTION-OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-----------------|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | FAS Frame Align | R/W   | 0       | FAS Alignment Declaration Algorithm Select                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| O   | Sel             | 17/44 |         | This bit specifies which algorithm the Receive E1 Framer block uses in its search for the FAS Alignment.                                                                                                                                                                                                                                                                                                                                                                         |

|     |                 |       |         | 0 = Selects the FAS Alignment Algorithm 1                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                 |       |         | 1 = Selects the FAS Alignment Algorithm 2                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                 |       |         | FAS Alignment Algorithm 1                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                 |       |         | If the Receive E1 Framer block has been configured to use "FAS Alignment Algorithm # 1", then it will acquire FAS alignment by performing the following three steps:                                                                                                                                                                                                                                                                                                             |

|     |                 |       |         | <b>Step 1</b> - The Receive E1 Framer block begins by searching for the correct 7-bit FAS pattern. Go to Step 2 if found.                                                                                                                                                                                                                                                                                                                                                        |

|     |                 |       |         | <b>Step 2</b> - Check if the FAS is absent in the following frame by verifying that bit 2 of the assumed timeslot 0 of the Non-FAS frame is a one. Go back to Step 1 if failed, otherwise, go to step 3.                                                                                                                                                                                                                                                                         |

|     |                 |       |         | <b>Step 3</b> - Check if the FAS is present in the assumed timeslot 0 of the third frame. Go back to Step 1 if failed.                                                                                                                                                                                                                                                                                                                                                           |

|     |                 |       |         | After the first three steps (if they all passed), the Receive E1 Framer Block will declare FAS in SYNC if Frame Check Sequence (Bit 1 of this register) is disabled. If Frame Check Sequence (Bit 1 of this register) is enabled, then the Receive E1 Framer Block will need to verify the correct frame alignment for an additional two frames.                                                                                                                                 |