## Hysteretic Boost-Buck (Ćuk) LED Driver IC

#### **Features**

- Constant current LED Driver

- Steps input voltage Up or Down

- ► Low EMI

- Variable frequency operation

- Internal 8 to 100V linear regulator

- Input and output current sensing

- Input current limit

- Enable & PWM dimming

- ► Ambient temperature rating up to 125°C

- ► Meets AEC-Q100 requirements

## **Applications**

Automotive LED Lighting

#### **Reference Documents**

- ► AEC-Q100 Rev. F, 7/18/2003

- ► SAE J1752-3

## **General Description**

The AT9933 is a variable frequency PWM controller IC, designed to control an LED lamp driver using a low-noise boost-buck (Ćuk) topology. The AT9933 uses patent-pending hysteretic current-mode control to regulate both the input and the output currents. This enables superior input surge immunity without the necessity for complex loop compensation. Input current control enables current limiting during startup, input under-voltage and output overload conditions. The AT9933 provides a low-frequency PWM dimming input that can accept an external control signal with a duty cycle of 0 - 100% and a high dimming ratio.

The AT9933 based LED driver is ideal for automotive LED lamps. The part is rated for up to 125°C ambient temperatures and is AEC-Q100-Compliant.

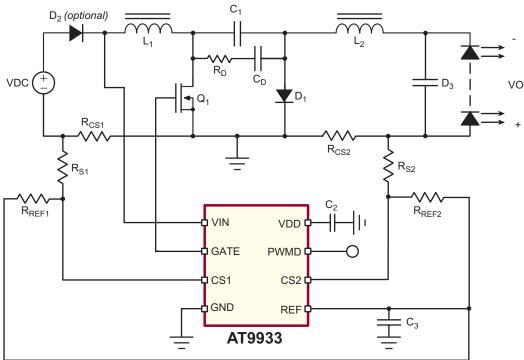

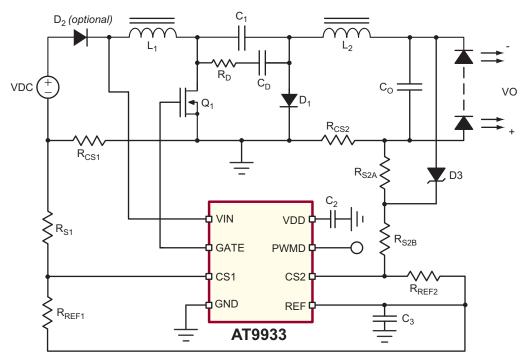

## **Typical Application Circuit**

## **Ordering Information**

| DEVICE | Package Option |  |  |  |  |

|--------|----------------|--|--|--|--|

| DEVICE | 8-Lead SOIC    |  |  |  |  |

| AT9933 | AT9933LG-G     |  |  |  |  |

## **Absolute Maximum Ratings**

| Parameter                                                                 | Value                             |  |  |  |  |  |  |

|---------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|--|

| V <sub>IN</sub> to GND                                                    | -0.5V to +100V                    |  |  |  |  |  |  |

| CS1, CS2                                                                  | -0.3V to (V <sub>DD</sub> + 0.3V) |  |  |  |  |  |  |

| PWMD to GND                                                               | -0.3V to (V <sub>DD</sub> + 0.3V) |  |  |  |  |  |  |

| GATE to GND                                                               | -0.3V to (V <sub>DD</sub> + 0.3V) |  |  |  |  |  |  |

| $V_{\text{DDMAX}}$                                                        | 12V                               |  |  |  |  |  |  |

| Continuous Power Dissipation (TA = +25°C)                                 |                                   |  |  |  |  |  |  |

| 8-Pin SOIC                                                                | 700mW                             |  |  |  |  |  |  |

| Junction to ambient thermal impedance (typical); using standard footprint | 128°C/W                           |  |  |  |  |  |  |

| Junction temperature                                                      | +150°C                            |  |  |  |  |  |  |

| Storage temperature range                                                 | -65°C to +150°C                   |  |  |  |  |  |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

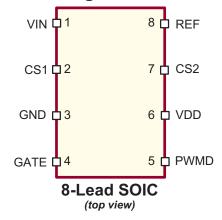

## **Pin Configuration**

### **Electrical Characteristics**

$V_{\scriptscriptstyle DD}$  undervoltage lockout

V<sub>DD</sub> undervoltage lockout

threshold

hysteresis

**UVLO**

$\Delta UVLO$

(The \* denotes the specifications which apply over the full operating ambient temperature range of -40°C <  $T_A$  < +125°C, otherwise the specifications are at  $T_A$  = 25°C.  $V_{IM}$  = 12V, unless otherwise noted)

| A = 0 · · · · · · · · · · · · · · · · · · |                                            |   |     |     |     |       |                                                                                     |

|-------------------------------------------|--------------------------------------------|---|-----|-----|-----|-------|-------------------------------------------------------------------------------------|

| Symbol                                    | Parameter                                  |   | Min | Тур | Max | Units | Conditions                                                                          |

| Input                                     |                                            |   |     |     |     |       |                                                                                     |

| V <sub>INDC</sub>                         | Input DC supply voltage range <sup>1</sup> | * | (2) | -   | 100 | V     | DC input voltage                                                                    |

| I <sub>INSD</sub>                         | Shut-down mode supply current <sup>1</sup> | - | -   | 0.5 | 1.0 | mA    | PWMD connected to GND,<br>$V_{IN} = 12V$                                            |

| Internal Regulator                        |                                            |   |     |     |     |       |                                                                                     |

| V <sub>DD</sub>                           | Internally regulated voltage               | * | 7.0 | 7.5 | 9.0 | V     | $V_{IN} = 8 - 100V$ , $I_{DD(ext)} = 0$ ,<br>500pF capacitor at GATE,<br>PWMD = GND |

6.70

500

6.95

٧

mV

V<sub>IN</sub> rising

6.45

<sup>-</sup>G indicates package is RoHS compliant ('Green')

| Symbol                | Description                                        |   | Min   | Тур  | Max        | Units | Conditions                                                                                             |

|-----------------------|----------------------------------------------------|---|-------|------|------------|-------|--------------------------------------------------------------------------------------------------------|

| Reference             |                                                    |   |       |      |            |       |                                                                                                        |

| V                     | REF pin voltage<br>-40°C < T <sub>A</sub> < +85°C  | - | 1.212 | 1.25 | 1.288      | V     | REF bypassed with a 0.1µF                                                                              |

| $V_{REF}$             | REF pin voltage<br>-40°C < T <sub>A</sub> < +125°C |   | 1.187 | 1.25 | 1.25 1.312 | V     | capacitor to GND, I <sub>REF</sub> = 0,<br>PWMD = 5.0V                                                 |

| $V_{REFLINE}$         | Line regulation of reference voltage               |   | 0     | -    | 20         | mV    | REF bypassed with a $0.1\mu$ F capacitor to GND, $I_{REF} = 0$ , $V_{DD} = 7.0 - 9.0V$ , PWMD = $5.0V$ |

| I <sub>REF</sub>      | Reference output current range                     |   | -0.01 |      | 500        | μA    | REF bypassed with a $0.1\mu$ F capacitor to GND, $I_{REF} = 0$ ; $V_{DD} = 7.0 - 9.0V$ , PWMD = $5.0V$ |

| $V_{REFLOAD}$         | Load regulation of reference voltage               |   | 0     | -    | 10         | mV    | REF bypassed with a 0.1μF capacitor to GND, I <sub>REF</sub> = 0 - 500μA PWMD = 5.0V                   |

| PWM Din               | nming                                              |   |       |      |            |       |                                                                                                        |

|                       | PWMD input low voltage                             | * | -     | -    | 0.8        | V     | $V_{DD} = 7.0V - 9.0V$                                                                                 |

| $V_{\text{PWMD(hi)}}$ | PWMD input high voltage                            |   | 2.0   | -    | -          | V     | $V_{DD} = 7.0V - 9.0V$                                                                                 |

| R <sub>PWMD</sub>     | PWMD pull-down resistance                          |   | 50    | 100  | 150        | kΩ    | V <sub>PWMD</sub> = 5.0V                                                                               |

| I <sub>PWMD</sub>     | Maximum current into PWMD pin                      |   | -     | -    | 5          | mA    |                                                                                                        |

| GATE                  |                                                    | • |       |      |            |       |                                                                                                        |

| SOURCE                | GATE short circuit current                         |   | 0.165 | -    |            | Α     | V <sub>GATE</sub> = 0V                                                                                 |

| ISINK                 | GATE sinking current                               |   | 0.165 | -    | -          | Α     | $V_{GATE} = V_{DD}$                                                                                    |

| T <sub>RISE</sub>     | GATE output rise time                              | - | -     | 30   | 50         | ns    | C <sub>GATE</sub> = 500pF                                                                              |

| T <sub>FALL</sub>     | GATE output fall time                              |   | -     | 30   | 50         | ns    | $C_{GATE} = 500pF$                                                                                     |

|                       | rent Sense Comparator                              |   |       |      | L          |       | GATE                                                                                                   |

| V <sub>TURNON1</sub>  | Voltage required to turn GATE on                   | * | 85    | 100  | 115        | mV    | CS2 = 200mV; CS1 increasing;<br>GATE goes LOW to HIGH                                                  |

| V <sub>TURNOFF1</sub> | Voltage required to turn GATE off                  | * | -15   | 0    | 15         | mV    | CS2 = 200mV; CS1 decreasing;<br>GATE goes HIGH to LOW                                                  |

| $T_{D1,ON}$           | Delay to output (turn on)                          | - | -     | 150  | 250        | ns    | CS2 = 200mV;<br>CS1 = 50mV to +200mV step                                                              |

| $T_{D1,OFF}$          | Delay to output (turn off)                         |   | -     | 150  | 250        | ns    | CS2 = 200mV;<br>CS1 = 50mV to -100mV step                                                              |

| Output C              | urrent Sense Comparator                            |   |       |      |            |       |                                                                                                        |

| V <sub>TURNON2</sub>  | Voltage required to turn GATE on                   |   | 85    | 100  | 115        | mV    | CS1 = 200mV; CS2 increasing;<br>GATE goes LOW to HIGH                                                  |

| V <sub>TURNOFF2</sub> | Voltage required to turn GATE off                  |   | -15   | 0    | 15         | mV    | CS1 = 200mV; CS2 decreasing;<br>GATE goes HIGH to LOW                                                  |

| $T_{D2,ON}$           | Delay to output (turn on)                          |   | -     | 150  | 250        | ns    | CS1 = 200mV;<br>CS2 = 50mV to +200mV step                                                              |

| $T_{D2,OFF}$          | Delay to output (turn off)                         |   | -     | 150  | 250        | ns    | CS1 = 200mV;<br>CS2 = 50mV to -100mV step                                                              |

<sup>2</sup> Depends on the current drawn by the part - see application section.

## **Pin Description**

| Pin Number | Pin  | Description                                                                                                                                               |  |  |  |  |

|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1          | VIN  | This pin is the input of a 8 - 100V voltage regulator.                                                                                                    |  |  |  |  |

| 2          | CS1  | These pins are used to sense the input and output currents of the boost-buck converter.                                                                   |  |  |  |  |

| 7          | CS2  | They are the non-inverting inputs of the internal comparators.                                                                                            |  |  |  |  |

| 3          | GND  | Ground return for all the internal circuitry. This pin must be electrically connected to the ground of the power train.                                   |  |  |  |  |

| 4          | GATE | This pin is the output gate driver for an external N-channel power MOSFET.                                                                                |  |  |  |  |

| 5          | PWMD | When this pin is left open or pulled to GND, the gate driver is disabled. Pulling the pin to a voltage greater than 2V will enable the gate drive output. |  |  |  |  |

| 6          | VDD  | This is a power supply pin for all internal circuits. It must be bypassed to GND with a low ESR capacitor greater than $0.1\mu F$ .                       |  |  |  |  |

| 8          | REF  | This pin provides accurate reference voltage. It must be bypassed with a 0.01 - 0.1 $\mu$ F capacitor to GND.                                             |  |  |  |  |

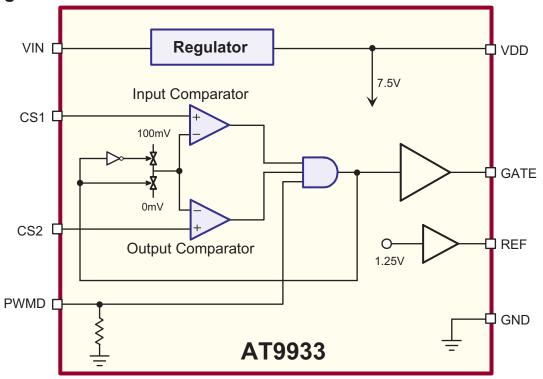

## **Block Diagram**

### **Functional Description**

#### **Power Topology**

The AT9933 is optimized to drive a continuous conduction mode (CCM) boost-buck DC/DC converter topology commonly referred to as "Ćuk converter" (see Circuit Diagram on page 1). This power converter topology offers numerous advantages useful for driving high-brightness light emitting diodes (HB LED). These advantages include step-up or step-down voltage conversion ratio and low input and output current ripple. The output load is decoupled from the input voltage with a capacitor making the driver inherently failure-safe for the output load.

The AT9933 offers a simple and effective control technique for use with a boost-buck LED driver. It uses two hysteretic mode controllers – one for the input and one for the output. The outputs of these two hysteretic comparators are AND-ED and used to drive the external FET. This control scheme gives accurate current control and constant output current in the presence of input voltage transients without the need for complicated loop design.

#### **Input Voltage Regulator**

The AT9933 can be powered directly from its VIN pin that takes a voltage from 8V to 100V. When a voltage is applied at the VIN pin, the AT9933 seeks to regulate a constant 7.5V (typ) at the VDD pin. The regulator also has a built in undervoltage lockout which shuts off the IC if the voltage at the VDD pin falls below the UVLO threshold.

The VDD pin must be bypassed by a low ESR capacitor (≥0.1µF) to provide a low impedance path for the high frequency current of the output gate driver.

The input current drawn from the VIN pin is a sum of the 1mA current drawn by the internal circuit and the current drawn by the gate driver (which in turn depends on the switching frequency and the gate charge of the external FET).

$$I_{IN} = 1mA + Q_G \cdot f_S \tag{1}$$

In the above equation,  $f_s$  is the switching frequency and  $Q_g$  is the gate charge of the external FET (which can be obtained from the datasheet of the FET).

#### Minimum Input Voltage at VIN pin

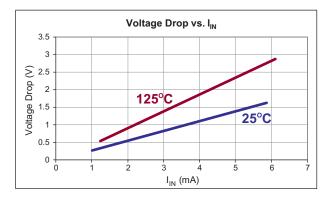

The minimum input voltage at which the converter will start and stop depends on the minimum voltage drop required for the linear regulator. The internal linear regulator will regulate the voltage at the VDD pin when  $\rm V_{IN}$  is between 8 and 100V. However, when  $\rm V_{IN}$  is less than 8V, the converter will still function as long as  $\rm V_{DD}$  is greater than the under voltage lockout. Thus, under certain conditions, the converter will be able to start at  $\rm V_{IN}$  voltages of less than 8V. The start/stop

voltages at the VIN pin can be determined using the maximum voltage drop across the linear regulator as a function of the current drawn. This data is shown in Fig. 1 for ambient temperatures of 25°C and 125°C.

Fig. 1. Maximum Voltage Drop vs. Input Current

Assume an ambient temperature of 125°C. Assuming the IC is driving a 15nC gate charge FET at 300kHz, the total input current is estimated to be 5.5mA (using Eqn. 1). At this input current, the maximum voltage drop from Fig. 1 can be approximately estimated to be  $\rm V_{\rm DROP}=2.7V.$  However, before the IC starts switching the current drawn will be 1mA. At this current level, the voltage drop is approximately  $\rm V_{\rm DROP1}=0.5V.$  Thus, the start/stop  $\rm V_{\rm IN}$  voltages can be computed to be:

$$VIN_{START} = UVLO_{MAX} + V_{DROP1}$$

= 6.95V + 0.5V

= 7.45V

$VIN_{STOP} = UVLO_{MAX} - \Delta UVLO + V_{DROP}$

= 6.95 - 0.5V + 2.7V

= 9.15V

Note that in this case, since the gate drive draws too much current,  $VIN_{START}$  is less than  $VIN_{STOP}$ . In such cases, the control IC will oscillate between ON and OFF if the input voltage is between the start and stop voltages. In these circumstances, it is recommended that the input voltage be kept higher than  $VIN_{STOP}$  (in this case the IC will operate normally if the input voltage is kept higher than 9.2V).

In case of input transients that reduce the input voltage below 8V (like cold crank condition in an automotive system), the VIN pin of the AT9933 can be connected to the drain of the MOSFET through a switching diode with a small (1nF) capacitor between VIN and GND (as long as the drain voltage does not exceed 100V). Since the drain of the FET is at a voltage equal to the sum of the input and output voltages, the IC will still be operational when the input goes below 8V. In these cases, a larger capacitor is needed to the VDD pin to supply power to the IC when the MOSFET is ON.

In this case  $V_{\text{DD UVLO}}$  cannot be relied upon to turn off the IC at low input voltages when input current levels can get too large. The input current limit must then be designed to limit the input current to safe levels during input undervoltage conditions.

#### Reference

An internally trimmed voltage reference of 1.25V is provided at the REF pin. The reference can supply a maximum output current of  $500\mu A$  to drive external resistor dividers.

This reference can be used to set the current thresholds of the two comparators as shown in the Typical Application Circuit.

#### **Current Comparators**

The AT9933 features two identical comparators with a builtin 100mV hysteresis. When the GATE is low, the inverting terminal is connected to 100mV and when the GATE is high, it is connected to GND. One comparator is used for the input current control and the other for the output current control.

The input side hysteretic controller is in operation during start-up, overload and input undervoltage conditions. This ensures that the input current never exceeds the designed value. During normal operation, the input current will be less than the programmed current and hence, the output of the input side comparator will be HIGH. The output of the AND gate will then be dictated by the output current controller.

The output side hysteretic comparator will be in operation during the steady state operation of the circuit. This comparator turns the MOSFET on and off based on the LED current.

#### **PWM Dimming**

PWM Dimming can be achieved by applying a TTL-compatible square wave signal at the PWM pin. When the PWMD pin is pulled high, the gate driver is enabled and the circuit operates normally. When the PWMD pin is left open or connected to GND, the gate driver is disabled and the external MOSFET turns off. The IC is designed so that the signal at the PWMD pin inhibits the driver only and the IC need not go through the entire start-up cycle each time ensuring a quick response time for the output current. The recommended

PWM Dimming frequency range is from 100Hz to a few kilo hertz.

The flying capacitor in the Ćuk converter (C1) is initially charged to the input Voltage VDC (through diodes D1 and D2). When the circuit is turned on and reaches steady state, the voltage across C1 will be VDC+VO. In the absence of diode D2, when the circuit is turned off, capacitor C1 will discharge through the LEDs and the input voltage source VDC. Thus, during PWM dimming, if capacitor C1 has to be charged and discharged each cycle, the transient response of the circuit will be limited. By adding diode D2, the voltage across capacitor C1 is held at VDC+VO even when the circuit is turned off enabling the circuit to return quickly to its steady state (and bypassing the start-up stage) upon being enabled.

## **Application Information**

#### **Over-voltage Protection**

Over-voltage protection can be added by splitting the output side resistor  $\rm R_{\rm S2}$  into two components and adding a zener diode D3 (see the Design Example Circuit on the following page). When there is an open LED condition, the diode D3 will clamp the output voltage and the zener diode current will be regulated by the sum of  $\rm R_{\rm S2A}$  and  $\rm R_{\rm CS2}$ .

#### **Damping Circuit**

The Cuk converter is inherently unstable when the output current is being controlled. An uncontrolled input current will lead to an un-damped oscillation between L1 and C1 causing excessively high voltages across C1. To prevent these oscillations, a damping circuit consisting of RD and CD is applied across the capacitor C1. This damping circuit will stabilize the circuit and help in the proper operation of the AT9933 based Cuk converter.

# Design and Operation of the Boost-Buck Converter

For details on the design for a Boost-Buck converter using the AT9933 and the calculation of the damping components, please refer to Application Note AN-H51.

## **Design Example Circuit**

#### **Design Example**

The choice of the resistor dividers to set the input and output current levels is illustrated by means of the design example given below.

The parameters of the power circuit are:

$$V_{IN\,MIN} = 9V$$

$$V_{IN\,MAX} = 16V$$

$$V_{O} = 28V$$

$$I_{O} = 0.35A$$

$$f_{S\,MIN} = 300kHz$$

Using these parameters, the values of the power stage inductors and capacitor can be computed as (see Application Note AN-H51 for details):

$$L1 = 82\mu H$$

$L2 = 150\mu H$

$C1 = 0.22\mu F$

The input and output currents for this design are:

$$I_{IN MAX} = 1.6A$$

$$\Delta I_{IN} = 0.21A$$

$$I_{O} = 350mA$$

$$\Delta I_{O} = 87.5mA$$

#### **Current Limits**

The current sense resistor ( $R_{\rm CS2}$ ), combined with the other resistors ( $R_{\rm S2}$  &  $R_{\rm REF2}$ ), determines the output current limits.

The current sense resistor ( $R_{\rm CS1}$ ), combined with the other resistors ( $R_{\rm S1}$  &  $R_{\rm REF1}$ ), determines the input current limits.

The resistors can be chosen using the following equations:

$$IXR_{CS} = 1.2VX \frac{R_S}{R_{RFF}} + 0.05V$$

(2)

$$\Delta I X R_{CS} = 0.1V X \frac{R_S}{R_{REF}} + 0.1V$$

(3)

Where I is the current (either  $I_O$  or  $I_{IN}$ ) and  $\Delta I$  is the peak-to-peak ripple in the current (either  $\Delta I_O$  or  $\Delta I_{IN}$ ).

For the input side, the current level used in the equations should be larger than the maximum input current so that it does not interfere with the normal operation of the circuit. The peak input current can be computed as:

$$I_{IN,PK} = I_{IN,MAX} + \frac{\Delta I_{in}}{2}$$

$$= 1.706A$$

(4)

Assuming a 30% peak-to-peak ripple when the converter is in input current limit mode, the minimum value of the input current will be:

$$I_{LIM,MIN} = 0.85 \cdot I_{IN,LIM} \tag{5}$$

Setting

$$I_{LIMMIN} = 1.05 \cdot I_{INPK} \tag{6}$$

The current level to limit the converter can then be computed.

$$I_{IN LIM} = \frac{1.05}{0.85} \bullet I_{IN PK}$$

(7)

= 2.1A

Using IO = 350mA and  $\Delta I_{O} = 87.5mA$  in (1) and (2),

$$R_{CS2} = 1.78\Omega$$

$$\frac{R_{S2}}{R_{REF2}}=0.5625$$

Before the design of the output side is complete, over voltage protection has to be included in the design. For this application, choose a 33V zener diode. This is the voltage at which the output will clamp in case of an open LED condition. For a 350mW diode, the maximum current rating at 33V works out to about 10mA. Using a 2.5mA current level during open LED conditions, and assuming the same  $R_{\rm SZ}/R_{\rm REF2}$  ratio,

$$R_{\rm CS2} + R_{\rm S2A} = 120\Omega \tag{8}$$

Choose the following values for the resistors:

$$R_{\rm CS2} = 1.65\Omega, \, 1/4W, \, 1\%$$

$R_{\rm REF2} = 10k\Omega, \, 1/8W, \, 1\%$

$R_{\rm S2A} = 100\Omega, \, 1/8W, \, 1\%$

$R_{\rm S2B} = 5.23k\Omega, \, 1/8W, \, 1\%$

The current sense resistor needs to be at least a 1/4W, 1% resistor.

Similarly, using  $I_{IN} = 2.1A$  and  $\Delta I_{IN} = 0.3xI_{IN} = 0.63$  in (1) and (2):

$$\begin{split} \frac{R_{S1}}{R_{REF1}} &= 0.442 \\ R_{CS1} &= 0.228 \Omega \\ P_{RCS1} &= I_{INLIM}^2 \bullet R_{CS1} = 1W \end{split}$$

Choose the following values for the resistors:

$$R_{\text{CS1}}$$

= parallel combination of three

0.68 $\Omega$ , 1/2W, 5%

$R_{\text{REF1}}$  = 10k $\Omega$ , 1/8W, 1%

$R_{\text{S1}}$  = 4.42k $\Omega$ , 1/8W, 1%

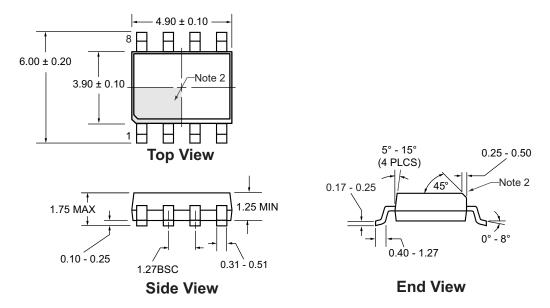

## 8-Lead SOIC (Narrow Body) Package Outline (LG)

Notes:

- 1. All dimensions in millimeters. Angles in degrees.

- 2. If the corner is not chamfered, then a Pin 1 identifier must be located within the area indicated.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell its products for use in such applications, unless it receives an adequate "product liability indemnification insurance agreement". **Supertex** does not assume responsibility for use of devices described and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the **Supertex** website: http://www.supertex.com.

©2006 **Supertex Inc.** All rights reserved. Unauthorized use or reproduction is prohibited.