# 30–36 GHz GaAs MMIC Power Amplifier

# **III Alpha**

#### AA032P1-00

#### **Features**

- Single Gate and Drain Biases

- 25 dBm Typical P<sub>1 dB</sub> Output Power at 31 GHz

- 11 dB Typical Small Signal Gain

- 0.25 µm Ti/Pd/Au Gates

- 100% On-Wafer RF and DC Testing

- 100% Visual Inspection to MIL-STD-883 MT 2010

#### Description

Alpha's two-stage reactively-matched Ka band GaAs MMIC power amplifier has a typical P<sub>1 dB</sub> of 25 dBm with 10 dB associated gain and 15% power added efficiency at 31 GHz. The chip uses Alpha's proven 0.25 µm MESFET technology, and is based upon MBE layers and electron beam lithography for the highest uniformity and repeatability. The FETs employ surface passivation to ensure a rugged, reliable part with through-substrate via holes and gold-based backside metallization to facilitate solder or epoxy die attach processes. Single gate and drain bias pads cover both stages, with the added convenience that the chip can be wire bonded from either side for either bias. All chips are screened for gain, output power, efficiency and Sparameters prior to shipment for guaranteed performance. A broad range of applications exist in both the military and commercial areas where high power and gain are required.

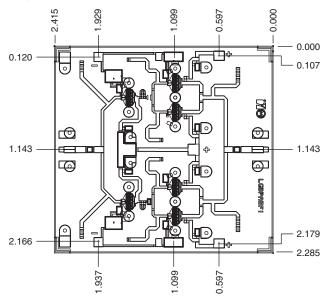

### **Chip Outline**

Dimensions indicated in mm. All DC (V) pads are  $0.1\,x\,0.1$  mm and RF In, Out pads are 0.07 mm wide. Chip thickness = 0.1 mm.

## **Absolute Maximum Ratings**

| Characteristic                          | Value             |  |

|-----------------------------------------|-------------------|--|

| Operating Temperature (T <sub>C</sub> ) | -55°C to +90°C    |  |

| Storage Temperature (T <sub>ST</sub> )  | -65°C to +150°C   |  |

| Bias Voltage (V <sub>D</sub> )          | 7 V <sub>DC</sub> |  |

| Power In (P <sub>IN</sub> )             | 22 dBm            |  |

| Junction Temperature (T <sub>J</sub> )  | 175°C             |  |

# Electrical Specifications at 25°C ( $V_{DS} = 6 \text{ V}$ , $V_{GS} = -1 \text{ V}$ )

| Parameter                             | Condition            | Symbol            | Min. | Typ. <sup>2</sup> | Max. | Unit |

|---------------------------------------|----------------------|-------------------|------|-------------------|------|------|

| Drain Current (at Saturation)         |                      | I <sub>DS</sub>   |      | 400               | 450  | mA   |

| Small Signal Gain                     | F = 30–31, 34–36 GHz | G                 | 8    | 11                |      | dB   |

| Input Return Loss                     | F = 30–31, 34–36 GHz | RL <sub>I</sub>   |      | -7                | -6   | dB   |

| Output Return Loss                    | F = 30–31, 34–36 GHz | RLO               |      | -8                | -6   | dB   |

| Output Power at 1 dB Gain Compression | F = 31 GHz           | P <sub>1 dB</sub> | 24   | 25                |      | dBm  |

| Saturated Output Power                | F = 31 GHz           | P <sub>SAT</sub>  | 25   | 27                |      | dBm  |

| Gain at Saturation                    | F = 31 GHz           | G <sub>SAT</sub>  |      | 8                 |      | dB   |

| Thermal Resistance <sup>1</sup>       |                      | $\Theta_{\sf JC}$ |      | 42                |      | °C/W |

<sup>1.</sup> Calculated value based on measurement of discrete FET.

<sup>2.</sup> Typical represents the median parameter value across the specified frequency range for the median chip.

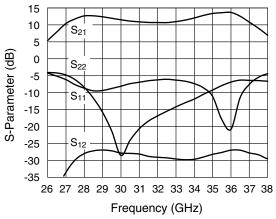

### **Typical Performance Data**

Typical Small Signal Performance S-Parameters (V<sub>DS</sub> = 6 V)

#### 28 27 26 P<sub>OUT</sub> 35 GHz 25 24 23 22 21 20 P<sub>OUT</sub> 28 GHz 19 18 P<sub>OUT</sub> 31 GHz 17 16 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 P<sub>IN</sub> (dBm)

**Typical Output Power Compression**

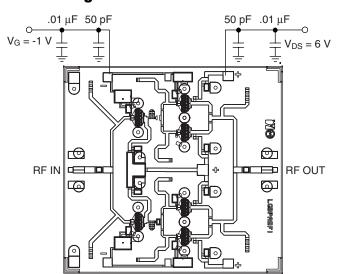

#### **Bias Arrangement**

The AA032P1-00 can be biased from either or both sides for both gate and drain biases.

For biasing on, adjust  $V_{GS}$  from zero to approximately -1 V. Adjust  $V_{DS}$  from zero to the desired value (4 V–6 V recommended). Adjust  $V_{GS}$  to achieve the desired  $I_{DS}$  (400 mA recommended). For biasing off, reverse the biasing on procedure.

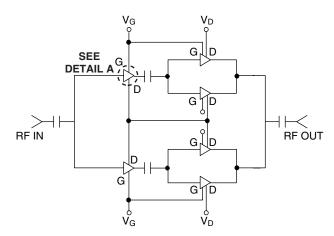

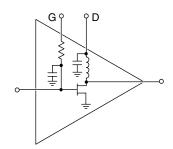

#### **Circuit Schematic**

Detail A