**D-20**

### STEREO 5W-20W DIGITAL AUDIO POWER AMPLIFIER CONTROLLER

#### Outline

YDA135 is digital audio power amplifier controller IC that is output power of 20W/channel on a 12V power supply operation.

This IC is combined with the general purpose Power MOSFET (hereafter called Power MOSFET) that are connected through BTL can configure an audio power amplifier with output power of 5W or 20W.

This IC accepts analog signal, converts it into digital pulse signal by the digital modulation circuitry and outputs the digital pulse signal for driving Power MOSFET. The Power MOSFET that is driven by this IC outputs large current digital pulses. The digital pulse signal is converted to audio signal through an external low pass filter, and sent to the speakers.

By using a general purpose Power MOSFET, very low cost digital amplifier system is configured. By adapting Yamaha's proprietary modulation system, the device provides low distortion and high signal to noise ratio at the highest level among digital amplifiers in the equiralent class.

This IC has the overcurrent detection function that detects overcurrent state by voltage drop of external resistors that detects the output current.

This IC has the high temperature detection function that detects high temperature by resistor value change of external element that detects temperature.

The operation of this IC is limited by using two control signal, SLEEP or MUTE. SLEEP signal stops all functions of this IC, and restrain to the power consumption at the minimum. MUTE signal brings Power MOSFET into nonconductive state, and mute the output of the device.

This IC is configured by two power supply; 5V for signal processing circuits, and 12V for Power MOSFET driving circuits.

#### ■ Features

- · High output power

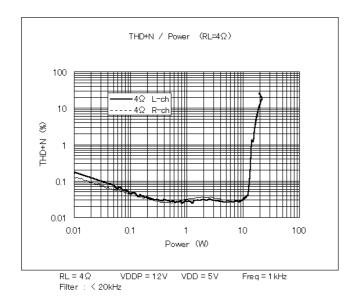

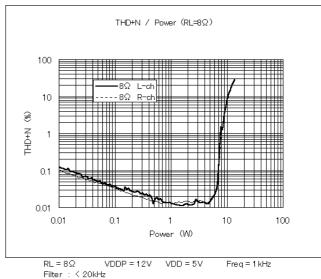

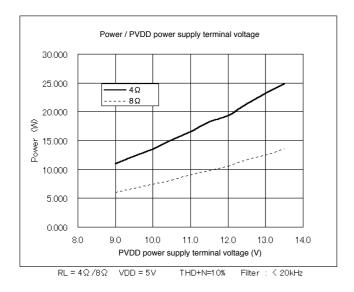

- 20W @ VDDP=12.0V RL=4Ω THD+N<10%

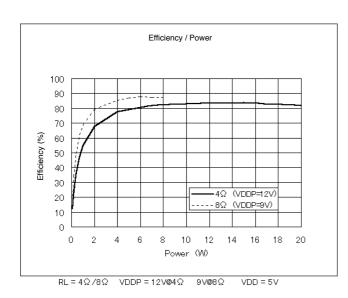

- · High efficiency operation

- 80 % @ VDDP=12.0V RL=4Ω Po=20W

- 85 % @ VDDP=12.0V RL=8Ω Po=10W

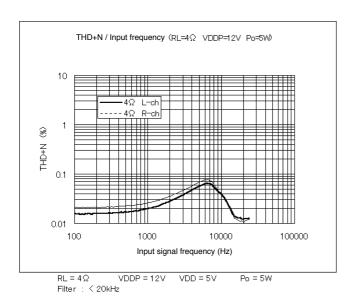

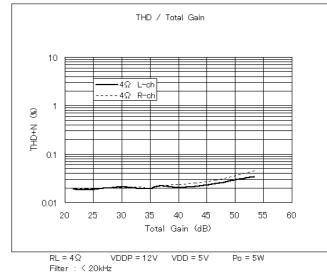

- Low distortion(THD+N)

- 0.03 % @ 1kHz RL=4Ω Po=7W

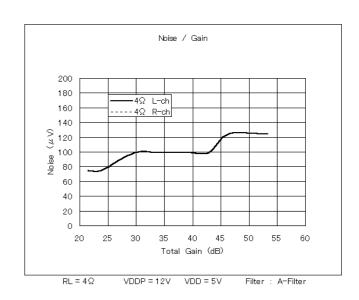

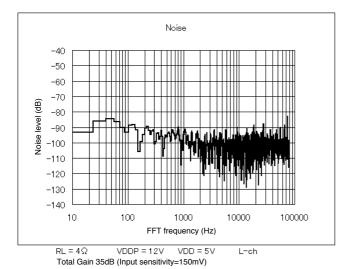

- · High signal to noise ratio

- 100 dB @ VDDP=12.0V Input sensitivity1.0V RL=4Ω

- 97 dB @ VDDP=12.0V Input sensitivity150mV RL=4Ω

- Low consumption current (12V/5V power supply)

- When Power MOSFET (FW332) is connected.

- 30mA /7mA @ VDDP=12.0V no signal

- 0.1mA/7mA @ VDDP=12.0V at mute  $1 \mu A/1 \mu A$  @ VDDP=12.0V at sleep

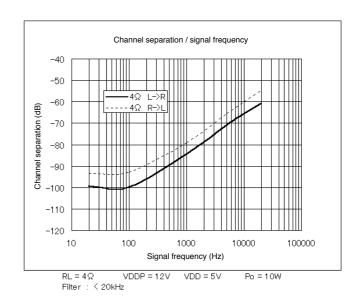

- CS(Channel separation)

80 dB @ 1kHz

- · Any gain setting by external resistors

- · Sleep function by SLEEP terminal

- · Output mute function by MUTE terminal

- Over current detection function (Power supply short-circuiting, Ground short-circuiting, Load short-circuiting)

- · High temperature detection function

- Pop noise suppression function at turn-on and turn-off

- 48-pin plastic LQFP (YDA135-VZ)

YAMAHA CORPORATION

YDA135CATALOG CATALOG No.:LSI-4DA135A2 2003.3

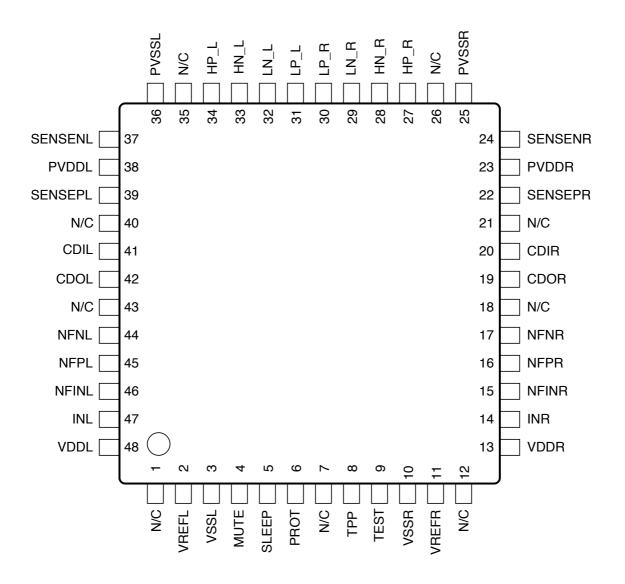

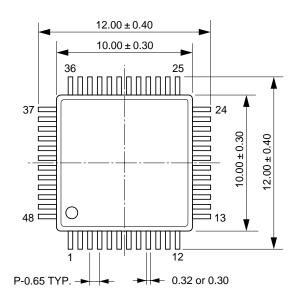

# ■ Terminal configuration

YDA135-VZ

<48 pin LQFP Top View>

# ■ Terminal function

| No. | Name    | I/O | Function                                     |

|-----|---------|-----|----------------------------------------------|

| 1   | N/C     | _   | Non connection                               |

| 2   | VREFL   | 0   | L channel reference voltage output           |

| 3   | VSSL    | _   | Ground for 5V power supply of L channel      |

| 4   | MUTE    | I   | Mute control                                 |

| 5   | SLEEP   | ı   | Sleep control                                |

| 6   | PROT    | Ō   | Warning signal output for detection function |

| 7   | N/C     | _   | Non connection                               |

| 8   | TPP     | I   | High temperature detection                   |

| 9   | TEST    | I   | IC test. Connect to VSSR                     |

| 10  | VSSR    | _   | Ground for 5V power supply of R channel      |

| 11  | VREFR   | 0   | R channel reference voltage output           |

| 12  | N/C     | _   | Non connection                               |

| 13  | VDDR    | _   | 5V Power supply of R channel                 |

| 14  | INR     | I   | R channel analog signal input                |

| 15  | NFINR   | 0   | R channel input gain setting                 |

| 16  | NFPR    | I   | R channel positive side feedback input       |

| 17  | NFNR    | I   | R channel negative side feedback input       |

| 18  | N/C     | _   | Non connection                               |

| 19  | CDOR    | 0   | R channel off time setting (output)          |

| 20  | CDIR    | I   | R channel off time setting (input)           |

| 21  | N/C     | _   | Non connection                               |

| 22  | SENSEPR | IH  | R channel overcurrent detection (PVDD side)  |

| 23  | PVDDR   | _   | 12V power supply of R channel                |

| 24  | SENSENR | IH  | R channel overcurrent detection (PVSS side)  |

| 25  | PVSSR   | _   | Ground for 12V power supply of R channel     |

| 26  | N/C     | _   | Non connection                               |

| 27  | HP_R    | ОН  | R channel positive side PMOS driving         |

| 28  | HN_R    | ОН  | R channel positive side NMOS driving         |

| 29  | LN_R    | ОН  | R channel negative side NMOS driving         |

| 30  | LP_R    | ОН  | R channel negative side PMOS driving         |

| 31  | LP_L    | ОН  | L channel negative side PMOS driving         |

| 32  | LN_L    | ОН  | L channel negative side NMOS driving         |

| 33  | HN L    | ОН  | L channel positive side NMOS driving         |

| 34  | HP_L    | ОН  | L channel positive side PMOS driving         |

| 35  | N/C     | _   | Non connection                               |

| 36  | PVSSL   | _   | Ground for 12V power supply of L channel     |

| 37  | SENSENL | IH  | L channel overcurrent detection (PVSS side)  |

| 38  | PVDDL   | _   | 12V power supply of L channel                |

| 39  | SENSEPL | IH  | L channel overcurrent detection (PVDD side)  |

| 40  | N/C     | _   | Non connection                               |

| 41  | CDIL    | I   | L channel off time setting (input)           |

| 42  | CDOL    | 0   | L channel off time setting (output)          |

| 43  | N/C     | _   | Non connection                               |

| 44  | NFNL    | I   | L channel negative side feedback input       |

| 45  | NFPL    | I   | L channel positive side feedback input       |

| 46  | NFINL   | 0   | L channel input gain setting                 |

| 47  | INL     | I   | L channel analog signal input                |

| 48  | VDDL    | _   | 5V power supply of L channel                 |

|     | l       |     | 1                                            |

Note. I/O: 5V input/5V output, IH/OH: 12V input/12V output

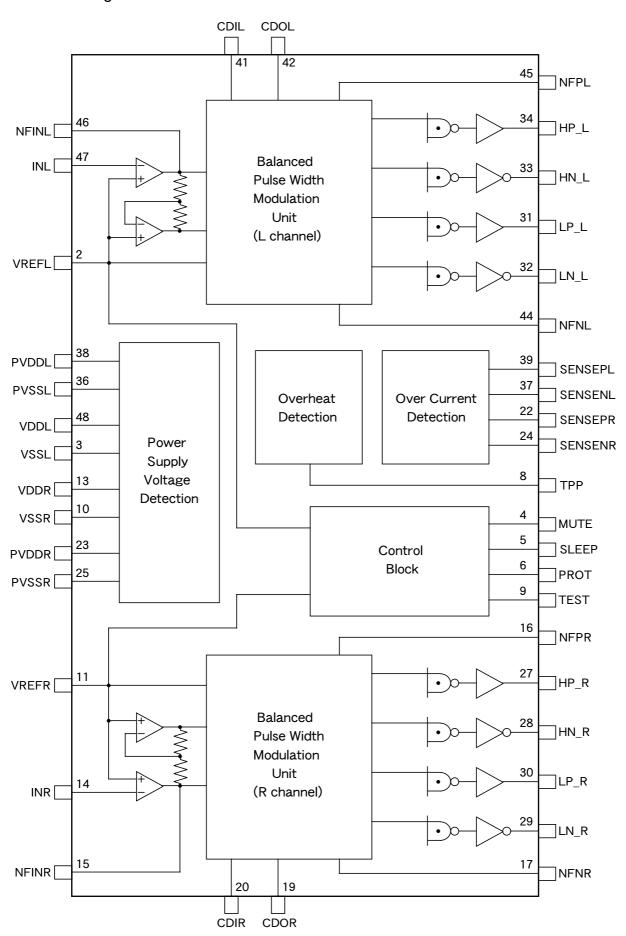

# ■ Internal block diagram

#### Description of terminal function

In the following explanations, "L" level and "H" level of SLEEP and MUTE terminals mean "VIL" and "VIH" respectively, and "L" level and "H" level of PROT terminal mean "VOL" and "VOH" respectively. "L" level and "H" level of output terminals such as HP\_L and HN\_L terminals also mean "VHOL" and "VHOH" respectively.

### Power supply and ground terminals

#### VDDL, VSSL, VDDR, VSSR (Pin No.48, 3, 13, 10)

VDDL and VSSL terminals are 5.0V power supply terminal and ground terminal for left channel signal processing circuit respectively. VDDR and VSSR terminals are 5.0V power supply terminal and ground terminal for right channel signal processing circuit respectively.

Left and right channels are equipped independent power supply terminal and ground terminal, respectively. All the ground terminals are connected through IC board (low resistor), but the power supply terminals for left and right channels are separated from each other.

#### PVDDL, PVSSL, PVDDR, PVSSR (Pin No.38, 36, 23, 25)

PVDDL and PVSSL are 12 V power supply and ground terminals for left channel Power MOSFET driving circuit respectively.

PVDDR and PVSSR are 12 V power supply and ground terminals for right channel Power MOSFET driving circuit respectively.

Left and right channels are equipped independent power supply terminal and ground terminal, respectively. All the ground terminals are connected through IC board (low resistor), but the power supply terminals for left and right channels are separated from each other.

## Analog terminals

#### INL, NFINL, INR, NFINR (Pin No.47, 46, 14, 15)

INL and NFINL are analog signal input and gain adjustment terminals for left channel.

INR and NFINR are analog signal input and gain adjustment terminals for right channel.

The terminals are connected respectively to the negative input terminal and output terminal of the first stage inversion operational amplifiers.

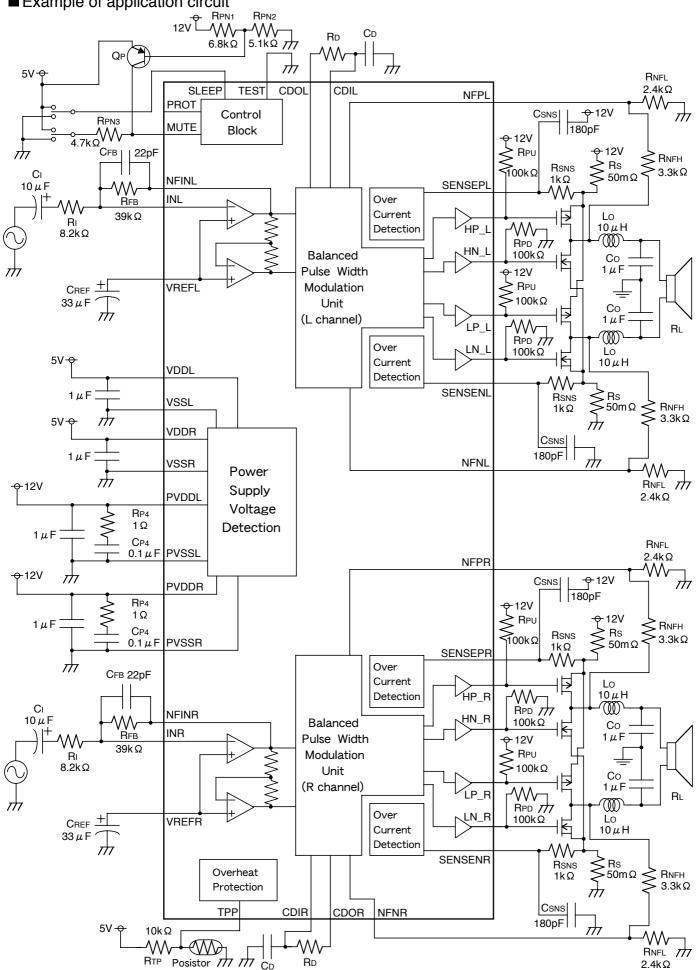

The amplifier gain is set by connecting an input resistor and a feedback resistor to both terminals as shown the "Example of application circuit".

The use of this inversion operational amplifier allows making a filter such as low band boost filter.

### VREFL, VREFR (Pin No.2, 11)

VREFL is the reference voltage output terminal for the left channel. It outputs 1/2 of 5V power supply terminal (VDDL) voltage.

VREFR is the reference voltage output terminal for the right channel. It outputs 1/2 of 5V power supply terminal (VDDR) voltage.

Connect a capacitor with capacitance necessary to stabilize the voltage. Refer to "Pop noise reduction functions".

#### NFPL, NFNL, NFPR, NFNR (Pin No.45, 44, 16, 17)

NFPL and NFNL are the digital amplifier feedback input terminals for left channel.

NFPR and NFNR are the digital amplifier feedback input terminals for right channel.

Connect the feedback signal of positive side and negative side of H-bridge configuration Power MOSFET output to each terminal. At this time, as described in the "Example of application circuit", divide the voltage of feedback signal with external resistor to prevent the maximum voltage from exceeding 5V and input to each terminal.

#### HP L, HN L, LP L, LN L, HP R, HN R, LP R, LN R (Pin No.34, 33, 31, 32, 27, 28, 30, 29)

HP\_L, HN\_L, LP\_L and LN\_L are Power MOSFET driving terminals for left channel.

HP\_L is a driving output terminal for positive side P channel Power MOSFET (PMOS), HN\_L is the one for positive side N channel Power MOSFET (NMOS), LP\_L is the one for negative side P channel Power MOSFET (PMOS), and LN\_L is the one for negative side N channel Power MOSFET (NMOS).

HP\_R, HN\_R, LP\_R and LN\_R are Power MOSFET driving terminals for right channel.

HP\_R is a driving output terminal for positive side P channel Power MOSFET (PMOS), HN\_R is the one for positive side N channel Power MOSFET (NMOS), LP\_R is the one for negative side P channel Power MOSFET (PMOS), and LN\_R is the one for negative side N channel Power MOSFET (NMOS).

#### CDIL, CDOL, CDIR, CDOR (Pin No.41, 42, 20, 19)

CDIL and CDOL are for connecting a resistor and a capacitor for setting off time of external Power MOSFET for left channel (refer to "Amplifier functions").

CDIR and CDOR are for connecting a resistor and a capacitor for setting off time of external Power MOSFET for right channel.

It is necessary to determine the resistor and capacitor to obtain a time constant according the characteristics of Power MOSFET that is to be used and distortion rate of amplifier you need. Refer to "Amplifier functions".

#### SENSEPL, SENSENL, SENSEPR, SENSENR (Pin No.39, 37, 22, 24)

SENSEPL and SENSENL are the overcurrent detection terminals for left channel.

SENSEPR and SENSENR are the overcurrent detection terminals for right channel.

As described in the "Example of application circuit", connect an end of the current detection resistor to power supply side and ground side of Power MOSFET, and connect other end of the resistor to SENSEPL and SENSENL terminals, and SENSEPR and SENSENR terminals respectively.

This IC determines that overcurrent state has occurred when the voltage drop at the current detection resistor becomes specified values (VOCPN and VDDP-VOCPP) or over.

It is necessary to determine the resistance of the current detection resistor optimally according to the characteristics of Power MOSFET.

When the overcurrent detection circuitry of left channel or right channel determines overcurrent state, "H" level is outputted from the warning signal output (PROT) terminal.

When the warning signal is outputted due to overcurrent detection, this IC keeps the warning signal output (PROT="H" level) after the current return to normal state.

#### TPP (Pin No.8)

TPP is the high temperature detection terminal.

As described in the "Example of application circuit", connect a temperature detection element (such as a posistor) between TPP terminal and 5 V system ground terminal. In addition, connect a resistor with proper value between TPP terminal and 5V system power supply terminal. At this time, arranges the temperature detection near Power MOSFET. As the temperature of Power MOSFET rises, the resistor value of the temperature detection element increases, and the voltage of TPP terminal also increases accordingly. This IC determines that high temperature state has occurred when the voltage of TPP terminal has become specified value (VTPP) or over, and outputs "H" level from the warning signal output (PROT) terminal.

When the warning signal is outputted due to high temperature detection, this IC keeps the warning signal output (PROT="H" level) after the temperature return to normal state.

#### Digital terminals

### SLEEP (Pin No.5)

SLEEP is the sleep control terminal. It controls both left and right channels simultaneously.

When SLEEP terminal is set at "H" level, all functions of this IC is stopped, and this IC is placed in the sleep state. At this time, all Power MOSFET driving terminals output signals that turn off the Power MOSFETs.

Though all Power MOSFETs are placed in the off state (non conductive state), the speaker terminal is made ground potential by the externally connected resistor.

At this time, restrain the power consumption at the minimum, and warning signal (PROT terminal output) is set at "L" level. When SLEEP terminal is changed from "H" level to "L" level, this IC goes into normal operation after sufficient time (starting time) to make each reference voltage reaches a fixed potential.

#### MUTE (Pin No.4)

MUTE is the mute control terminal. It controls both left and right channels simultaneously.

When MUTE terminal is set at "H" level, all Power MOSFET driving terminals output signals that turns off the Power MOSFETs. Though all Power MOSFETs are placed in the off state (non conductive state), the speaker terminal is made ground potential by the externally connected resistor, and the amplifier becomes mute state. At this time, the overcurrent protection function stops.

When MUTE terminal is set to "L" level, this IC goes into normal operating state.

#### PROT (Pin No.6)

PROT is the warning signal output terminal that has both overcurrent and high temperature detection functions. The terminal outputs "H" level when either function detects an abnormality state.

When the warning signal (PROT terminal="H" level) is outputted by abnormality state detection, this IC keep the warning signal output after return to normal state.

The warning signal is cancelled by changing the state of SLEEP terminal to "H" level or turning off the power supply.

#### TEST (Pin No.9)

This is the terminal for testing. Connect to VSSR terminal.

# ■ Mode setting and error detection

|       |      |     |        | L channel |      |        |      | R channel |        |        |        |        |      |      |      |      |        |        |      |                                                         |

|-------|------|-----|--------|-----------|------|--------|------|-----------|--------|--------|--------|--------|------|------|------|------|--------|--------|------|---------------------------------------------------------|

| SLEEP | MUTE | ТРР | SENSPL | SENSNL    | HP_L | J_NH   | LP_L | LN_L      | HMOS_L | T_SOM1 | SENSPR | SENSNR | HP_R | HN_R | LP_R | LN_R | HMOS_R | LMOS_R | PROT | Mode                                                    |

| Н     | *    | *   | *      | *         | Η    | L      | Η    | L         | L      | L      | *      | *      | Η    | ┙    | Н    | L    | L      | L      | ш    | Sleep mode                                              |

| L     | Η    | Р   | *      | *         | Η    | ┙      | Н    | L         | L      | L      | *      | *      | Н    | L    | Н    | L    | L      | L      | Χ    | Mute mode                                               |

| L     | Η    | F   | *      | *         | Η    | $\Box$ | Τ    | L         | L      | L      | *      | *      | Ι    | Ш    | Н    | L    | L      | L      | Ι    | Mute mode / High temperature detection                  |

| L     | L    | Р   | Р      | Р         | Χ    | Χ      | Χ    | Х         | Х      | Х      | Р      | Р      | Χ    | Χ    | Х    | Χ    | Χ      | Х      | Χ    | 2 channel output mode                                   |

| L     | L    | F   | Р      | Р         | Χ    | Х      | Χ    | Х         | Х      | Х      | Р      | Р      | Х    | Х    | Х    | Χ    | Х      | Х      | Ι    | 2 channel output mode / High temperature detection      |

| L     | ┙    | Р   | F      | Р         | Χ    | Χ      | Χ    | Х         | Х      | Х      | Р      | Р      | Χ    | Χ    | Х    | Χ    | Χ      | Х      | Ι    | 2 channel output mode / L channel overcurrent detection |

| L     | Ĺ    | Р   | Р      | F         | Χ    | Χ      | Χ    | Χ         | Х      | Χ      | Р      | Р      | Χ    | Χ    | Χ    | Χ    | Χ      | Χ      | Τ    | 2 channel output mode / L channel overcurrent detection |

| Ĺ     | L    | Р   | Р      | Р         | Χ    | Χ      | Χ    | Χ         | X      | Χ      | F      | Р      | Χ    | Χ    | Χ    | Χ    | Χ      | Χ      | Η    | 2 channel output mode / R channel overcurrent detection |

| L     | L    | Р   | Р      | Р         | Χ    | X      | Χ    | Χ         | X      | Χ      | Р      | F      | Χ    | Χ    | Χ    | Χ    | Χ      | Χ      | Н    | 2 channel output mode / R channel overcurrent detection |

#### Note:

- 1) HMOS\_L, LMOS\_L, HMOS\_R and LMOS\_R terminal mean outputs of Power MOSFET that are positive at left channel side, negative at left channel side, positive at right channel side, and negative at right channel side respectively.

- "L" means that the terminals are pulled down by the resistor that is used in the "Example of application circuit". "X" means pulse outputting state.

- 2) "X" of PROT terminal means that is in state of either "L" or "H" by the previous state.

- 3) "P" of SENSE\* and TPP terminals means normal state (Pass), and "F" means abnormal state (Fail).

- 4) "X" of output terminals such as HP\_L, HN\_L terminals means pulse outputting state.

- 5) "\*" means "Don't care".

# ■ Description of functions

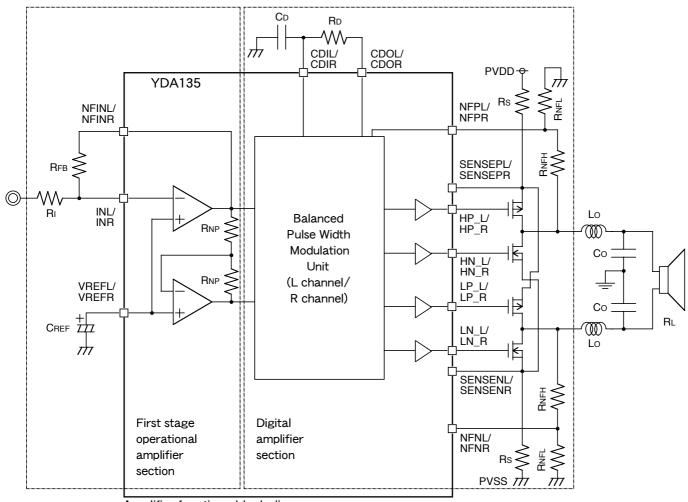

#### Amplifier functions

Amplifier functions block diagram

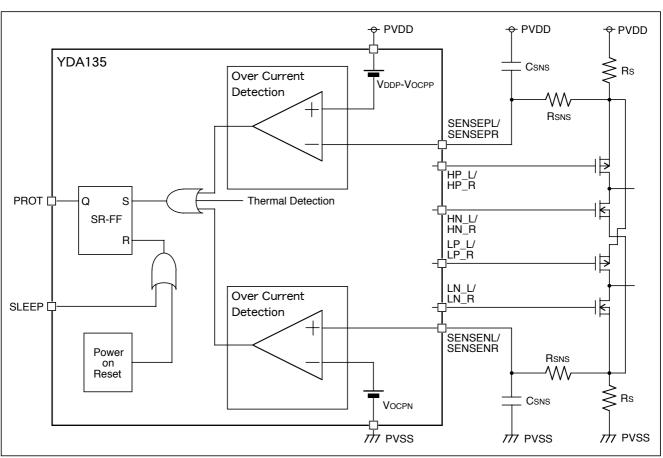

The amplifier section of this IC consists of the first stage operational amplifier and the second digital amplifier. The gain of the first stage operational amplifier is set with externally connecting an input resistor (RI) and feedback resistor (RFB). The second stage digital amplifier connects Power MOSFET externally, of which output is fed back to the modulation circuitry of the digital amplifier section through the external feedback resistors (RNFH and RNFL). This feature realizes the low distortion rate.

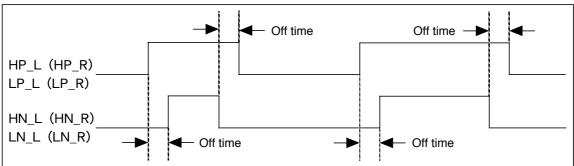

To prevent occurrence of penetration current caused by simultaneous on state of external Power MOSFET, a period in which both PMOS and NMOS are not on state ("off time") is provided. This time is set by using an external resistor (RD) and capacitor (CD).

The output of Power MOSFET is connected to the speakers through the secondary low pass filter consisting of an inductor (Lo) and a capacitor (Co). This feature removes the carrier frequency component contained in the output of Power MOSFET, and sent only audio signals to the speakers.

#### Gain setting

The gain of first stage operational amplifier is calculated by the following formula. The gain of the digital amplifier section that includes the gain (8dB) of internal digital amplifier section and gain of the external feedback resistor is calculated by the following formula.

|                                           |                     | Gain                                                      |

|-------------------------------------------|---------------------|-----------------------------------------------------------|

| First stage operational amplifier section | 20*log(2*RFB/RI) dB | (Gain is set by RI and RFB. Condition : RI > $2k\Omega$ ) |

| Digital amplifier section                 | 8+20*log(1+RNFH/RN  | FL) dB                                                    |

An "Example of application circuit" uses RI= $8.2k\Omega$ , RFB= $39k\Omega$ , RNFH= $3.3k\Omega$  and RNFL= $2.4k\Omega$ , which give total gain (Av) that is calculated by using the following formula. With this setting, the input sensitivity is 150mVrms, where the maximum output can be obtained when the input is 150mVrms.

Av (dB) =

$$20*\log(2*39/8.2) + 8 + 20*\log(1+3.3/2.4)$$

= 35.1 dB

This section explains how to set the gain for maximum level of the input signal. The relationship between the maximum level of input signal, Vin (peak value), RI and RFB is given by the following formula. (When RNFH= $3.3k\Omega$ , RNFL= $2.4k\Omega$ .)

Vin(peak value) = RI / RFB

For example, when setting as Vin = 300mVrms, the formula is "300mVrms\*  $\sqrt{2} = RI / RFB$ ". When RFB = 39k $\Omega$ , the value of RI is approximately 16k $\Omega$ . Set the value of RI as 2k $\Omega$  or less.

When setting the gain of the operational amplifier, which is initial stage, it is necessary to observe the restrictions that are described in "Pop noise reduction functions". Due to the limitation on operational amplifier driving capability, it is necessary to make the feedback resistance (RFB)  $10k\Omega$  or over.

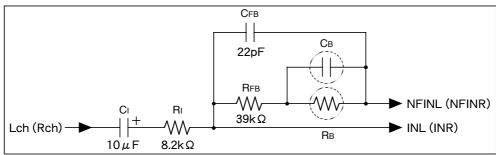

The use of the initial stage operational amplifier section allows configuration of a "Low band boost filter circuit" described below.

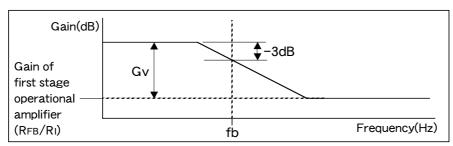

This filter has a frequency response which is similar to the "Characteristics of low band boost filter" described below, and the amount of boost (Gv) for the gain of initial stage inversion operational amplifier, and the cut-off frequency (fb) at a point where the boost gain is reduced by 3dB can be described by the following formula.

Low band boost filter circuit

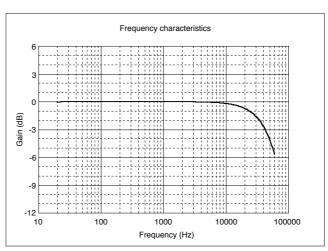

Characteristics of low band boost filter

Gv(dB) = 20\*log((RFB + RB)/RFB)

$fb(Hz) = 1/(2 \pi *CB*RB)$

When low band boost function is used, the total gain in the low band that is boosted after it is amplified by the digital amplifier section becomes "total gain (Av) + boost amount (Gv)".

For the "Example of application circuit", a capacitor (CFB) for cutting off high frequency range is attached for limiting the band of input signal. The value can be adjusted if necessary. (Cut-off frequency =  $1/(2\pi * CFB*RFB)$ ). DC cutting capacitor (Ci) is attached for limiting the input DC current. This capacitor and input resistor (Ri) constitutes a low cutoff filter. Set the filter for sufficiently low cutoff frequency. (Cut-off frequency =  $1/(2\pi * CI*RI)$ ).

The external feedback resistors (RNFH and RNFL) are set so that they meet the following relational expression depending on the input stage power supply voltage (VDD) and output stage power supply voltage (PVDD). For RNFL, select the largest value resistor meeting this expression.

Use the resistor with an accuracy of 1% for reduction of offset voltage.

$RNFL \leq VDD/(VDDP - VDD)*RNFH$

$600\Omega \le (RNFH + RNFL) \le 6k\Omega$

#### Selection of Power MOSFET

Power MOSFET can be selected on the user side within the range of the absolute maximum rating. When selecting Power MOSFET, take note of the following matters.

- The drain side voltage may be twice the maximum power supply voltage due to the counter electromotive force developed in the inductive load.

- When VDDP=12V, use Power MOSFET of which withstand voltage VDS is 30V or higher.

- For the gate voltage, the voltage VDDP is applied. Therefore, use Power MOSFET of which withstand voltage VGS is 20V or higher.

- Due to the limitation of allowable power consumption of this IC, use Power MOSFET of which total input charges (VDS=10V, VGS=10V) is 9 nC or less.

To prevent destruction of Power MOSFET caused by simultaneous turn-on of PMOS and NMOS of Power MOSFET, off time such as the following "Power MOSFET output waveform and off time" can be set for Power MOSFET depending on the resistor (RD) and capacitor (CD) that are connected to CDIL, CDIR, CDOL and CDOR terminals. Connect a proper resistor (RD) and capacitor (CD) according the characteristics of Power MOSFET.

As the time constant is made smaller, off time becomes shorter. Adjust the off time so that the penetration current does not flow through the Power MOSFET, as shorter off time can cause penetration current to flow.

As the time constant is made larger, off time becomes longer. Longer off time makes the margin from the moment of simultaneous turn on of the Power MOSFET larger, but at the same time, the distortion characteristic changes for the worse.

Power MOSFET output waveform and off time

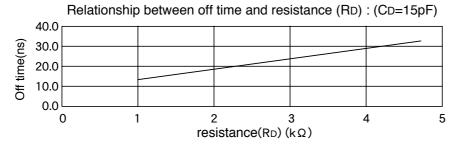

An indication of off time is in the range approximately from 10ns to 40ns. As an example, the relationship between the resistance (RD) and off time is as described by the "Relationship between off time and resistance (RD)" described below when the capacitance (CD) = 15pF.

#### Selection of inductor for output filter

The cutoff frequency (fc) of the LC low pass filter that is connected to the output of the Power MOSFET can be obtained by using the following formula.

To obtain an ideal frequency response, set the Q value of LCR resonance circuit to approximately 0.7.

fc(Hz) =

$$1/(2*\pi*\sqrt{(Lo*Co)})$$

Q =  $1/RL*\sqrt{(Lo/Co)} = 0.7$

Typically, the one with the following value is used depending on the speaker impedance assuming that the cutoff frequecy of 50kHz is used.

| RL(Load impedance) | Lo(Inductance) | Co(Capacitor) |  |  |  |

|--------------------|----------------|---------------|--|--|--|

| 4Ω                 | 10μH           | 1μF           |  |  |  |

| 8Ω                 | 22 μ Η         | 0.47 μ F      |  |  |  |

| 16Ω                | 39 μ Η         | 0.27 μ F      |  |  |  |

The distortion factor and voice quality may be affected by the type of coil to be used. Select the best suited one according to the response required.

#### Overcurrent detection functions

The overcurrent detection is a function that determines that the overcurrent state has occurred and set PROT terminal to "H" level, when the current flowing in the external Power MOSFET has become equal to or higher than the specified value. (This IC does not internally perform processing that turns off Power MOSFET automatically in such case.)

For the "Example of application circuit", the circuit related to the overcurrent detection function is as shown in the following figure, "Overcurrent detection function block diagram".

Connect a current detection resistor (Rs) between PMOS (source side) pin and power supply pin PVDD of Power MOSFET, and between NMOS (source side) pin and PVSS pin. Connect PMOS (source side) pin and SENSEPL pin through the low pass filter consisting of RsNs and CsNs, and NMOS (source side) and SENSENL pins as well. To prevent erroneous detection of glitch noise that can occur at switching of Power MOSFET, be sure to use the low pass filter consisting of RsNs and CsNs. Connect SENSEPR pin and SENSENR pin in the same way. This IC recognizes an overcurrent state when the potential of SENSEPL pin or SENSEPR pin has decreased below the overcurrent detection threshold voltage (Vocpp) for a certain period (Tocp), bringing PROT pin to "H" level. When the potential of SENSENL pin or SENSENR pin has increased over the overcurrent detection threshold voltage (Vocpn) for a certain period, it recognizes the overcurrent state, bringing PROT pin to "H" level. At this time, set SLEEP pin of MUTE pin to "H" to force the Power MOSFET to OFF.

After this, inputting "H" level once to SLEEP or turning off the power supply and then on again can restore the output of PROT pin to initial "L" state.

When it is not necessary to use the overcurrent detection function, connect SENSEPL pin and SENSEPR to PVDD, and SENSENL pin and SENSENR pin to PVSS (to disable the function).

When in sleep mode (SLEEP pin = "H" level) or in mute mode (MUTE pin = "H" level), this IC sets the Power MOSFET to OFF state, and thus, the overcurrent detection function of both L channel and R channel are stopped. For this circuit, use the overcurrent detection resistor (Rs) with low inductive component. The resistance is to be determined based on the drain current rating (IDMAX: pulse current) and overcurrent threshold voltages (VOCPP, VOCPN) according to the conditions described below.

Rs ≥ VOCPN / IDMAX

Overcurrent detection function block diagram

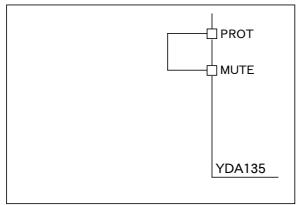

When overcurrent has been detected, Power MOSFET can be protected by the following methods.

- (1)Turning off Power MOSFET when overcurrent has been detected.

Connect PROT terminal and MUTE terminal externally as shown in the following "Power MOSFET protection circuit". With this method, the device is brought into mute state when overcurrent has been detected, where Power MOSFET is turned off to limit the current flowing into Power MOSFET. At this time, the protected state can be cancelled by setting SLEEP terminal to "H" level or by bringing VDD or PVDD power supply terminal voltage to the level below the shut off voltage once.

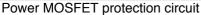

- (2)Turning off Power MOSFET when overcurrent has been detected and restarting it.

Connect PROT terminal and SLEEP terminal through external circuit as shown in the following "External automatic restoration circuit". With this method, SLEEP terminal becomes "H" level when overcurrent has been detected, and this IC is brought into sleep state (Power MOSFET is turned off). After this, when a certain period that depends on the RC time constant has elapsed, SLEEP terminal becomes "L" level where this IC restarts automatically.

External automatic restoration circuit

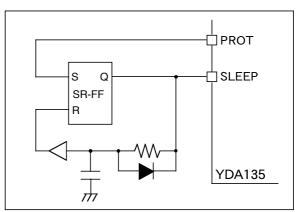

#### High temperature detection functions

The high temperature detection is a function that determines that the high temperature state has occurred and set PROT terminal to "H" level when the temperature of the temperature detection element (such as posistor\*1) that is placed in the location that is thermally equivalent with Power MOSFET has become equal to or higher than the specified value. (This IC does not internally perform processing that turns off Power MOSFET automatically in such case.)

For the "Example of application circuit", the circuit related to the high temperature detection function is as shown in the next page, "High temperature detection function block diagram".

\*1: "posistor" is a registered trade mark of Murata Manufacturing Co., Ltd. for their positive thermisters.

High temperature detection function block diagram

Connect the temperature detection element with positive temperature coefficient between VSS and TPP terminal by the number of pieces required.

In addition, connect a resistor(RTP) between TPP terminal and VDD power supply terminal. Resistor value of temperature detection element is changed by rise in temperature. Select a resistor so that the threshold (VTPP) is attained depending on the characteristic of the temperature detection element.

This IC determines that high temperature state has occurred when the potential of TPP terminal has exceeded the high temperature detection threshold voltage (VTPP) for a certain period (TTPP), and then sets PROT terminal to "H" level. At this time, set SLEEP terminal or MUTE terminal to "H" level to turn off Power MOSFET forcibly to limit the temperature rise.

PROT terminal output can be returned to initial "L" level output state by inputting "H" level once to SLEEP terminal or by turning off the power and then on again.

In sleep mode (SLEEP="H"), the high temperature detection function of this IC is disabled.

Since TPP terminal is a single terminal, the temperature detection circuit detects temperature of two channels collectively outside of this IC.

When the high temperature detection function is not used, connet TPP to the ground (to disable the high temperature detection function).

When high temperature state has been detected, Power MOSFET can be protected by the following methods.

- (1)Turning off Power MOSFET when high temperature has been detected.

- Connect PROT terminal and MUTE terminal externally as shown in the "Power MOSFET protection circuit" of the previous page. With this method, the device is brought into mute state when high temperature has been detected, where Power MOSFET is turned off to limit the current flowing into Power MOSFET to allow reduction of the temperature. At this time, the protected state can be cancelled by setting SLEEP terminal to "H" level once or by bringing VDD or PVDD power supply terminal voltage to the level below the shut off voltage once.

- (2)Turning off Power MOSFET when high temperature has been detected and restarting it after a certain period. Connect PROT terminal and SLEEP terminal through external circuit as shown in the "External automatic restoration circuit" of the previous page.

- With this method, SLEEP terminal becomes "H" level when high temperature has been detected, and this IC is brought into sleep state (Power MOSFET is turned off). After this, when a certain period that depends on the RC time constant has elapsed, SLEEP terminal becomes "L" level where this IC restarts automatically.

#### Sleep control functions

When SLEEP terminal is set to H" level, this IC changes into sleep mode. When SLEEP terminal is set to "L" level, this IC changes into normal operating state. In sleep mode, all functions are disabled, and power consumption is minimized.

At this time, all Power MOSFET driving terminals output signals that turns off the Power MOSFETs. Though all Power MOSFETs become off state, the speaker terminal is made ground potential by the externally connected resistors (RNFL and RNFH).

When MUTE terminal is changed from "H" level to "L" level, restarting sequence operates internally. This IC changes into normal operating state after the period that is set with a capacitor connected to VREFL terminal and VREFR terminal (starting time) has elapsed.

When SLEEP terminal is set to "H" level, PROT terminal is set to "L" level forcibly.

#### Output mute control functions

When MUTE terminal is set to H" level, this IC change into mute mode. When MUTE terminal is set to "L" level, this IC change into normal operating state. In the mute mode, the internal clock stops. At this time, all Power MOSFET driving terminals output signals that turns off the Power MOSFETs. Though all Power MOSFETs become off state, the speaker terminal is made ground potential by the externally connected resistors (RNFL and RNFH).

#### Pop noise reduction functions

This IC includes pop noise reduction function that works when turn on and turn off the power supply and enabling or canceling sleep mode.

At power on, this IC starts the starting sequence after 12V system's power supply voltage (VDDP) for Power MOSFET driving circuit and 5 V system's power supply voltage (VDD) for signal processing circuit has exceeded their low voltage malfunction prevention threshold (VUV12 and VUV5) respectively. In the starting sequence, the pop noise can be reduced because the mute mode is canceled after the potential of input signal terminals (INL and INR) and potential of reference voltage output terminals (VREFL and VREFR) have stabilized sufficiently (after the elapse of starting period).

Also, when shutting off the power supply, the pop noise can be reduced by reducing 12V power supply voltage and 5V power supply voltage below the low voltage malfunction prevention threshold (VUV12 and VUV5) earlier than the shift of the potential of input signal terminals (INL and INR) and potential of reference voltage output terminals (VREFL and VREFR).

The pop noise is also reduced by enabling the mute mode when the 5V system power supply voltage has changed 10% of 1/2 of VREF terminal voltage. Moreover, the pop noise can be reduced by using MUTE terminal control circuit as shown in the "Example of application circuit" when the speed of reduction of the power supply voltage is slow.

When the sleep mode is disabled, the pop noise can be reduced by using the starting sequence.

When the sleep mode is enabled, the pop noise is reduced because the mute mode is enabled simultaneously. To make the pop noise reduction function operate effectively when turning on the power supply, it is necessary to set the values of capacitor (CREF) that is connected to VREFL terminal and VREFR terminal, the resistor (RI) and capacitor (CI) that are connected to INL terminal and INR terminal as described below.

CREF > RI \* CI / 5000

### Pop noise reduction functions

Starting time is a period for each reference voltage to reach the specified potential (for charging capacitors (CREF) of VREFL and VREFR terminals) when the power supply is turned on or is turned on again. This period varies in relation to the capacitance (CREF) of VREFL and VREFR terminals. The table of starting time is as follows:

| CREF capacitor( $\mu$ F) | Starting time (sec) |

|--------------------------|---------------------|

| 2                        | 0.13                |

| 10                       | 0.33                |

| 30                       | 0.85                |

| 50                       | 1.40                |

# How to supply power to 5V system

Since the operation of the 5V system power supply of this IC is guaranteed in the wide fluctuation range (10%), the power can be generated from 12V system power supply by using a zener diode. This features allows to operate this IC by using only a 12V power supply.

# Monaural operation

This IC can be operated in monaural mode by modifying the "Example of application circuit" as follows. At this time, left channel is to be used.

It is not necessary to connect the resistors and capacitors, Power MOSFET and filter coils for right channel.

Terminal treatment in monaural operation

| Pin No. | Name    | Terminal treatment          |

|---------|---------|-----------------------------|

| 10      | VSSR    | Connect to ground           |

| 11      | VREFR   | Non connection              |

| 13      | VDDR    | Connect to 5V power supply  |

| 14      | INR     | Connect to 47Pin INL        |

| 15      | NFINR   | Non connection              |

| 16      | NFPR    | Connect to 5V power supply  |

| 17      | NFNR    | Connect to ground           |

| 19      | CDOR    | Connect to 20Pin CDIR       |

| 20      | CDIR    | Connect to 19Pin CDOR       |

| 22      | SENSEPR | Connect to 12V power supply |

| 23      | PVDDR   | Connect to 12V power supply |

| 24      | SENSENR | Connect to ground           |

| 25      | PVSSR   | Connect to ground           |

| 27      | HP_R    | Non connection              |

| 28      | HN_R    | Non connection              |

| 29      | LN_R    | Non connection              |

| 30      | LP_R    | Non connection              |

■ Example of application circuit

#### ■ Electrical characteristics

#### 1. Absolute maximum rating

| Item                                                 | Symbol | Min. | Max.     | Unit       |

|------------------------------------------------------|--------|------|----------|------------|

| Power supply voltage for 12V system (PVDD) *1,*2, *3 | VDDP   | -0.3 | 14.0     | V          |

| Power supply voltage for 5V system (VDD) *1, *2, *4  | VDD    | -0.3 | 7.0      | V          |

| Input and output voltage for 12V system *5           | VINP   | -0.5 | VDDP+0.5 | V          |

| Input and output voltage for 5V system *6            | VIN    | -0.5 | VDD+0.5  | V          |

| Storage temperature                                  | Tstg   | -50  | 125      | $^{\circ}$ |

Note: The absolute maximum rating is a value that must not be exceeded to guarantee the reliability and life of this IC, and thus, the use of this IC over the rating even for a moment may break down the device immediately or deteriorate its reliability severely.

- \*1: Vss covers all ground terminals including VSS, VSSL, VSSR, PVSSL and PVSSR. Place all VSS terminals in the same potential.

- \*2: The voltage is referenced to Vss=0V.

- \*3: 12V system power supply terminal (PVDD) covers PVDDL and PVDDR terminals.

- \*4: 5V system power supply terminal (VDD) covers VDDL and VDDR terminals.

- \*5: 12V system input/output terminal covers SENSENL, SENSEPL, SENSENR, SENSEPR, HP\_L, HN\_L, LP\_L, LN\_L, HP\_R, HN\_R, LP\_R and LN\_R terminals.

- \*6: 5V system input/output terminal covers SLEEP, MUTE, PROT, TPP, INL, NFINL, VREFL, NFPL, NFNL, CDIL, CDOL, INR, NFINR, VREFR, NFPR, NFNR, CDIR and CDOR terminals.

#### 2. Recommended operating conditions

| Item                                                  | Symbol | Min. | Тур. | Max. | Unit       |

|-------------------------------------------------------|--------|------|------|------|------------|

| Power supply voltage for 12V system *1                | PVDD   | 9.0  | 12.0 | 13.5 | V          |

| Power supply voltage for 5V system *2                 | VDD    | 4.5  | 5.0  | 5.5  | V          |

| Operating ambient temperature( ambient temperatureTa) | Тор    | 0    | 25   | 70   | $^{\circ}$ |

Note: When this IC is used outside of the above voltage range may lead to malfunction of the IC, possibly causing generation of noise on the speakers.

#### 3.DC characteristics (Vss=0V, VDD=5V $\pm$ 0.5V, VDDP=9V $\sim$ 13.5V, Ta=0°C $\sim$ 70°C)

| Item                                                                          | Symbol   | Condition   | Min.     | Тур.     | Max.    | Unit     |

|-------------------------------------------------------------------------------|----------|-------------|----------|----------|---------|----------|

| HP_L,HN_L,LP_L,LN_L,HP_R,HN_R, LP_R,LN_R output voltage "H" level             | Vнон     | IOH=-10mA   | VDDP-0.4 |          |         | V        |

| HP_L,HN_L,LP_L,LN_L,HP_R,HN_R, LP_R,LN_R output voltage "L" level             | VHOL     | IOL=10mA    |          |          | 0.4     | ٧        |

| PROT output voltage "H" level                                                 | Vон      | IOH=-80 μ A | VDD-1.0  |          |         | V        |

| PROT output voltage "L" level                                                 | Vol      | IOL=1.6mA   |          |          | 0.4     | V        |

| SLEEP, MUTE input voltage "H" level                                           | VIH      |             | 0.7*VDD  |          |         | /        |

| SLEEP, MUTE input voltage "L" level                                           | VIL      |             |          |          | 0.3*VDD | \<br>\   |

| Power supply side overcurrent detection threshold voltage                     | *1 VOCPP |             |          | VDDP-0.5 |         | <b>\</b> |

| Ground side overcurrent detection threshold voltage *2                        | VOCPN    |             |          | 0.5      |         | \<br>\   |

| Overcurrent detection delay time                                              | Тоср     |             |          | 0.4      |         | μs       |

| High temperature detection threshold voltage                                  | VTPP     |             |          | 1/2*VDD  |         | \<br>\   |

| High temperature detection delay time                                         | Ттрр     |             |          | 0.4      |         | μs       |

| 12V power supply side threshold voltage prevention of low voltage malfunction | VUV12    |             |          | 5.0      |         | <        |

| 5V power supply side threshold voltage prevention of low voltage malfunction  | VUV5     |             |          | 3.5      |         | ٧        |

| Consumption current (sleep mode) VDE                                          | ISLEEP   |             |          | 1        |         | μΑ       |

| PVD                                                                           | D ISLLL  |             |          | 1        |         | μΑ       |

| Consumption current (mute mode) VDD                                           | ) IMUTE  |             |          | 7        | _       | mA       |

| PVD                                                                           | D IIIII  |             |          | 0.1      |         | mA       |

| Consumption current (2 channel output mode) VDE                               | DIDD     |             |          | 7        |         | mA       |

| (no signal, no filter) PVD                                                    | D TIDE   |             |          | 30       |         | mA       |

Note: \*1: PVDD side overcurrent detection terminal covers SENSEPL, SENSEPR terminals.

<sup>\*1:</sup> The voltage is referenced to Vss=0V.

<sup>\*2:</sup> PVSS side overcurrent detection terminal covers SENSENL, SENSENR terminals.

### 4. Analog characteristics (Vss=0V, VDD=5.0V, VDDP=12.0V, Ta=25°C, load impedance=4Ω, Frequency=1kHz)

| Item                                           | Symbol | Condition               | Min. | Тур. | Max. | Unit |

|------------------------------------------------|--------|-------------------------|------|------|------|------|

| Maximum output                                 | Po     | THD=0.1%                |      | 13   |      | W    |

|                                                |        | THD=1%                  |      | 14   |      | W    |

|                                                |        | THD=10%                 |      | 20   |      | W    |

| Voltage gain<br>(RI=8.2kΩ, RFB=39kΩ)           | Av     |                         |      | 35.1 |      | dB   |

| Total harmonic distortion (Band Width: 20kHz ) | THD+N  | Po=7W                   |      | 0.03 |      | %    |

| Signal/noise ratio(A-Filter,                   | SNR    | Input sensitivity 150mV |      | 97   |      | dB   |

| Band Width: 20kHz, Po=20W)                     |        | Input sensitivity 1.0V  |      | 100  |      | dB   |

| Channel separation                             | CS     |                         |      | 80   |      | dB   |

| Maximum efficiency                             | η      | Load impedance=8Ω       |      | 85   |      | %    |

|                                                |        | Load impedance=4Ω       |      | 80   |      | %    |

| Output offset voltage                          | Vo     |                         |      | 30   |      | mV   |

Note: All analog characteristics shown above are the values obtained on the Yamaha's evaluation environment.

The characteristics may vary according to the Power MOSFET, coils, capacitors and pattern layout that are used in the system.

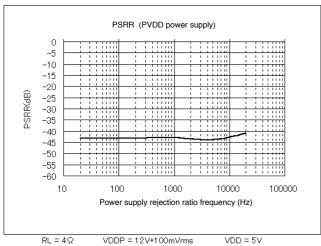

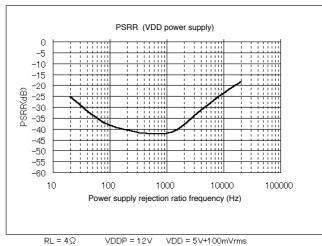

# ■ Characteristics example

Filter: < 20kHz

Filter : < 20kHz

Filter : < 20kHz

VDDP=12V VDD=5V Lo=10 μ H Co=1 μ F

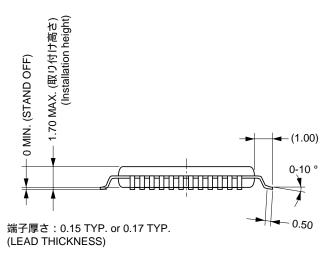

### ■ External dimensions of package

YDA135-VZ

C-PK48VP-0

モールドコーナー形状は、本図面と若干異なるタイプもあります。 カッコ内の寸法値は参考値とする。 モールド外形寸法はバリを含まない。 単位(UNIT): mm(millimeters)

The shape of the molded corner may slightly different from the shape in this diagram.

The figure in the parenthesis ( ) should be used as a reference.

Plastic body dimensions do not include burr of resin.

UNIT: mm

注)表面実装 LSI は保管条件及び、半田付けについての特別な配慮が必要です。 詳しくはヤマハ代理店までお問い合わせ下さい。

Note: The LSIs for surface mount need special consideration on storage and soldering conditions. For detailed information, please contact your nearest Yamaha agent.

#### **IMPORTANT NOTICE**

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL, OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANY THIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRANGIMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

Note) The specifications of this product are subject to change without notice.

| <br>Agency — |

|--------------|

|              |

|              |

|              |

|              |

|              |

|              |

# YAMAHA CORPORATION

#### Semiconductor Sales & Marketing Department

- Head Office 203, Matsunokijima, Toyooka-mura, Iwata-gun, Shizuoka-ken, 438-0192, Japan Tel. +81-539-62-4918 Fax. +81-539-62-5054

- Tokyo Office 2-17-11, Takanawa, Minato-ku, Tokyo, 108-8568, Japan

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

- Osaka Office 3-12-12, Minami Senba, Chuo-ku Osaka City, Osaka, 542-0081, Japan Tel. +81-6-6252-6221 Fax. +81-6-6252-6229