# 41KD Interrupt Holding Register

#### **Features**

- Up to four interrupt inputs per interrupt holding register

- Cascadable inputs and outputs for expansion

- Convenient interface signals: A0, E, R/W

- Individually maskable interrupt inputs

- Masking and interrupt registers may be read or written to verify operational integrity

- TTL/CMOS-compatible

- Low-power Schottky LSTTL-technology

#### **Description**

The 41KD Interrupt Holding Register (IHR) is designed to capture, mask, store, and retrieve interrupt signals in systems that contain integrated read and write control signals.\* The system must supply read and write timing via the 41KD device's enable signal. Control logic is provided that permits processor interfacing on a memory-mapped basis to all microprocessors or microcomputers. When queried by the processor for interrupts, the IHR returns a linear indication of pending interrupts on a one-to-one basis rather than a binary weighted priority indication. Various processor subroutines can be used to prioritize and stack pending interrupts. A single IHR can accommodate up to four interrupt inputs; however, cascadable inputs and outputs are provided for expansion. The IHR is an LSTTL-technology device and is packaged in a 16-pin plastic DIP (41KD), 16-pin plastic SOJ package (41KD-J), or in a 16-pin plastic SOIC package (41KD-W).

# **User Information**

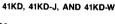

Figure 1. Block Diagram

<sup>\*</sup> Systems that have separate read and write control signals should use the 146R Interrupt Holding Register (DS87-315DBIP).

**Table 1. Pin Descriptions**

| ,      |   |                  |    |              |

|--------|---|------------------|----|--------------|

| ΨĒ     | 1 |                  | 16 | ☐ Vcc        |

| Ē      | 2 |                  | 15 | ⊒ R/W        |

| IHR3 🗆 | 3 |                  | 14 | □ D3         |

| īHŘ2 □ | 4 | 41KD             | 13 | □ D2         |

| IHR1 [ | 5 | 41KD-J<br>41KD-W | 12 | <b>□</b> D1  |

| IHRO [ | 6 |                  | 11 | □ <b>D</b> 0 |

| ΙŌ 🗆   | 7 |                  | 10 | □ A0         |

| GND [  | 8 |                  | 9  | MR           |

|        |   |                  |    |              |

| Pin   | Symbol    | Туре | Name                       |  |

|-------|-----------|------|----------------------------|--|

| 1     | 11        | ı    | Interrupt Input            |  |

| 2     | Ē         | ı    | Chip Enable                |  |

| 3—6   | IHR3—IHR0 | ı    | Interrupt Holding Register |  |

| 7     | ĪŌ        | 0    | Interrupt Output           |  |

| 8     | GND       | _    | Ground                     |  |

| 9     | MR        | 1    | Master Reset               |  |

| 10    | AO        | 1    | Address Input              |  |

| 11—14 | D0—D3     | 1/0  | Data Input and Output      |  |

| 15    | R/W       | ı    | Read or Write Signal       |  |

| 16    | Vcc       | _    | 5.0 ±0.5 V                 |  |

Figure 2. Pin Function Diagram

#### Overview

The internal architecture of the IHR is based on one section of control logic and two 4-bit-wide registers (masking and interrupt).

**Control Logic.** The control logic interfaces the masking and interrupt registers with the processor bus. The system software can read or write either the masking or interrupt register by accepting Addresses (A0), Chip Enable  $(\overline{E})$ , and Read/Write  $(R/\overline{W})$  signals, and can initialize the IHR with a Master Reset  $(\overline{MR})$  signal.

The Address line input (A0) addresses the desired register for a read or write operation. When A0 is a logic low, the input addresses the interrupt register. When A0 is a logic high, the input addresses the masking register.

The Chip Enable input  $(\overline{E})$  enables all IHR read and write operations via the data bus. A read or write operation may be performed only when  $\overline{E}$  is a logic low.

The Read/Write input  $(R/\overline{W})$  selects either a read or write operation for the register. A write operation occurs when  $R/\overline{W}$  is a logic low and a read occurs when it is a logic high.

The Master Reset input  $(\overline{MR})$  is an overriding clear input that initializes the IHR. As long as  $\overline{MR}$  is a logic low, all internal flip-flops are reset (low state). When the  $\overline{MR}$  low is removed, the masking register is in the "non-mask" condition and the interrupt register is in the "no-interrupt" condition. The state of the Chip Enable will not affect the operation of the Master Reset.

Masking Register. The 4-bit masking register inhibits one or more of the corresponding interrupt holding inputs (IHR0—IHR3). A logic high written to the masking register (via the data bus) inhibits an interrupt from setting the corresponding interrupt holding latch.

Interrupt Register. The 4-bit interrupt register contains the status of the four interrupt flip-flops. This register normally contains all zeros, indicating that no interrupt requests have occurred. The individual register flip-flops are set (made a logic high) by the presence of an external active low level at any one or all of the interrupt holding inputs (IHRO—IHR3), providing the corresponding masking register bit is a logic low. There is a one-to-one correspondence between the Interrupt Masking Register and the Interrupt Input Signals. The Interrupt Output (IO) and the Interrupt Input (II) lines are used for IHR cascading.

The Interrupt Output ( $\overline{IO}$ ) goes low if any of the four flip-flops of the interrupt register are set (high) or if the Interrupt Input ( $\overline{II}$ ) is set low. Chip Enable has no effect on the Interrupt Output, which is always enabled.

The Interrupt Input  $(\overline{II})$  is used to cascade IHRs. When  $\overline{II}$  is a logic high, the  $\overline{IO}$  line functions as previously described. When  $\overline{II}$  is a logic low, the  $\overline{IO}$  line goes low and stays low until  $\overline{II}$  is returned to a logic high.

Table 2. Truth Table

| Ē | MR | R/W | A0 | Device Function          |

|---|----|-----|----|--------------------------|

| 1 | ×  | X   | Х  | Device Inactive          |

| 0 | 0  | Х   | Х  | Reset IHR                |

| 0 | 1  | 1   | 0  | Read Interrupt Register  |

| 0 | 1  | 1   | 1  | Read Masking Register    |

| 0 | 1  | 0   | 0  | Write Interrupt Register |

| 0 | 1  | 0   | 1  | Write Masking Register   |

Note: X indicates a "don't care" condition (logic 1 or 0)

#### **Characteristics**

#### **Electrical Characteristics**

$TA = -40 \text{ to } +85 \text{ °C}, VCC = 5.0 \pm 0.5 \text{ V}$

| Parameter                                                                                                                                             | Symbol     | Min        | Max  | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------|------|

| Input Voltages Low Level High Level                                                                                                                   | VIL<br>VIH | 0.0<br>2.0 | 0.7  | V    |

| Input Clamp Diode Voltage<br>(VCC = 4.5 V, II = -5 mA)                                                                                                | Vıĸ        | _          | -1.5 | V    |

| Output Voltages (Data Input/Output, D0—D3) (Vcc = 4.5 V) Low Level (IoL = 8 mA) Low Level (IoL = 16 mA) High Level (IoH = $-800 \mu$ A)               | Vol        |            | 0.4  | V    |

|                                                                                                                                                       | Vol        |            | 0.5  | V    |

|                                                                                                                                                       | Voh        | 2.5        | —    | V    |

| Output Voltages (Interrupt Output, $\overline{\text{IO}}$ ) (Vcc = 4.5 V)  Low Level (IoL = 4 mA)  Low Level (IoL = 8 mA)  High Level (IoH = -400 μA) | Vol        |            | 0.4  | V    |

|                                                                                                                                                       | Vol        |            | 0.5  | V    |

|                                                                                                                                                       | Voh        | 2.5        |      | V    |

| Input Currents (VCC = 5.5 V)  Low Level (VI = 0.4 V)  High Level (VI = 2.7 V)  High Level (VI = 5.5 V)                                                | lil        | _          | 0.36 | mA   |

|                                                                                                                                                       | lih        | _          | 0.02 | mA   |

|                                                                                                                                                       | lih        | _          | 0.1  | mA   |

| Short-Circuit Output Current (VCC = 5.5 V)  Data Input/Output (D0—D3)  Interrupt Output (IO)                                                          | los        | -40        | -200 | mA   |

|                                                                                                                                                       | los        | -20        | -100 | mA   |

| Power Supply Current Drain (Vcc = 5.5 V)                                                                                                              | Icc        |            | 100  | mA   |

# 41KD Interrupt Holding Register

#### **Maximum Ratings**

| Power Supply Voltage (Vcc)       |       | 7.0 Vdc |

|----------------------------------|-------|---------|

| Input Voltage (VIH)              |       | 5.5 Vdc |

| Operating Temperature Range (TJ) | 25 to | +125 °C |

| Storage Temperature Range (Tstg) | 40 to | +125 °C |

Maximum ratings are defined as the limiting conditions that the user can apply to the device under all variations of circuit and environmental conditions. If any rating is exceeded, permanent damage to the device may result.

Bonding or soldering of the external leads of the devices can be performed safely at temperatures up to 300 °C.

#### **Timing Characteristics**

TA = 25 °C, CL = 15 pF, VCC = 5.0 V

| Parameters     | Description                | Min | Тур   | Max | Unit | Notes         |

|----------------|----------------------------|-----|-------|-----|------|---------------|

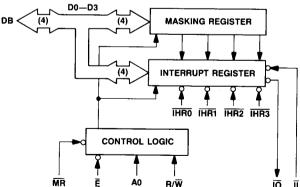

| tavel          | Address Set-Up Time        | 30  |       | _   | ns   | Figure 3      |

| trwhel         | Read/Write Set-Up Time     | 30  | _     | _   | ns   | Figure 3      |

| telov          | Data Bus On Time           | l — |       | 60  | ns   | Figures 3 & 5 |

| <b>t</b> avdv  | Register Access Time       | 40  | _     | _   | ns   | Figure 3      |

| tehdz          | Data Bus Off Time          | -   | _     | 60  | ns   | Figures 3 & 5 |

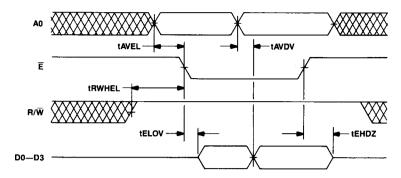

| taveh          | Address Set-Up Time        | 30  | _     | _   | ns   | Figure 4      |

| trwleh         | Read/Write Set-Up Time     | 30  | _     | _   | ns   | Figure 4      |

| teleh          | Write Pulse Width Time     | 100 | _     | _   | ns   | Figure 4      |

| toveh          | Data Set-Up Time           | 75  | _     | _   | ns   | Figure 4      |

| <b>t</b> EHDX  | Data Hold Time             | 0   | _     | -   | ns   | Figure 4      |

| tehrwh         | Read/Write Hold Time       | 15  | _     | _   | ns   | Figure 4      |

| <b>t</b> EHAX  | Address Hold Time          | 30  | ļ · _ | _   | ns   | Figure 4      |

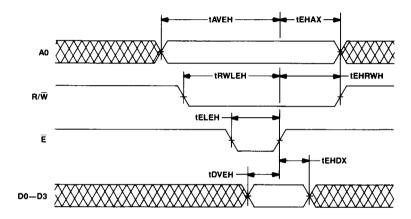

| tavrwh         | Address Set-Up Time        | 30  | _     | _   | ns   | Figure 5      |

| <b>t</b> ELRWH | Enable Set-Up Time         | 30  | _     | _   | ns   | Figure 5      |

| trwlwrh        | Write Pulse Width Time     | 100 | _     | _   | ns   | Figure 5      |

| trwldz         | Data Bus Off Time          | _   | _     | 60  | ns   | Figure 5      |

| tovrwh         | Data Set-Up Time           | 75  | _     | _   | ns   | Figure 5      |

| trwhdx         | Data Hold Time             | 0   | _     | _   | ns   | Figure 5      |

| trwhov         | Data Bus On Time           | _   |       | 60  | ns   | Figure 5      |

| trwheh         | Enable Hold Time           | 30  | _     | _   | ns   | Figure 5      |

| trwhax         | Address Hold Time          | 30  | _     | _   | ns   | Figure 5      |

| tipw           | Interrupt Pulse Width Time | 60  |       |     | ns   | IHR to Latch  |

| tiio           | Interrupt Response Time    | 75  | _     |     | ns   | IHR to IO     |

| tiio           | Interrupt Cascade Time     | 40  |       | _   | ns   | II to IO      |

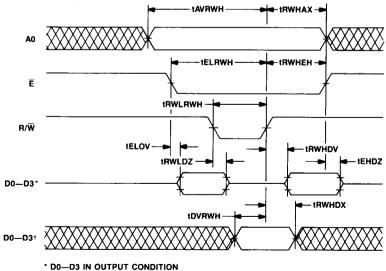

## **Timing Diagrams**

Figure 3. Read Cycle (R/W Used to Access Data)

Figure 4. Write Cycle (E Used to Write Data)

\* D0—D3 IN OUTPUT CONDITION \* D0—D3 IN INPUT CONDITION

Figure 5. Write Cycle (R/W Used to Write Data)

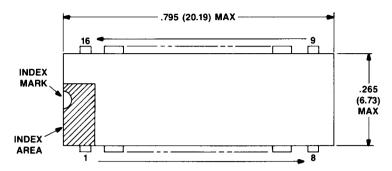

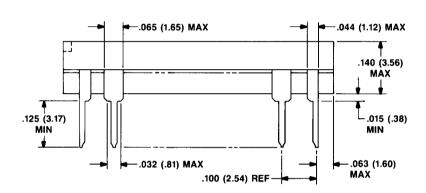

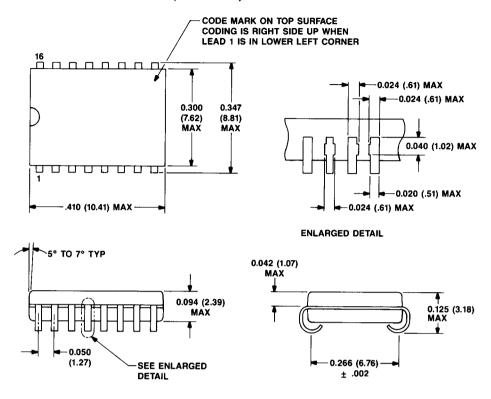

# **Outline Diagrams**

Dimensions in inches and (millimeters)

#### 16-Pin Plastic DIP

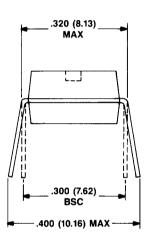

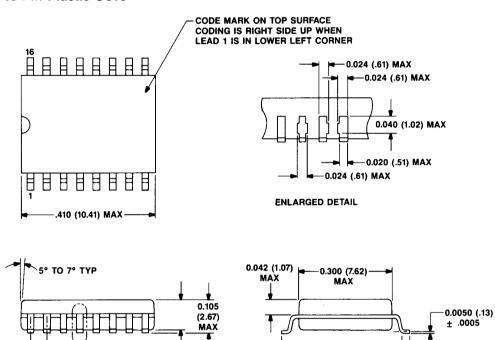

#### 16-Pin Plastic SOJ

#### Dimensions in inches and (millimeters)

# 41KD Interrupt Holding Register

#### 16-Pin Plastic SOIC

0.024 (.61) ± .003 -

0.406 (10.31) ± .002 -

## **Ordering Information**

0.050

(1.27)

| Device Code | Package             | Comcode   |

|-------------|---------------------|-----------|

| 41KD        | 16-Pin Plastic DIP  | 103257903 |

| 41KD-J      | 16-Pin Plastic SOJ  | 104450929 |

| 41KD-W      | 16-Pin Plastic SOIC | 104450937 |

0.094 (2.39)

SEE ENLARGED

DETAIL

For additional information, contact your AT&T Account Manager, or call:

☐ AT&T Microelectronics Dept. 51AL230230 555 Union Boulevard Allentown, PA 18103 1-800-372-2447

In Canada, call: 1-800-553-2448

- ☐ AT&T Microelectronics GmbH Freischützstrasse 92 D-8000 Munich 81 West Germany Tel. 0 89/95 97 0 Telex 5 216 884

- ☐ AT&T Microelectronics Pte. Ltd. 745 Lorong 5 Toa Payoh Singapore 1231 Tel. 259-6622 Telex RS42898 FAX 259-2244

- ☐ AT&T Japan

7F, Fukoku Seimei Bldg.,

2-2-2, Uchisaiwai-cho,

Chiyoda-ku, Tokyo 100 Japan

Tel. (03) 502-3055

Telex J32562 ATTIJ

FAX (03) 593-3307

AT&T reserves the right to make changes to the product(s) or circuit(s) described herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product or circuit.

Copyright © 1988 AT&T All Rights Reserved Printed in USA

June 1988

DS87-316DBIP

008185 1 2