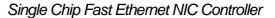

#### 1. General Description

The DM9102D is a fully integrated and cost effective single chip Fast Ethernet NIC controller. It is designed with low power and high performance process. It is a 2.5/3.3V device with 5V tolerance.

The DM9102D provides direct interface to the PCI bus and supports bus master mode to achieve the high performance of the PCI bus. It fully complies with PCI 2.2. In the media side, the DM9102D interfaces to the UTP3, 4, 5 in 10Base-T and the UTP5 in 100Base-TX. It is fully compliant with the IEEE 802.3u Spec. The auto-negotiation and auto-MDI/MDIX function can automatically configure the

DM9102D to take the maximum advantage of its abilities. The DM9102D also supports IEEE 802.3x's full-duplex flow control to prevent the receive overflow of link partner. The IPv4 IP/TCP/UDP checksum generation and checking can reduce the system CPU utilization.

The DM9102D supports two types of power management mechanisms. The main mechanism is based on the OnNow architecture, which is required for PC99. The alternative mechanism is based upon the remote Wake-On-LAN mechanism.

#### 2. Block Diagram

### **Table of Contents**

| 1. General Description                        | 1  | 6.2.13 Sample Frame                             |

|-----------------------------------------------|----|-------------------------------------------------|

| 0.01.1.0:                                     | •  | 6.2.14 Watchdog and                             |

| 2. Block Diagram                              | 3  | 0.0 DUDAN                                       |

| 2.5                                           |    | 6.3 PHY Managemen                               |

| 3. Features                                   | 4  | 6.3.1 Basic Mode Cor                            |

| 1 D. O. M                                     | _  | - Register 0                                    |

| 4 Pin Configuration: DM9102D 128pin LQFP      | 5  | 6.3.2 Basic Mode Stat                           |

|                                               |    | - Register 1                                    |

| 5. Pin Description                            |    | 6.3.3 PHY Identifier Ro                         |

| 5.1 PCI Bus Interface Signals                 |    | - Register 2                                    |

| 5.2 Boot ROM and EEPROM Interfaces            | 7  | 6.3.4 PHY Identifier Re                         |

| 5.3 LED Pins                                  | 8  | - Register 3                                    |

| 5.4 Network Interface                         | 8  | 6.3.5 Auto-negotiation                          |

| 5.5 Miscellaneous Pins                        | 8  | - Register 4                                    |

| 5.6 Power Pins                                | 9  | 6.3.6 Auto-negotiation                          |

| 5.7 NC Pins                                   | 10 | (ANLPAR) - Regis                                |

| 5.8 strap Pins                                | 10 | 6.3.7 Auto-negotiation                          |

| ·                                             |    | - Register 6                                    |

| 6. Register Definition                        | 11 | 6.3.8 DAVICOM Spec                              |

| 6.1 PCI Configuration Registers               |    | - Register 10H                                  |

| 6.1.1 Identification ID                       |    | 6.3.9 DAVICOM Spec                              |

| 6.1.2 Command & Status                        |    | Register (DSCSR) - R                            |

| 6.1.3 Revision ID                             |    | 6.3.10 10Base-T Conf                            |

| 6.1.4 Miscellaneous Function                  |    | - Register 12H                                  |

| 6.1.5 I/O Base Address                        |    | 6.3.11 Power Down C                             |

| 6.1.6 Memory Mapped Base Address              |    | - Register 13H                                  |

| 6.1.7 Subsystem Identification                | 16 | 6.3.12 Auto-MDI/MDI                             |

| 6.1.8 Expansion ROM Base Address              |    | - Register 14H                                  |

| 6.1.9 Capabilities Pointer                    |    | rtogiotor i ii i i i i i i i i i i i i i i i i  |

| 6.1.10 Interrupt & Latency Configuration      |    | 7. Functional Descripti                         |

| 6.1.11 Device Specific Configuration Register |    | 7.1 System Buffer Ma                            |

| 6.1.12 Power Management Register              |    | 7.1.1 Overview                                  |

| 6.1.13 Power Management Control/Status        |    | 7.1.2 Data Structure a                          |

| o.r. for ower management control otates       | 20 | Figure 7-1                                      |

| 6.2 Control and Status Register (CR)          | 21 | 7.1.3 Buffer Managem                            |

| 6.2.1 System Control Register (CR0)           |    | 7.1.4 Descriptor List: E                        |

| 6.2.2 Transmit Descriptor Poll Demand (CR1)   |    | 7.1.4 Descriptor List. L                        |

| 6.2.3 Receive Descriptor Poll Demand (CR2)    |    | 7.2 Initialization Proce                        |

| 6.2.4 Receive Descriptor Base Address (CR3)   | 22 | 7.2.1 Data Buffer Proc                          |

| 6.2.5 Transmit Descriptor Base Address (CR4)  |    | 7.2.1 Data Buller Floo<br>7.2.2 Receive Data Bu |

| 6.2.6 Network Status Report Register (CR5)    |    |                                                 |

|                                               |    | Figure 7-2                                      |

| 6.2.7 Network Operation Register (CR6)        |    | 7.2.3 Transmit Data B                           |

| 6.2.8 Interrupt Mask Register (CR7)           |    | Figure 7-3                                      |

| 6.2.9 Statistical Counter Register (CR8)      |    | 7.3 Network Function                            |

| 6.2.10 Management Access Register (CR9)       |    | 7.3.1 Overview                                  |

| 6.2.11 PHY Status Register (CR12)             |    | 7.3.2 Receive Process                           |

| 6.2.12 Sample Frame Access Register (CR13)    | 30 | 7.3.3 Transmit Proces                           |

| 6.2.13 Sample Frame Data Register (CR14)6.2.14 Watchdog and Jabber Timer Register (CR15) |     |

|------------------------------------------------------------------------------------------|-----|

| 6.3 PHY Management Register Set                                                          | .32 |

| - Register 0                                                                             | .33 |

| - Register 1                                                                             | .34 |

| - Register 2                                                                             | .35 |

| 6.3.4 PHY Identifier Register #2 (PHYIDR2) - Register 3                                  | .35 |

| 6.3.5 Auto-negotiation Advertisement Register (ANAR) - Register 4                        | .35 |

| 6.3.6 Auto-negotiation Link Partner Ability Register (ANLPAR) - Register 5               | .36 |

| 6.3.7 Auto-negotiation Expansion Register (ANER) - Register 6                            | .37 |

| 6.3.8 DAVICOM Specified Configuration Register (DSCI - Register 10H                      |     |

| 6.3.9 DAVICOM Specified Configuration and Status<br>Register (DSCSR) - Register 11H      |     |

| 6.3.10 10Base-T Configuration/Status (10BTSCRCSR) - Register 12H                         |     |

| 6.3.11 Power Down Control Register (PWDOR) - Register 13H                                | .40 |

| 6.3.12 Auto-MDI/MDIX ControlRegister (MDIX)                                              |     |

| - Register 14H                                                                           |     |

| 7. Functional Description                                                                |     |

| 7.1.1 Overview                                                                           | .41 |

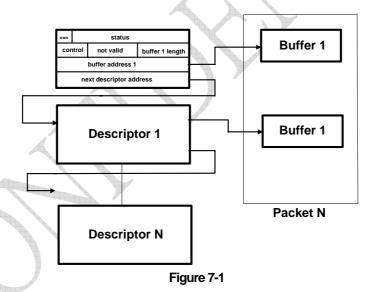

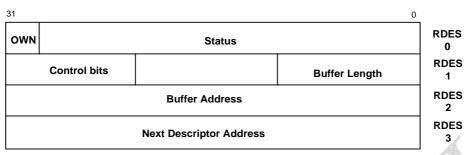

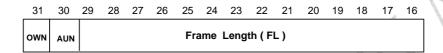

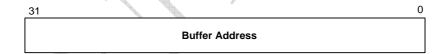

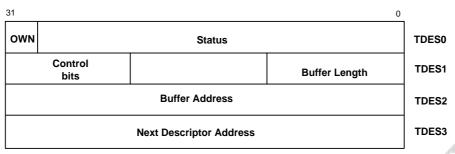

| 7.1.2 Data Structure and Descriptor List                                                 |     |

| Figure 7-1                                                                               |     |

| 7.1.3 Buffer Management: Chain Structure Method                                          |     |

| 7.1.4 Descriptor List: Buffer Descriptor Format                                          |     |

| 7.2 Initialization Procedure                                                             |     |

| 7.2.1 Data Buffer Processing Algorithm                                                   |     |

| 7.2.2 Receive Data Buffer Processing                                                     |     |

| Figure 7-27.2.3 Transmit Data Buffer Processing                                          |     |

| Figure 7-3                                                                               |     |

| 7.3 Network Function                                                                     |     |

| 7.3.1 Overview                                                                           |     |

| 7.3.2 Receive Process and State Machine                                                  |     |

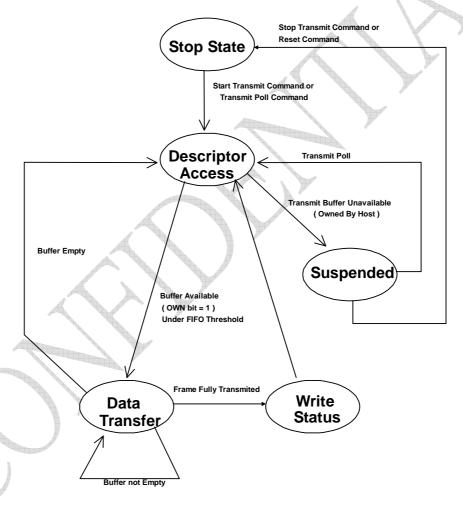

| 7.3.3 Transmit Process and State Machine                                                 | 48  |

# Single Chip Fast Ethernet NIC Controller

| 7.3.4 Physical Layer Overview                        | 48 |

|------------------------------------------------------|----|

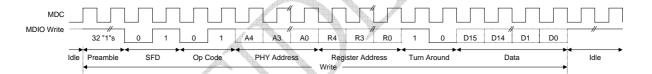

| 7.4 Serial Management Interface                      | 49 |

| 7.4.1 Management Interface - Read Frame Structure    | 49 |

| 7.4.2 Management Interface - Write Frame Structure   | 49 |

| 7.5 Power Management                                 | 51 |

| 7.5.1 Overview                                       |    |

| 7.5.2 PCI Function Power Management Status           | 51 |

| 7.5.3 The Power Management Operation                 |    |

| 7.6 Sample Frame Programming Guide                   | 53 |

| 7.7 EEPROM Overview                                  |    |

| 7.7.1 Subsystem ID                                   | 54 |

| 7.7.2 Vendor ID                                      | 54 |

| 7.7.3 Auto_ Load_ Control                            | 54 |

| 7.7.4 New_ Capabilities_ Enable                      | 54 |

| 7.7.5 PMC                                            | 54 |

| 7.7.6 Byte Offset (15)                               | 54 |

| 7.7.7 Ethernet Address                               |    |

| 7.7.8 Example of DM9102D EEPROM Format               | 55 |

| 7.8 External MII Interface                           | 56 |

| 7.8.1 The Sharing Pin Table                          | 56 |

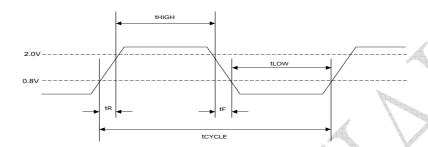

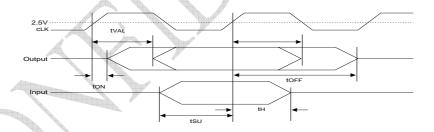

| 8. DC and AC Electrical Characteristics              | 57 |

| 8.1 Absolute Maximum Ratings( 25°C )                 | 57 |

| 8.2 Operating Conditions                             |    |

| 8.3 DC Electrical Characteristics                    |    |

| 8.4 AC Electrical Characteristics & Timing Waveforms |    |

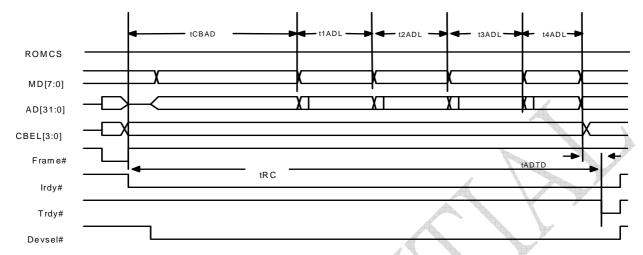

| 8.4.1 PCI Clock Specifications Timing                |    |

| 8.4.2 Other PCI Signals Timing Diagram               |    |

| 8.4.3 Boot ROM Timing                                | 60 |

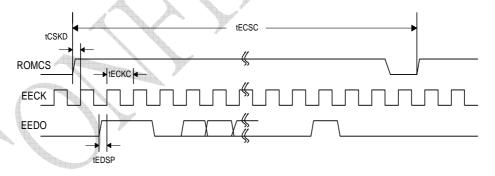

| 8 4 4 FFPROM Read Timing                             | 60 |

| 8.4.5 TP Interface61                                  |

|-------------------------------------------------------|

| 8.4.6 Oscillator/Crystal Timing61                     |

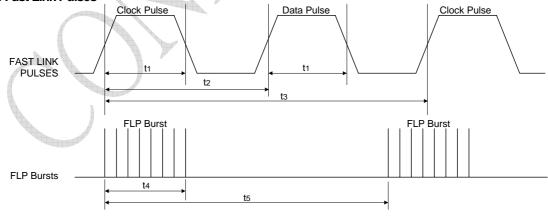

| 8.4.7 Auto-negotiation and Fast Link Pulse Timing     |

| Parameters61                                          |

| 8.4.8 Fast Link Pulses61                              |

|                                                       |

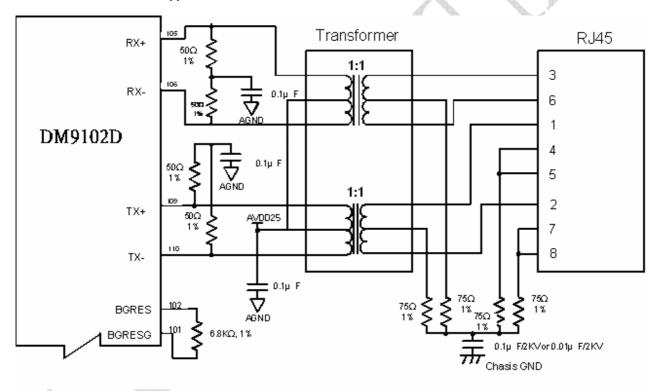

| 9. Application Notes                                  |

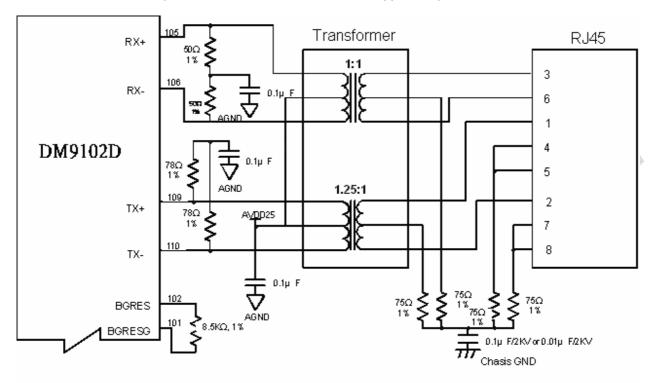

| 9.1 Network Interface Signal Routing62                |

| 9.2 10Base-T/100Base-TX Application Figure 9-162      |

| 9.3 10Base-T/100Base-TX (Power Reduction Application) |

| Figure 9-263                                          |

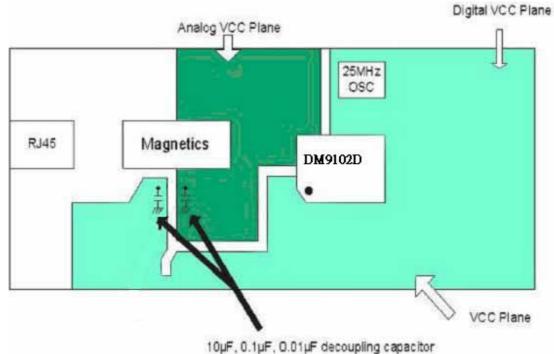

| 9.4 Power Supply Decoupling Capacitors Figure 9-364   |

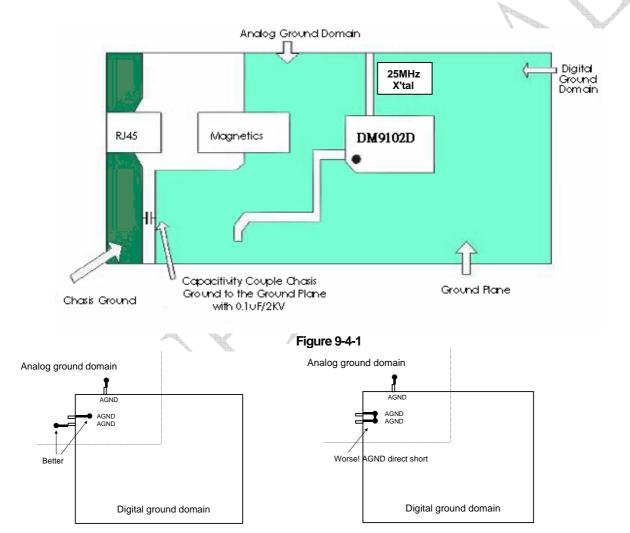

| 9.5 Ground Plane Layout                               |

| Figure 9-4-1 Figure 9-4-2 Figure 9-4-365              |

| 9.6 Power Plane Partitioning Figure 9-566             |

| 9.7 Magnetics Selection Guide                         |

| Table 9-1: 10/100M Magnetic Sources67                 |

| Table 9-2: Magnetic Specification Requirements67      |

| 9.8 Crystal Selection Guide                           |

| Table 9-3: Crystal Specifications68                   |

| Figure 9-6: Crystal Circuit Diagram68                 |

|                                                       |

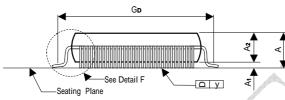

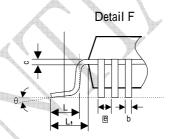

| 10 Package Information69                              |

| Package Information (128 pin, LQFP)69                 |

| 3 1 2 7 7 2 7                                         |

| 11 Ordering Information 70                            |

#### 3. Features

- Integrated Fast Ethernet MAC, Physical Layer and transceiver in one chip.

- 128 pin LQFP with CMOS process.

- +2.5/3.3V Power supply with +5V tolerant I/O.

- Comply with PCI specification 2.2.

- PCI bus master architecture.

- PCI bus burst mode data transfer.

- Two large independent transmission and receipt FIFO.

- Up to 256K bytes Boot EPROM or Flash interface.

- EEPROM 93C46 interface automatically supports node ID load and configuration information.

- Comply with IEEE 802.3u 100Base-TX and 802.3 10Base-T.

- Comply with IEEE 802.3u auto-negotiation protocol for automatic link type selection.

- Support IEEE 802.3x Full Duplex Flow Control.

- VLAN frame length support.

- IP/TCP/UDP checksum generation and checking.

- Zero copy supporting.

- Comply with ACPI and PCI Bus Power Management.

- Support the MII (Media Independent Interface) for an external PHY.

- Support Wake-On-LAN function and remote wake-up (Magic packet, Link Change and Microsoft<sup>®</sup> wake-up frame).

- Support 4 Wake-On-LAN (WOL) signals (active high pulse, active low pulse, active high, active low.)

- High performance 100Mbps clock generator and data recovery circuit.

- Digital clock recovery circuit, using advanced digital algorithm to reduce jitter.

- Adaptive equalization circuit and Baseline wandering restoration circuit for 100Mbps receiver.

- Provides Loopback mode for easy system diagnostics.

- Support auto-MDI/MDIX.

- Low power consumption modes:

- Power reduced mode (cable detection)

- Power down mode

- Selectable TX drivers for 1:1 or 1.25:1 transformers for additional power reduction. (1.25:1 transformers for Non Auto MDIX only).

Preliminary datasheet Version: DM9102D-DS-P02 Jan. 14, 2005

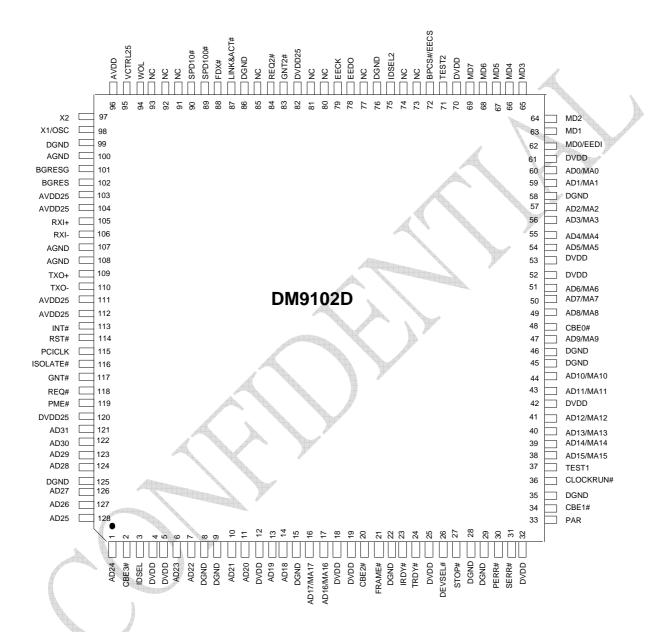

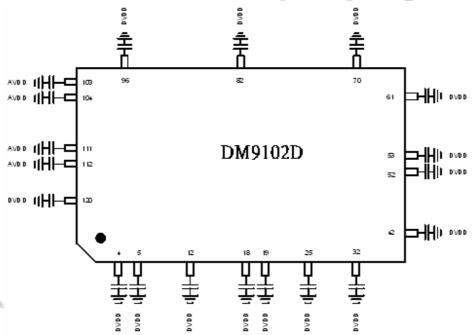

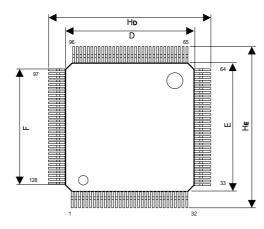

### 4. Pin Configuration: 128 pin LQFP

# 5. Pin Description

I = Input, O = Output, I/O = Input / Output, O/D = Open Drain, P = Power, # = asserted Low

5.1 PCI Bus Interface Signals

| Pin No. | Pin Name | I/O | Description                                                                                                                                                                                                                                                 |

|---------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 128LQFP |          |     |                                                                                                                                                                                                                                                             |

| 113     | INT#     | O/D | Interrupt Request This signal will be asserted low when an interrupted condition as defined in CR5 is set, and the corresponding mask bit in CR7 is et.                                                                                                     |

| 114     | RST#     | I   | System Reset When this signal is low, the DM9102D performs the internal system reset to its initial state.                                                                                                                                                  |

| 115     | PCICLK   | I   | PCI system clock PCI bus clock that provides timing for DM9102D related to PCI bus transactions.                                                                                                                                                            |

| 117     | GNT#     | I   | Bus Grant This signal is asserted low to indicate that DM9102D has been granted ownership of the bus by the central arbiter.                                                                                                                                |

| 118     | REQ#     | 0   | Bus Request The DM9102D will assert this signal low to request the ownership of the bus.                                                                                                                                                                    |

| 119     | PME#     | O/D | Power Management Event.  The DM9102D drives it low to indicates that a power management event has occurred.                                                                                                                                                 |

| 3       | IDSEL    | I   | Initialization Device Select This signal is asserted high during the Configuration Space read/write access.                                                                                                                                                 |

| 21      | FRAME#   | I/O | Cycle Frame This signal is driven low by the DM9102D master mode to indicate the beginning and duration of a bus transaction.                                                                                                                               |

| 23      | IRDY#    | I/O | Initiator Ready This signal is driven low when the master is ready to complete the current data phase of the transaction. A data phase is completed on any clock when both IRDY# and TRDY# are sampled asserted.                                            |

| 24      | TRDY#    | I/O | Target Ready This signal is driven low when the target is ready to complete the current data phase of the transaction. During a read, it indicates that valid data is asserted. During a write, it indicates that the target is prepared to accept data.    |

| 26      | DEVSEL#  | I/O | Device Select The DM9102D asserts the signal low when it recognizes its target address after FRAME# is asserted. As a bus master, the DM9102D will sample this signal which insures its destination address of the data transfer is recognized by a target. |

| 27      | STOP#    | I/O | Stop This signal is asserted low by the target device to request the                                                                                                                                                                                        |

|                           |           |           | master device to stop the current transaction.                  |

|---------------------------|-----------|-----------|-----------------------------------------------------------------|

| 30                        | PERR#     | I/O       | Parity Error                                                    |

|                           |           |           | The DM9102D as a master or slave will assert this signal low    |

|                           |           |           | to indicate a parity error on any incoming data.                |

| 31                        | SERR#     | I/O       | System Error                                                    |

|                           |           |           | This signal is asserted low when address parity is detected     |

|                           |           |           | with enabled PCICS bit31 (detected parity error.) The system    |

|                           |           |           | error asserts two clock cycles after the falling address if an  |

|                           |           |           | address parity error is detected.                               |

| 33                        | PAR       | I/O       | Parity                                                          |

|                           |           |           | This signal indicates even parity across AD0~AD31 and           |

|                           |           |           | C/BE0#~C/BE3# including the PAR pin. This signal is an          |

|                           |           |           | output for the master and an input for the slave device. It is  |

|                           |           |           | stable and valid one clock after the address phase.             |

| 2,20,34,48                | C/BE3#    | 1/0       | Bus Command/Byte Enable                                         |

|                           | C/BE2#    |           | During the address phase, these signals define the bus          |

|                           | C/BE1#    |           | command or the type of bus transaction that will take place.    |

|                           | C/BE0#    |           | During the data phase these pins indicate which byte lanes      |

|                           |           |           | contain valid data. C/BE0# applies to bit7-0 and C/BE3#         |

|                           |           |           | applies to bit31-24.                                            |

| 121,122,123,124,126,127,  | AD31~AD0/ | I/O       | Address & Data or Boot ROM Address                              |

| 128,1,6,7,10,11,13,14,16, | MA17~MA0  |           | These are multiplexed address and data bus signals. As a        |

| 17,38,39,40,41,43,44,47,  |           |           | bus master, the DM9102D will drive address during the first     |

| 49,50,51,54,55,56,57,59,  |           | A         | bus phase. During subsequent phases, the DM9102D will           |

| 60                        |           | 400000000 | either read or write data expecting the target to increment its |

|                           |           |           | address pointer. As a target, the DM9102D will decode each      |

|                           |           |           | address on the bus and respond if it is the target being        |

|                           |           |           | addressed.                                                      |

|                           |           |           | AD17~AD0 can also be used as boot ROM address                   |

|                           |           |           | MA17~MA0 when the boot ROM is accessed.                         |

#### 5.2 Boot ROM and EEPROM Interfaces

| Pin No.              | Pin Name   | 1/0 | Description                                                 |

|----------------------|------------|-----|-------------------------------------------------------------|

| 128LQFP              |            |     |                                                             |

| 62                   | MD0/EEDI   | I   | Boot ROM Data Input/EEPROM Data In                          |

|                      |            |     | This is a multiplexed pin used by EEDI and MD0.             |

|                      |            |     | When boot ROM is selected, it acts as boot ROM data input,  |

|                      |            |     | otherwise the DM9102D will read the contents of EEPROM      |

|                      |            |     | serially through this pin.                                  |

| 63,64,65,66,67,68,69 | MD1~MD7    | I   | Boot ROM Data Input Bus                                     |

| 72                   | BPCS#/EECS | 0   | Boot ROM (active low )or EEPROM Chip Selection.             |

| 78                   | EEDO       | 0   | EEPROM Data Out                                             |

|                      |            |     | This pin is used serially to write op-codes, addresses and  |

|                      |            |     | data into the EEPROM.                                       |

| 79                   | EECK       | 0   | EEPROM Serial Clock                                         |

|                      |            |     | This pin is used as the clock for the EEPROM data transfer. |

#### 5.3 LED Pins

| Pin No. | Pin Name  | VO  | Description                |

|---------|-----------|-----|----------------------------|

| 128LQFP |           |     |                            |

| 87      | LINK&ACT# | O/D | LED Output Pin, Active Low |

|    |         |     | mode 0 = Link and traffic LED. Active low to indicate normal link, and it will flash as a traffic LED when transmitting or receiving.  mode 1 = traffic LED only |

|----|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 88 | FDX#    | O/D | LED Output Pin, Active Low                                                                                                                                       |

|    |         |     | mode 0 = Full duplex LED<br>mode 1 = Full duplex LED                                                                                                             |

| 89 | SPD100# | O/D | LED Output Pin, Active Low                                                                                                                                       |

|    |         |     | mode 0 = 100Mbps LED                                                                                                                                             |

|    |         |     | mode 1 = 100Mbps LED                                                                                                                                             |

| 90 | SPD10#  | O/D | LED Output Pin, Active Low                                                                                                                                       |

|    |         |     | mode 0 = 10Mbps LED                                                                                                                                              |

|    |         |     | mode 1 = Link LED                                                                                                                                                |

#### 5.4 Network Interface

| Pin No. | Pin Name | VO | Description                                                   |

|---------|----------|----|---------------------------------------------------------------|

| 128LQFP |          |    |                                                               |

| 105,106 | RXI+     |    | 100M/10Mbps Differential Input Pair.                          |

|         | RX-      |    | These two pins are differential receive input pair for        |

|         |          |    | 100BASE-TX and 10BASE-T. They are capable of receiving        |

|         |          |    | 100BASE-TX MLT-3 or 10BASE-T Manchester encoded               |

|         |          |    | data.                                                         |

| 109,110 | TXO+     | 0  | 100M/10Mbps differential output pair.                         |

|         | TXO-     |    | These two pins are differential output pair for 100BASE-TX    |

|         |          |    | and 10BASE-T. This output pair provides controlled rising and |

|         |          |    | falling time, designed to filter the transmitter's output.    |

#### 5.5 Miscellaneous Pins

| Pin No. | Pin Name    | VO  | Description                                                                                                                                                                                                                                                                         |

|---------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 128LQFP |             | 1   |                                                                                                                                                                                                                                                                                     |

| 75      | IDSEL2      | 0   | PCI IDSEL 2.                                                                                                                                                                                                                                                                        |

|         |             |     | When this pin is pulled high, the PCI multiple function is present, and it act as PCI IDSEL2 function.                                                                                                                                                                              |

| 84      | REQ2#       | 0   | PCI Request 2                                                                                                                                                                                                                                                                       |

|         |             |     | If the PCI multiple function mode is selected, this pin act as the PCI REQ2# function.                                                                                                                                                                                              |

| 83      | GNT2#       | I   | PCI GNT2#                                                                                                                                                                                                                                                                           |

|         |             |     | If the PCI multiple function mode is selected, this pin act as GNT2# function.                                                                                                                                                                                                      |

|         | 7           |     | When this pin is pulled high, the DM9102D is in LED mode 1 otherwise the led mode 0 is selected.                                                                                                                                                                                    |

| 36      | CLOCKRUN#   | I/O | Clockrun#                                                                                                                                                                                                                                                                           |

| 30      | GLOCKINOIN# | 1/0 | The clockrun# signal is used by the system to pause or slow down the PCI clock signal. It is used by the DM9102D to enable or disable suspension or restart of the PCI clock. When the CLOCKRUN# pin is not used, this pin should be connected to an external pulled down resistor. |

| 71      | TEST2       | I   | TEST mode control 2                                                                                                                                                                                                                                                                 |

|         |             |     | In normal operation, tie high to this pin.                                                                                                                                                                                                                                          |

| 37  | TEST1    | I | TEST Mode Control 1                                               |

|-----|----------|---|-------------------------------------------------------------------|

|     |          |   | In normal operation, tie low to this pin.                         |

| 94  | WOL      | 0 | Wake up signal.                                                   |

|     |          |   | The DM9102D can assert this pin if it detects link status         |

|     |          |   | change, magic packet, or sample frame match. The default is       |

|     |          |   | low active pulse mode. The DM9102D also supports High/Low         |

|     |          |   | and Pulse/Level options from EEPROM setting.                      |

| 97  | X2       | 0 | Crystal feedback output                                           |

|     |          |   | This pin is used for crystal connection only. Leave this pin open |

|     |          |   | if oscillator is used.                                            |

| 98  | X1/OSC   | 1 | Crystal or Oscillator Input. (25MHz±50ppm)                        |

|     |          |   | Connect to a 25MHz Oscillator or series resonance,                |

|     |          |   | fundamental frequency crystal.                                    |

| 102 | BGRES    | 1 | Bandgap Voltage Reference Resistor.                               |

|     |          |   | It connects to a 6.8K 1% error tolerance resistor between this    |

|     |          |   | pin and BGRESG pin, to provide an accurate current reference      |

|     |          |   | for DM9102D (10Base-T/100Base-TX Application).                    |

| 116 | ISOLATE# | 1 | Isolate                                                           |

|     |          |   | This pin is used to isolate the DM9102D from the PCI bus.         |

|     |          |   |                                                                   |

|     |          |   |                                                                   |

| 95  | VCTRL25  | 0 | Voltage 2.5V control                                              |

|     |          | A | This pin can be used to control a BJT transistor 's base pin to   |

|     |          |   | generate a stable 2.5V power in BJT's drain pin .                 |

### 5.6 Power Pins

| J.O FOWEI FILIS           |          |     |                                         |

|---------------------------|----------|-----|-----------------------------------------|

| Pin No.                   | Pin Name | 1/0 | Description                             |

| 128LQFP                   |          |     |                                         |

| 101                       | BGRESG   | P   | Bandgap Ground                          |

|                           |          |     | It is used together with the BGRES pin. |

| 100,107,108               | AGND     | P   | Analog Ground                           |

| 103,104,111,112           | AVDD25   | P   | Analog Power, +2.5V                     |

| 96                        | AVDD     | Р   | Analog Power, +3.3V                     |

| 8,9,15,22,28,29,35,45,    | DGND     | Р   | Digital Ground                          |

| 46,58,76,86,99,125        |          |     |                                         |

| 82,120                    | DVDD25   | Р   | Digital Power, +2.5V                    |

| 4,5,12,18,19,25,32,42,52, | DVDD     | Р   | Digital Power, +3.3V                    |

| 53,61,70                  |          |     |                                         |

#### 5.7 NC Pins

10

| Pin No.<br>128LQFP             | Pin Name | VO | Description                                                           |

|--------------------------------|----------|----|-----------------------------------------------------------------------|

| 73,74,77,80,81,85,91,92,<br>93 | NC       | -  | These pins are unused in application and should let them unconnected. |

## 5.8 strap pins table

1: pull-high 1K~10K, 0: default floating.

| Pin No. | Pin Name   |                                  | Description |     |

|---------|------------|----------------------------------|-------------|-----|

| 72      | BPCS#/EECS | Disable Auto-MDIX                | A           |     |

|         |            | 1: auto-MDIX disabled            |             |     |

|         |            | 0: auto-MDIX enabled             |             |     |

| 75      | IDSEL2     | PCI multiple function            |             |     |

|         |            | 1: enable PCI multiple function  |             |     |

|         |            | 0: disable PCI multiple function |             | pr. |

| 83      | GNT2#      | LED mode                         | 1           |     |

|         |            | 1: LED mode 1                    |             | JP  |

|         |            | 0: LED mode 0                    |             |     |

### 6. Register Definition

#### **6.1 PCI Configuration Registers**

The definitions of PCI Configuration Registers are based on the PCI specification revision 2.2 and it provides the initialization and configuration information to operate the PCI interface in the DM9102D. All registers can be accessed with byte, word, or double word mode. As defined in PCI specification 2.1, read accesses to reserve or unimplemented registers will return a value of "0." These registers are to be described in the following sections.

The default value of PCI configuration registers after reset.

| Description                            | Identifier | Address Offset | Value of Reset         |

|----------------------------------------|------------|----------------|------------------------|

| Identification                         | PCIID      | 00H            | 91021282H              |

| Command & Status                       | PCICS      | 04H            | 02100000H*             |

| Revision                               | PCIRV      | 08H            | 02000050H              |

| Miscellaneous                          | PCILT      | 0CH            | BIOS determine         |

| I/O Base Address                       | PCIIO      | 10H            | System allocate        |

| Memory Base Address                    | PCIMEM     | 14H            | System allocate        |

| Reserved                               |            | 18H - 28H      | 0000000H               |

| Subsystem Identification               | PCISID     | 2CH            | load from EEPROM       |

| Expansion ROM Base Address             | PCIROM     | 30H            | 00000000H              |

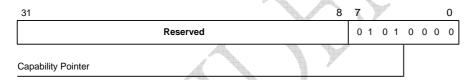

| Capability Pointer                     | CAP_PTR    | 34H            | 0000050H               |

| Reserved                               |            | 38H            | 00000000H              |

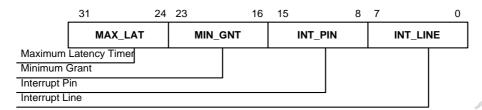

| Interrupt & Latency                    | PCIINT     | 3CH            | System allocate bit7~0 |

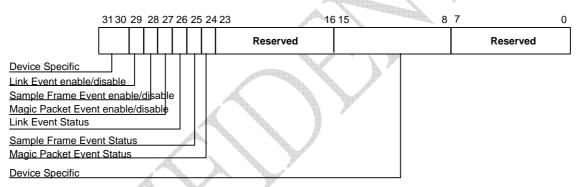

| Device Specific Configuration Register | PCIUSR     | 40H            | 0000000H**             |

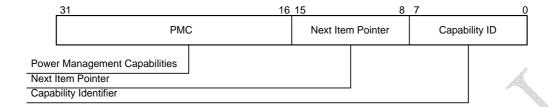

| Power Management Register              | PCIPMR     | 50H            | C0310001H**            |

| Power Management Control & Status      | PMCSR      | 54H            | 00000100H              |

<sup>\*</sup> It is written to 02100007H by most BIOS.

#### **Key to Default**

In the register description that follows, the default column takes the form <Reset Value>

Where:

<Reset Value>:

Bit set to logic oneBit set to logic zero

X No default value

<Access Type>:

RO = Read only

RW = Read/Write

R/C: means Read / Write & Write "1" for Clear.

<sup>\*\*</sup> It may be changed from EEPROM in application.

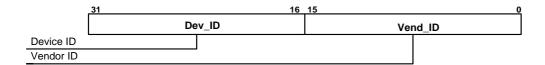

#### 6.1.1 Identification ID (xxxxxx00H - PCIID)

| Bit   | Default | Туре | Description                                                                                         |

|-------|---------|------|-----------------------------------------------------------------------------------------------------|

| 16:31 | 9102H   | RO   | The field identifies the particular device. Unique and fixed number for the DM9102D is 9102H.       |

| 0:15  | 1282H   | RO   | This field identifies the manufacturer of the device. Unique and fixed number for Davicom is 1282H. |

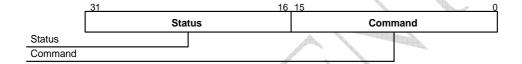

#### 6.1.2 Command & Status (xxxxxx04H - PCICS)

| ſ | Ri+ | Dofault | Tyne | Description |

|---|-----|---------|------|-------------|

| ı | Bit | Detault | rype | Description |

|       | Ì  | Ī   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | 0  | R/C | Detected Parity Error The DM9102D samples the AD[0:31], C/BE[0:3]#, and the PAR signal to check parity and to set parity errors. In slave mode, the parity check falls on command phase and data valid phase (IRDY# and TRDY# both active). In master mode, the DM9102D will check each data phase, during a memory read cycle, for parity error. During a memory write cycle, if an error occurs, the PERR# signal will be driven by the target. This bit is set by the DM9102D and cleared by writing "1". There is no effect by writing "0" |

|       |    | 5.0 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 30    | 0  | R/C | Signal For System Error This bit is set when the SERR# signal is driven by the DM9102D. This system error occurs when an address parity is detected under the condition that bit 8 and bit 6 in command register below are set                                                                                                                                                                                                                                                                                                                 |

| 29    | 0  | R/C | Master Abort Detected This bit is set when the DM9102D terminates a master cycle with the master-abort bus transaction                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 28    | 0  | R/C | Target Abort Detected This bit is set when the DM9102D terminates a master cycle due to a target-abort signal from other targets                                                                                                                                                                                                                                                                                                                                                                                                               |

| 27    | 0  | R/C | Send Target Abort (0 for No Implementation) The DM9102D will never assert the target-abort sequence                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 26:25 | 01 | R/C | DEVSEL Timing (01 Select Medium Timing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 20.20 | 01 | 100 | Medium timing of DEVSEL# means the DM9102D will assert DEVSEL#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |    |     | signal two clocks after FRAME# is sample "asserted"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 24    | 0  | R/C | Data Parity Error Detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | -  |     | This bit will take effect only when operating as a master and when a Parity Error Response Bit in command configuration register is set. It is set under two conditions:  (i) PERR# asserted by the DM9102D in memory data read error  (ii) PERR# sent from the target due to memory data write error                                                                                                                                                                                                                                          |

| 23    | 0  | RO  | Slave Mode Fast Back-To-Back Capable (0 for No Support)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 20    |    |     | This bit is always reads "1" to indicate that the DM9102D is capable of accepting fast back-to-back transaction as a slave mode device                                                                                                                                                                                                                                                                                                                                                                                                         |

| 22    | 0  | RO  | User-Definable Feature Supported (0 for No Support)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 21    | 0  | RO  | 66 MHz (0 for No Capability)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 20    | 1  | RO  | New Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |    |     | This bit indicates whether this function implements a list of extended capabilities such as PCI power management. This bit may be updated by EEPROM. When set this bit indicates the presence of New Capability. A                                                                                                                                                                                                                                                                                                                             |

|       |    |     | value of 0 means that this function does not implement New Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 19:10 | 0  | RO  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9     | 0  | RO  | Master Mode Fast Back-To-Back (0 for No Support)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |    |     | The DM9102D does not support master mode fast back-to-back                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       |    |     | capability and will not generate fast back-to-back cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8     | 0  | RW  | SERR# Driver Enable/Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |    |     | This bit controls the assertion of SERR# signal output. The SERR# output                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |    |     | will be asserted on detection of an address parity error and if both this bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |    |     | and bit 6 are set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7     | 0  | RO  | Address/Data Stepping (0 for No Stepping)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6     | 0  | RW  | Parity Error Response Enable/Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |    |     | Setting this bit will enable the DM9102D to assert PERR# on the detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |   |    | of a data parity error and to assert SERR# for reporting address parity error                                                                                                                                                                                                                                                                                                  |

|---|---|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 | 0 | RO | VGA Palette Snooping (0 for No Support)                                                                                                                                                                                                                                                                                                                                        |

| 4 | 0 | RO | Memory Write and Invalid (0 for No Implementation) The DM9102D only generates memory write cycle                                                                                                                                                                                                                                                                               |

| 3 | 0 | RO | Special Cycles (0 for No Implementation)                                                                                                                                                                                                                                                                                                                                       |

| 2 | 1 | RW | Master Device Capability Enable/Disable When this bit is set, DM9102D has the ability of master mode operation                                                                                                                                                                                                                                                                 |

| 1 | 1 | RW | Memory Space Access Enable/Disable This bit controls the ability of memory space access. The memory access includes memory mapped I/O access and Boot ROM access. As the system boots up, this bit will be enabled by BIOS for Boot ROM memory access. While in normal operation, using memory mapped I/O access, this bit should be set by driver before memory access cycles |

| 0 | 1 | RW | I/O Space Access Enable/Disable This bit controls the ability of I/O space access. It will be set by BIOS after power on                                                                                                                                                                                                                                                       |

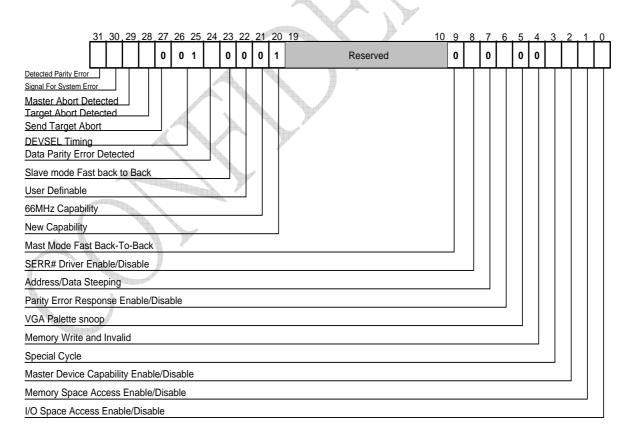

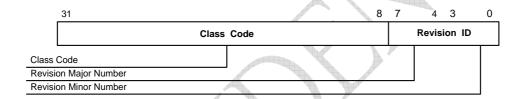

## 6.1.3 Revision ID (xxxxxx08H - PCIRV)

14

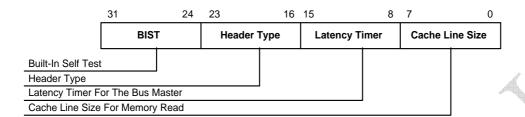

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Default | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Description                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 31:8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 020000H | RO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Class Code (020000H)                                                            |

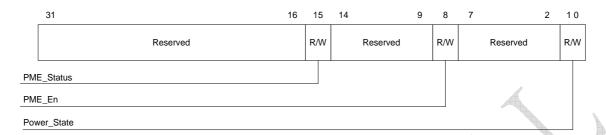

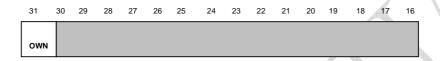

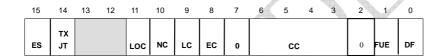

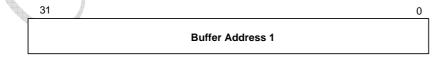

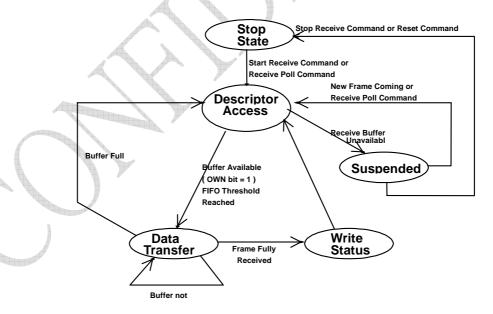

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .al     | The state of the s | This is the standard code for Ethernet LAN controller                           |