# TSC692E Floating Point Unit

User's Manual

for Embedded Real time 32–bit Computer (ERC32)

for SPACE Applications

# **Table of Contents**

| 1. Introduction                                      |    |

|------------------------------------------------------|----|

| 1.1. Scope                                           |    |

| 2. TSC692E Overview                                  | 1  |

| 2.1. SPARC RISC Standard Functions:                  |    |

| 2.2. Fault Tolerant and Test MECHANISM Improvements: |    |

| 2.3. Presentation of the ERC32                       |    |

| Concept                                              |    |

| Functional Description                               |    |

| 3. Standard TSC692E Functions                        | 2  |

| 3.1. TSC692E Functional Description                  |    |

| 3.2. Floating–Point/Integer Unit Interface           |    |

| 3.2.1. TSC692E RT Instruction Fetch and Execution    |    |

| 3.2.1.1 Instruction Fetch                            |    |

| 3.2.1.2. Instruction Execution                       |    |

| 3.2.1.2.1 Instruction Execution                      |    |

| 3.2.1.2.2. FPop Queuing                              |    |

| 3.2.2. Instruction Pipeline Flush                    |    |

| 3.2.2.1. Hold Signals                                |    |

| 3.2.2.2. Interlocking with FHOLD                     |    |

| 3.2.2.3. FNULL Signal                                |    |

| 3.3. TSC692E Programming Model                       |    |

| 3.3.1. TSC692E Registers                             |    |

| 3.3.1.1 f Registers                                  |    |

| 3.3.1.2. FP Queue                                    |    |

| 3.3.1.3. Floating–Point Status Register (FSR)        |    |

| 3.3.2. TSC692E Floating–Point Instructions           |    |

| 3.3.3. TSC692E Internal Operation                    |    |

| 3.3.3.1. Exception Handling                          |    |

| 3.3.4. TSC692E IEEE–754 Compliance                   |    |

| 3.3.4.1 IEEE Definitions                             |    |

| 3.3.4.2. IEEE Floating—point Data Formats            |    |

| 3.3.4.2.1 Single–Precision Floating–Point            |    |

| 3.3.4.2.2. Double–Precision Floating–Point           |    |

| 3.3.5. NaN Format                                    |    |

| 3.3.6. TSC692E Exception Cases                       |    |

| 3.4. TSC692E Signal Descriptions                     |    |

| 3.4.1. Integer Unit Interface Signals                |    |

| 3.4.2. Coprocessor Interface Signals                 |    |

| 3.4.3. System/Memory Interface Signals               |    |

| 3.4.4. TAP signals                                   |    |

| 3.4.5. Power and Clock Signals                       |    |

| 5.4.3. I Owel allu Clock Signals                     | 2  |

| 4. Fault Tolerant and Test MECHANISM                 | 30 |

| 4.1. Fault Tolerant and Test Support Signals         |    |

|                                                      |    |

|     | 4.1.1. Parity Checking                                        | 30 |

|-----|---------------------------------------------------------------|----|

|     | 4.1.2. Master/Checker Mode                                    | 31 |

|     | 4.1.3. Test Access Port                                       | 31 |

|     | 4.1.4. Miscellaneous                                          | 31 |

| 4.2 | Parity Checking                                               | 31 |

|     | 4.2.1. Introduction                                           | 31 |

|     | 4.2.2. Error handling scheme in TSC692E                       | 31 |

|     | 4.2.3. Parity Checking on Control Pads for the FPU            | 32 |

|     | 4.2.3.1. Input control signals                                | 32 |

|     | 4.2.3.1.1. Output control signals                             | 32 |

|     | 4.2.4. Parity Checking on address bus                         | 32 |

|     | 4.2.5. Parity Checking on data bus                            | 32 |

|     | 4.2.6. Internal Parity Checking                               | 32 |

|     | 4.2.7.Non RT 602 Mode                                         | 32 |

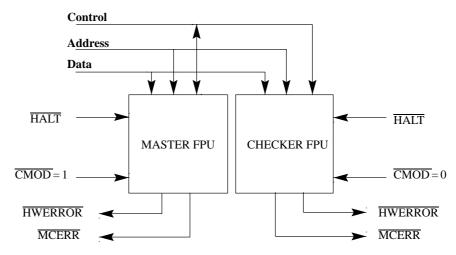

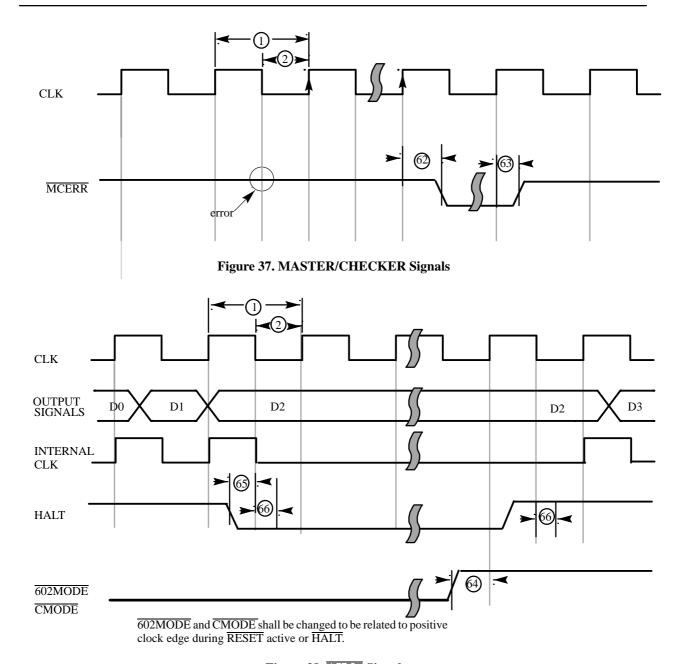

| 4.3 | Master/checker Operation                                      | 34 |

|     | 4.3.1. Basic function                                         | 35 |

|     | 4.3.2. Master/Checker signals                                 | 35 |

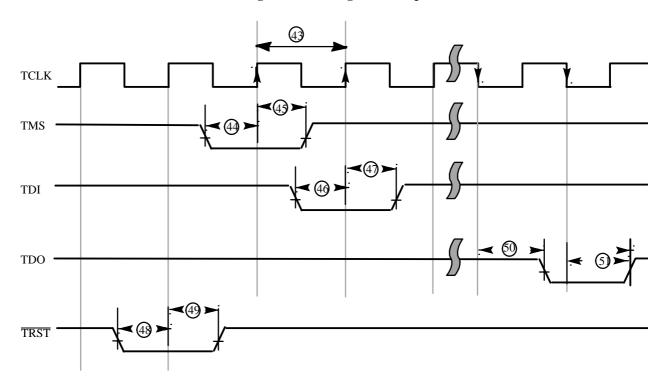

| 4.4 | . IEEE Standard Test Access Port & Boundary-Scan Architecture | 36 |

|     | 4.4.1. TAP signals                                            | 36 |

|     | 4.4.2. TAP Controller                                         | 36 |

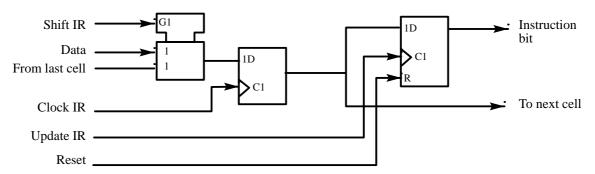

|     | 4.4.3. The Instruction Register                               | 36 |

|     | 4.4.3.1. Design and Construction of the instruction register  | 37 |

|     | 4.4.3.2. BYPASS Instruction                                   | 37 |

|     | 4.4.3.3. EXTEST Instruction                                   | 37 |

|     | 4.4.3.4. INTEST Instruction                                   | 37 |

|     | 4.4.3.5. SAMPLE/PRELOAD Instruction                           | 37 |

|     | 4.4.4. The Device Identification Register                     | 38 |

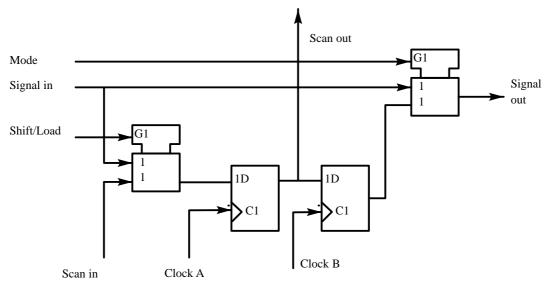

|     | 4.4.5. Internal Scan Path                                     |    |

|     | Boundary scan test register                                   |    |

| 4.6 | Parity on odd and even bits of the register file bits         | 38 |

| _ 1 |                                                               | 20 |

|     | Electrical and Mechanical Specifications                      |    |

|     | . TSC692E Maximum Ratings and DC Characteristics              |    |

|     | 5.1.1. TSC692E Maximum Rating                                 |    |

|     | 5.1.2. TSC692E Operating Range                                |    |

|     | 5.1.3. TSC692E DC Characteristics Over the Operating Range    |    |

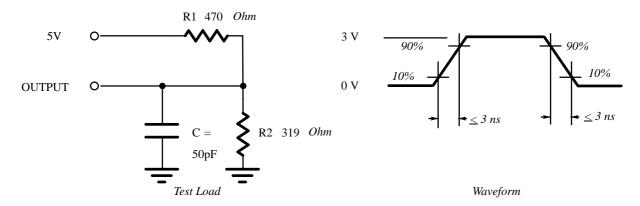

|     | 5.1.4. TSC692E AC Test Loads and Waveforms                    |    |

|     | TSC692E AC Characteristics                                    |    |

|     | 5.2.1. TSC692E AC Waveforms                                   |    |

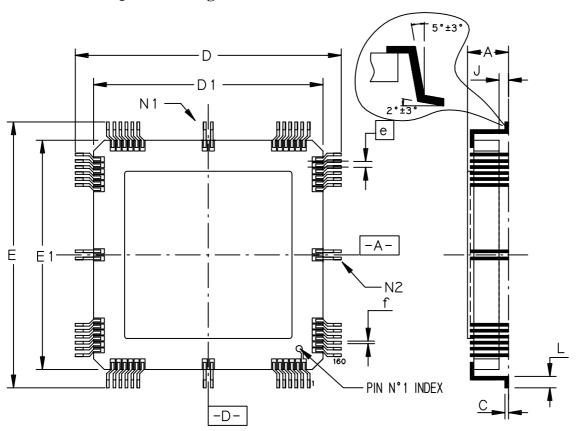

|     | . TSC692E Package Descriptions                                |    |

|     | 5.3.1. 160-Pin MQFP-L Package                                 |    |

|     | 5.3.2. 160-Pin MQFP-L Pin Assignment                          | 51 |

toc2 Rev. H (02 Dec.96)

# **List of Tables**

| Fable 1. Load instruction execution                             | 8  |

|-----------------------------------------------------------------|----|

| Table 2. Store instruction execution                            | 8  |

| Table 3. FPop execution                                         | 8  |

| Table 4. FHOLD Resource/Operand Dependency Cases                | 14 |

| Fable 5. Floating–Point Status Register Summary                 | 17 |

| Fable 6. Floating–Point Load and Store Instruction Cycle Count  | 19 |

| Fable 7. Floating–Point Operate (FPops) Instruction Cycle Count | 20 |

| Table 8. Untrapped FP result in same format as operand          | 24 |

| Table 9. Untrapped FP result in different format                | 24 |

| Table 10. FCC[1:0] Condition Codes                              | 26 |

| Fable 11. priority within traps                                 | 32 |

| Table 12. Instruction Register Encoding                         | 37 |

| Fable 13. TSC692E Operating Range                               | 39 |

| Table 14. TSC692E DC Characteristics over the operating range   | 39 |

| Fable 15. TSC692E Capacitance Ratings [1]                       | 39 |

| Table 16 TSC692E Characteristics at 14/25 MHz                   | 40 |

# **List of Figures**

| ERC32 Architecture                                          |    |

|-------------------------------------------------------------|----|

| Figure 1. TSC692E Functional Block Diagram                  |    |

| Figure 2. TSC692E Block Diagram (without parity checking)   | 6  |

| Figure 3. TSC692E Hardware Interface                        |    |

| Figure 4. Instruction Fetch (Cache Hit)                     |    |

| Figure 5. Floating–Point Instruction Dispatching            |    |

| Figure 6. Floating–Point Compare (FCMP) Execution           |    |

| Figure 7. Floating–Point Instruction Pipeline During A Trap |    |

| Figure 8. Effect of FLUSH on LDF Instruction                |    |

| Figure 9. Effect of FLUSH on STF Instruction                |    |

| Figure 10. Effect of FLUSH on FPop Instruction              |    |

| Figure 11. Effect of FLUSH on FCMP Instruction              |    |

| Figure 12. f Register Organization                          |    |

| Figure 13. f Register Addressing                            |    |

| Figure 14. Floating–Point Status Register                   |    |

| Figure 15. FPU Operation Modes                              |    |

| Figure 16. Floating–Point Exception Handshake               |    |

| Figure 17. Single–Precision Floating–Point Format           |    |

| Figure 18. Double–Precision Floating–Point Format           |    |

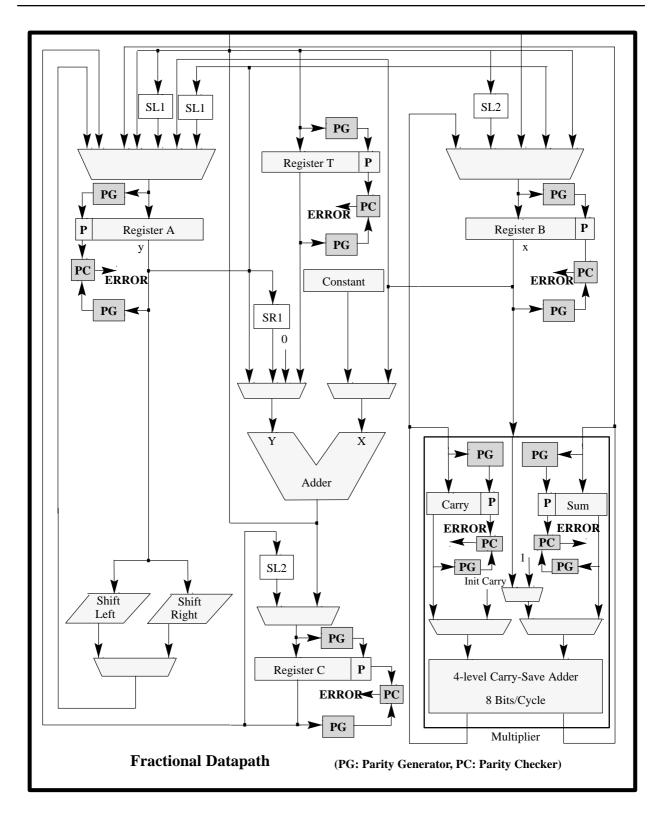

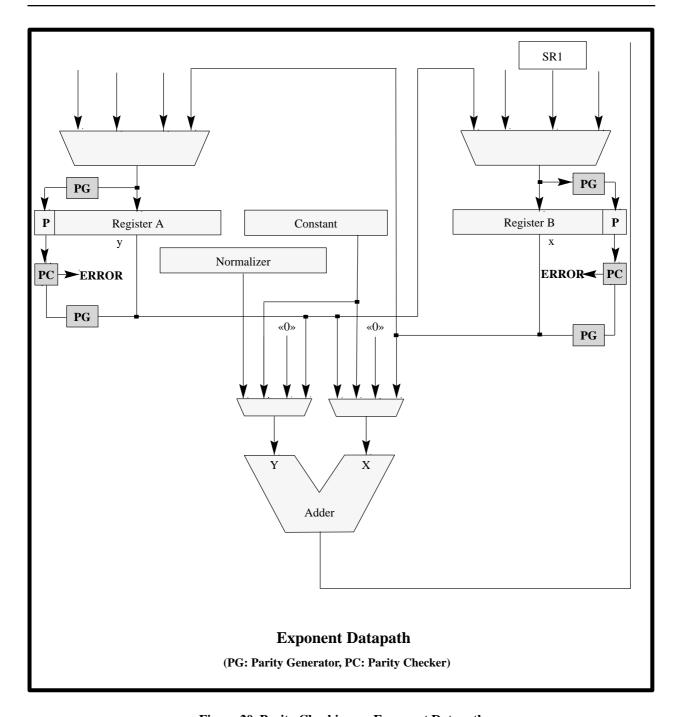

| Figure 19. Parity Checking on Fractional Datapath           |    |

| Figure 20. Parity Checking on Exponent Datapath             |    |

| Figure 21. Master/Checker configuration                     |    |

| Figure 22. Instruction Register Cell                        |    |

| Figure 23. Boundary Scan Cell                               |    |

| Figure 24. TSC692E AC Test Loads and Waveforms              | 40 |

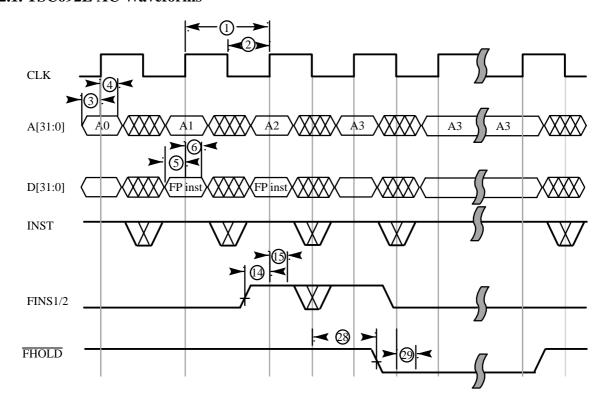

| Figure 25. Floating–Point FHOLD Assertion                   |    |

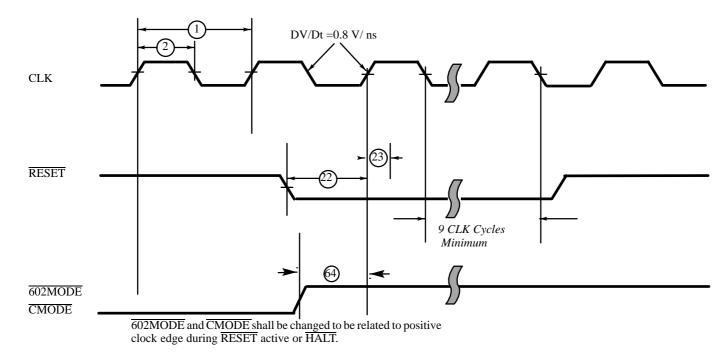

| Figure 26. Clock and RESET Timing                           | 43 |

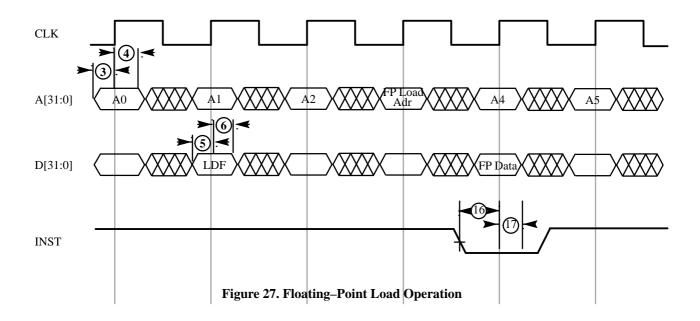

| Figure 27. Floating–Point Load Operation                    |    |

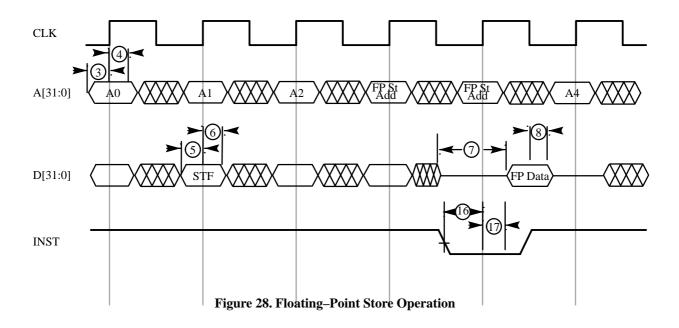

| Figure 28. Floating–Point Store Operation                   |    |

| Figure 29. Effect of FLUSH on Store Timing                  |    |

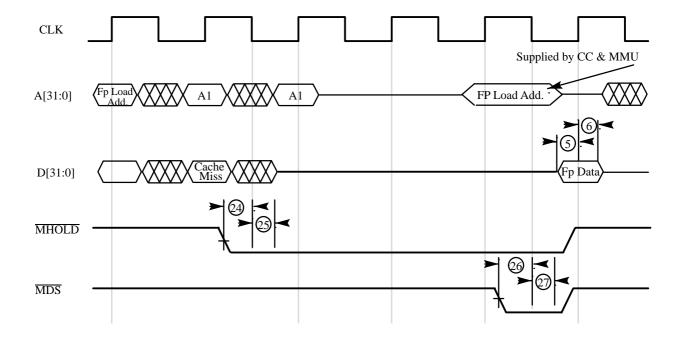

| Figure 30. Floating–Point Load Cache Miss                   |    |

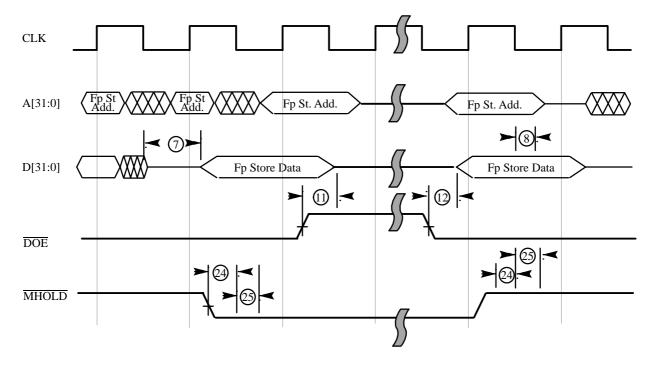

| Figure 31. Floating–Point Store Cache Miss                  |    |

| Figure 32. Floating–Point Compare                           |    |

| Figure 33. Floating–Point Trap                              |    |

| Figure 34. TAP Signals                                      |    |

| Figure 35. HWERROR Timing                                   | 48 |

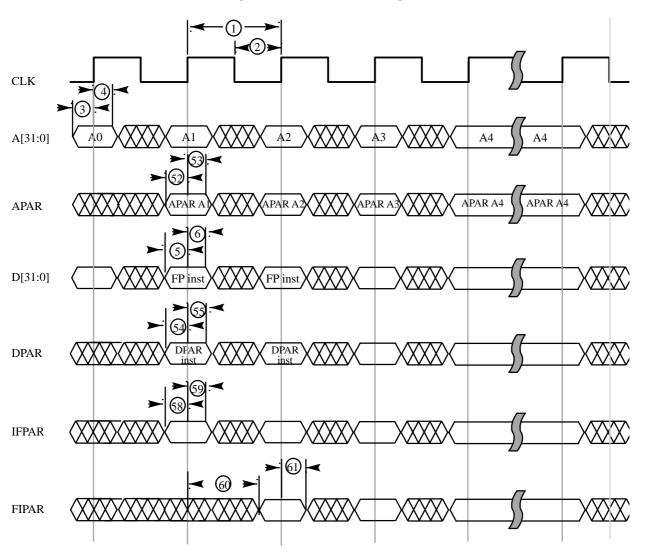

| Figure 36. PARITY Signals                                   |    |

| Figure 37. MASTER/CHECKER Signals                           | 49 |

| Figure 38. HALT Signal                                      | 49 |

# **TSC692E Floating Point Unit**

### 1. Introduction

## **1.1. Scope**

This document presents a preliminary datasheet of the TSC692E RT Floating Point Unit device specification. It is organized in three chapters:

- Standard FPU (TSC692E) Functions (Chapter 3)

- Fault MECHANISM and Test MECHANISM (Chapter 4)

- Electrical and Mechanical Specification (Chapter 5)

Chapter 3 presents standard functions including some adaptations due to the introduction of fault tolerance MECHANISM. Without losing the full binary compatibility with the entire SPARC V7.0 application software base.

Chapter 4 and 5 deal with the new added functions introduced in the TSC692E to improve the reliability of space applications. These new functions do not impact the SPARC V7.0 compatibility.

### 2. TSC692E Overview

#### 2.1. SPARC RISC Standard Functions:

- Full compatibility with Standard ANSI/IEEE 754-1985 for binary Floating Point Arithmetic

- 64-bit Internal Datapath

- Based on Floating-Point Unit from SUN

- Tightly coupled Integer-Unit interface

#### 2.2. Fault Tolerant and Test MECHANISM Improvements:

- Parity checking on 98% of the total number of latches with hardware error traps

- Parity checking of address, data pads and IU/FPU control pads

- Master/Checker operation

- IEEE Standard Test Access Port & Boundary-Scan Architecture

- Possibility to disable the bus parity checking

- Manufactured using Atmel Wireless & Microcontrollers Space hardened 0.8 μm SCMOS-RT technology

- Part of the ERC32 high performance 32-bit computing core

To support applications requiring an extremely high level of reliability, the following improvements were introduced in the standard SPARC RISC FPU TSC692E:

- Several independent fault detection MECHANISMs to support the design of fault tolerant system like parity checking and master/checker operations.

- Support of sophisticated PC board level tests applicating the IEEE Standard Test Access Port and Boundary Scan Architecture.

- Hardening of the process by construction, using restricted full static CMOS design rules for all critical blocks of the circuit such as register file, ROMs, BUSSES etc...

• Hardened device processing using the 0.8 μm SCMOS-RT TECHNOLOGY.

Thanks to careful handling of the improvements, the introduced modifications have neither reduced the performance of the device nor changed the full binary compatibility with the entire SPARC V7.0 application software. Improvements in FPU design have decreased the power consumption.

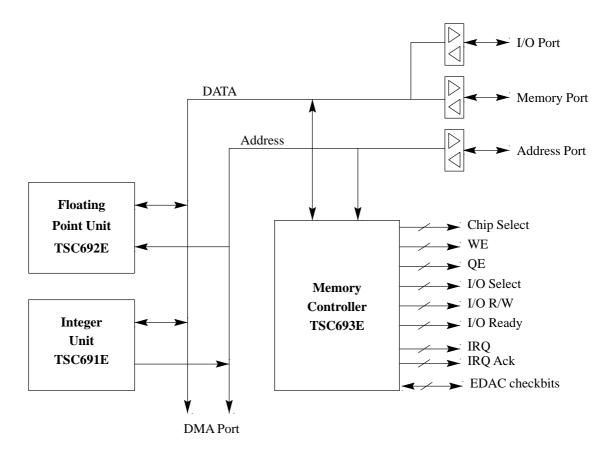

#### 2.3. Presentation of the ERC32

The TSC692E Floating Point Unit is, with the TSC691E Integer Unit and the TSC693E (Memory Controller), a part of the ERC32 Computing Core.

#### Concept

The objective of the ERC32 is to provide a high performance 32-bit computing core, with which computers for on-board embedded real-time applications can be built. The core will be characterized by low circuit complexity and power consumption. Extensive concurrent error detection and support for fault tolerance and reconfiguration will also be emphasized.

In addition to the main objective the ERC32 core will be possible to use for performance demanding research applications in deep space probes. The radiation tolerance and error masking are therefore important. For the real-time applications the system might be fail-operational rather than fail-safe. By including support for reconfiguration of the error-handling the different demands from the applications can be optimized for the best purpose in each case.

The ERC32 will be used as a building block only requiring memory and application specific peripherals to be added to form a complete on-board computer. All other system support functions will be provided by the core.

#### **Functional Description**

The ERC32 will incorporate the followings functions:

- Processor, which consists of one integer unit and one floating point unit. The processor includes concurrent error detection facilities.

- Memory controller (TSC693E), which is a unit consisting of all necessary support functions such as memory

control and protection, EDAC, wait state generator, timers, interrupt handler, watch dog, UARTs and test and

debug support. The unit also includes concurrent error detection facilities.

- Oscillator (optional).

- Buffers necessary to interface with memory and peripherals.

Next figure schematically shows the ERC32 architecture and external functions added to form a complete system.

**ERC32 Architecture**

# 3. Standard TSC692E Functions

The TSC692E Floating—Point Unit (FPU) is a high—performance, single—chip implementation of the SPARC reference floating—point unit. The TSC692E FPU is designed to provide execution of single and double—precision floating—point instructions concurrently with execution of integer instructions by the TSC691E Integer Unit (IU). The TSC692E is compliant to the ANSI/IEEE-754 (1985) floating—point standard.

The TSC692E provides a 64-bit Fractional/Exponent/Sign internal datapath for efficient execution of double-precision floating-point instructions. All implemented instructions are executed within hardware. For efficient data management, the TSC692E provides thirty-two 32-bit floating-point registers. These 32-bit registers can be concatenated for use as 64-bit registers for double-precision operations. The internal 64-bit architecture of the TSC692E allows high speed execution of both single- and double-precision operations.

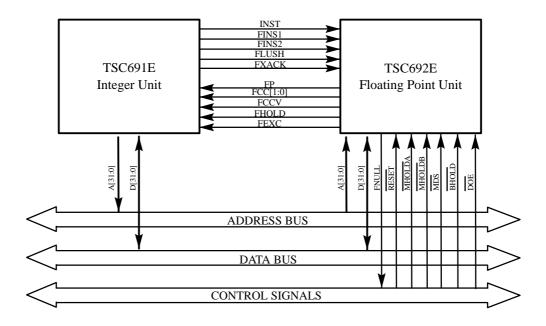

The SPARC floating-point/integer unit interface supports concurrent execution of integer and floating-point instructions. The tightly coupled floating-point/integer unit interface requires the integer unit to provide all addressing and control signals for memory access. All instructions are fetched by the integer unit, and these instructions are simultaneously latched and decoded by both the TSC691E and TSC692E. Execution of a floating-point instruction is enabled by TSC691E, which signals the TSC692E to begin execution of the floating-point instruction when that instruction reaches the execute stage of the TSC691E instruction pipeline. In the case of a floating-point load or store instruction, the TSC691E executes the FP load or store in conjunction with the TSC692E by asserting address and control signals for memory access while the TSC692E loads or stores the data. All other floating-point instructions execute independently of the integer unit and in parallel with integer instruction execution.

The floating-point/integer unit interface provides hardware interlocking to ensure synchronization between the TSC691E and TSC692E. Hardware interlocking ensures software compatibility among SPARC systems with different levels of floating-point performance.

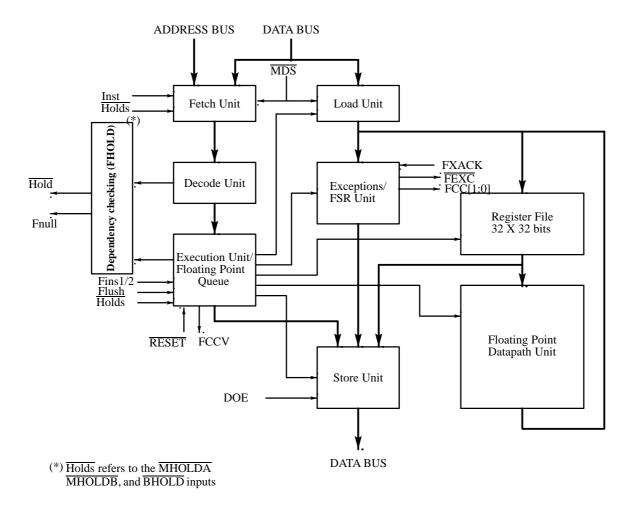

## 3.1. TSC692E Functional Description

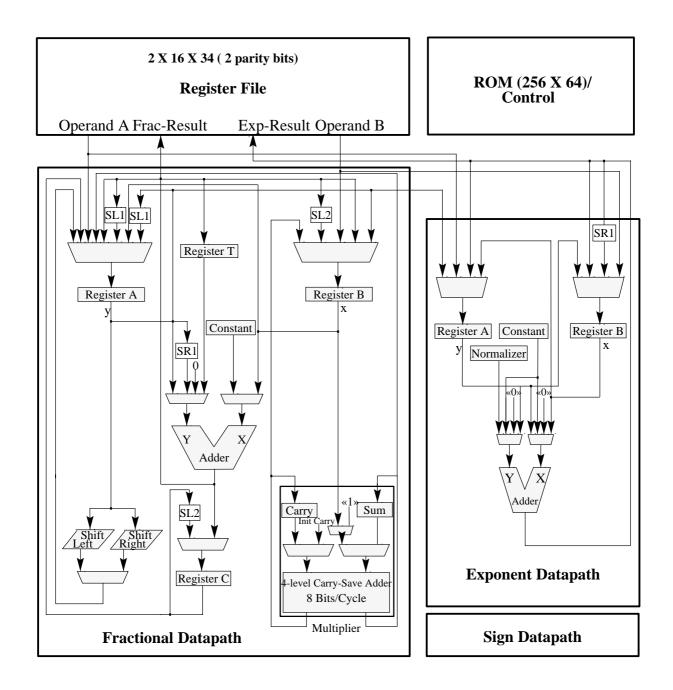

Figure 1. illustrates the functional block diagram for the TSC692E. The fetch unit captures instructions and their addresses from the D[31:0] and A[31:0] busses. The decode unit contains logic to decode the floating–point instruction opcodes. The execution unit handles all instruction execution. The execution unit includes a floating–point queue (FP queue), which contains stored floating–point operate (FPop) instructions (see Section 3.3.2) under execution and their addresses. The execution unit controls the load unit, the store unit, and the datapath unit.

The load unit holds data that is fetched from memory via the data bus before it is written into the register file. The register file contains the 32 f registers. The exceptions/floating-point status register (FSR) unit keeps the status of completing FPops, as well as the operating mode of the TSC692E. The store unit holds data that is supplied to the data bus during a store operation. The dependency checking unit checks for conditions where the FPU must freeze the TSC691E integer unit pipeline so that an incoming instruction does not overflow the floating-point queue. The datapath unit contains arithmetic logic used by FPops to operate on the data in the register file and is comprised of a Fractional, Exponent and Sign units. Figure 2. gives a more detailed block diagram of the TSC692E.

The TSC692E provides three types of registers: f registers, FSR, and the FP queue. The f registers are the thirty-two floating-point operand registers, each 32-bits in size. Adjacent even-odd f register pairs (for instance, f0 and f1 can be concatenated to support double-precision operands). The FSR is a 32-bit status and control register. It keeps track of rounding modes, floating-point trap types, queue status, condition codes, and various IEEE exception information. The floating-point queue contains the floating-point instruction currently under execution, along with its corresponding address. The floating-point queue provides an efficient method of handling floating-point exceptions. When an FPop instruction causes a floating-point exception, the queue contains the offending instruction/address pair along. The TSC691E integer unit acknowledges the floating-point exception, enters a floating-point trap routine, empties the queue, and corrects the exception case. After the exception case is corrected, unfinished floating-point instruction found in the floating-point queue is either executed or emulated in the trap handler before returning to normal execution.

The TSC692E depends upon the TSC691E to assert all addresses and control signals for memory access. Floating—point loads and stores are executed in conjunction with the TSC691E, which provides addresses and control signals while the TSC692E supplies or stores the data. Instruction fetch for integer and floating—point instructions is provided by the TSC691E. When the TSC691E integer unit asserts an address for an instruction fetch, it asserts the INST signal one clock later. The TSC692E floating—point unit uses INST to determine when a valid instruction is present on the D[31:0] bus. The instruction, which appears on the data bus on the next clock cycle, is latched and paired with its corresponding address. In any given cycle, one instruction/address pair is stored by the TSC692E, regardless of whether the instruction is an integer or floating—point instruction. This instruction/address pair may be selected for execution by the TSC691E upon asserting the FINS1 or FINS2 signal. The FINS1 or FINS2 signals enables a floating—point instruction to begin execution by the TSC692E.

Upon decoding a floating–point instruction, the TSC691E will assert the FINS1 or the FINS2 signal to enable the TSC692E to begin execution. The FINS1 or FINS2 signal is asserted during the decode stage of the floating–point instruction, and is recognized by the TSC692E at the beginning of the execute stage of the floating–point instruction. This ensures synchronization of the decode and execute stages of a floating–point instruction between instruction pipelines of the TSC691E and the TSC692E.

Figure 1. TSC692E Functional Block Diagram

Figure 2. TSC692E Block Diagram (without parity checking)

## 3.2. Floating-Point/Integer Unit Interface

The TSC692E is designed to directly interface with the TSC691E without external glue logic. Figure 3. illustrates the signals required to interconnect the TSC691E and TSC692E. The control signals illustrated in Figure 3. are used to interface with the remainder of the CPU system components. The FNULL, RESET, BHOLD, MHOLDA or MHOLDB,

MDS, and DOE signals are used by the a Cache Controller(CC) and Memory Management Unit (MMU) for cache interface and virtual bus arbitration. The signal descriptions for the TSC692E signals are described in Section 3.4.

Figure 3. TSC692E Hardware Interface

#### 3.2.1. TSC692E RT Instruction Fetch and Execution

The TSC692E uses a four-stage instruction pipeline consisting of fetch, decode, execute, and write stages (F, D, E, and W). The instruction pipelines for the TSC691E and the TSC692E are concurrent and synchronized; a floating-point instruction will be in the same stage in both processors. Multiple cycle instructions such as floating-point operate instructions (FPops) leave the pipeline after the W stage and enter the FP queue until completion.

Addresses for both integer unit and floating—point unit instructions are supplied by the TSC691E. The TSC692E FPU latches all instructions and the corresponding addresses from the D[31:0] and A[31:0] busses. The TSC692E uses the INST signal, supplied by the TSC691E, to identify an instruction fetch by the integer unit.

Decode of the latched instruction occurs on the next clock cycle, with both the IU and the FPU decoding the instruction simultaneously. During the decode stage of the floating–point instruction, the FPU checks for operand and resource dependencies. When the TSC691E integer unit decodes a FPop, it asserts the FINS1 or FINS2 signal. This occurs before the end of the decode stage, and is used by the TSC692E to initiate the execution of a floating–point instruction. If the TSC692E has detected an operand or resource dependency during the decode stage, the FPU will assert  $\overline{\text{FHOLD}}$  as the instruction begins the execution stage. This freezes the integer unit's pipeline until the FPU can resolve the dependency.

If no resource or operand dependencies exist, the decoded floating-point instruction begins execution. Instructions entering execution are stored in the FP queue, where they are held until execution is completed. Note that if the FP

queue is full during an instruction's decode stage, the TSC692E asserts FHOLD as the instruction enters the execution stage in order to halt the TSC691E. FHOLD is released when space becomes available in the FP queue.

The following tables describe the execution phases of TSC692E instructions. Additional cycles beyond the F, D, E, and W stages are denoted as Wh (Write hold). Wh stages are equivalent to the additional cycles held by IOPs in the TSC691E.

Table 1. Load instruction execution

| Cycle     | Action                                                                                         |

|-----------|------------------------------------------------------------------------------------------------|

| D stage   | Decode instruction, check operand dependencies                                                 |

| E stage   | FHOLD if necessary                                                                             |

| W stage   | Capture data from D[31:0] bus (LDF, LDFSR), capture MSW from D[31:0] bus (LDDF).               |

| Wh1 stage | Write data into FP registers or FSR register (LDF, LDFSR), capture LSW from D[31:0] bus (LDDF) |

| Wh2 stage | Write data into register (LDDF)                                                                |

#### **Table 2. Store instruction execution**

| Cycle                    | Action                                                                                                 |

|--------------------------|--------------------------------------------------------------------------------------------------------|

| D stage                  | Decode instruction, check operand dependencies                                                         |

| E stage                  | FHOLD if necessary, read data from FSR register or FP queue                                            |

| W stage (mid-cycle)      | Drive data onto D[31:0] bus (STF, STFSR), drive MSW or FP queue address onto D[31:0] bus (STDF, STDFQ) |

| Wh1 stage<br>(mid-cycle) | Stop driving D[31:0] bus (STF, STFSR), drive LSW or FP queue opcode onto D[31:0] bus (STDF, STDFQ)     |

| Wh2 stage<br>(mid-cycle) | Stop driving D[31:0] bus                                                                               |

#### Table 3. FPop execution

| Cycle    | Action                                                                   |

|----------|--------------------------------------------------------------------------|

| D stage  | Decode FPop, check resource and operand dependencies                     |

| E stage  | FHOLD if necessary, read operand(s) from register file                   |

| W stage  | Read any additional operands from register file; start computing results |

| FP Queue | Compute, FPop in queue                                                   |

| FP Queue | Check exception status                                                   |

| FP Queue | Update FSR, write results or signal FP exception trap if necessary       |

#### 3.2.1.1. Instruction Fetch

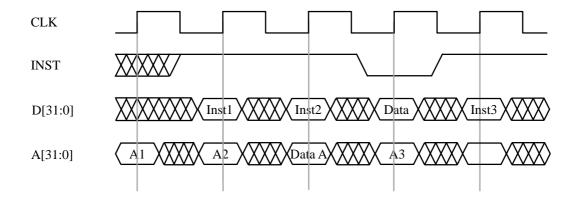

As the TSC691E fetches an instruction, the TSC692E captures it at the same time from the D[31:0] bus. The address corresponding to this instruction is captured from the A[31:0] in the previous cycle. The INST signal is used to determine when a valid instruction is present on the D[31:0] bus, and when a valid address has been fetched from the A[31:0] bus in the previous cycle. Figure 4. illustrates an example of an instruction fetch with a cache hit. The transactions on the address and data busses show two instruction fetches followed by a data fetch.

Figure 3. Instruction Fetch (Cache Hit)

Figure 4. Instruction Fetch (Cache Miss on A2)

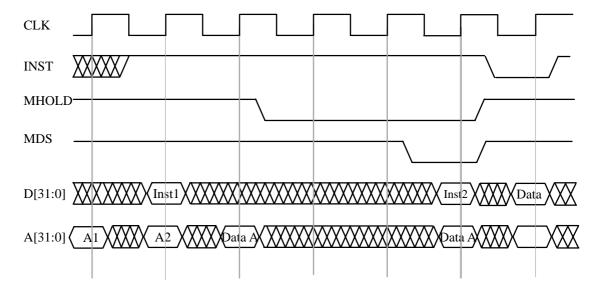

In the case of an instruction cache miss, a memory hold signal ( $\overline{MHOLDA}$ ,  $\overline{MHOLDB}$ , or  $\overline{BHOLD}$ ) is driven low by the cache system starting in the cycle following the instruction fetch. The instruction which was captured from the D[31:0] bus is invalid and is replaced when the system returns a valid instruction on the D[31:0] bus. The hold signal lasts for several cycles during which time the  $\overline{MDS}$  signal is asserted by the cache system, notifying the TSC692E that the valid instruction is available on the D[31:0] bus.  $\overline{MDS}$  is also used when there is a cache miss on data (via load instructions) so the instruction is reloaded only if INST was asserted in the previous non-hold cycle. The same sequence of transactions in Figure 4. are used in Figure 5., except that the second instruction fetch (Inst 2) experiences a cache miss.

#### 3.2.1.2. Instruction Execution

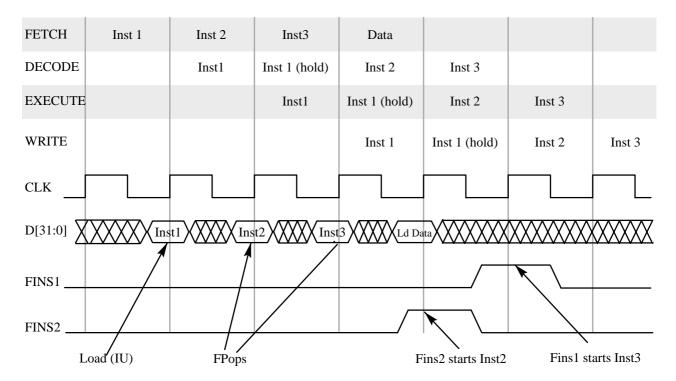

The FINS1 and FINS2 signals notify the TSC692E when to launch a floating-point instruction. When FINS1/FINS2 is received, the floating-point instruction is in the D stage of the TSC691E integer unit pipeline. The example in Figure 6. shows a situation where both FINS1 and FINS2 are used. A load instruction is followed by two FPops. The first FPop is fetched while the load instruction is executing. Because the load takes more than one cycle to execute, the starting of the FPop is deferred, and thus the instruction is held in the instruction buffer of the TSC692E. When the TSC691E reaches the D stage of the first FPop (Inst 2), it issues FINS2 to start the FPop. When the D stage of the second FPop (Inst 3) is reached, FINS1 is issued to start the second FPop.

FINS1 and FINS2 are never asserted in the same cycle. Both FINS1 and FINS2 are ignored in the following conditions:

- 1 FLUSH is asserted.

- 2 MHOLDA, MHOLDB, BHOLD, CHOLD, or FHOLD is asserted.

- 3 FCCV or CCCV is deasserted.

Figure 5. Floating-Point Instruction Dispatching

Figure 6. Floating-Point Compare (FCMP) Execution

#### 3.2.1.2.1. Floating-Point Compare Execution

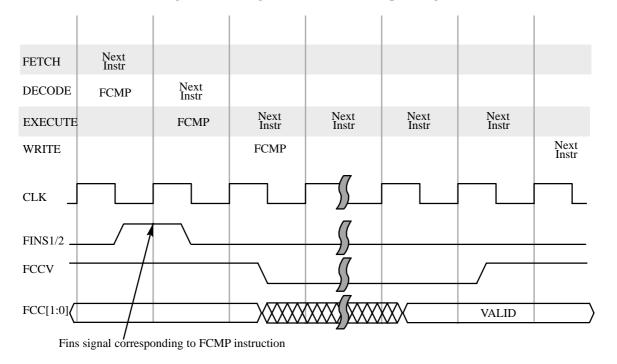

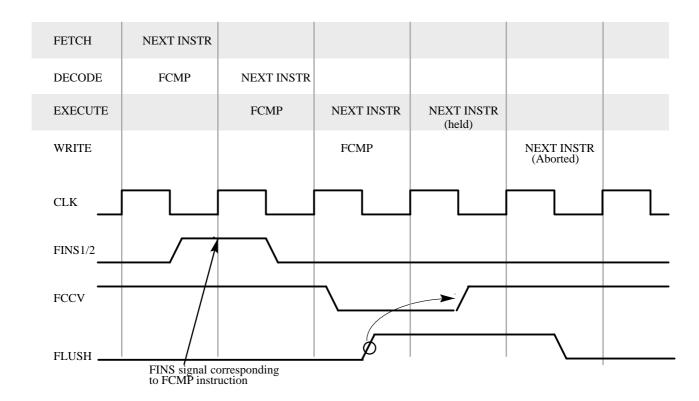

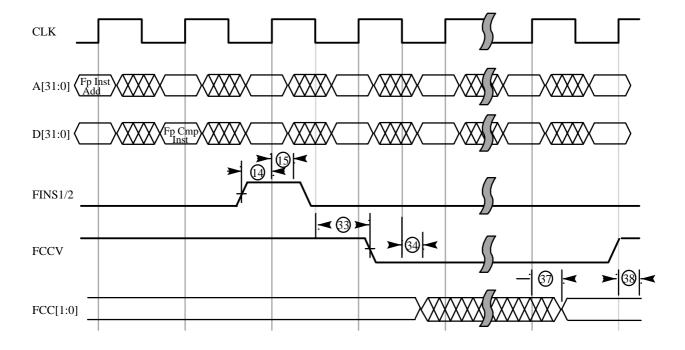

Floating–point compare instructions cause the instruction pipeline to be frozen by the use of FCCV, starting from the E stage of the instruction following the compare instruction until the FCC condition codes become valid. FCCV is deasserted, causing the TSC691E to HALT execution until FCCV is asserted. Figure 7. illustrates the timing of FCCV relative to the FCMP instruction and the FCC condition codes.

FCCV is deasserted in the W stage of the FCMP instruction. The instruction that immediately follows the FCMP is held in its E stage until FCCV is reasserted. FCC[1:0] is valid one cycle before FCCV is reasserted. For unimplemented compare instructions, the TSC692E freezes the instruction pipeline and causes an unimplemented FPop trap, which the TSC691E takes immediately.

#### **3.2.1.2.2. FPop Queuing**

When a FPop has passed the first cycle of the W stage and FLUSH has not been asserted, the FPop enters the FP queue. Note that the W stage of an FPop may be extended to more than one cycle if a hold condition exists. As an FPop completes execution successfully and results are written to the register file, it is removed from the FP queue.

#### 3.2.2. Instruction Pipeline Flush

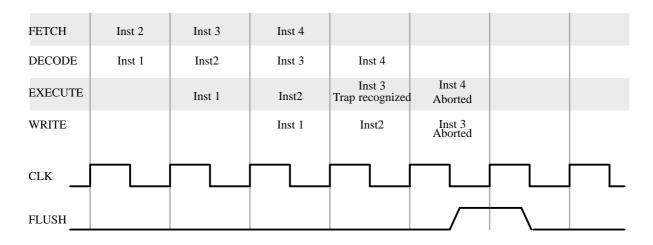

When a trap or interrupt occurs in the integer unit, normal program execution is  $\overline{HALT}$ ed and control is transferred to the trap handler. The instruction in the E stage of the pipeline and any instructions fetched after it are aborted and must be restarted after the trap handler is done (or emulated in the trap handler). Instructions that have not yet been transferred to the FP queue are aborted by the TSC692E when the trap occurs. The TSC691E asserts the FLUSH signal in the W stage of the instruction to be aborted (refer to Figure 8.). FPop which was issued before this instruction continues execution (and is in the queue) while instructions issued after it are aborted.

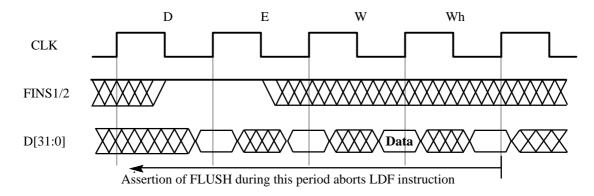

The following figures illustrate how each type of floating—point instruction is affected by the FLUSH signal. Figure 9. illustrates the effect of the FLUSH signal during a load floating—point instruction (LDF). A FLUSH signal asserted anytime on or before the last Wh stage of a load instruction causes the load to abort, leaving the contents of the floating—point register file unchanged.

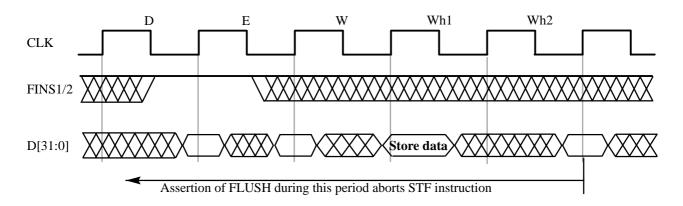

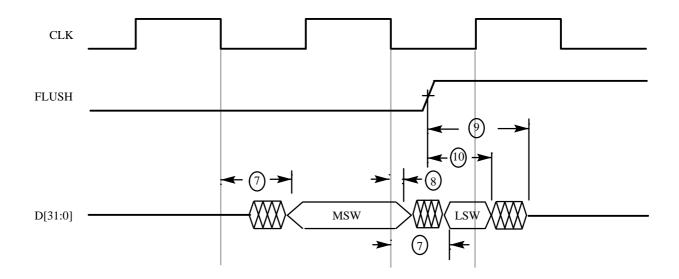

*Figure 10.* illustrates the effect of FLUSH on a store floating–point instruction (STF). A FLUSH signal asserted on or before the last Wh stage of a store instruction causes the store to abort and the TSC692E to stop driving the D[31:0] bus by the middle of the next clock cycle.

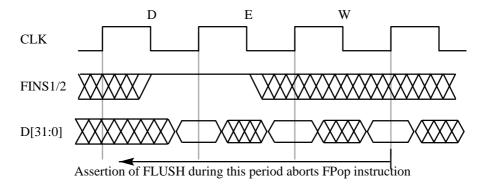

*Figure 11.* illustrates the effect of FLUSH on a FPop instruction. A FLUSH signal asserted anytime on or before the W stage of a FPop instruction causes the FPop to abort, leaving the contents of the register file and the FSR unchanged by that instruction. FPop that has passed the W stage but is still executing (stored in the FP queue) is not affected.

*Figure 12.* illustrates the effect of FLUSH on a floating–point compare. FLUSH asserted in the W stage of a FCMP instruction causes the FCMP to abort, leaving the FSR unchanged by that instruction. FCCV is reasserted in the next clock cycle.

Figure 7. Floating-Point Instruction Pipeline During A Trap

Figure 8. Effect of FLUSH on LDF Instruction

Figure 9. Effect of FLUSH on STF Instruction

Figure 10. Effect of FLUSH on FPop Instruction

Figure 11. Effect of FLUSH on FCMP Instruction

#### 3.2.2.1. Hold Signals

If MHOLDA, MHOLDB, BHOLD, CHOLD, or FHOLD is active, or FCCV or CCCV is inactive, the instruction pipelines of the TSC691E and TSC692E are frozen. FHOLD and FCCV are generated by the TSC692E, CHOLD and CCCV are generated by the coprocessor, and the others are generated by the system.

In the TSC692E, "freezing" or "holding" the instruction pipeline means that instructions that are still being tracked by the TSC691E are not allowed to continue executing. The instructions are allowed to continue execution when all of the hold signals are inactive and all of the condition code valid signals are active. Holds affect all load/store instructions, and only FPops which are in the F, D, E and W stages of the instruction pipeline. Hold signals do not affect the execution of a FPop in the FP queue.

#### 3.2.2.2. Interlocking with FHOLD

In some situations it is necessary to stop the TSC691E pipeline, either because a FP load/store instruction must be suspended due to an operand dependency, or because the TSC692E cannot accept any more instructions due to a resource dependency.  $\overline{FHOLD}$  is used to freeze the instruction pipeline in these cases. Table 4. describes mandatory conditions under which  $\overline{FHOLD}$  is asserted.

Operand dependencies listed in Table 4. apply to all FPops that are defined in the architecture. For example, suppose an unimplemented FPop is in the FP queue, waiting to cause an exception. If a store instruction is issued to the TSC692E to store the contents of the unimplemented FPop's destination register, the store instruction must cause a FHOLD so that the wrong data is not stored. The unimplemented FPop eventually causes a trap that is taken by the TSC691E in the E stage of the store instruction.

The following simplification could be applied when handling all unimplemented FPops: when an unimplemented FPop has been issued to the TSC692E but has not yet caused a trap, assert FHOLD on the next floating-point instruction issued until FEXC is asserted. There is no loss in performance because any FPops entering the FP queue after the unimplemented FPop would be re–executed after the unimplemented FPop has been taken care of in the trap handler.

#### Table 4. FHOLD Resource/Operand Dependency Cases

|                 | Resource Dependencies:                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                 | If the TSC692E will not have FP queue entry available to accommodate additional FPops, the TSC692E asserts FHOLD to stop the TSC691E from issuing any more instructions to the TSC692E. |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Operand Dep     | pendencies:                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| LDF,<br>LDDF    | Load data from<br>memory to f register                                                                                                                                                  | Load instructions must not overwrite the source or destination registers of any FPop that has not completed execution. In other words, the rd. field of the load instruction must not refer to the same $f$ register as any valid rs1, rs2 or rd field of an outstanding FPop. The source registers of FPops (rs1, rs2) may not be altered because an FP exception trap would require that the source registers be unaltered for the trap handler. |  |  |  |  |

| STF,<br>STDF    | Store data from f register to memory                                                                                                                                                    | If a store instruction accesses an <i>f</i> register that is the destination register of an FPop that has not yet finished execution, the store instruction waits until all outstanding FPops with that register as a destination are complete.                                                                                                                                                                                                    |  |  |  |  |

| LDFSR,<br>STFSR | Load/store data<br>between memory and<br>floating-point status<br>register                                                                                                              | If any instructions are currently executing in the TSC692E when a LDFSR/STFSR instruction is issued by the TSC691E, the TSC692E holds until all instructions have completed execution and are no longer in the FP queue.  If a LDFSR instruction is currently executing in the TSC692E when an FPop or STFSR is issued by the TSC691E, the TSC692E holds until LDFSR instruction has completed execution                                           |  |  |  |  |

| STDFQ           | Store FP queue while<br>qne=1 and in<br>execution mode                                                                                                                                  | If a STDFQ is issued by the TSC691E when the Floating-Point Queue is empty (qne=0) and the TSC692E is in execution mode, the TSC692E holds until STDFQ instruction has completed execution.                                                                                                                                                                                                                                                        |  |  |  |  |

| UNIMP           | Unimplemented FP operation                                                                                                                                                              | If an unimplemented FPop has been issued to the TSC692E but has not yet caused a trap, the TSC692E holds on the next floating–point instruction issued by the TSC691E.                                                                                                                                                                                                                                                                             |  |  |  |  |

If the TSC692E goes into exception mode,  $\overline{FHOLD}$  is deasserted. If there is a floating–point sequence error (see Section 3.3.3),  $\overline{FHOLD}$  is asserted for two cycles. This is the only case where  $\overline{FHOLD}$  is asserted in the exception mode.

If a floating–point trap condition occurs while  $\overline{FHOLD}$  is asserted,  $\overline{FHOLD}$  is deasserted at least one cycle after  $\overline{FEXC}$  is asserted. Similarly, if FCCV is deasserted, it is reasserted at least one cycle after  $\overline{FEXC}$  is asserted. For the  $\overline{FHOLD}$  case, the TSC691E takes the FP trap on the FP instruction that triggered the  $\overline{FHOLD}$ .

#### 3.2.2.3. FNULL Signal

FNULL is used to signal a pipeline delay of the TSC691E by the TSC692E. FNULL replaces FCCV and FHOLD for informing the system that the pipeline is being held. FNULL is asserted when either FHOLD is asserted or FCCV is deasserted. This signal is used as an input by the CC and MMU to monitor pipeline freezes initiated by the TSC692E.

## 3.3. TSC692E Programming Model

#### 3.3.1. TSC692E Registers

The TSC692E has three types of user accessible registers: the f registers, the FP queue, and the Floating–point Status Register (FSR). The f registers are the TSC692E data registers. The FSR is the TSC692E status and operating mode register. The FP queue contains the TSC692E instruction that has started execution and is awaiting completion. The following section describes these registers in detail.

#### **3.3.1.1. f** Registers

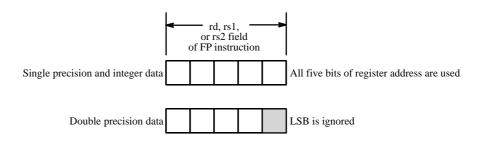

The TSC692E provides 32 registers for floating—point operations, referred to as *f* registers. These registers are 32 bits in length, which can be concatenated to support 64—bit double words. Extended precision instructions are not supported in the TSC692E. Figure 13. illustrates the data organization for the *f* registers.

Integer and single precision data requires a single 32-bit f register. Double precision data requires 64 bits of storage and occupies an even-odd pair of adjacent f registers.

The TSC692E forces register addressing to match the data type specified by the floating–point instruction. This ensures data alignment in the f register file for double precision data. Figure 14. illustrates how the TSC692E uses the five register address bits in a floating–point instruction for the different types of data. Single data word transfers (integer,

single-precision floating-point) can be stored in any register. Consequently, all five bits of the register address specified in the floating-point instruction are valid. Double precision data must reside in an even-odd pair of adjacent registers. By ignoring the LSB of the register address for a FPop requiring a register pair, the TSC692E ensures data alignment.

|                | f0  | f1  | f2  | f3  |

|----------------|-----|-----|-----|-----|

|                | f4  | f5  | f6  | f7  |

|                | f8  | f9  | f10 | f11 |

|                | f12 | f13 | f14 | f15 |

|                | f16 | f17 | f18 | f19 |

|                | f20 | f21 | f22 | f23 |

|                | f24 | f25 | f26 | f27 |

|                | f28 | f29 | f30 | f31 |

|                |     |     |     |     |

|                |     |     |     |     |

| recision data  | MSW | LSW | MSW | LSW |

|                |     |     |     |     |

|                |     |     |     |     |

| l integer data |     |     |     |     |

|                |     |     |     |     |

Double pr

Single precision or signed

Figure 12. f Register Organization

Figure 13. f Register Addressing

#### 3.3.1.2. FP Queue

The TSC692E maintains a floating-point queue of the instruction that has started execution, but has yet to complete execution. The FP queue is used to accommodate the multiple clock nature of floating-point instructions and to support the handling of FP exceptions.

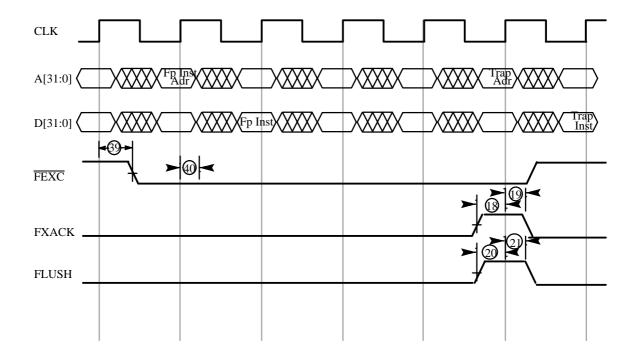

When the TSC692E encounters an exception case, it asserts  $\overline{FEXC}$  and enters pending exception mode. The TSC692E remains in pending exception mode until the TSC691E encounters another floating-point instruction, at which time the TSC691E asserts the FXACK signal to force the TSC692E into exception mode. When the TSC692E enters the exception mode, floating-point execution halts until the FP queue is emptied. This allows the TSC691E to store the floating-point instructions under execution when the exception case occurred. Emptying the FP queue frees the TSC692E for use by the trap handler without losing the pre–exception state of the TSC692E.

The FP queue contains the 32-bit address and 32-bit FPop instruction of one instruction under execution. Floating-point load and store instructions and FP branch instructions are not queued. The entry of the FP queue is accessible by executing the store double floating-point queue (STDFQ) instruction. A load FP queue instruction does not exist, as the FP queue must be loaded by launching instructions.

Figure 14. Floating-Point Status Register

#### 3.3.1.3. Floating-Point Status Register (FSR)

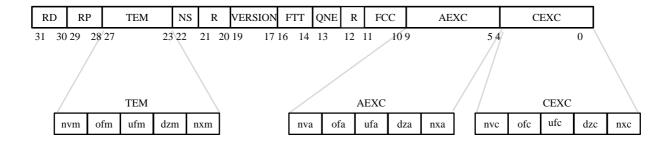

The following paragraphs describe the bit fields of the floating-point status register (FSR). Refer to Table 5. (following page) for bit assignments for the FSR fields.

**RD** *FSR*(31:30). Rounding Direction: These two bits define the rounding direction used by the TSC692E during an FP arithmetic operation.

**RP** FSR(29:28). Unused - always set to 0.

**TEM** *FSR*(27:23). Trap Enable Mask: These five bits enable traps caused by FPops. These bits are ANDed (1= enable, 0= disable) with the bits of the CEXC (current exception field) to determine whether to force a floating–point exception to the TSC691E. All trap enable fields correspond to the similarly named bit in the CEXC field (see below). The TEM field only affects which bits in the CEXC field will cause the FEXC signal to be asserted.

NS FSR(22). Non–Standard floating point: This bit is always set to 0 (IEEE mode).

**version** *FSR*(19:17). The version number is used to identify the SPARC floating–point processor type. This field is set to 100 (4H) for the TSC692E, and is read–only.

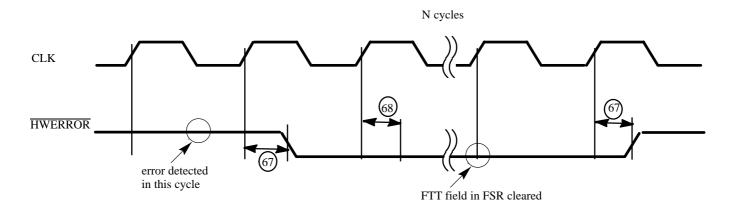

**FTT** *FSR*(16:14). Floating–point Trap Type: This field identifies the floating point trap type of the current FP exception. This field can be read and written, and must be cleared by software.

QNE FSR(13). Queue Not Empty: This bit signals whether the FP queue is empty. (0= empty, 1= not empty)

FCC FSR(11:10). Floating-point Condition Codes: These two bits report the FP condition codes (see Table 5.).

**AEXC** FSR(9:5). Accumulated EXCeptions: This field reports the accumulated FP exceptions that are masked by the TEM field. All masked exception cases are ORed with the contents of the AEXC and accumulated as status. All accumulated fields have the same definition as the corresponding field for CEXC (see below). This field can be read and written, and must be cleared by software (see Table 5.).

**CEXC** *FSR*(*4:0*). Current EXCeptions: This field reports the current FP exceptions. This field is automatically cleared upon the execution of the next floating–point instruction. CEXC status is not lost upon assertion of a floating–point exception, because instructions following a valid exception are not executed by the TSC692E. The five CEXC bits are:

- nvc = 1 indicates invalid operation exception. This is defined as an operation using an improper operand value. An example of this is 0/0.

- ofc = 1 indicates overflow exception. The rounded result would be larger in magnitude than the largest normalized number in the specified format.

- ufc = 1 indicates underflow exception. The rounded result is inexact, and would be smaller in magnitude than the smallest normalized number in the indicated format.

- dzc = 1 indicates division-by-zero: X/0, where X is subnormal or normalized. Note that 0/0 does not set the dzc bit.

- nxc = 1 indicates inexact exception. The rounded result differs from the infinitely precise correct result.

R FSR 21,20 and 12. Reserved - always set to 0.

# **Table 5. Floating-Point Status Register Summary**

| Field   | Values                          | FSR<br>bits | Description                                                                                                                                                                       | Loadable by<br>LDFSR |

|---------|---------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| RD      | 0 - Round to nearest (tie-even) | 31:30       | Rounding Direction                                                                                                                                                                | yes                  |

|         | 1 - Round to 0                  |             |                                                                                                                                                                                   |                      |

|         | 2 - Round to +                  |             |                                                                                                                                                                                   |                      |

|         | 3 - Round to -                  |             |                                                                                                                                                                                   |                      |

| RP      | Unused Bits                     | 29:28       | Unused always set to 0                                                                                                                                                            | no                   |

| TEM     | 0 - Disable trap                | 27:23       | Trap Enable Mask                                                                                                                                                                  | yes                  |

|         | 1 - Enable trap                 |             |                                                                                                                                                                                   |                      |

|         | NVM                             | 27          | invalid operation trap mask                                                                                                                                                       |                      |

|         | OFM                             | 26          | overflow trap mask                                                                                                                                                                |                      |

|         | UFM                             | 25          | underflow trap mask                                                                                                                                                               |                      |

|         | DZM                             | 24          | divide by zero trap mask                                                                                                                                                          |                      |

|         | NXM                             | 23          | inexact trap mask                                                                                                                                                                 |                      |

| NS      | 0 - Disable                     | 22          | Non–standard Floating–point:<br>0 = IEEE mode; multiplier and ALU generate denormalized<br>operand exceptions and produce unrounded normalized values<br>on underflow exceptions. | no                   |

|         | 1 - Enable                      |             | 1 = FAST mode; multiplier and ALU flush denormalized operands to zero and round underflow results to zero.                                                                        |                      |

| version | 0 - 7                           | 19:17       | FPU version number                                                                                                                                                                | no                   |

| FTT     | 0 - None                        | 16:14       | Floating-point trap type                                                                                                                                                          | no                   |

|         | 1 - IEEE Exception              |             |                                                                                                                                                                                   |                      |

|         | 2 - Unfinished FPop             |             |                                                                                                                                                                                   |                      |

|         | 3 - Unimplemented FPop          |             |                                                                                                                                                                                   |                      |

|         | 4 - Sequence Error              |             |                                                                                                                                                                                   |                      |

|         | 5 - Data Bus Error              |             |                                                                                                                                                                                   |                      |

|         | 6 - Restartable Error           |             |                                                                                                                                                                                   |                      |

|         | 7 - Non-Restartable Error       |             |                                                                                                                                                                                   |                      |

| QNE     | 0 - queue empty                 | 13          | Queue Not Empty                                                                                                                                                                   | no                   |

| FCC     | 0 - =                           | 11:10       | Floating-point Condition Codes                                                                                                                                                    | yes                  |

|         | 1 - <                           |             |                                                                                                                                                                                   |                      |

|         | 2 ->                            |             |                                                                                                                                                                                   |                      |

|         | 3 - Unordered                   |             |                                                                                                                                                                                   |                      |

| AEXC    |                                 | 9:5         | Accrued Exception Bits                                                                                                                                                            | yes                  |

|         | NVA                             | 9           | accrued invalid exception                                                                                                                                                         |                      |

|         | OFA                             | 8           | accrued overflow exception                                                                                                                                                        |                      |

|         | UFA                             | 7           | accrued underflow exception                                                                                                                                                       |                      |

| Field | Values                       | FSR<br>bits   | Description                      | Loadable by<br>LDFSR |

|-------|------------------------------|---------------|----------------------------------|----------------------|

|       | DXA                          | 6             | accrued divide by zero exception |                      |

|       | NXA                          | 5             | accrued inexact exception        |                      |

| CEXC  | C 4:0 Current Exception Bits |               | yes                              |                      |

|       | NVC                          | 4             | current invalid exception        |                      |

|       | OFC                          | 3             | current overflow exception       |                      |

|       | UFC                          | 2             | current underflow exception      |                      |

|       | DZC                          | 1             | current divide by zero exception |                      |

|       | NXC                          | 0             | current inexact exception        |                      |

| r     | Always set to 0              | 21, 20,<br>12 | reserved bits                    | no                   |

### 3.3.2. TSC692E Floating-Point Instructions

SPARC floating–point instructions are separated into three groups: floating–point load/store, floating–point branch (FBfcc), and floating–point operate instructions (FPops). Floating–point load/store instructions are used to transfer data to and from the data registers (f registers). FP load/store instructions also allow the TSC691E integer unit to read and write the floating–point status register (FSR) and to read the entry of the floating–point queue. Floating–point load and store instructions are executed by both the TSC691E and the TSC692E; the TSC691E supplying all address and control signals for memory access and the TSC692E loading or storing the data.

Floating–point branch (FBfcc) instructions (and coprocessor branch instructions (CBccc)) are executed by the TSC691E, since the TSC691E is responsible for generating address and control signals for memory access. Conditional FBfcc branches are based upon the FCC[1:0] signals supplied by the TSC692E. FCC[1:0] is set by executing a FCMP instruction, which belongs to the FPop group of instructions. Floating–point branch instructions will cause the TSC691E to recognize a pending floating–point exception in the same manner as other floating–point instructions (see Section 3.3.3).

FPops include all other floating—point instructions executed by the TSC692E. Floating—point operate instructions (FPops) include basic numeric operations (add, subtract, multiply, and divide), conversions between data types, register to register moves, and floating—point number comparison. FPops operate only on data in the floating—point registers.

The SPARC architecture supports four data types: 32-bit signed integer, single-precision FP, double-precision FP, and extended-precision FP. Extended precision instructions are defined in the SPARC architecture, but are not supported in the TSC692E. The TSC692E supports execution of extended precision floating-point instructions by asserting an unimplemented instruction trap. This allows the TSC691E to trap to a software emulation of extended precision floating-point.

Seven load/store instructions are executed by the TSC692E. The following describes the TSC692E load/store instructions:

LDF and LDDF transfer data from memory to f registers 32 and 64 bits at a time, respectively.

STF and STDF transfer data from the f registers to memory in data widths of 32 and 64 bits.

LDFSR and STFSR allow the FSR to be read and written to.

STDFQ is a privileged instruction which allows the FP queue to be read.

All FPops operate only on data located in the  $\underline{f}$  registers. The FPops are divided into four groups: basic arithmetic operations, compares, format conversions, and register—to—register moves. Move operations do not cause exceptions. The converts, moves and the square root instruction use only a single source operand. FP compare instructions modify only the FCC[1:0] signals. FPops are dispatched in one cycle in the TSC691E, and require multiple cycles to execute in the TSC692E.

Table 6. and Table 7. illustrate the TSC692E instructions and their execution cycle count. For further information on the SPARC floating–point instructions, please refer to Chapter 6, SPARC Instruction Set.

# Table 6. Floating–Point Load and Store Instruction Cycle Count

| Mnemonic | Operation                   | Cycles |

|----------|-----------------------------|--------|

| LDF      | load floating-point         | 2      |

| LDDF     | load double floating-point  | 3      |

| LDFSR    | load FSR                    | 2      |

| STF      | store floating-point        | 3      |

| STDF     | store floating-point double | 4      |

| STFSR    | store FSR                   | 3      |

| STDFQ    | store double FP queue       | 4      |

Table 7. Floating-Point Operate (FPops) Instruction Cycle Count

| Mnemonic | Operation                                 | Min. | Cycles <sup>[a]</sup><br>Max. | Тур. |

|----------|-------------------------------------------|------|-------------------------------|------|

| FABSs    | absolute value                            | 2    | 2                             | 2    |

| FADDs    | add single                                | 4    | 4                             | 17   |

| FADDd    | add double                                | 4    | 4                             | 17   |

| FCMPs    | compare single                            | 4    | 4                             | 15   |

| FCMPd    | compare double                            | 4    | 4                             | 15   |

| FCMPEs   | compare single and exception if unordered | 4    | 4                             | 15   |

| FCMPEd   | compare double and exception if unordered | 4    | 4                             | 15   |

| FDIVs    | divide single                             | 6    | 20                            | 38   |

| FDIVd    | divide double                             | 6    | 35                            | 56   |

| FMOVs    | move                                      | 2    | 2                             | 2    |

| FMULs    | multiply single                           | 5    | 5                             | 25   |

| FMULd    | multiply double                           | 7    | 9                             | 32   |

| FNEGs    | negate                                    | 2    | 2                             | 2    |

| FSQRTs   | square root single                        | 6    | 37                            | 51   |

| FSQRTd   | square root double                        | 6    | 65                            | 80   |

| FSUBs    | subtract single                           | 2    | 4                             | 17   |

| FSUBd    | subtract double                           | 4    | 4                             | 17   |

| FdTOi    | convert double to integer                 | 7    | 7                             | 14   |

| FdTOs    | convert double to single                  | 3    | 3                             | 16   |

| FiTOs    | convert integer to single                 | 5    | 6                             | 13   |

| FiTOd    | convert integer to double                 | 4    | 6                             | 13   |

| FsTOi    | convert single to integer                 | 6    | 6                             | 13   |

| FsTOd    | convert single to double                  | 2    | 2                             | 14   |

<sup>[</sup>a]. These cycle counts assume that the operands are available in the register file. A load-use interlock may add up to 2 cycles to the typical cycle count.

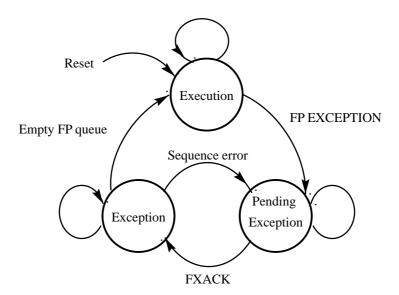

#### 3.3.3. TSC692E Internal Operation

The TSC692E operates in one of three modes: execution mode, pending exception mode, and exception mode (see Figure 16.). After reset, the TSC692E enters execution mode, which is the normal mode of operation. When the TSC692E encounters a floating–point exception condition, the TSC692E asserts  $\overline{FEXC}$  and enters the pending exception mode. All FPop instructions under execution at this point are suspended. The TSC691E asserts FXACK and enters the floating–point trap when the next floating point instruction is encountered. Upon receiving FXACK, the TSC692E FPU enters exception mode. The TSC692E returns to execution mode as soon as the trap handler empties the FP queue using STore Double Floating–point Queue instructions (STDFQ).

#### 3.3.3.1. Exception Handling

Upon encountering an exception condition, the TSC692E asserts  $\overline{FEXC}$  to notify the TSC691E that a floating-point exception has occurred and enters the pending exception mode. The TSC691E enters the trap handler on the next

<sup>[</sup>b]. Max. Cycles is for NaN and Denormalized subresults.

floating—point instruction it encounters in the instruction stream, asserting FXACK to signal to the TSC692E that the trap is being taken. At this point, the TSC692E enters exception mode and the FP queue contains instruction and address of the FP operation which caused the FP exception (see Figure 16.).

Upon receiving FXACK from the TSC691E, the mode of the TSC692E changes from pending exception to exception mode. An FP exception can only be caused while the FPU is moving between these two modes or by executing STDFQ when FP queue is empty (qne field in FSR equal to 0). All FPops in the TSC692E stop executing during pending exception and exception modes. While in exception mode, the TSC692E will execute only store floating—point instructions until the FP queue is emptied. All floating—point store instructions are allowed while in this operating mode (particularly STDFQ and STFSR) and they cannot cause an exception trap. Any load or FPop issued to the TSC692E while in this mode causes a sequence error and returns the TSC692E to exception pending mode and sets the ftt sequence error field in FSR. The instruction that caused the sequence error is not entered into the FP queue. Once the queue is emptied by STDFQ instruction, the TSC692E returns to execution mode.

If a STDFQ instruction is executed when the FP queue is empty (qne field in FSR equal to 0, FPU in execute mode), the FPU generates an immediate trap and sets the ftt field in FSR to sequence error, but the FPU remains in the execute mode.

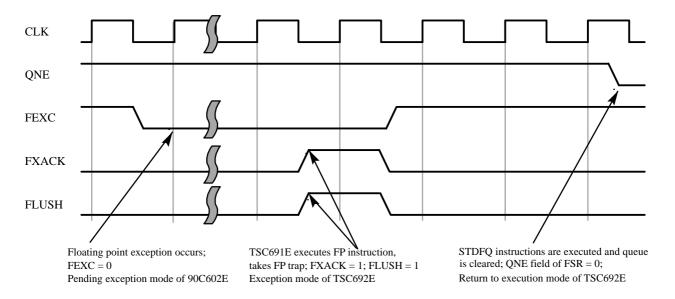

Figure 17. illustrates the handshake of signals between the TSC691E and the TSC692E during a floating–point exception. The que (queue not empty) bit of the FSR is shown in Figure 17. to illustrate the dependency of clearing the FP queue to return to execution mode.

Figure 15. FPU Operation Modes

Figure 16. Floating-Point Exception Handshake

#### 3.3.4. TSC692E IEEE-754 Compliance

The TSC692E meets the requirements of the IEEE Std. 754–1985 for floating–point arithmetic. Accuracy of the results of its operations are within  $\pm \frac{1}{2}$  LSB, as specified by the IEEE standard. The following sections describe the IEEE format as implemented on the TSC692E.

#### 3.3.4.1. IEEE Definitions

The following terms are used extensively in describing the IEEE-754 floating-point data formats. This section is directly quoted from the *IEEE Standard for Binary Floating-Point Arithmetic*.

#### biased exponent

The sum of the exponent and a constant (bias) chosen to make the biased exponent's range nonnegative. (Note in the remainder of this section, the term "exponent" refers to a biased exponent.)

#### binary floating-point number

A bit string characterized by three components: a sign, a signed exponent and a significand. Its numerical value, if any, is the signed product of its significand and two raised to the power of its exponent.

#### Denormalized

Denormalized numbers are those numbers whose magnitude is smaller than the smallest magnitude representable in the format. They have a zero exponent and a denormalized non–zero fraction. Denormalized fraction means that the hidden bit is zero.

The TSC692E can directly operate on denormalized operands. The TSC692E never assert an unfinished FPop exception when an operation results in a denormalized number.

### denormalized number

(DNRM) A non-zero floating-point number whose exponent has a reserved value, usually the format's minimum, and whose explicit or implicit leading significand bit is zero. (Denormalized numbers are also referred to as subnormal in this text.)

#### fraction

The field of the significand that lies to the right of its implied binary point.

#### NaN

Not a number, a symbolic entry encoded in floating—point format. They are used to signal invalid operations and as a way of passing status information through a series of calculations. NaNs arise in one of two ways: they can be generated by the TSC692E upon an invalid operation or they may be supplied by the user as an input

operand. NaN is further subdivided into two categories: quiet and signaling. Signaling NaNs signal the invalid operation exception whenever they appear as operands. Quiet NaNs propagate through almost every arithmetic operation without signaling exceptions.

#### Normalized

Most calculations are performed on normalized numbers. For single–precision, they have a biased exponent range of 1 to 255, which results in a true exponent range of -126 to +127. The normalized number type implies a normalized significand (hidden bit is 1).

#### significand

The component of a binary floating—point number that consists of an explicit or implicit leading bit to the left of its implied binary point and a fraction field to the right.

#### true exponent

The component of a binary floating—point number that normally signifies the integer power to which 2 is raised in determining the value of the represented number.

#### Zero

The IEEE zero has all fields except the sign field equal to zero. The sign bit determines the sign of zero (i.e., the IEEE format defines a + 0 and a - 0).

#### 3.3.4.2. IEEE Floating-point Data Formats

The TSC692E directly supports single— and double—precision floating—point data formats. Extended—precision instructions (non-implemented) encountered by the TSC692E cause an unimplemented instruction trap to be asserted by the TSC692E. This allows software to emulate extended—precision instructions through the use of a trap handler. Single— and double-precision formats are described in this section.

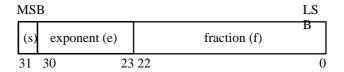

Figure 17. Single-Precision Floating-Point Format

Figure 18. Double-Precision Floating-Point Format

#### 3.3.4.2.1. Single-Precision Floating-Point

Single–precision floating–point data are 32–bits wide and consist of three fields: a single sign bit (s), an eight–bit biased exponent (e), and a 23–bit fraction (f). Figure 18. illustrates the single–precision floating–point format.

The IEEE standard defines single-precision floating-point numbers according to the following conventions:

(+0, -0) If e = 0 and f = 0, then the value  $V = (-1)^{s} * (0)$  Note that two representations of zero exist, one positive and one negative

DNRM (denormalized) If e = 0 and  $f \neq 0$ , then the value V = DNRM

Normalized If 0 < e < 255, then value  $V = (-1)^s * (2^{e-127}) * (1.f)$  Note that 1.f is the significand. The one to the left of the binary point is the so–called "hidden bit." This bit is not

stored as part of the floating-point word; it is implied. For a number to be

normalized, it must have this one to the left of the binary point.

$(+\infty, -\infty)$  If e = 255 and f = 0, then value  $V = (-1)^s * \infty$

NaN (not a number) If e = 255 and  $f \neq 0$ , then value V = NaN.

The value is a quiet NaN if the first bit of the fraction is 1, and a signaling NaN if the

first bit of the fraction is 0 (at least one bit must be non–zero).

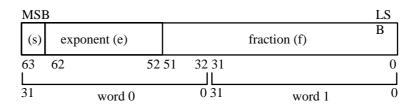

#### 3.3.4.2.2. Double-Precision Floating-Point

Double–precision floating–point data are 64–bits wide and consist of three fields: a single sign bit (s), an eleven–bit biased exponent (e), and a 52–bit fraction (f). Figure 19. illustrates the double–precision floating–point format.

The IEEE standard defines double-precision floating-point numbers according to the following conventions:

$(+0, -0) \hspace{1cm} If \ e=0 \ and \ f=0, \ then \ value \ V=(-1)^{\boldsymbol{s}\,*}(0)$

DNRM If e = 0 and  $f \neq 0$ , then value V = DNRM

Normalized If 0 < e < 2047, then value  $V = (-1)^s * (2^{e-1023}) * (1.f)$

$(+\infty, -\infty)$  If e = 2047 and f = 0, then value  $V = (-1)^{s} * \infty$

NaN If e = 2047 and  $f \neq 0$ , then value V = NaN.

The value is a quiet NaN if the first bit of the fraction is 1, and a signaling NaN if the first bit of the fraction is 0 (at least one bit must be non–zero).

#### 3.3.5. NaN Format

The TSC692E uses different NaN format. Table 8. and Table 9. give returned values for untrapped floating-point result.

Table 8. Untrapped FP result in same format as operand

| RS2, RS1 | number   | QNaN2  | SNaN2  |

|----------|----------|--------|--------|

| none     | IEEE 754 | QNaN2  | ME_NaN |

| number   | IEEE 754 | QNaN2  | ME_NaN |

| QNAN1    | QNaN1    | QNaN1  | ME_NaN |

| SNAN1    | ME_NaN   | ME_NaN | ME_NaN |

- QNaN results have their sign bit equal to 0.

- ME\_NaN is 0x 7fff 0000 (Single Precision)

- ME\_NaN is 0x 7fff e000 0000 0000 (Double Precision)

Table 9. Untrapped FP result in different format

| RS2 Operation | +QNaN   | -QNaN   | +SNaN  | -SNaN  |

|---------------|---------|---------|--------|--------|

| fstoi         | +imax   | -imax   | +imax  | -imax  |

| fstod         | (QNaN2) | (QNaN2) | ME_NaN | ME_NaN |

| fdtos         | ME_NaN  | ME_NaN  | ME_NaN | ME_NaN |

| fdtoi         | +imax   | -imax   | +imax  | -imax  |

- -imax is 0x 8000 0000

- +imax is 0x 7fff ffff

- (QNaN2) is a copy of the mantissa bits of the operand, with the extra low

- order bits zeroed, and the sign bit zeroed

#### 3.3.6. TSC692E Exception Cases

The following section describes the TSC692E exception cases, including exceptions specified by the IEEE-754 standard.

<u>Unfinished</u> FPop. In IEEE-754 standard, this exception case can occur when operations on normalized floating—point numbers either encounter a denormalized operand or produce a denormalized result. This exception case is asserted upon executing any FPop encountering a NaN as one of the operands. The TSC692E never asserts this exception since all implemented instructions are executed within hardware.

<u>Unimplemented</u> FPop. This exception is asserted by the TSC692E upon encountering a defined SPARC FPop instruction that is not supported by the TSC692E. This includes all operations using extended–precision format operands. The trap handler is expected to emulate the unimplemented instruction.