# DUAL FORWARD-CONDUCTING P-GATE THYRISTORS PROGRAMMABLE OVERVOLTAGE PROTECTORS

## TISP6L7591 SLIC Protector

#### **Rated for Standard Lightning Wave Shapes**

| Wave Shape | Standard          | I <sub>PP</sub> |

|------------|-------------------|-----------------|

| 2/10       | GR-1089-CORE      | ±80             |

| 10/700     | ITU-T K.20 & K.21 | ±40             |

| 10/1000    | GR-1089-CORE      | ±30             |

#### **Rated for AC Fault Currents**

| AC<br>Hz | Time<br>s | I <sub>TSM</sub> |

|----------|-----------|------------------|

| 50/60    | 0.01      | ±5               |

| 30/00    | 1         | ±3.5             |

| Gate Trigger Current        | 15 mA max.               |

|-----------------------------|--------------------------|

| High V <sub>S</sub> Voltage | 80 V max.                |

| High Holding Current        | 150 mA min.              |

| <b>N</b>                    | UL Recognized Components |

#### Description

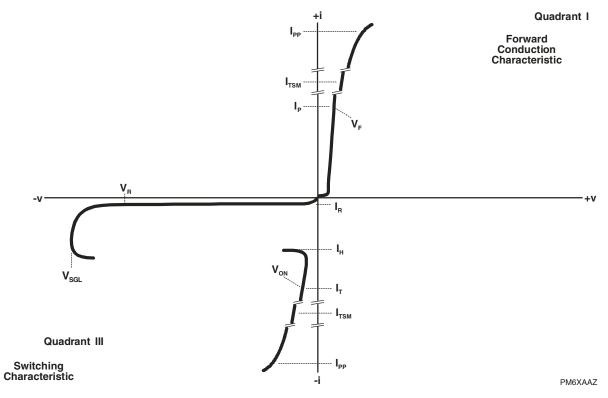

The TISP6L7591 is a dual forward-conducting buffered p-gate overvoltage protector. It is designed to protect monolithic SLICs (Subscriber Line Interface Circuits) against overvoltages on the telephone line caused by lightning, a.c. power contact and induction. The TISP6L7591 limits voltages that exceed the SLIC supply rail voltage.

The SLIC line driver section is typically powered from 0 V (ground) and a negative voltage,  $V_{\rm S}$ , in the region of -20 V to -80 V. The protector gate is connected to this negative supply. This references the protection (clipping) voltage to the negative supply voltage. The negative protection voltage will then track the negative supply voltage and the overvoltage stress on the SLIC is minimized.

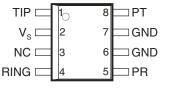

#### D Package (Top View)

MD6XAND

#### **Device Symbol**

SD6XAEE

| Pin | Symbol                  | Comment        | Pin                  | Symbol         | Comment       |

|-----|-------------------------|----------------|----------------------|----------------|---------------|

| 1   | TIP                     | Line-side TIP  | 8                    | PT             | Protected TIP |

| '   | H                       | Line-side HF   | ie-side TIP   8   PT |                | to SLIC       |

| 2   | Vs                      | Supply voltage | 7                    | GND            | Ground        |

|     | to Gate                 | GIND           | around               |                |               |

| 3   | NC                      | No Internal    | 6                    | GND            | Ground        |

|     | 140                     | connection     | connection           |                | around        |

| 4   | 4 RING Line-side RING 5 |                | PR                   | Protected RING |               |

| 4   | THING                   | Line-side Hind | 3                    | iΠ             | to SLIC       |

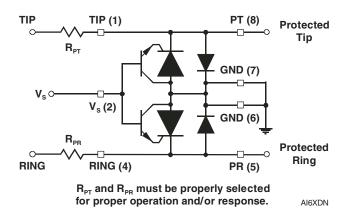

Note: Pins 1 and 4 must always be connected to the protection resistors shown in Figures 2 and 3 (Line Feed Circuitry). The SLIC can be connected either to the protected outputs (pins 5 and 8) or to the inputs (pins 1 and 4).

Positive overvoltages are clipped to ground by diode forward conduction. Negative overvoltages are initially clipped close to the SLIC negative supply rail value. If sufficient current is available from the overvoltage, then the protector will switch into a low voltage on-state condition. As the overvoltage subsides the high holding current of TISP6L7591 crowbar prevents d.c. latchup.

These monolithic protection devices are fabricated in ion-implanted planar vertical power structures for high reliability and in normal system operation they are virtually transparent. The TISP6L7591 is available in 8-pin plastic small-outline surface mount package.

#### **How To Order**

| Device     | Package                 | Carrier                  | For Standard<br>Termination Finish<br>Order As | For Lead Free<br>Termination Finish<br>Order As |

|------------|-------------------------|--------------------------|------------------------------------------------|-------------------------------------------------|

| TISP6L7591 | D (8-pin Small-Outline) | R (Embossed Tape Reeled) | TISP6L7591DR                                   | TISP6L7591DR-S                                  |

\*RoHS Directive 2002/95/EC Jan 27 2003 including Annex

MAY 2002 - REVISED FEBRUARY 2005

Specifications are subject to change without notice.

Customers should verify actual device performance in their specific applications.

# **TISP6L7591 SLIC Protector**

### BOURNS®

| Absolute Maximum Ratings, T <sub>A</sub> = 25 °C (Unless Otherwise Noted)                        |                                            |             |      |  |

|--------------------------------------------------------------------------------------------------|--------------------------------------------|-------------|------|--|

| Rating                                                                                           | Symbol                                     | Value       | Unit |  |

| Repetitive peak TIP or RING off-state voltage, $V_{(VS)(TIP)} = 0$ , $V_{(VS)(RING)} = 0$        | V <sub>(TIP)M</sub> , V <sub>(RING)M</sub> | -100        | V    |  |

| Repetitive peak V <sub>S</sub> voltage, V <sub>TIP</sub> = 0, V <sub>RING</sub> = 0              | V <sub>(VS)M</sub>                         | -80         | V    |  |

| Non-repetitive peak pulse current (see Notes 1, 2 and 3)                                         |                                            |             |      |  |

| 10/1000 μs (Bellcore GR-1089-CORE, open-circuit voltage wave shape 10/1000 μs)                   | 1                                          | 30          | Α    |  |

| 5/320 μs (ITU-T K.20 & K.21, open-circuit voltage wave shape 10/700 μs)                          | I <sub>PP</sub>                            | 40          | _ ^  |  |

| 2/10 μs (Bellcore GR-1089-CORE, open-circuit voltage wave shape 2/10 μs)                         |                                            | 80          |      |  |

| Non-repetitive peak on-state current, 50 Hz to 60 Hz (see Notes 1, 2 and 3)                      |                                            |             |      |  |

| 10 ms                                                                                            | I <sub>TSM</sub>                           | 5           | Α    |  |

| 1 s                                                                                              |                                            | 3.5         |      |  |

| Non-repetitive peak V <sub>S</sub> current, half sine wave 10 ms, cathodes commoned (see Note 1) | I <sub>(VS)M</sub>                         | +2          | Α    |  |

| Operating free-air temperature range                                                             | T <sub>A</sub>                             | -40 to +85  | °C   |  |

| Storage temperature range                                                                        | T <sub>stg</sub>                           | -40 to +125 | °C   |  |

- NOTES: 1. Initially the protector must be in thermal equilibrium. The surge may be repeated after the device returns to its initial conditions.

- 2. These non-repetitive rated currents are peak values for either polarity. The rated current values may be applied either to the Ring to Ground or to the Tip to Ground terminal pairs. Additionally, both terminal pairs may have their rated current values applied simultaneously (in this case the Ground terminal current will be twice the rated current value of an individual terminal pair).

- 3. Supply Voltage,  $V_S$ , range -20 V to -80 V.

| Electrica           | Electrical Characteristics, T <sub>A</sub> = 25 °C (Unless Otherwise Noted) |                                                               |                        |       |     |                     |      |

|---------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------|------------------------|-------|-----|---------------------|------|

|                     | Parameter Test Conditions                                                   |                                                               | Min                    | Тур   | Max | Unit                |      |

| V <sub>F</sub>      | Forward voltage                                                             | I <sub>P</sub> = 5 A, t <sub>P</sub> = 1 ms                   |                        |       |     | 3                   | V    |

| V <sub>FP</sub>     | Peak forward voltage                                                        | I <sub>PP</sub> = 30 A, 10/1000                               |                        |       |     | 15                  | V    |

| I <sub>GT</sub>     | Gate trigger current                                                        | V <sub>S</sub> = -48 V                                        |                        | 0.2   |     | 15                  | mA   |

| I <sub>H</sub>      | Holding current                                                             | $t_P = 10 \text{ ms}, V_S = -48 \text{ V}$                    |                        | -150  |     |                     | mA   |

| V <sub>T</sub>      | Trip voltage                                                                | d.c.                                                          |                        |       |     | V <sub>S</sub> -2.8 | V    |

| V <sub>SGL</sub>    | Dynamic trip voltage                                                        | I <sub>PP</sub> = -30 A, 10/1000, V <sub>S</sub> = -48 V      |                        |       |     | -63                 | V    |

| 1                   | Reverse gate current                                                        | $V_S = -75 \text{ V}, V_{TIP} = 0, V_{RING} = 0$              | T <sub>A</sub> = 25 °C |       |     | -5                  | μΑ   |

| I <sub>RG</sub>     | neverse gate current                                                        | VS = -73 V, VTIP = 0, VRING = 0                               | T <sub>A</sub> = 70 °C |       |     | -50                 | μΑ   |

| dv <sub>R</sub> /dt | Critical rate of voltage rise                                               | TIP or RING lead                                              |                        | ±1000 |     |                     | V/μs |

| V <sub>ON</sub>     | On-state voltage                                                            | $I_T = -0.5 \text{ A}, t_P = 1 \text{ ms}$                    |                        |       |     | -3                  | V    |

| VON                 | On-state voltage                                                            | $I_T = -3.0 \text{ A}, t_P = 1 \text{ ms}$                    |                        |       |     | -4                  | V    |

| I <sub>R</sub>      | Reverse current                                                             | $V_{R} = -85 \text{ V}, I_{G} = 0$                            | $T_A = 25  ^{\circ}C$  |       |     | -5                  | μΑ   |

| 'н                  | (Gate open) $V_R = -63 \text{ v, } I_G = 0$                                 |                                                               | T <sub>A</sub> = 70 °C |       |     | -50                 | μΑ   |

| C <sub>off</sub>    | TIP or RING to GND                                                          | $f = 1 \text{ MHz}, V_d = 1 \text{ V}, I_G = 0, (see Note 4)$ | V <sub>R</sub> = -3 V  |       |     | 50                  | pF   |

| Ооп                 | off-state capacitance                                                       | 1 - 1 Willi2, Vd - 1 V, IG - 0, (300 Note 4)                  | V <sub>R</sub> = -48 V |       |     | 40                  | pF   |

NOTE 4: These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The unmeasured device terminals are a.c. connected to the guard terminal of the bridge.

#### **Parameter Measurement Information**

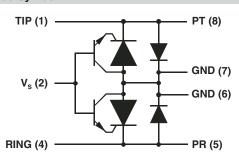

Figure 1. Typical Voltage-Current Characteristic of the SLIC Protector Unless Otherwise Noted, All Voltages are Referenced to the Anode

### **Letter Symbol Definitions**

| Symbol           | Parameter                                           |

|------------------|-----------------------------------------------------|

| I <sub>H</sub>   | Thyristor holding current                           |

| I <sub>GT</sub>  | Gate trigger current into V <sub>S</sub> pin        |

| Ι <sub>P</sub>   | Pulse current                                       |

| I <sub>PP</sub>  | Peak pulse current                                  |

| I <sub>RG</sub>  | Reverse current V <sub>S</sub> to TIP or RING       |

| I <sub>T</sub>   | TIP or RING current when thyristor is on            |

| I <sub>R</sub>   | Reverse current, TIP or RING to GND                 |

| V <sub>F</sub>   | Forward voltage, TIP or RING to GND                 |

| V <sub>FP</sub>  | Peak forward voltage, TIP or RING to GND            |

| V <sub>T</sub>   | Trip voltage, TIP or RING to V <sub>S</sub>         |

| $V_{SGL}$        | Dynamic trip voltage, TIP or RING to V <sub>S</sub> |

| V <sub>ON</sub>  | Thyristor on voltage at I <sub>T</sub>              |

| $V_R$            | TIP or RING voltage when thyristor is off           |

| C <sub>off</sub> | Off-state capacitance, TIP or RING to Ground        |

#### **APPLICATIONS INFORMATION**

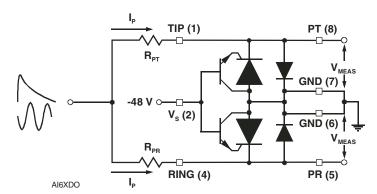

Figure 2. Standard Configuration

Figure 3. Test Circuit

# TISP6L7591 SLIC Protector

**BOURNS®**

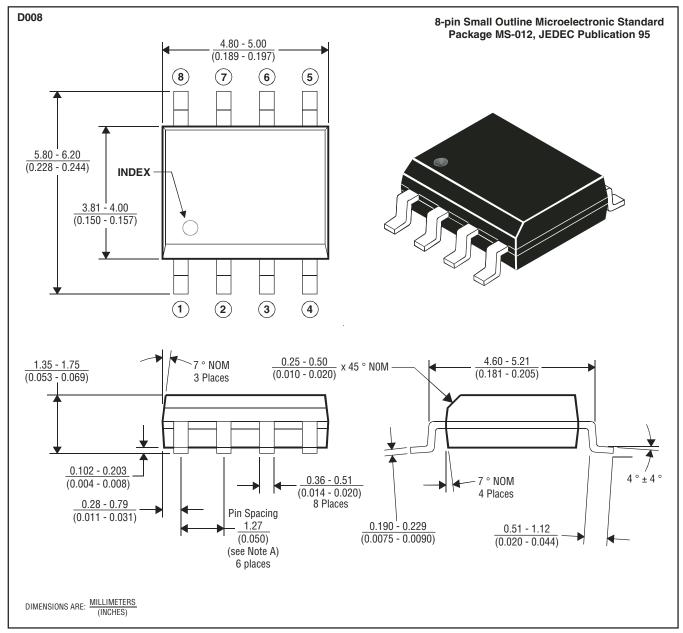

#### **MECHANICAL DATA**

#### **Device Symbolization Code**

Devices will be coded as below.

| Device      | Symbolization Code |

|-------------|--------------------|

| TISP6L7591D | L7591              |

#### **MECHANICAL DATA**

#### **D008 Plastic Small-outline Package**

This small-outline package consists of a circuit mounted on a lead frame and encapsulated within a plastic compound. The compound is designed to withstand normal soldering temperatures with no deformation and circuit performance characteristics will remain stable when operated in most high humidity conditions. Leads require no additional cleaning or processing when used in soldered assembly.

MDXXAAE

- NOTES: A. Leads are within 0.25 (0.010) radius of true position at maximum material condition.

- B. Body dimensions do not include mold flash or protrusion.

- C. Mold flash or protrusion shall not exceed 0.15 (0.006).

- D. Lead tips to be planar within ±0.051 (0.002).

#### **MECHANICAL DATA**

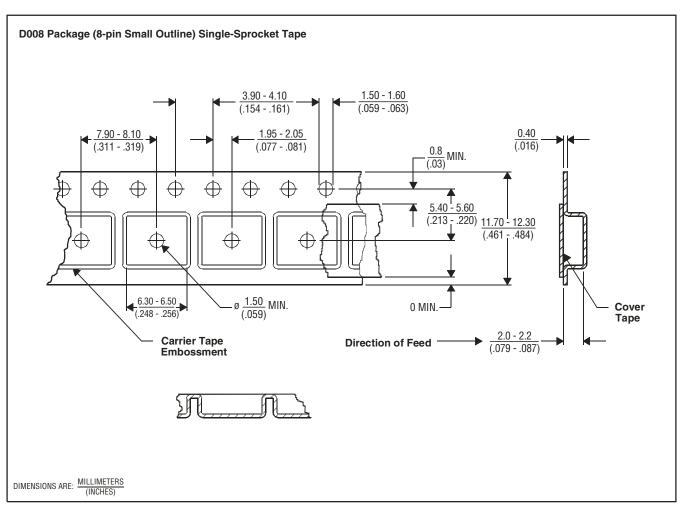

### **D008 Tape Dimensions**

NOTES: A. Taped devices are supplied on a reel of the following dimensions:-

**MDXXATC**

330 +0.0/-4.0 Reel diameter: (12.99 + 0.0 / -.157)

$100 \pm 2.0$ Reel hub diameter:  $\overline{(3.937 \pm .079)}$

$13.0 \pm 0.2$ Reel axial hole:  $(.512 \pm .008)$

B. 2500 devices are on a reel.

<sup>&</sup>quot;TISP" is a trademark of Bourns, Ltd., a Bourns Company, and is Registered in U.S. Patent and Trademark Office. "Bourns" is a registered trademark of Bourns, Inc. in the U.S. and other countries.