# VCSO BASED CLOCK GENERATOR

#### **GENERAL DESCRIPTION**

The M928-02 is a PLL (Phase Locked Loop) based

clock generator that uses an internal VCSO (Voltage Controlled SAW Oscillator) to produce a very low jitter output clock. From the M928-02-622.0800, an output clock frequency of 622.08MHz is provided from eight LVPECL clock

output pairs. (Other frequencies are available; consult factory.) The accuracy of the output frequency is assured by the internal PLL that phase-locks the internal VCSO to the reference input frequency (19.44MHz for the M928-02-622.0800). The input reference can either be an external crystal, utilizing the internal crystal oscillator, or a stable external clock source such as a packaged crystal oscillator.

#### **FEATURES**

- ◆ Output clock frequency range 300MHz to 700MHz (Consult factory for frequency availability)

- ◆ Eight identical LVPECL output pairs

- ♦ Jitter 0.7ps rms (@622.08MHz, over 12kHz-20MHz), typ.

- ◆ Ideal for OC-48/STM-16 clock reference

- ◆ Output-to-output skew < 100ps

- **◆ External XTAL or LVCMOS reference input**

- ◆ Integrated SAW (surface acoustic wave) delay line

- ♦ Single 3.3V power supply

- ◆ Small 9 x 9 mm SMT (surface mount) package

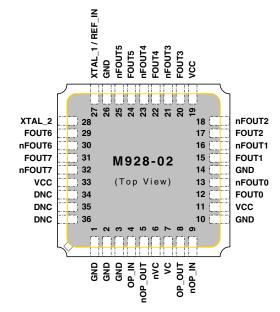

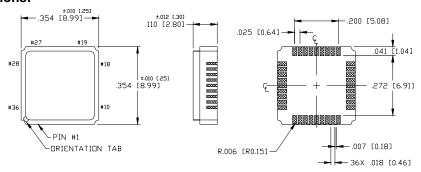

### PIN ASSIGNMENT (9 x 9 mm SMT)

Figure 1: Pin Assignment

# **Example Output Frequency Configurations** (M928-02-622.0800)

| Ref Clock<br>Frequency<br>(MHz) | PLL<br>Multiplication<br>Ratio | VCSO and<br>Output<br>Frequency<br>(MHz) | Application  |

|---------------------------------|--------------------------------|------------------------------------------|--------------|

| 19.44                           | 32                             | 622.08                                   | OC-48/STM-16 |

**Table 1: Example Output Frequency Configurations**

#### SIMPLIFIED BLOCK DIAGRAM

### M928-02-622.08 (Other Frequencies Available) **VSCO External** LVPECL Crystal Frequency XTAL Output or Multiplying osc **Clock Pairs** Reference **PLL** (622.08MHz) Clock Input (19.44MHz) External Loop Filter

Figure 2: Simplified Block Diagram

M928-02 Datasheet Rev 0.4 Revised 30Jul2004

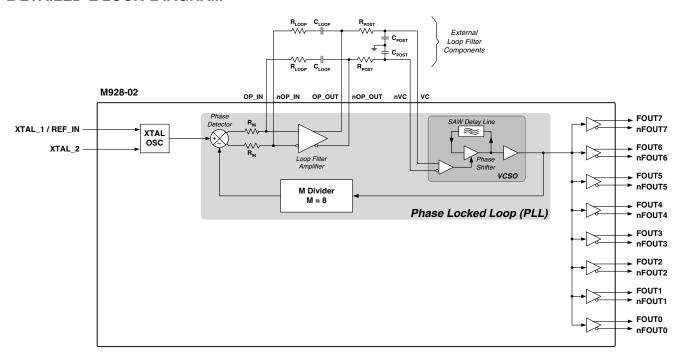

### **DETAILED BLOCK DIAGRAM**

Figure 3: Detailed Block Diagram

# **PIN DESCRIPTIONS**

| Number              | Name              | I/O      | Configuration          | Description                                                                                       |

|---------------------|-------------------|----------|------------------------|---------------------------------------------------------------------------------------------------|

| 1, 2, 3, 10, 14, 26 | GND               | Ground   |                        | Power supply ground connections.                                                                  |

| 4 9                 | OP_IN<br>nOP_IN   | Input    |                        |                                                                                                   |

| 5<br>8              | nOP_OUT<br>OP_OUT | Output   | _                      | External loop filter connections. See Figure 5.                                                   |

| 6<br>7              | nVC<br>VC         | Input    | _                      |                                                                                                   |

| 11, 19, 33          | VCC               | Power    |                        | Power supply connection, connect to +3.3V.                                                        |

| 12, 13              | FOUT0, nFOUT0     |          |                        |                                                                                                   |

| 15, 16              | FOUT1, nFOUT1     | =        |                        |                                                                                                   |

| 17, 18              | FOUT2, nFOUT2     | _        |                        |                                                                                                   |

| 20, 21              | FOUT3, nFOUT3     | - Output | No internal terminator | Clock output pairs, differential LVPECL output                                                    |

| 22, 23              | FOUT4, nFOUT4     | – Output | No internal terminator | ·                                                                                                 |

| 24, 25              | FOUT5, nFOUT5     | _        |                        | (622.08 MHz for the <b>M928-02-622.0800</b> )                                                     |

| 29, 30              | FOUT6, nFOUT6     | _        |                        |                                                                                                   |

| 31, 32              | FOUT7, nFOUT7     | _        |                        |                                                                                                   |

| 27                  | XTAL_1 / REF_IN   | Input    |                        | External crystal connection. Also accepts LVCMOS/LVTTL compatible clock source.                   |

| 28                  | XTAL_2            | Input    |                        | External crystal connection. Leave unconnected when driving pin 27 with external clock reference. |

| 34, 35, 36          | DNC               |          | Do Not Connect.        | Internal nodes. Connection to these pins can cause erratic device operation.                      |

Table 2: Pin Descriptions

### **FUNCTIONAL DESCRIPTION**

The M928-02 is a PLL (Phase Locked Loop) based clock generator that generates output clocks synchronized to an input reference clock.

The M928-02 combines the flexibility of a VCSO (Voltage Controlled SAW Oscillator) with the stability of a crystal oscillator.

#### **Input Reference**

The 19.44MHz input reference can either be an external, discrete crystal device or a stable external clock source such as a packaged crystal oscillator:

- If an external crystal is used with the on-chip crystal oscillator circuit (XTAL OSC), the external crystal should be a parallel-resonant, fundamental mode crystal. Apply it to the XTAL\_1 / REF\_IN and XTAL\_2 input pins. External crystal load capacitors are also required.

- If an external LVCMOS/LVTTL clock source is used, apply it to the XTAL\_1 / REF\_IN input pin.

In either case, the reference clock is supplied directly to the phase detector of the PLL.

#### The PLL

The PLL (Phase Locked Loop) includes the phase detector, the VCSO, and a feedback divider (labeled "M Divider").

The feedback divider is a digital circuit that divides the VCSO output frequency by a numerical value "M" in order to match the input reference frequency.

By controlling the frequency and phase of the VCSO, the phase detector precisely locks the frequency and phase of the feedback divider output to that of the input reference. This creates an output frequency that is a multiple of the reference frequency (which is output from the VCSO).

The relationship between the VCSO output frequency, the M Divider, and the input reference frequency is defined as follows:

$$Fvcso = M \times Fxtal$$

For the M928-02-622.0800 (see "Ordering Information" on pg. 6):

- VCSO output frequency = 622.08MHz

- M = 32

- Input reference frequency = 19.44MHz

Therefore, for the M928-02-622.0800:

$$622.08MHz = 32 \times 19.44MHz$$

The VCSO center output frequency of 622.08MHz enables the product of  $M \times$  input crystal frequency to fall within the lock range of the VCSO.

# **APPLICATION INFORMATION**

This section includes information on the optional external crystal and on the external loop filter.

The subsections on the loop filter provide example component values and also briefly describe the SAW PLL simulator tool and additional application information available at www.icst.com.

#### **External Crystal Specifications**

If an external crystal is used with the on-chip crystal oscillator circuit (XTAL OSC), the external crystal should have the following general specifications:

#### Crystal Specifications

|                | Parameter                                | Min     | Тур    | Max  | Unit |

|----------------|------------------------------------------|---------|--------|------|------|

|                | Crystal Type                             | AT-c    | cut qu | artz |      |

|                | Mode of Oscillation                      | Fun     | dame   | ntal |      |

| f <sub>0</sub> | Frequency Range                          | 16      |        | 40   | MHz  |

| ESR            | Equivalent Series Resistance             | е       |        | 50   | Ω    |

|                | Spurious Response (non-ha                | rmonic) |        | -40  | dBc  |

| C <sub>L</sub> | Load Capacitance, parallel load resonant | 16      |        | 32   | pF   |

| P <sub>0</sub> | Drive Level                              | 0.1     |        | 1.0  | mW   |

Table 3: Crystal Specifications

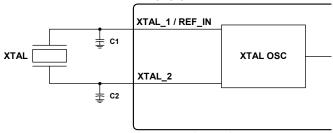

The external crystal will be applied to the XTAL\_1 / REF\_IN and XTAL\_2 input pins. External crystal load capacitors are also required.

# Recommended External Crystal Configuration M928-02

Figure 4: Recommended External Crystal Configuration

XTAL Load Capacitance Specification = 18 pF C1 = 27 pF

$C2 = 33 \, pF$

External load capacitors C1 and C2 present a load of 15 pf to the crystal (they are seen in series by the crystal through the common ground connection). With the additional of PCB trace capacitance and M928-02 input capacitance, the total load to the crystal is about 18 pf.

#### **External Loop Filter**

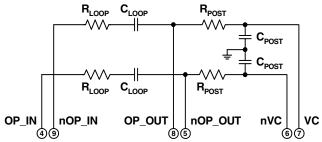

To provide stable PLL operation, and thereby a low jitter output clock, the M928-02 requires the use of an external loop filter. This is provided via the provided filter pins (see Figure 5).

Figure 5: External Loop Filter

The loop filter is implemented as a differential circuit to minimize system noise interference. Due to the differential signal path design, the implementation requires two identical complementary RC filters as shown here.

See Table 4, Example External Loop Filter Component Values, below.

#### **Example External Loop Filter Component Values**

| PLL Bandwidth (kHz) | Damping<br>Factor | R loop<br>(kΩ) | C loop<br>(μF) | R post<br>(kΩ) | C post<br>(pF) |

|---------------------|-------------------|----------------|----------------|----------------|----------------|

| 0.395               | 2.0               | 1.5            | 4.70           | 20             | 3300           |

| 1.2                 | 2.9               | 4.7            | 1.00           | 20             | 1000           |

| 10 <sup>1</sup>     | 2.4               | 39.0           | 0.01           | 20             | 240            |

Table 4: Example External Loop Filter Component Values

Note 1: Recommended for minimum output jitter when using a crystal or crystal oscillator reference.

Refer to the M928-02 product web page at www.icst.com/products/summary/m928-02.htm for additional product information.

#### **PLL Simulator Tool Available**

A free PC software utility is available on the ICS website (www.icst.com). The M2000 Timing Modules PLL Simulator is a downloadable application that simulates PLL jitter and wander transfer characteristics. This enables the user to set appropriate external loop component values in a given application.

Refer to the SAW PLL Simulator Software web page at www.icst.com/products/calculators/m2000filterSWdesc.htm for additional information.

# ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Symbol          | Parameter            | Rating                       | Unit |

|-----------------|----------------------|------------------------------|------|

| V <sub>I</sub>  | Inputs               | -0.5 to $V_{\rm CC}$ +0.5    | V    |

| V <sub>o</sub>  | Outputs              | -0.5 to V <sub>CC</sub> +0.5 | ٧    |

| V <sub>cc</sub> | Power Supply Voltage | 4.6                          | V    |

| T <sub>s</sub>  | Storage Temperature  | -45 to +100                  | °C   |

**Table 5: Absolute Maximum Ratings**

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in Recommended Conditions of Operation, DC Characteristics, or AC Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

# **RECOMMENDED CONDITIONS OF OPERATION**

| Symbol          | Parameter               |            | Min   | Тур | Max   | Unit |

|-----------------|-------------------------|------------|-------|-----|-------|------|

| V <sub>CC</sub> | Positive Supply Voltage | Э          | 3.135 | 3.3 | 3.465 | V    |

| TΔ              | Ambient Operating Te    | nperature  |       |     |       |      |

| , A             |                         | Commercial | 0     |     | +70   | °C   |

|                 |                         | Industrial | -40   |     | +85   | °C   |

Table 6: Recommended Conditions of Operation

# **ELECTRICAL SPECIFICATIONS**

#### **DC Characteristics**

Unless stated otherwise,  $V_{CC}$  = 3.3V  $\pm 5\%$ ,  $T_A$  = 0 °C to +70 °C (commercial),  $T_A$  = -40 °C to +85 °C (industrial),  $F_{VCSO}$  = 622.08MHz,  $T_A$  LVPECL outputs terminated with 50 $\Omega$  to  $T_{CC}$  - 2V

| ;                                      | Symbol           | Parameter                   |                       | Min                  | Тур | Max                  | Unit |

|----------------------------------------|------------------|-----------------------------|-----------------------|----------------------|-----|----------------------|------|

| Power Supply                           | $V_{CC}$         | Positive Supply Voltage     |                       | 3.135                | 3.3 | 3.465                | V    |

|                                        | I <sub>cc</sub>  | Power Supply Current        | -                     |                      | 375 |                      | mA   |

| Reference                              | $V_{IH}$         | Input High Voltage          |                       | $(V_{cc}/2)+0.5$     |     | V <sub>cc</sub> +0.3 | V    |

| Clock<br>Input                         | V <sub>IL</sub>  | Input Low Voltage           | XTAL_1 / REF_IN       | -0.3                 |     | $(V_{cc}/2)+0.5$     | V    |

| mput                                   | I <sub>IH</sub>  | Input High Current          | (XTAL_2 disconnected) |                      |     | 150                  | μΑ   |

|                                        | I <sub>IL</sub>  | Input Low Current           | -                     | -5.0                 |     |                      | μΑ   |

| Crystal or<br>Reference<br>Clock Input | C <sub>IN</sub>  | Input Capacitance           | XTAL_1 / REF_IN       |                      |     | 4                    | pF   |

| Differential                           | V <sub>OH</sub>  | Output High Voltage         |                       | V <sub>CC</sub> -1.4 |     | V <sub>cc</sub> -1.0 | V    |

| Output                                 | V <sub>OL</sub>  | Output Low Voltage          | FOUT, nFOUT (0-7)     | V <sub>CC</sub> -2.0 |     | V <sub>cc</sub> -1.7 | V    |

|                                        | V <sub>P-P</sub> | Peak to Peak Output Voltage | -                     | 0.6                  |     | 0.85                 | V    |

Note 1: For other VCSO center frequencies, contact ICS

#### Table 7: DC Characteristics

#### **AC Characteristics**

Unless implied otherwise,  $V_{CC}$  = 3.3V  $\pm 5\%$ ,  $T_A$  = 0 °C to +70 °C (commercial),  $T_A$  = -40 °C to +85 °C (industrial),  $F_{VCSO}$  = 622.08MHz, <sup>1</sup> LVPECL outputs terminated with 50 $\Omega$  to  $V_{CC}$  - 2V

| Symbol           | Parameter               |                     | Min          | Тур          | Max | Unit   | Test Conditions |

|------------------|-------------------------|---------------------|--------------|--------------|-----|--------|-----------------|

| F <sub>OUT</sub> | Output Frequency Rang   | је                  | 300          |              | 700 | MHz    |                 |

| F <sub>IN</sub>  | Nominal Input Frequenc  | cy, XTAL_1 / REF_IN |              | 19.44        |     | MHz    |                 |

| APR              | VCSO Pull-Range         |                     | <u>+</u> 100 | <u>+</u> 150 |     | ppm    |                 |

| Φn               | Single Side Band        | 1kHz Offset         |              | -100         |     | dBc/Hz |                 |

|                  | Phase Noise             | 10kHz Offset        |              | -110         |     | dBc/Hz |                 |

|                  | @622.08MHz              | 100kHz Offset       |              | -134         |     | dBc/Hz |                 |

| J(t)             | Jitter (rms)            |                     |              | 0.7          | 1.0 | ps     | 12kHz to 20MHz  |

| t <sub>DC</sub>  | Output Duty Cycle, High | n Time              | 45           | 50           | 55  | %      |                 |

| t <sub>R</sub>   | Output Rise Time        | FOUT, nFOUT (0-7)   | 200          | 275          | 350 | ps     | 20% to 80%      |

| t <sub>F</sub>   | Output Fall Time        | FOUT, nFOUT (0-7)   | 200          | 275          | 350 | ps     | 20% to 80%      |

| t <sub>s</sub>   | Output Skew             | Between Any Pair    |              |              | 100 | ps     |                 |

Note 1: For other VCSO center frequencies, contact ICS

Table 8: AC Characteristics

#### DEVICE PACKAGE - 9 x 9mm CERAMIC LEADLESS CHIP CARRIER **Mechanical Dimensions:**

Refer to the SAW PLL application notes web page at www.icst.com/products/appnotes/SawPIIAppNotes.htm for application notes, including recommended PCB footprint, solder mask, and furnace profile.

- 1. DIMENSIONS ARE IN INCHES, DIMENSIONS

- IN [ ] ARE MM

- 2. UNLESS OTHERWISE SPECIFIED ALL DIMENSIONS ARE  $\pm .005$  [.13]

Figure 6: Device Package - 9 x 9mm Ceramic Leadless Chip Carrier

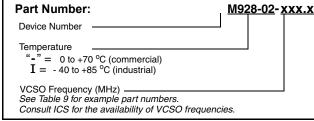

#### ORDERING INFORMATION

#### **Part Numbering Scheme**

Figure 7: Part Numbering Scheme

#### **Example Part Numbers**

| For Output Frequencies (MHz) | Temperature | Order Part Number |

|------------------------------|-------------|-------------------|

| 622.08                       | commercial  | M928-02-622.0800  |

| 022.00                       | industrial  | M928-02I622.0800  |

| 300 to 700                   | commercial  | M928-02-xxx.xxxx  |

| 300 10 700                   | industrial  | M928-02Ixxx.xxxx  |

Table 9: Example Part Numbers

Consult ICS for the availability of VCSO frequencies

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems (ICS) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any ICS product for use in life support devices or critical medical instruments.