TOSHIBA

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

## T6A04A

### COLUMN AND ROW DRIVER LSI FOR A DOT MATRIX GRAPHIC LCD

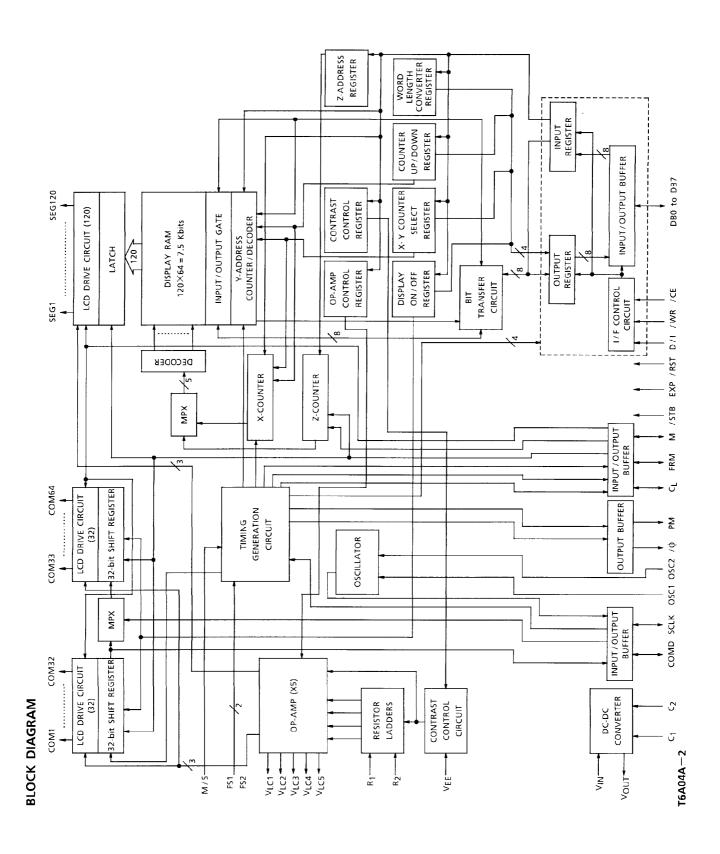

The TOSHIBA T6A04A is a driver for a small-or mediumscale dot matrix graphic LCD. It includes the functions of the TOSHIBA T9841B (column driver) and the TOSHIBA T9842B (row driver). It has an 8-bit interface circuit and can be operated with an 80-Series MPU. It generates all the timing signals for the display with an on-chip oscillator. It receives 8-bit data from an MPU, latches the data to an on-chip RAM, and displays the image on the LCD (the data in the display RAM correspond to the dots on the display). The device has 120 column driver outputs and 64 row driver outputs enabling it to drive a 120-dot by 64-dot LCD. In addition, there are resistors to divide the bias voltage, a power supply op-amp, DC-DC converter  $(+5V\rightarrow -5V)$  and contrast control circuit, enabling the LCD to be driven by a single power supply. The device can be connected to another T6A04A to drive a 240-dot by 64-dot LCD.

|                              |      | Unit: mm |  |  |  |  |  |  |

|------------------------------|------|----------|--|--|--|--|--|--|

| T6A04A                       | LEAD | PITCH    |  |  |  |  |  |  |

| 10A04A                       | IN   | OUT      |  |  |  |  |  |  |

| (UAW, 6NS)                   | 1.0  | 0.28     |  |  |  |  |  |  |

| Please contact Toshiba or an |      |          |  |  |  |  |  |  |

authorized Toshiba dealer for information on package dimensions.

TCP (Tape Carrier Package)

### **FEATURES**

- On-chip display RAM capacity:  $120 \times 64 = 7.5$  Kbits

- Display RAM data

- ① Display data = 1 ..... LCD turns on.

- ② Display data = 0 ...... LCD turns off.

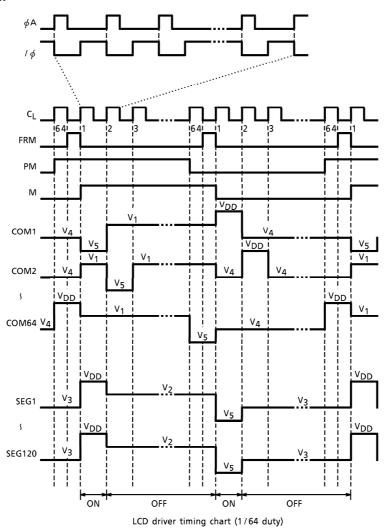

- 1/64 duty cycle

- Word length of display data can be switched between eight bits and six bits according to the character font.

- LCD driver outputs: 120 column driver outputs and 64 row driver outputs

- Interface with 80-Series MPU

- On-chip oscillator with one external resistor

- Low power consumption

- On-chip resistors to divide bias voltage, on-chip operational amplifier for LCD supply, on-chip DC-DC converter, on-chip contrast control circuit

- CMOS process

- Operating voltage: 4.5 to 5.5V

- Operating voltage for LCD drive signal:  $V_{DD} V_{EE} = 16.0V$  (max)

- Package: TCP (Tape Carrier Package)

980910EBE2

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

Polyimide base film is hard and thin. Be careful not to injure yourself on the film or to scratch any other parts with the film. Try to design and manufacture products so that there is no chance of users touching the film after assembly, or if they do , that there is no chance of them injuring themselves. When cutting out the film, try to ensure that the film shavings do not cause accidents. After use, treat the leftover film and reel spacers as industrial waste.

Light striking a semiconductor device generates electromotive force due to photoelectric effects. In some cases this can cause the device to malfunction.

- malfunction This is especially true for devices in which the surface (back), or side of the chip is exposed. When designing circuits, make sure that devices are protected against incident light from external sources. Exposure to light both during regular operation and during inspection must be taken into

- account. The products described in this document are subject to the foreign exchange and foreign trade laws. The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

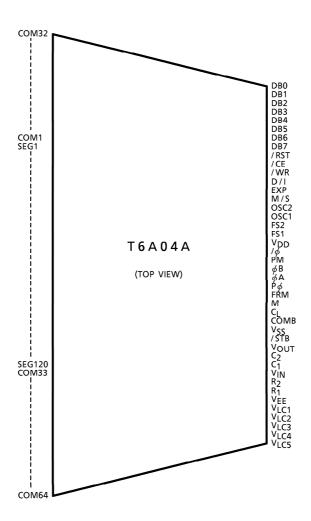

### **PIN ASSIGNMENT**

(\*) The Above diagram shows the pin configuration of the LSI chip; it does not show the configuration of the tape carrier package.

### **PIN FUNCTIONS**

| PIN NAME       | 1/0    | FUNCTIONS                                                                                                                                                                                                                                                                                                                                                               |

|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEG1 to SEG120 | Output | Column driver output                                                                                                                                                                                                                                                                                                                                                    |

| 3231 13 323123 | Gutput | Row driver output                                                                                                                                                                                                                                                                                                                                                       |

| COM1 to COM64  | Output | <ul> <li>Disable expansion mode (EXP = L, M/S = H)         → COM1 to COM64 are enabled.</li> <li>Enable expansion mode/master mode (EXP = H, M/S = H)         → COM1 to COM32 are enabled and COM33 to COM64 are disabled.</li> <li>Enable expansion mode/slave mode (EXP = H, M/S = L)         → COM1 to COM32 are disabled and COM33 to COM64 are enabled.</li> </ul> |

| CL             | 1/0    | Input/output for shift clock pulse  ■ Master mode (M/S=H)→Output  ■ Slave mode (M/S=L)→Input                                                                                                                                                                                                                                                                            |

| М              | 1/0    | Input/output for frame signal  ■ Master mode (M/S=H)→Output  ■ Slave mode (M/S=L)→Input                                                                                                                                                                                                                                                                                 |

| FRM            | 1/0    | Input/output for display synchronous signal  ■ Master mode (M/S=H)→Output  ■ Slave mode (M/S=L)→Input                                                                                                                                                                                                                                                                   |

| Ρφ, φΑ, φΒ     | 1/0    | Input / output system clock signal  ■ Master mode (M / S = H) → Output  ■ Slave mode (M / S = L) → Input                                                                                                                                                                                                                                                                |

| COMD           | 1/0    | Input/output row signal data  ■ Master mode (M/S=H)→Output  ■ Slave mode (M/S=L)→Input                                                                                                                                                                                                                                                                                  |

| DB0 to DB7     | 1/0    | Data bus                                                                                                                                                                                                                                                                                                                                                                |

| D/I            | Input  | Input for data/instruction select signal  ■ D/I=H→ indicates that the data on DB0 to DB7 is display data.  ■ D/I=L→ indicates that the data on DB0 to DB7 is control data.                                                                                                                                                                                              |

| /WR            | Input  | Input for write select signal                                                                                                                                                                                                                                                                                                                                           |

| / CE           | Input  | Input for chip enable signal                                                                                                                                                                                                                                                                                                                                            |

| / RST          | Input  | Input for reset signal  ◆ /RST = L→Reset state                                                                                                                                                                                                                                                                                                                          |

| / STB          | Input  | Input for standby signal  ■ Usually connected to V <sub>DD</sub> ■ /STB = L→ T6A04A is in standby state and cannot accept any commands or data.  Column driver signal and row driver signal are at the V <sub>DD</sub> level                                                                                                                                            |

| FS1, FS2       | Input  | Input for frequency selection                                                                                                                                                                                                                                                                                                                                           |

| PIN NAME                             | 1/0      | FUNCTIONS                                                                                                                                                                  |                      |                |         |  |  |  |  |  |

|--------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|---------|--|--|--|--|--|

| EXP                                  | Input    | <ul> <li>Input for expansion mode selection</li> <li>M/S=H→ enables expansion mode. Two chips</li> <li>M/S=L→ disables expansion mode.</li> </ul>                          | can be               | used to        | gether. |  |  |  |  |  |

| M/S                                  | Input    | <ul> <li>Input for master/slave selection</li> <li>M/S=H→T6A04A is master chip.</li> <li>M/S=L→T6A04A is slave chip.</li> </ul>                                            |                      |                |         |  |  |  |  |  |

| OSC1, OSC2                           | _        | When using the internal clock oscillator, connect a resistor between OSC1 and OSC2.  When using an external clock, connect the clock as input to OSC1 and leave OSC2 open. |                      |                |         |  |  |  |  |  |

|                                      |          | Input for LCD drive bias selection  LCD drive bias selection is shown in the                                                                                               | R <sub>2</sub>       | R <sub>1</sub> | Bias    |  |  |  |  |  |

|                                      |          | following table                                                                                                                                                            | 0                    | 0              | 1/6     |  |  |  |  |  |

| R <sub>1</sub> , R <sub>2</sub>      | _        |                                                                                                                                                                            | 0                    | 1              | 1/7     |  |  |  |  |  |

|                                      |          |                                                                                                                                                                            | 1                    | 0              | 1/8     |  |  |  |  |  |

|                                      |          |                                                                                                                                                                            | 1                    | 1              | 1/9     |  |  |  |  |  |

| C <sub>1</sub> , C <sub>2</sub>      | <b> </b> | Connected by a capacitor for DC-DC converter                                                                                                                               |                      |                |         |  |  |  |  |  |

| V <sub>IN</sub>                      | _        | Input for DC-DC converter. Connect to V <sub>DD</sub> .                                                                                                                    |                      |                |         |  |  |  |  |  |

| Vout                                 | _        | DC-DC converter output                                                                                                                                                     |                      |                |         |  |  |  |  |  |

| V <sub>EE</sub>                      | _        | Power supply for LCD driver circuit  When using on-chip DC-DC converter, connect '                                                                                         | V <sub>EE</sub> to ' | Vout           |         |  |  |  |  |  |

| V <sub>LC1</sub> to V <sub>LC5</sub> | _        | When using on-chip DC-DC converter, connect V <sub>EE</sub> to V <sub>OUT</sub> Power supply for LCD driver circuit  M/S=H→ bias voltage output  M/S=L→ bias voltage input |                      |                |         |  |  |  |  |  |

| $V_{DD}$                             | _        | Power supply for logic circuit                                                                                                                                             |                      |                |         |  |  |  |  |  |

| V <sub>SS</sub>                      |          | Ground: Reference                                                                                                                                                          |                      |                |         |  |  |  |  |  |

| PM                                   | _        | Pre-frame signal for TOSHIBA T9841B                                                                                                                                        |                      |                |         |  |  |  |  |  |

| Ι φ                                  | _        | Output system clock for TOSHIBA T9841B                                                                                                                                     |                      |                |         |  |  |  |  |  |

### **FUNCTION OF EACH BLOCK**

### Interface logic

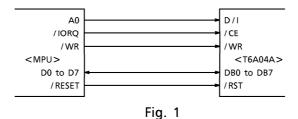

The T6A04A can be operated with an 80-Series MPU.

Fig. 1 shows an example of the interface.

### Input register

This register stores 8-bit data from the MPU. The D/I signal distinguishes between command data and display data.

### • Output register

This register stores 8-bit data from the display RAM. When display data is read, the display data specified by the address in the address counter is stored in this register. After that, the address is automatically incremented or decremented. Therefore, when an address is set, the correct data does not appear as the first data item that is read. The data in the specified address location appears as the second data item that is read.

### X-address counter

The X-address counter is a 64-up/down counter. It holds the row address of a location in the display RAM.

Writing data to or reading data from the display RAM causes the X-address to be automatically incremented or decremented.

### Y-(page) address counter

The Y-(Page) address counter is either a 15-up/down counter, when the word length is eight bits, or a 20-up/down counter, when the word length is six bits. It holds the column address of a location in the display RAM. Writing data to or reading data from the display RAM causes the Y-address to be automatically incremented or decremented.

### Z-address counter

The Z-address counter is a 64-up counter that provides the display RAM data for the LCD drive circuit. The data stored in the Z-address register is sent to the Z-address counter as the Z start address.

For instance, when the Z start address is 32, the counter increments as follows: 32, 33, 34 ..., 62, 63, 0, 1, 2 ... 30, 31, 32. Therefore, the display start line is line 32 of the display RAM.

### Up/down register

The 1-bit datum stored in this register selects either Up or Down mode for the X-and Y-(Page) address counters.

### Counter select register

The 1-bit datum stored in this register selects the X-address counter or Y-(Page) address counter.

### • Display ON/OFF register

This 1-bit register holds the display ON/OFF state. In the OFF state, the output data from the display RAM is cleared. In the ON state, the display RAM data is displayed. The display ON/OFF state does not affect the data in the display RAM.

### Z-address register

This 6-bit register holds the data which specifies the display start line. The data is loaded into the Z-address counter on the FRM signal. Using the Z-address register, vertical scrolling is possible.

### Word length register

The 1-bit datum stored in this register selects the word length: eight bits per word or six bits per word.

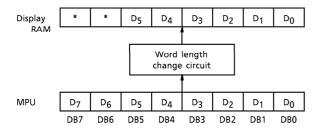

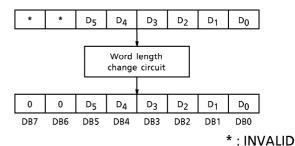

### • Word length change circuit

This circuit is controlled by the word length register. when the word length is eight bits, data is transferred eight bits at a time. When the word length is six bits, the data transfer method is shown in Fig. 2 as follows:

Fig. 2

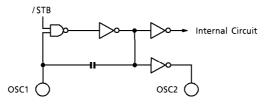

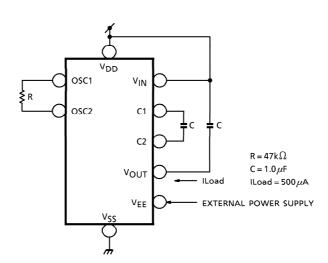

### Oscillator

The T6A04A includes an on-chip oscillator. When using this oscillator, connect an external resistor between OSC1 and OSC2, as shown in Fig. 3. When using an external clock, connect the clock input to OSC1 and leave OSC2 open.

Fig. 3

### • Timing generation circuit

This circuit divides the signals from the oscillator and generates the display timing signals and the operating clock signal.

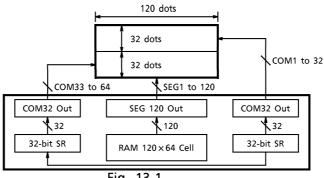

### • Shift register

The T6A04A has two 32-bit shift registers. In disable expansion mode, both the shift registers are enabled. These two 32-bit shift registers can be combined to form a 64-bit shift register. In enable expansion mode the 32-bit shift register for COM1 to COM32 is enabled in master chip mode, and the 32-bit shift register for COM33 to COM64 is enabled in slave chip mode.

### • Latch circuit

The latch circuit latches data from the display RAM on the rising edge of the C<sub>L</sub> signal.

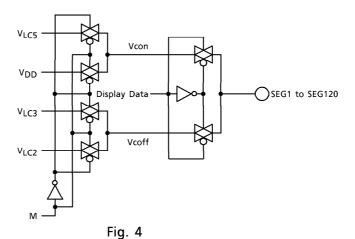

### Column driver circuit

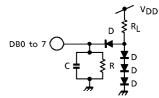

The column driver circuit consists of 120 driver circuits. One of the four LCD driving levels is selected by the combination of the M signal and the display data transferred from the latch circuit. Details of the column driver circuit are shown in Fig. 4.

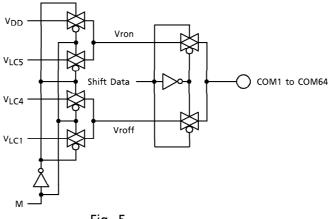

### Row driver circuit

The row driver circuit consists of 64 driver circuits. One of the four LCD driving levels is selected by the combination of the M signal and the data from the shift-register. Details of the row driver circuit are shown in Fig. 5.

Fig. 5

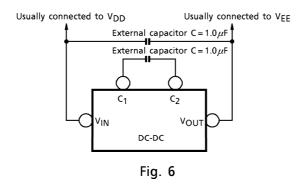

### DC-DC converter

The T6A04A has an on-chip DC-DC converter. When +5V is applied to  $V_{IN}$ , the DC-DC converter generates -5V at  $V_{OUT}$ . The voltage from  $V_{OUT}$  will drop due to the load current for  $V_{EE}$ . This characteristic is defined in "Electrical Characteristics".

Normally the value of external capacitors is  $1.0\mu\text{F}$ ; this value may need some adjustment according to the application. When the T6A04A is in standby state,  $V_{\text{OUT}} = 0V$ . See Fig. 6.

When using an external power supply, input the voltage to V<sub>EE</sub> and leave the C1, C2 V<sub>OUT</sub> pins open.

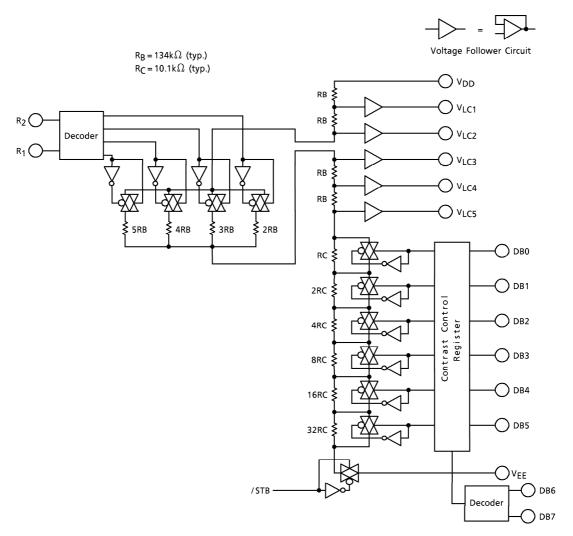

• Voltage divider resistors, contrast control circuit

The T6A04A has on-chip resistors which include op-amps, that divide the bias voltage, and a contrast control circuit. The voltage bias is modified by the values of  $R_1$  and  $R_2$ . One of four biases can be selected. These resistors and the contrast control circuit are shown in Fig. 7 below.

Fig. 7

### • Op-amp, op-amp control register

The T6A04A has five operational amplifiers which determine the LCD driving level. The power supplied by these op-amps is modified by the contents of the op-amp control register to match the LCD panel. The op-amp can also be controlled in such a way that it supplies full current on the rising edge of C<sub>1</sub> and a reduced current otherwise.

To maintain good LCD contrast, connect a capacitor between the op-amp output and  $V_{DD}$ . The value of the capacitor should normally be in the range 0.1 to  $1.0\mu F$ .

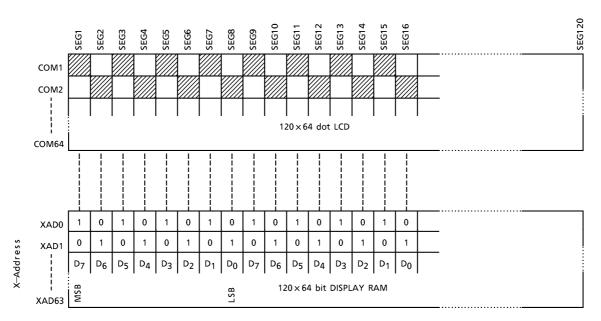

### Display RAM

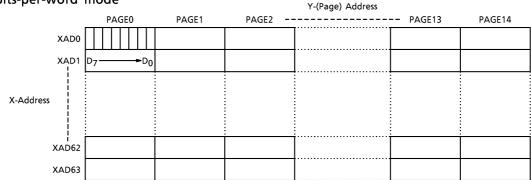

The display RAM consists of 64 rows x 120 columns for a total of 7680 cells. It is directly bit-mapped to the LCD. The relation between the display RAM and LCD is shown in Fig. 8.

When the word length is set to eight bits, the display RAM is arranged in 15 pages and each page contains 64 words. When the word length is set to six bits, the display RAM is arranged in 20 pages and each page contains 64 words. See Fig. 8.

Fig. 8

### (2) 6-bits-per-word mode

Fig. 9

### **COMMAND DEFINITIONS**

| COMMAND<br>NAME | D/I | /WR | DB7 | DB6 | DB5        | DB4   | DB3   | DB2   | DB1     | DB0 | FUNCTION                                                            |

|-----------------|-----|-----|-----|-----|------------|-------|-------|-------|---------|-----|---------------------------------------------------------------------|

| DPE             | 0   | 0   | 0   | 0   | 0          | 0     | 0     | 0     | 1       | 1/0 | Display ON (1) / OFF (0)                                            |

| 86E             | 0   | 0   | 0   | 0   | 0          | 0     | 0     | 0     | 0       | 1/0 | Word Length: 8 bits (1) / 6 bits (0)                                |

| UDE             | 0   | 0   | 0   | 0   | 0          | 0     | 0     | 1     | 1/0     | 1/0 | Counter Select : DB1 Y (1)/X (0) Mode Select : DB0 UP (1)/ DOWN (0) |

| CHE             | 0   | 0   | 0   | 0   | 0          | 1     | 1     | *     | *       | *   | Test Mode Select                                                    |

| OPA1            | 0   | 0   | 0   | 0   | 0          | 1     | 0     | *     | 1/0     | 1/0 | Op-amp Power Control 1                                              |

| OPA2            | 0   | 0   | 0   | 0   | 0          | 0     | 1     | *     | 1/0     | 1/0 | Op-amp Power Control 2                                              |

| SYE             | 0   | 0   | 0   | 0   | 1          | Y-(Pa | ge) A | ddres | s (0 to | 19) | Y-(Page) Address Set                                                |

| SZE             | 0   | 0   | 0   | 1   |            | Z-Ac  | dress | (0 to | 63)     |     | Z-Address Set                                                       |

| SXE             | 0   | 0   | 1   | 0   |            | X-Ac  | dress | (0 to | 63)     |     | X-Address Set                                                       |

| SCE             | 0   | 0   | 1   | 1   | CON        | TRAS  | r con | ITROL | (0 tc   | 63) | Contrast Set                                                        |

| STRD            | 0   | 1   | В   | 8/6 | D          | R     | 0     | 0     | Y/X     | U/D | Status Read                                                         |

| DAWR            | 1   | 0   |     |     | Write Data |       |       |       |         |     | Display Data Write                                                  |

| DARD            | 1   | 1   |     |     | Read Data  |       |       |       |         |     | Display Data Read                                                   |

<sup>\*:</sup> INVALID

### • Display ON/OFF select (DPE)

| /WR | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   |

Display ON (03H) Display OFF (02H)

This command turns display ON/OFF. It does not affect the data in the display RAM.

(Note) An L input on / RST turns display OFF.

### • Word length 8 bits/6 bits select (86E)

| /WR | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

8 Bits/Word Mode (01H)

6 Bits/Word Mode (00H)

This command sets the word length for display RAM data to eithers six bits or eight bits.

(Note) An L input on /RST sets the word length to eight bits per word.

• X/Y (page) counter, up/down mode select (UDE)

| /WR | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 0   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   |

X-Counter/Down Mode (04H) X-Counter/Up Mode (05H) Y-Counter/Down Mode (06H) Y-Counter/Up Mode (07H)

This command selects the counter and the up/down mode. For instance, when X-counter/up mode is selected, the X-address is incremented in response to every data read and write. However, when X-counter/up mode is selected, the address in the Y-(Page) counter will not change. Hence the Y-address must be set (with the SYE command) before it can be changed.

(Note) An L input to /RST sets the Y-counter to up mode.

• Test mode select (CHE)

| /WR | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 1   | 1   | *   | *   | *   |

\* · INI\/Δ11Γ

This command selects the test mode. Do not use this command.

• Set Y-(page) address (SYE)

| /WR | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 1   | Α   | Α   | Α   | Α   | Α   |

Range: 8-bit/Word: 20H to 2EH (Page 0 to Page 14) 6-bit/Word: 20H to 33H (Page 0 to Page 19)

When operating in 8-bits-per-word mode, this command selects one of the 15 pages from the display RAM. (Do not try to select a page outside this range.) When operating in 6-bits-per-word mode, this command selects one of the 20 pages from the display RAM.

(Note) An L input to /RST sets the Y-address to page 0.

• Set Z-address (SZE)

| /WR | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 1   | Α   | Α   | Α   | Α   | Α   | Α   |

Range: 40H to 7FH (ZAD0 to ZAD63)

This command sets the top row of the LCD screen, irrespective of the current X-address. For instance, when the Z-address is 32, the top row of the LCD screen is address 32 of the display RAM, and the bottom row of the LCD screen is address 31 of the display RAM.

(Note) An L input to / RST sets the Z-address to 0.

### • Set X-address (SXE)

| /WR | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 1   | 0   | Α   | Α   | Α   | Α   | Α   | Α   |

Range: 80H to BFH (XAD0 to XAD63)

This command sets the X-address (in the range 0 to 63). An L input to /RST sets the X-address to 0.

### • Set contrast (SCE)

| /WR | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 1   | 1   | Α   | Α   | Α   | Α   | Α   | Α   |

Range: C0H to FFH

This command sets the contrast for the LCD. The LCD contrast can be set in 64 steps. The command COH selects the brightest level; the command FFH selects the darkest.

### Op-amp control 1 (OPA1)

| /WR | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 1   | 0   | *   | Α   | Α   |

\* : INVALID

Range: 10H to 13H (when DB2 = 0)

This command sets the power supply strength for the operational amplifier. This command selects one of four levels. The command 10H selects the lowest power supply strength and the command 13H selects the maximum strength.

(Note) An L input to /RST sets the op-amp power supply strength to the lowest level.

### • Op-amp control 2 (OPA2)

| /WR | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 1   | *   | Α   | Α   |

\* : INVALID

Range: 08H to 0BH (when DB2 = 0)

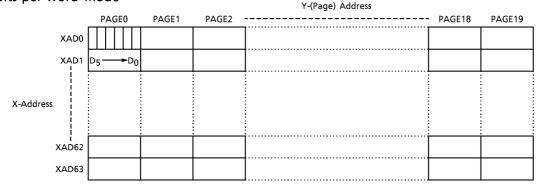

This command enhances the power supply strength of the operational amplifier over a short period from the rising edge of C<sub>L</sub>. This command selects one of four levels of strength.

(Note) An L input to /RST sets t to 0 for op-amp. See Fig. 10.

The amplifier's strength is enhanced over the period denoted by  $\leftrightarrow$ , starting on the rising edge of  $C_L$ .

Fig. 10

### Status read (STRD)

| /WR | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1   | 0   | В   | 8/6 | D   | R   | 0   | 0   | Y/X | U/D |

B (Busy) : When B = 1 the T6A04A is executing an internal operation and no

instruction can be accepted except STRD.

When B = 0 the T6A04A can accept an instruction.

8/6 (Word Length): When 8/6=1 the word length of the display data is eight bits per word.

When 8/6=0 the word length of the display data is six bits per word.

D (Display) : When D = 1 display is ON.

When D = 0 display is OFF.

R (Reset) : When R = 1 the T6A04A is in reset state.

When R = 0 the T6A04A is in operating state.

Y/X (Counter) : When Y/X = 1 the Y counter is selected.

When Y/X=0 the X counter is selected.

U/D (Up/Down) : When U/D=1 the X and Y counters are in up mode.

When U/D=0 the X and Y counters are in down mode.

• Write/read display data (DAWR/DARD)

| /WR | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 1   | D   | D   | D   | D   | D   | D   | D   | D   |

| 1   | 1   | D   | D   | D   | D   | D   | D   | D   | D   |

DAWR: Display Data Write

DARD: Display Data Read

The command DAWR writes the display data to the display RAM. The command DARD outputs the display data from the display RAM. However, when a data read is executed, the correct data does not appear on the first data reading. Therefore, ensure that the T6A04A performs a dummy data read before reading the actual data.

### **FUNCTION DESCRIPTION**

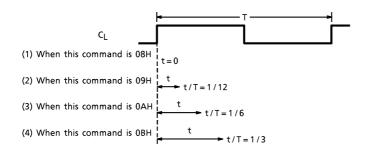

X-address counter and Y-(page) address counter

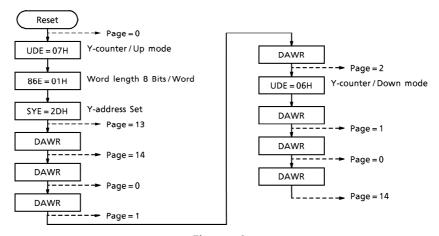

Fig. 11-1 shows a sample operation involving the X-address counter.

After Reset is executed, the X-address (XAD) becomes 0, then X-counter/up mode is selected. Next, the X-address is set to 62 using the SXE command.

After data has been written or read, the X-address is automatically incremented by 1.

After X-counter/down mode has been selected and data has been written or read, the X-address is automatically decremented by 1.

When the X-counter is selected, the Y-counter is not incremented or decremented.

Fig. 11-1

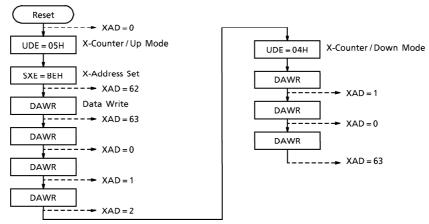

Fig. 11-2 shows a sample operation involving the Y-address counter in 8-bit word length mode. After Reset is executed, the Y-(page) address (Page) becomes 0, then Y-(page) counter/up mode and 8-bit word length mode are selected. After data has been written or read, the Y-(page) address counter is automatically incremented by 1.

After Y-(page) counter/down mode has been selected and data has been written or read, the Y-(page) address is automatically decremented by 1.

When the Y-(page) counter is selected, the X-counter is not incremented or decremented.

Fig. 11-2

When operating in 6-bit word length mode, the Y-(page) address counter can court up to 19. If Page = 18 in up mode, after data has been written or read, the Y-(page) address (Page) becomes 0.

If Page = 0 in down mode, after data has been written or read, the Y-(page) address (Page) becomes 18.

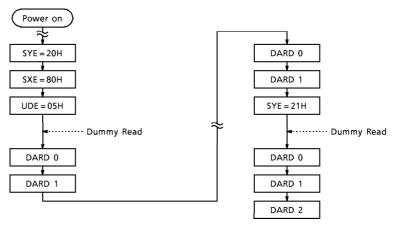

### • Data read

When reading data, there are some cases when dummy data must be read. This is because when the data read command invoked, the data pointed to by the address counter is transferred to the output register; the contents of the output register are then transferred by the next data read command.

Therefore when reading data straight after power-on or straight after an address-setting command, such as SYE or SXE, a dummy data read must be performed. See Fig. 12.

Fig. 12

### • Reset function

When /RST = L, the reset function is executed and the following settings are mode.

(1) Display ..... OFF

(2) Word length ...... 8 bits/word

(3) Counter mode ..... Y-counter/up mode

(4) Y-(page) address

Page = 0

(5) X-address

XAD = 0

(6) Z-address

ZAD = 0

(7) Op-amp1 (OPA1)

min

(8) Op-amp2 (OPA2)

min

### Standby function

When /STB = L, the T6A04A is in standby state. The internal oscillator is stopped, power consumption is reduced, and the power supply level for the LCD ( $V_{LC1}$  to  $V_{LC5}$ ) becomes  $V_{DD}$ .

### Busy flag

When the T6A04A is executing an internal operation (other than the STRD command), the busy flag is set to logical H. The state of the busy flag is output in response to the STRD command. While the busy flag is H, no instruction can be accepted (except the STRD command). The busy state period (T) is as follows.

2/fosc≤T≤4/fosc [seconds] fosc : Frequency of OSC1

### Oscillation frequency

The frequency select pins (FS1 and FS2), are used to set the relation between the oscillation frequency (f<sub>OSC</sub>) and frame frequency (f<sub>M</sub>), as shown in the table below.

| $R_f$ (k $\Omega$ ) | f <sub>OSC</sub> (kHz) | f <sub>/ <math>\phi</math></sub> (kHz) | f <sub>FRM</sub> (Hz) | f <sub>M</sub> (Hz) | FS1 | FS2 |

|---------------------|------------------------|----------------------------------------|-----------------------|---------------------|-----|-----|

| 1000                | 26.88                  | 13.44                                  | 70                    | 35                  | 0   | 0   |

| 480                 | 53.76                  | 26.88                                  | 70                    | 35                  | 1   | 0   |

| 105                 | 215.00                 | 107.50                                 | 70                    | 35                  | 0   | 1   |

| 50                  | 430.10                 | 215.00                                 | 70                    | 35                  | 1   | 1   |

### (Note) The resistance values are typical values.

The oscillation frequency depends on how the device is mounted. It is necessary to adjust the oscillation frequency to a target value.

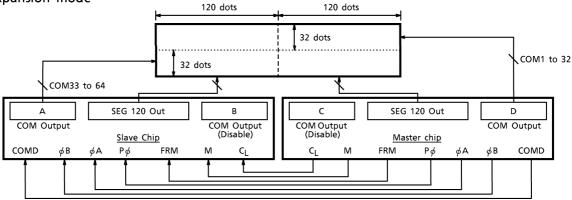

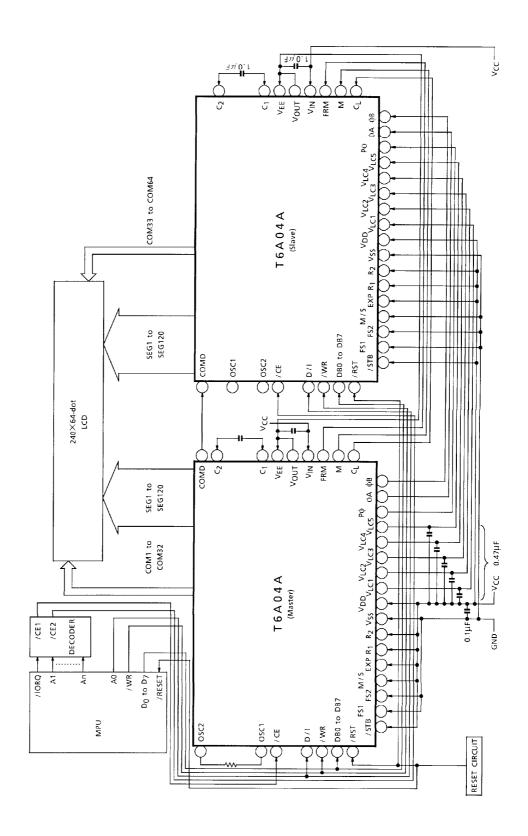

### Expansion function

The T6A04A's expansion function, allows two, T6A04As to drive an LCD panel of up to 240 by 64 dots

The table below shows the functions which can be selected with the M/S and EXP pins.

|     |   | M                                                                                                           | / <b>S</b>                                                                                                                                                                                    |

|-----|---|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |   | Н                                                                                                           | L                                                                                                                                                                                             |

| EXP | Н | <ul> <li>Two-chip mode (enable expansion mode)</li> <li>Master chip COM1 to COM32 are available.</li> </ul> | <ul> <li>Two-chip mode (enable expansion mode)</li> <li>Slave chip</li> <li>COM33 to COM64 are available.</li> <li>Timing signals and power voltage are supplied from master chip.</li> </ul> |

|     | L | <ul><li>Single-chip mode (disable expansion mode)</li><li>COM1 to COM32 are available.</li></ul>            | Do not select.                                                                                                                                                                                |

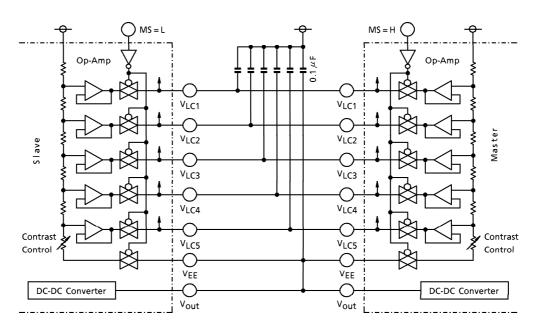

Figs. 13-1 and -2 illustrate application examples of disable expansion mode and enable expansion mode.

Enable Expansion Mode (two-chip mode)

As shown in Fig. 13-2, and Fig. 14 the master chip supplies the LCD drive signals and power voltage to the slave chip (the oscillator, the timing circuits, op-amp and contrast control circuit are disabled).

COM1 to COM32 of the master chip and COM33 to COM64 of the slave chip are available (COM33 to COM64 of the master chip and COM1 to COM32 of the slave chip are disabled).

The T9841B is available as an expansion driver for the T6A04A (a T6A04A and T9841B can drive a  $200 \times 64$ -dot LCD panel).

### (1) Disable expansion mode

Fig. 13-1

### (2) Expansion mode

Fig. 13-2

Fig. 14

### LCD DRIVER WAVEFORM

**ABSOLUTE MAXIMUM RATINGS (Ta = 25°C)**

| ITEM                  | SYMBOL                                                    | RATING                                          | UNIT |

|-----------------------|-----------------------------------------------------------|-------------------------------------------------|------|

| Supply Voltage (1)    | V <sub>DD</sub> (Note 1)                                  | -0.3 to 7.0                                     | V    |

| Supply Voltage (2)    | V <sub>LC1</sub> , 2, 3, 4, 5<br>V <sub>EE</sub> (Note 3) | V <sub>DD</sub> – 18.0 to V <sub>DD</sub> + 0.3 | V    |

| Input Voltage         | V <sub>IN</sub> (Note 1, 2)                               | -0.3 to V <sub>DD</sub> + 0.3                   | V    |

| Operating Temperature | T <sub>opr</sub>                                          | – 20 to 75                                      | °C   |

| Storage Temperature   | T <sub>stg</sub>                                          | – 55 to 25                                      | °C   |

(Note 1) Referenced to  $V_{SS} = 0V$

(Note 2) Applies to all data bus pins and input pins except VEE, VLC1, VLC2, VLC3, VLC4 and VLC5.

(Note 3) Ensure that the following condition is always maintained.  $V_{DD} \ge V_{LC1} \ge V_{LC2} \ge V_{LC3} \ge V_{LC4} \ge V_{LC5} \ge V_{EE}$

### **ELECTRICAL CHARACTERISTICS**

DC CHARACTERISTICS

TEST CONDITIONS (Unless otherwise noted,  $V_{SS} = 0V$ ,  $V_{DD} = 5.0V \pm 10\%$ ,  $V_{LC5} = 0V$ ,  $T_{a} = -20$  to  $75^{\circ}$ C)

| 1231 CONDITIONS (Ciness Galerwise Hoted, 435 – 64, 4DD – 3.64 – 1677, 4ECS – 64, 14 – 126 (6.73 C) |         |                                     |                      |                                                                    |                           |          |                          |      |                                                                                                                                                       |  |

|----------------------------------------------------------------------------------------------------|---------|-------------------------------------|----------------------|--------------------------------------------------------------------|---------------------------|----------|--------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ITEN                                                                                               | Μ       | SYMBOL                              | TEST<br>CIR-<br>CUIT | TEST CONDITIONS                                                    | MIN                       | TYP.     | MAX                      | UNIT | PIN NAME                                                                                                                                              |  |

| Operating Supply (1)                                                                               |         | $V_{DD}$                            | _                    | -                                                                  | 4.5                       | _        | 5.5                      | V    | V <sub>DD</sub> , V <sub>IN</sub>                                                                                                                     |  |

| Operating Supply (2)                                                                               |         | V <sub>LC5</sub><br>V <sub>EE</sub> | _                    | _                                                                  | V <sub>DD</sub><br>- 16.0 |          | V <sub>DD</sub><br>- 4.0 | V    | V <sub>EE</sub> , V <sub>LC5</sub>                                                                                                                    |  |

| Input                                                                                              | H Level | V <sub>IH1</sub>                    | _                    | _                                                                  | 0.7<br>V <sub>DD</sub>    | _        | $V_{DD}$                 | V    | M/S, EXP, R <sub>1</sub> , R <sub>2</sub> , C <sub>L</sub> , M, FRM, $\phi$ A,                                                                        |  |

| Voltage (1)                                                                                        | L Level | V <sub>IL1</sub>                    | _                    | -                                                                  | 0                         | _        | 0.3<br>V <sub>DD</sub>   | ٧    | $\phi$ B, COMD, FS1,<br>FS2, P $\phi$                                                                                                                 |  |

| Input                                                                                              | H Level | V <sub>IH2</sub>                    | _                    | _                                                                  | 2.2                       | <b> </b> | $V_{DD}$                 | V    | DB0 to DB7, D/I,<br>/WR, /CE, /RST,                                                                                                                   |  |

| Voltage (2)                                                                                        | L Level | V <sub>IL2</sub>                    | _                    | _                                                                  | 0                         | _        | 0.8                      | V    | / STB                                                                                                                                                 |  |

| Output                                                                                             | H Level | V <sub>OH1</sub>                    | _                    | I <sub>OH</sub> = -400μA                                           | V <sub>DD</sub><br>- 0.4  | _        | V <sub>DD</sub>          | ٧    | $C_L$ , $M$ , $FRM$ , $P\phi$ ,                                                                                                                       |  |

| Voltage (1)                                                                                        | L Level | V <sub>OL1</sub>                    | _                    | I <sub>OL</sub> = 400μA                                            | 0                         | _        | 0.4                      | V    | COMD, $\phi A$ , $\phi B$                                                                                                                             |  |

| Output                                                                                             | H Level | V <sub>OH2</sub>                    | _                    | $I_{OH} = -205 \mu A$                                              | 2.4                       |          | $v_{DD}$                 | ٧    | D/I, /WR, /CE,                                                                                                                                        |  |

| Voltage (2)                                                                                        | L Level | V <sub>OL2</sub>                    | _                    | I <sub>OL</sub> = 1.6mA                                            | 0                         | _        | 0.4                      | ٧    | DB0 to DB7, /RST, /STB                                                                                                                                |  |

| Column Out<br>Resistance                                                                           | put     | Rcol                                |                      | $V_{DD} - V_{LC5}$<br>= 11.0V<br>Load current<br>= $\pm 100 \mu A$ |                           | ı        | 7.5                      | kΩ   | SEG1 to SEG120                                                                                                                                        |  |

| Row Output<br>Resistance                                                                           |         | Rrow                                | _                    | $V_{DD} - V_{LC5}$<br>= 11.0V<br>Load current<br>= $\pm 100 \mu A$ |                           | _        | 1.5                      | kΩ   | COM1 to COM64                                                                                                                                         |  |

| Input Leakage                                                                                      |         | I <sub>IL</sub>                     | _                    | V <sub>IN</sub> = V <sub>DD</sub> to GND                           | <b>–</b> 1                | _        | 1                        | μΑ   | M/S, EXP, R <sub>1</sub> , R <sub>2</sub> ,<br>C <sub>L</sub> , M, FRM, D/I,<br>/WR, COMD, /CE,<br>DB0 to DB7, /STB,<br>/RST, FS1, FS2,<br>P¢, ¢A, ¢B |  |

| ITEM                            | SYMBOL                         | TEST<br>CIR-<br>CUIT | TEST CONDITIONS | MIN         | TYP.  | MAX  | UNIT | PIN NAME   |

|---------------------------------|--------------------------------|----------------------|-----------------|-------------|-------|------|------|------------|

| Operating Freq.                 | $f\phi$                        | _                    | _               | 10          | _     | 250  | kHz  | <b>/</b> φ |

| External Clock Freq.            | f <sub>ex</sub>                | _                    | _               | 20          | _     | 500  | kHz  | OSC1       |

| External Clock Duty             | f <sub>duty</sub>              | _                    | _               | 45          | 50    | 55   | %    | OSC1       |

| External Clock Rise / Fall Time | t <sub>r</sub> /t <sub>f</sub> |                      | _               | _           | _     | 50   | ns   | $V_{DD}$   |

| Current Consumption (1)         | I <sub>DD1</sub>               | l                    | (Note 1)        |             | 850   | 1400 | μΑ   | $V_{DD}$   |

| Current Consumption (2)         | I <sub>DD2</sub>               | 1                    | (Note 2)        |             | 950   | 1600 | μΑ   | $V_{DD}$   |

| Current Consumption (3)         | IDDSTB                         |                      | (Note 3)        | <b>–</b> 1  | _     | 1    | μΑ   | $V_{DD}$   |

| Output Voltage                  | Vo                             | 1                    | (Note 4)        | <b>-4.0</b> | - 4.2 | _    | ٧    | Vout       |

- (Note 1)  $V_{DD}$  = 5.0V  $\pm$  10%,  $V_{EE}$  =  $V_{OUT}$  (from DC-DC converter) Master mode, no data access  $R_f$  = 47k $\Omega$ , no load 1/9 bias, FS1, 2 = H, op-amp strength at minimum level

- (Note 2)  $V_{DD}$  = 5.0V  $\pm$  10%,  $V_{EE}$  =  $V_{OUT}$  (from DC-DC Converter) Master mode, data access cycle  $f_{/CE}$  = 1MHz  $R_f$  = 47k $\Omega$ , No load 1/9 bias, FS1, 2 = H, op-amp strength at minimum level

- (Note 3)  $V_{DD} = 5.0V \pm 10\%$ ,  $V_{DD} V_{EE} = 16V$ Master mode, / STB = L

- (Note 4) V<sub>IN</sub> = 5.0V, ILoad =  $500\mu$ A, V<sub>EE</sub> = -5.0V (external power supply) C1 C2 =  $1.0\mu$ F, V<sub>IN</sub> V<sub>OUT</sub> =  $1.0\mu$ F, R = 47k $\Omega$ , Ta = 25°C

### **TEST CIRCUIT**

1.

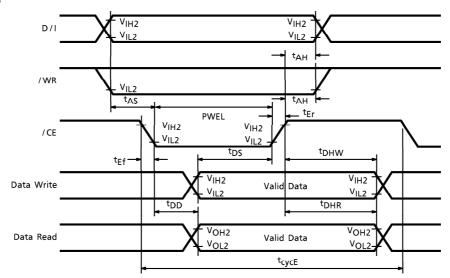

### **AC CHARACTERISTICS**

TEST CONDITIONS ( $V_{SS} = 0V$ ,  $V_{DD} = 5.0V \pm 10\%$ ,  $T_{a} = -20$  to  $75^{\circ}$ C)

| · 33 , DI             |                                   |     |     |      |

|-----------------------|-----------------------------------|-----|-----|------|

| ITEM                  | SYMBOL                            | MIN | MAX | UNIT |

| Enable Cycle Time     | t <sub>cycE</sub>                 | 500 | _   | ns   |

| Enable Pulse Width    | PWEL                              | 220 | _   | ns   |

| Enable Rise/Fall Time | t <sub>Er</sub> , t <sub>Ef</sub> |     | 20  | ns   |

| Address Set-up Time   | tAS                               | 40  |     | ns   |

| Address Hold Time     | <sup>t</sup> AH                   | 0   |     | ns   |

| Data Set-up Time      | t <sub>DS</sub>                   | 60  | _   | ns   |

| Data Hold Time        | <sup>t</sup> DHW                  | 10  | -   | ns   |

| Data Delay Time       | t <sub>DD</sub> (Note)            |     | 200 | ns   |

| Data Hold Time        | t <sub>DHR</sub> (Note)           | 10  | _   | ns   |

LOAD CIRCUIT

$R_L=2.4k\Omega$   $R=11k\Omega$  C = 130pF (including wiring capacitance) D = 151588

(Note) With load circuit connected

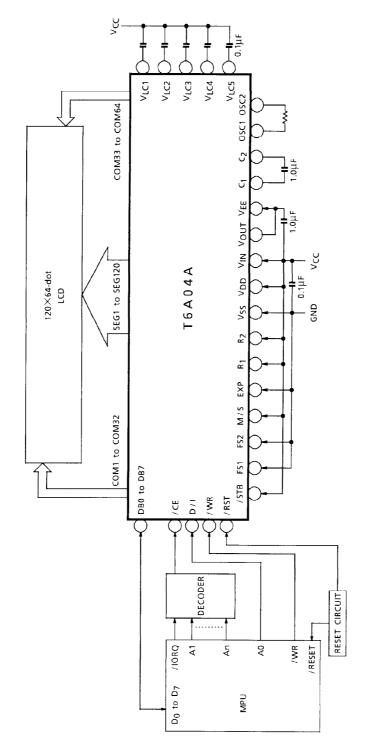

# APPLICATION CIRCUIT

(1) T6A04A single-chip mode

- Oscillation frequency is at a minimum.

- LCD drive bias is 1/9.

- DC-DC converter is used.

T6A04A-26

## APPLICATION CIRCUIT

(2) T6A04A two-chip mode

- Oscillation frequency is at a minimum.

- LCD drive bias is 1/9.

- DC-DC converter is used.

T6A04A-27