## Micropower 3.3 V, 100 mA Low Dropout Linear Regulator with NOCAP™

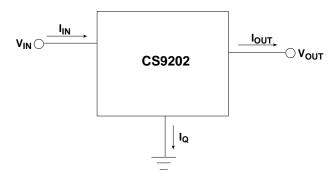

The CS9202 is a precision 3.3 V, 100 mA voltage regulator with low quiescent current (450  $\mu$ A typ. @ 100  $\mu$ A load). The 3.3 V output is accurate within  $\pm 2\%$  and supplies 100 mA of load current.

The regulator is protected against reverse battery, short circuit, over voltage, and over temperature conditions. The device can withstand 74 V peak transients making it suitable for use in automotive environments. ON's proprietary NOCAP solution is the first technology which allows the output to be stable without the use of an external capacitor. NOCAP is suitable for slow switching or steady loads.

#### **Features**

- NOCAP

- Low Quiescent Current (450 μA typ. @ 100 μA load)

- 3.3 V, ±2% Output

- 100 mA Output Current Capability

- Fault Protection

- 74 V Peak Transient Voltage

- − −15 V Reverse Voltage

- Short Circuit

- Thermal Shutdown

- Overvoltage Shutdown

- Internally Fused Leads

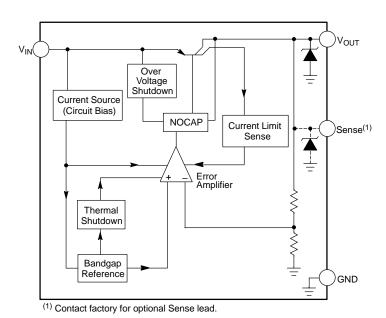

Figure 1. Block Diagram

### ON Semiconductor™

http://onsemi.com

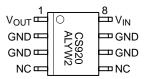

SO-8 DF SUFFIX CASE 751

# PIN CONNECTIONS AND MARKING DIAGRAM

A = Assembly Location

WL, L = Wafer Lot YY, Y = Year WW, W = Work Week

#### ORDERING INFORMATION

| Device      | Package | Shipping         |  |

|-------------|---------|------------------|--|

| CS9202YDF8  | SO-8    | 95 Units/Rail    |  |

| CS9202YDFR8 | SO-8    | 2500 Tape & Reel |  |

#### CS9202

#### **MAXIMUM RATINGS\***

| Parameter                                                                                             |                                 | Value              | Unit   |

|-------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|--------|

| Power Dissipation                                                                                     |                                 | Internally Limited | -      |

| Input Voltage (V <sub>IN</sub> ): DC Peak Transient Voltage (60 V Load Dump @ V <sub>IN</sub> = 14 V) |                                 | –15 to 36<br>74    | V<br>V |

| Output Current                                                                                        |                                 | Internally Limited | -      |

| ESD Susceptibility (Human Body Model)                                                                 |                                 | 4.0                | kV     |

| Package Thermal Resistance:   Junction–to–Case, $R_{\theta JC}$ Junction–to–Ambient, $R_{\theta JA}$  |                                 | 25<br>110          | °C/W   |

| Junction Temperature                                                                                  |                                 | -40 to +150        | °C     |

| Storage Temperature                                                                                   |                                 | -55 to +150        | °C     |

| Lead Temperature Soldering:                                                                           | Reflow (SMD styles only) Note 1 | 230 Peak           | °C     |

<sup>1. 60</sup> second maximum above 183°C.

### $\textbf{ELECTRICAL CHARACTERISTICS} \quad \text{(4.5 V} \leq \text{V}_{IN} \leq 26 \text{ V, I}_{OUT} = 1.0 \text{ mA, } -40^{\circ}\text{C} \leq \text{T}_{J} \leq 125^{\circ}\text{C; unless otherwise stated.)}$

| Parameter                            | Test Conditions                                                                                                                                                                                                                                                           | Min            | Тур            | Max            | Unit           |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|

| Output Stage                         |                                                                                                                                                                                                                                                                           |                |                |                |                |

| Output Voltage, V <sub>OUT</sub>     | $\begin{array}{c} 9.0 \text{ V} < \text{V}_{\text{IN}} < 16 \text{ V},  100 \text{ uA} \leq \text{I}_{\text{OUT}} \leq 100 \text{ mA} \\ 4.5 \text{ V} < \text{V}_{\text{IN}} < 26 \text{ V},  100 \text{ uA} \leq \text{I}_{\text{OUT}} \leq 100 \text{ mA} \end{array}$ | 3.234<br>3.201 | 3.300<br>3.300 | 3.366<br>3.399 | V              |

| Load Regulation                      | $V_{IN} = 14 \text{ V}, 100  \mu\text{A} \le I_{OUT} \le 100 \text{ mA}$                                                                                                                                                                                                  | _              | 5              | 50             | mV             |

| Line Regulation                      | 4.5 V < V < 26 V, I <sub>OUT</sub> = 1.0 mA                                                                                                                                                                                                                               | _              | 5              | 50             | mV             |

| Quiescent Current, (I <sub>Q</sub> ) | $\begin{split} I_{OUT} &= 100~\mu\text{A},~V_{IN} = 12~\text{V} \\ I_{OUT} &\leq 50~\text{mA} \\ I_{OUT} &\leq 100~\text{mA} \end{split}$                                                                                                                                 | -              | 450<br>4<br>12 | 750<br>6<br>20 | μA<br>mA<br>mA |

| Ripple Rejection                     | $7.0 \text{ V} \le \text{VI}_{\text{N}} \le 17 \text{ V}, \text{ I}_{\text{OUT}} = 100 \text{ mA}, \text{ f} = 120 \text{ Hz}$                                                                                                                                            | 60             | 75             | -              | dB             |

| Current Limit                        | -                                                                                                                                                                                                                                                                         | 105            | 200            | -              | mA             |

| Short Circuit Output Current         | V <sub>OUT</sub> = 0 V                                                                                                                                                                                                                                                    | 25             | 125            | _              | mA             |

| Thermal Shutdown (Note 2)            | -                                                                                                                                                                                                                                                                         | 150            | 180            | -              | °C             |

| Overvoltage Shutdown                 | V <sub>OUT</sub> ≤ 1.0 V                                                                                                                                                                                                                                                  | 28             | 32             | 36             | V              |

$<sup>2. \ \ \, \</sup>text{This parameter is guaranteed by design, but not parametrically tested in production.}$

#### PACKAGE LEAD DESCRIPTION

| Package Lead Number |                  |                             |  |

|---------------------|------------------|-----------------------------|--|

| SO-8                | Lead Symbol      | Function                    |  |

| 1                   | V <sub>OUT</sub> | 3.3 V, ± 2%, 100 mA output. |  |

| 2, 3, 6, 7          | GND              | Ground.                     |  |

| 4, 5                | NC               | No connection.              |  |

| 8                   | V <sub>IN</sub>  | Input voltage.              |  |

<sup>\*</sup>The maximum package power dissipation must be observed.

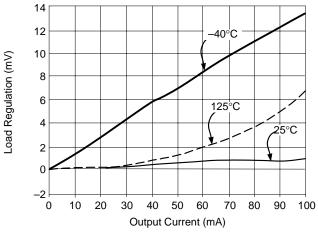

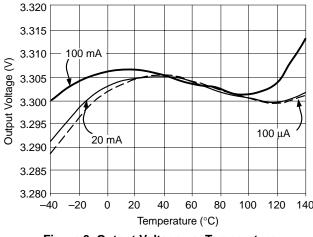

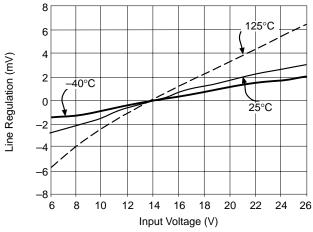

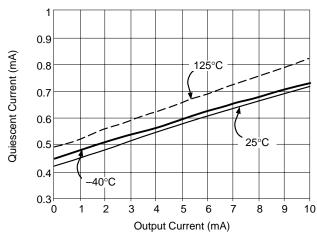

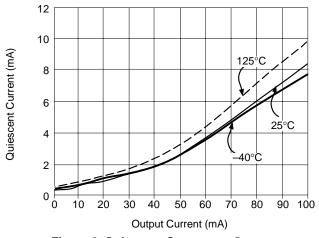

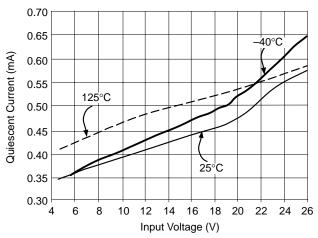

#### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 2. Load Regulation vs. Output Current V<sub>IN</sub> = 14 V

Figure 3. Output Voltage vs. Temperature  $V_{\text{IN}} = 14 \text{ V}$

Figure 4. Line Regulation vs. Input Voltage  $I_{OUT} = 100 \mu A$

Figure 5. Quiescent Current vs. Output Current (Lightly Loaded)  $V_{IN} = 14 \text{ V}$

Figure 6. Quiescent Current vs. Output Current V<sub>IN</sub> = 14 V

Figure 7. Quiescent Current vs. Input Voltage  $I_{OUT}$  = 100  $\mu$ A

#### **CIRCUIT DESCRIPTION**

# VOLTAGE REFERENCE AND OUTPUT CIRCUITRY

#### **Output Stage Protection**

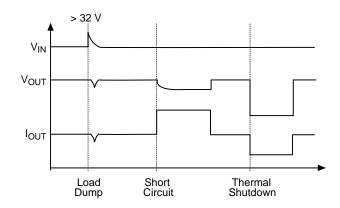

The output stage is protected against overvoltage, short circuit and thermal runaway conditions (Figure 8).

If the input voltage rises above 32 V (typ), the output shuts down. This response protects the internal circuitry and enables the IC to survive unexpected voltage transients.

Should the junction temperature of the power device exceed 180°C (typ) the power transistor is turned off. Thermal shutdown is an effective means to prevent die overheating since the power transistor is the principle heat source in the IC.

Figure 8. Typical Circuit Waveforms for Output Stage Protection

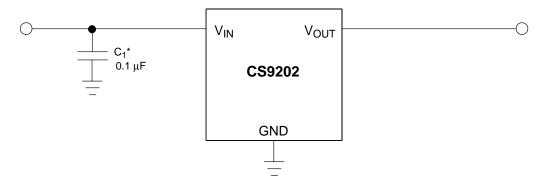

<sup>\*</sup> C1 is required if regulator is distant from power source filter.

Figure 9. Application and Test Diagram

#### **APPLICATION NOTES**

#### STABILITY CONSIDERATIONS / NOCAP

Normally a low dropout or quasi-low dropout regulator (or any type requiring a slow lateral PNP in the control loop) necessitates a large external compensation capacitor at the output of the IC. The external capacitor is also used to curtail offshoot, determine startup delay time and load transient response.

Traditional LDO regulators typically have low unity gain bandwidth, display overshoot and poor ripple rejection. Compensation is also an issue and depends on the external capacitor value, ESR (Equivalent Series Resistance) and board layout parasitics that all can create oscillations if not properly accounted for. NOCAP is an ON Semiconductor exclusive output stage which internally compensates the LDO regulator over temperature, load and line variations without the need for an expensive external capacitor

NOCAP is ideally suited for slow switching or steady loads. If the load is characterized by transient current events, an output storage capacitor may be needed. If this is the case, the capacitor should be no larger than 100 nF. With loads that require greater transient suppression, a regulator with a traditional output stage (such as the CS8221) may be better suited for proper operation.

# CALCULATING POWER DISSIPATION IN A SINGLE OUTPUT LINEAR REGULATOR

The maximum power dissipation for a single output regulator (Figure 10) is:

$$PD(max) = {VIN(max) - VOUT(min)} IOUT(max) + VIN(max)IQ$$

(1)

where:

V<sub>IN(max)</sub> is the maximum input voltage,

V<sub>OUT(min)</sub> is the minimum output voltage,

$I_{OUT\left(max\right)}$  is the maximum output current for the application, and

$I_Q$  is the quiescent current the regulator consumes at  $I_{OUT(max)}. \label{eq:lower}$

Once the value of  $P_{D(max)}$  is known, the maximum permissible value of  $R_{\Theta JA}$  can be calculated:

$$R_{\Theta JA} = \frac{150^{\circ}C - T_{A}}{P_{D}}$$

(2)

Figure 10. Single output regulator with key performance parameters labeled.

The value of  $R_{\Theta JA}$  can then be compared with those in the package section of the data sheet. Those packages with  $R_{\Theta JA}$ 's less than the calculated value in equation 2 will keep the die temperature below 150°C.

In some cases, none of the packages will be sufficient to dissipate the heat generated by the IC, and an external heatsink will be required.

#### **HEAT SINKS**

A heat sink effectively increases the surface area of the package to improve the flow of heat away from the IC and into the surrounding air.

Each material in the heat flow path between the IC and the outside environment will have a thermal resistance. Like series electrical resistances, these resistances are summed to determine the value of  $R_{\Theta JA}$ :

$$R_{\Theta JA} = R_{\Theta JC} + R_{\Theta CS} + R_{\Theta SA}$$

(3)

where:

$R_{\Theta JC}$  = the junction–to–case thermal resistance,

$R_{\Theta CS}$  = the case-to-heatsink thermal resistance, and

$R_{\Theta SA}$  = the heatsink-to-ambient thermal resistance.

$R_{\Theta JC}$  appears in the package section of the data sheet. Like  $R_{\Theta JA}$ , it too is a function of package type.  $R_{\Theta CS}$  and  $R_{\Theta SA}$  are functions of the package type, heatsink and the interface between them. These values appear in heat sink data sheets of heat sink manufacturers.

### CS9202

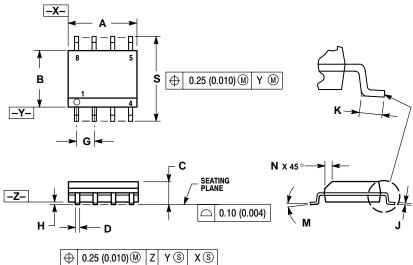

### **PACKAGE DIMENSIONS**

#### SO-8 **DF SUFFIX** CASE 751-07 ISSUE W

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |      | INCHES    |       |  |

|-----|-------------|------|-----------|-------|--|

| DIM | MIN         | MAX  | MIN       | MAX   |  |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |  |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |  |

| С   | 1.35        | 1.75 | 0.053     | 0.069 |  |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |  |

| G   | 1.27 BSC    |      | 0.050 BSC |       |  |

| Н   | 0.10        | 0.25 | 0.004     | 0.010 |  |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |  |

| K   | 0.40        | 1.27 | 0.016     | 0.050 |  |

| M   | 0 °         | 8 °  | 0 °       | 8 °   |  |

| N   | 0.25        | 0.50 | 0.010     | 0.020 |  |

| S   | 5.80        | 6.20 | 0.228     | 0.244 |  |

### CS9202

# **Notes**

NOCAP is a trademark of ON Semiconductor, and is patented.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone:** 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax:** 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

**JAPAN**: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031

Phone: 81–3–5740–2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.