# **3-Port JTAG Gateway**

# **Description**

The AS91L1003U is a one to 3-port JTAG gateway. It partitions a single JTAG chain into three separate chains. These separate chains can be optionally configured to operate as a single chain

The AS91L1003U device is used to provide enhanced capabilities to the standard IEEE1149.1. It enables the IEEE1149.1 interface to be used in a true Multi-Drop environment without any additional signals. This Multi-Drop capability enables the standard IEEE1149.1 interface to be used not just for stand alone Printed Circuit Board (PCB) testing, but complete system testing including all PCBs within a system back plane environment.

The AS91L1003U provides the capability of partitioning the PCB into multiple smaller IEEE1149.1 scan chains totally under software

control. Partitioning the IEEE1149.1 chains on the PCB has several benefits, which include easier fault diagnostics capabilities, as a fault on one of the IEEE1149.1 Local Scan Ports (LSPs) does not render the PCB un-testable, faster flash programming on the PCB's and removal of IEEE1149.1 signal loading issues.

All of the protocols required for addressing the AS91L1003U device via the Multi-Drop capability and the protocols for configuring which of the three IEEE1149.1 LSPs of the AS91L1003U are to be used, is handled via the 3<sup>rd</sup> party ATPG tools from vendors like Asset-Intertech and JTAG Technologies. In a Multi-Drop environment, it is also possible to perform interconnect tests between multiple PCBs within the system thus extending the interconnect tests to the back plane itself.

# **Key Features**

- Device Multi-Drop addressable via the IEEE 1149.1 protocol

- Support for 3 local scan chains addressable via the IEEE 1149.1 interface

- Support for Pass-Through™

- Support for the IEEE 1149.1 USERCODE instruction

- Support for Status instruction enabling nonintrusive monitoring of the system card

- Local Scan Port (LSP) enable signal provides the ability to use non IEEE 1149.1 compliant devices that require JTAG enable signal

- Provides the ability to initiate Self-Test on a remote PCB via a standard IEEE 1149.1 command

- Support for JTAG Technologies AutoWR™ feature

- Pinout and feature set compatible (complete second source) with the Firecron JTS03U device

- Available in a 100-pin LQFP or a 100-pin FPBGA lead free package

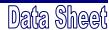

# **Device Block Diagram**

Figure 1 - AS91L1003U Device Block Diagram

### **Alliance Semiconductor**

## **AS91L1003U Gateway Functional Description**

The basic structure of the AS91L1003U device is shown in Figure 1. The core of the device is the 16-state IEEE1149.1 TAP controller state machine. All accesses to the internal registers of the AS91L1003U device are controlled via this state machine during normal operation as per the IEEE1149.1 standard. The address selection logic enables the AS91L1003U to operate in a Multi-Drop environment within system backplane.

The address selection logic compares the scanned address to the slot address value presented on the I/O of the AS91L1003U device. The LSP park/unpark logic provides control through instructions scanned in under the IEEE1149.1 protocol, to select which LSP will be placed into the active scan chain. The passthrough and LSP connection logic selects the signal paths for the LSP IEEE1149.1 signals. The device also supports a Pass-Through mode which

enables the primary IEEE1149.1 signals to be routed to any of the LSPs. This signal routing is selectable via I/O pins on the AS91L0003U device.

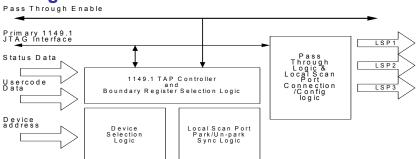

The AS91L1003U operation is controlled via core blocks through three closely coupled state machines. Figure-2 shows the device selection state machine. The AS91L1003U will perform an address compare on the slot address presented at its I/O and the value scanned in via the IEEE1149.1. If the value matches, then the AS91L1003U becomes selected and is ready for normal access via IEEE1149.1 commands. If the address does not match then the device will proceed to the unselected mode, where it will remain until the AS91L1003U is issued a GOTOWAIT instruction or a reset occurs via the LSP RESET either TRST or pin.

Figure 2 - AS91L1003U **Selection Logic State machine**

Figure 3 - The LSP Park/Unpark State Machine

The LSP Park/Unpark state machine controls the insertion of the LSPs into the current active scan chain. The ability to park the LSP in certain IEEE1149.1 states, enable the AS91L1003U to perform several functions including backplane interconnect testing and IC BIST.

## AS91L1003U Detailed Mode of Operation

#### Addressing the AS91L1003U device

After a Test-Logic-Reset or power-up, the AS91L1003U device will be in its Wait-for-Selection state with its TDO pin tri-stated, thus avoiding contention in a Multi-Drop environment. The AS91L1003U device will respond to a deviceselect sequence for a particular address that is auto generated by third party test tools with respect to the address that is pre-loaded on its S(5..0) pins. Once this sequence has been completed, the AS91L1003U device will respond to normal IEEE 1149.1 instructions. Note that addresses 60-63 have been reserved and the AS91L1003U device will not respond if the user selects these addresses.

To be selected, the AS91L1003U device should be in the Wait-for-Selection mode which can be entered into by issuing an asynchronous reset (through the deassertion of TRST) or by issuing synchronous reset (through the assertion of TMS for five cycles of TCK). After the device has been selected, it can be issued a GOTOWAIT instruction or a reset of the AS91L1003U device.

The internal IEEE1149.1 state machine of the AS91L1003U device is taken to the Shift-IR phase and the required Device-ID is shifted into the Instruction register. As the IEEE1149.1 state machine passes through the Update-IR phase, the address is matched to the value on the S(5-0) pins on the AS91L1003U device; if the values match then the AS91L1003U device is selected and is ready to receive any normal IEEE1149.1 command.

| S(5-0) value           | IR (7 – 0) value |

|------------------------|------------------|

| < 3A hex or 60 decimal | XXVVVVV          |

Table 1 - AS91L1003U Device Selection Table

Table 2 - AS91L1003U Multi Cast Group Selection Table

Selection Binary **Function** Mode Address XX000000 to Single AS91L1003U Single Address XX111010 selected the TDO of Mode the device will be active All accessible Broad-XX111011 Cast Mode AS91L1003U devices are selected for operation. TDO on all devices will be in HighZ Multi-Cast XX111100 Access all AS91L1003U device Group 0 that have been placed in GRP0 by their MCGR contents Multi-Cast XX111101 Access all Group 1 AS91L1003U device that have been placed in GRP1 by their MCGR contents Multi-Cast XX111110 Access all AS91L1003U device Group 2 that have been placed in GRP2 by their MCGR contents Multi-Cast XX111111 Access all Group 3 AS91L1003U device that have been placed in GRP3 by their MCGR contents

Table 3 - AS91L1003U Device Register Description

| Register<br>Name                              | Description                                                                                     |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------|

| Instruction<br>Register                       | AS91L1003U device addressing<br>and instruction-decode<br>IEEE Std. 1149.1 required<br>register |

| Boundary-<br>Scan<br>Register                 | IEEE Std. 1149.1 required register                                                              |

| Bypass<br>Register                            | IEEE Std. 1149.1 required register                                                              |

| Device<br>Identification<br>Register          | IEEE Std. 1149.1 optional<br>register                                                           |

| User Code<br>Register                         | IEEE Std. 1149.1 optional register                                                              |

| Status<br>Register                            | AS91L1003U device non intrusive 8-bit register pre load able from the I/O pins                  |

| Self Test<br>Register                         | AS91L1003U device specific single bit register for initiating self testing on a PCB             |

| Mode<br>Register                              | AS91L1003U device local-port configuration and control bits                                     |

| Auto Write<br>Register                        | AS91L1003U device Auto Write feature enable register                                            |

| Local Scan<br>Port Async<br>Reset<br>Register | AS91L1003U device Async reset register for the LSPs                                             |

| Instructions    | Hex Op-<br>Code | Binary Op-<br>Code | Data Register                                                            |

|-----------------|-----------------|--------------------|--------------------------------------------------------------------------|

| BYPASS          | FF              | 11111111           | Bypass Register                                                          |

| EXTEST          | 00              | 00000000           | Boundary-Scan Register                                                   |

| SAMPLE/PRELOAD  | 81              | 10000001           | Boundary-Scan Register                                                   |

| IDCODE          | AA              | 10101010           | Device Identification Register                                           |

| UNPARK          | E7              | 11100111           | Device Identification Register                                           |

| PARKTLR         | C5              | 11000101           | Device Identification Register                                           |

| PARKRTI         | 84              | 10000100           | Device Identification Register                                           |

| PARKPAUSE       | C6              | 11000110           | Device Identification Register                                           |

| GOTOWAIT*       | C3              | 11000011           | Device Identification Register                                           |

| MODESELECT      | 8E              | 10001110           | Mode Register                                                            |

| MCGRSELECT      | 03              | 00000011           | Multi-Cast Group Register.                                               |

| SOFTRESET       | 88              | 10001000           | Device Identification Register                                           |

| USERCODE        | 97              | 10010111           | User Programmable 32 Bit Identification Register                         |

| AUTOWR          | 98              | 10011000           | Auto Write Feature Enable Register                                       |

| STEST_PCB       | 99              | 10011001           | Single bit low pulse used to initiate function on PCB (SELF_TEST pin)    |

| STATUS_BYTE     | 9A              | 10011010           | User programmable status byte (USER_STATUS_DATA pins)                    |

| LSP_ASYNC_RESET | 9B              | 10011011           | Toggles LSP TRST while maintaining the AS91L1003U in the selected state. |

| Other Undefined | TBD             | TBD                | Device Identification Register                                           |

Table 4 - AS91L1003U Device Instruction Register OpCodes

Note: All instructions act on a single selected AS91L1003U device only.

<sup>\*</sup> This instruction causes the AS91L1003U to become unselected and revert to the Wait-for-Selection state.

## AS91L1003U device Register descriptions

#### **Bypass Register**

It is a mandatory single bit register that can be connected between PRIM\_TDI and PRIM\_TDO of the AS91L1003U device.

#### **Multi-Cast Group Register**

This 2-bit data register enables the host system to place the AS91L1003U into one of four distinct addressable groups.

| MCGR Register Bits [10] | Binary Selection Address | MCGR GROUP |

|-------------------------|--------------------------|------------|

| 00                      | XX111100                 | GRP0       |

| 01                      | XX111101                 | GRP1       |

| 10                      | XX111110                 | GRP2       |

| 11                      | XX111111                 | GRP3       |

**Table 5 - Multicast Group Register Mapping**

Note: The MCGR is reset to 00 upon receiving TRST or the entering of the Test-Logic-Reset state.

#### **IDCODE** Register

It is an optional 32-bit register that can be connected between PRIM TDI and PRIM TDO of the AS91L1003U device. The contents of the IDCODE register will be loaded with the following data when the AS91L1003U enters Test-Logic-Reset or passes through Capture-IR:

"000000000000000011011111"

Bits 0 to 11 indicate ALSC Jedec ID value of: "001101101111"

Bits 12 to 27 indicate the part number of the device: "000000000010000"

Bits 28 to 31 indicate the revision of the device: "0000"

#### **USERCODE** Register

The USERCODE is a 32-bit register that can addressed via standard IEEE1149.1 commands, which are automatically generated by third party test tools. The end user has the ability to program the binary value that will be transmitted back to the host via the USERCODE command; by setting the binary pattern on the USERCODE pins on the AS91L1003U device.

\* The AS91L1003U is a complete second source and pin for pin replacement of the Firecron JTS03U device.

#### STATUS BYTE Register

The STATUS BYTE register on the AS91L1003U device provides a means to sense the value on the USER STATUS DATA pins on the AS91L1003U device. This is an 8-bit field where the user can non-intrusively monitor signals on the printed circuit card via the IEEE1149.1 interface. The data in the register is loaded each time the state machine passes through the Capture-DR phase.

Note: Value is positive logic.

#### SELF\_TEST Register

The AS91L1003U device supports a single output pin that can be controlled via the IEEE1149.1 interface. When the instruction is loaded into the AS91L1003U instruction register, a single bit data register is connected which is set to zero when the TAP state machine enters Capture-DR. This will cause the SELF TEST pin to pulse low for one cycle of TCK, during the Update-DR phase. This low going pulse can be used to initiate self-tests on PCB's in a rack via the JTAG interface.

### LSP\_ASYNC\_RST Register

The AS91L1003U device supports async reset tests on the devices connected to the LSPs. The standard method of performing these tests by utilizing the PRIM TRST pin cannot be used as it will cause the AS91L1003U to deselect and all its internal registers to be reset. In order to enable async reset tests on the LSP, the test tool should instruct the device to toggle the local scan port reset pins while maintaining the set up information in the AS91L1003U. When the instruction is loaded into the AS91L1003U instruction register, a single bit data register is connected which is always set to zero when the TAP state machine enters Capture-DR. This will cause the LSP TRST pins to pulse low for one TCK cycle, during the Update-DR phase.

### **AUTOWR Register**

This is a 3-bit register that controls the passthrough of the JTAG Technologies AutoWR™ signal to any Local Scan Port. The register is reset to all zeros when entering the Test-Logic-Reset state.

| AutoWr Register<br>(Bit 2 – Bit 0) | LSP 3<br>AutoWr Signal | LSP 2<br>AutoWr Signal | LSP 1<br>AutoWr Signal |

|------------------------------------|------------------------|------------------------|------------------------|

| 000                                | High Z                 | High Z                 | High Z                 |

| 001                                | High Z                 | High Z                 | Active                 |

| 011                                | High Z                 | Active                 | Active                 |

| 100                                | Active                 | High Z                 | High Z                 |

| 101                                | Active                 | High Z                 | Active                 |

| 110                                | Active                 | Active                 | High Z                 |

| 111                                | Active                 | Active                 | Active                 |

Table 6 - AUTOWR Register Mapping

#### MODE\_SELECT Register

The Mode\_Select register allows the Local Scan Port of the AS91L1003U to be connected in various different configurations. A LSP is selected for connection within the scan chain by the contents of the Mode Select register.

If the Local Scan Port is not parked in a stable state, i.e.: Pause-DR, Pause-IR, Run-Test-Idle or Test-Logic-Reset, it will be connected into the active scan chain. If all LSPs are parked in a stable state, then the AS91L1003U will perform a loopback of TDI->Register->TDO.

| Mode_Select Register<br>(Bit 7 -> Bit 0) | LSP Configuration (If Port Unparked)                |

|------------------------------------------|-----------------------------------------------------|

| XXX0X000                                 | TDI->Register->TDO                                  |

| XXX0X001                                 | TDI->Register->LSP1->PAD->TDO                       |

| XXX0X010                                 | TDI->Register->LSP2->PAD->TDO                       |

| XXX0X011                                 | TDI->Register->LSP1->PAD->LSP2->PAD->TDO            |

| XXX0X100                                 | TDI->Register->LSP3->PAD->TDO                       |

| XXX0X101                                 | TDI->Register->LSP1->PAD->LSP3->PAD->TDO            |

| XXX0X110                                 | TDI->Register->LSP2->PAD->LSP3->PAD->TDO            |

| XXX0X111                                 | TDI->Register->LSP1->PAD->LSP2->PAD->LSP3->PAD->TDO |

**Table 7 - Mode Select Register Mapping**

X = don't care

**Register** = AS91L1003U device instruction register or any of the AS91L1003U device test data registers.

**PAD** = Insertion of a 1-bit register for data synchronization.

Upon entering Test-Logic-Reset, the register bits will be loaded with "0000000".

2003, 2004 © Copyright Alliance Semiconductor Corporation. All Rights reserved.

## Pass-Through Support within the AS91L1003U Device

The AS91L1003U device supports a Pass-Through mode where the primary or master IEEE1149.1 JTAG signals can be routed to any one of the LSPs. When this mode is activated, the "Debug Enable" signal for that LSP will go active, which can be used to place a processor such as the MPC8260 into BDM (Background Debug Mode) if required. If no processors are present in the LSP, the Pass-Through mode can be used to assist in the generation of the test vectors or memory tests for the devices that are linked into

the selected LSP. The pass-through feature has the effect of simplifying the test vector generation for the LSP, as it also has the effect of removing the AS91L1003U device from the test vector generation process.

The pass-through mode can be used in FPGA or PLD programming applications, where a direct path between the primary and a specific LSP is desired.

| PASS_THRU_ENABLE | PASS_THRU_SEL(1) | PASS_THRU_SEL(0) | Active LSP       |

|------------------|------------------|------------------|------------------|

| High             | Х                | Х                | Normal Operation |

| Low              | Low              | Low              | LSP1             |

| Low              | Low              | High             | LSP2             |

| Low              | High             | Low              | LSP3             |

Table 8 - Pass-Through mode in AS91L1003U

Note: When PASS\_THRU\_ENABLE enable is deasserted (logic "1"), then the LSPs are under control of the AS91L1003U device logic.

# **Signal Description**

| PIN NAME  | PIN<br>TYPE | PIN<br>NUMBER<br>LQFP | PIN<br>NUMBER<br>FPBGA | DESCRIPTION                                                                                                                                                                                                             | Stable signals states, with device unselected and active outputs on the device |

|-----------|-------------|-----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| LSP1_TCK  | OUT         | 31                    |                        | IEEE1149.1 Test Clock on Local Scan Port 1 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 00.  This pin is tri-stated for all other combinations.       | Buffered version<br>of signal present<br>on primary TCK                        |

| LSP1_TMS  | OUT         | 32                    |                        | IEEE1149.1 Test Mode Select on Local Scan Port 1 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 00.  This pin is tri-stated for all other combinations. | Logic '1'                                                                      |

| LSP1_TDO  | OUT         | 35                    |                        | IEEE1149.1 Test Data Out on Local Scan Port 1 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 00.  This pin is tri-stated for all other combinations.    | Logic '1'                                                                      |

| LSP1_TDI  | IN          | 33                    |                        | IEEE1149.1 Test Data In on Local<br>Scan Port 1 when<br>PASS_THRU_ENABLE is HIGH.<br>Pin is in Pass-Through mode when<br>PASS_THRU_ENABLE = 0 and<br>PASS_THRU_SEL[1:0] = 00.                                           |                                                                                |

| LSP1_TRST | OUT         | 29                    |                        | IEEE1149.1 Test Reset on Local Scan Port 1 when PASS_THRU_ENABLE is HIGH. Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 00.                                                            | Buffered version<br>of signal present<br>on primary TRST                       |

| PIN NAME    | PIN<br>TYPE | PIN<br>NUMBER<br>LQFP | PIN<br>NUMBER<br>FPBGA | DESCRIPTION                                                                                                                                                                                                            | Stable signals states, with device unselected and active outputs on the device |

|-------------|-------------|-----------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| LSP1_AutoWR | OUT         | 30                    |                        | Flash, Memory Auto-Write on Local Scan Port 1 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 00.  This pin is tri-stated for all other combinations.   | Logic '1'                                                                      |

| LSP1_DE     | OUT         | 28                    |                        | Pass-Through Debug Enable Output on Local Scan Port 1.  Active low output when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] =00.  This pin is high for all other combinations.                                          | Logic '1'                                                                      |

| LSP2_TCK    | OUT         | 41                    |                        | IEEE1149.1 Test Clock on Local Scan Port 2 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 01.  This pin is tri-stated for all other combinations.      | Buffered version<br>of signal present<br>on primary TCK                        |

| LSP2_TMS    | OUT         | 42                    |                        | IEEE1149.1 Test Mode Select on Local Scan Port 2 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 01. This pin is tri-stated for all other combinations. | Logic '1'                                                                      |

| LSP2_TDO    | OUT         | 45                    |                        | IEEE1149.1 Test Data Out on Local Scan Port 2 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 01.  This pin is tri-stated for all other combinations.   | Logic '1'                                                                      |

| PIN NAME    | PIN<br>TYPE | PIN<br>NUMBER<br>LQFP | PIN<br>NUMBER<br>FPBGA | DESCRIPTION                                                                                                                                                                                                          | Stable signals states, with device unselected and active outputs on the device |

|-------------|-------------|-----------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| LSP2_TDI    | IN          | 44                    | K7                     | IEEE1149.1 Test Data In on Local Scan Port 2 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 01.                                                      |                                                                                |

| LSP2_TRST   | OUT         | 37                    | K5                     | IEEE1149.1 Test Reset on Local Scan Port 2 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 01.                                                        | Buffered version<br>of signal present<br>on primary TRST                       |

| LSP2_AutoWR | OUT         | 40                    | K6                     | Flash, Memory Auto-Write on Local Scan Port 2 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 01.  This pin is tri-stated for all other combinations. | Logic '1'                                                                      |

| LSP2_DE     | OUT         | 36                    | J5                     | Pass-Through Debug Enable Output on Local Scan Port 2.  Active low output when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] =01.  This pin is high for all other combinations.                                        | Logic '1'                                                                      |

| LSP3_TCK    | OUT         | 49                    | K9                     | IEEE1149.1 Test Clock on Local Scan Port 3 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 10.  This pin is tri-stated for all other combinations.    | Buffered version<br>of signal present<br>on primary TCK                        |

| PIN NAME            | PIN<br>TYPE | PIN<br>NUMBER<br>LQFP | PIN<br>NUMBER<br>FPBGA | DESCRIPTION                                                                                                                                                                                                             | Stable signals states, with device unselected and active outputs on the device |

|---------------------|-------------|-----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| LSP3_TMS            | OUT         | 50                    | K10                    | IEEE1149.1 Test Mode Select on Local Scan Port 3 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 10.  This pin is tri-stated for all other combinations. | Logic '1'                                                                      |

| LSP3_TDO            | OUT         | 53                    | H10                    | IEEE1149.1 Test Data Out on Local Scan Port 3 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 10.  This pin is tri-stated for all other combinations.    | Logic '1'                                                                      |

| LSP3_TDI            | IN          | 52                    | J10                    | IEEE1149.1 Test Data In on Local Scan Port 3 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 10.                                                         |                                                                                |

| LSP3_TRST           | OUT         | 47                    | J8                     | IEEE1149.1 Test Reset on Local Scan Port 3 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 10.                                                           | Buffered version<br>of signal present<br>on primary TRST                       |

| LSP3_LSP_<br>AutoWR | OUT         | 48                    | K8                     | Flash, Memory Auto-Write on Local Scan Port 3 when PASS_THRU_ENABLE is HIGH.  Pin is in Pass-Through mode when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] = 10.  This pin is tri-stated for all other combinations.    | Logic '1'                                                                      |

| PIN NAME    | PIN<br>TYPE | PIN<br>NUMBER<br>LQFP | PIN<br>NUMBER<br>FPBGA | DESCRIPTION                                                                                                                                                                                                                                             | Stable signals states, with device unselected and active outputs on the device |

|-------------|-------------|-----------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| LSP3_DE     | OUT         | 46                    | H7                     | Pass-Through Debug Enable Output on Local Scan Port 3.  Active low output when PASS_THRU_ENABLE = 0 and PASS_THRU_SEL[1:0] =10.  This pin is high for all other combinations.                                                                           | Logic '1'                                                                      |

| PRIM_TCK    | IN          | 87                    | A6                     | IEEE1149.1 Primary Test Clock<br>Input.                                                                                                                                                                                                                 |                                                                                |

| PRIM_TMS    | IN          | 21                    | G2                     | IEEE1149.1 Primary Test Mode<br>Select Input.                                                                                                                                                                                                           |                                                                                |

| PRIM_TDO    | OUT         | 20                    | G1                     | IEEE1149.1 Primary Test Data<br>Output.<br>This pin is tri-stated when<br>AS91L1003 is not selected.                                                                                                                                                    | HighZ                                                                          |

| PRIM_TDI    | IN          | 19                    | G3                     | IEEE1149.1 Primary Test Data Input                                                                                                                                                                                                                      |                                                                                |

| PRIM_TRST   | IN          | 22                    | H2                     | IEEE1149.1 Primary Test Reset Input.  This active low asynchronous reset input signal places AS91L1003U in Wait-for-Selection state.                                                                                                                    |                                                                                |

| PRIM_AutoWR | IN          | 16                    | F1                     | Primary Auto-Write Input controlled by test equipment to shorten Flash memory programming.                                                                                                                                                              |                                                                                |

| S[5:0]      | IN          | 8,7,6,5,100,<br>99    | D2,D1,D3,C2,<br>B2,A2  | Slot Address (5:0) Inputs.  Used to set address at which  AS91L1003U will respond; typically set by hardwired connection on the backplane.                                                                                                              |                                                                                |

| *TOE        | IN          | 88                    | В6                     | Test Output Enable Input.  Tri-states all LSPs, when asserted low.                                                                                                                                                                                      |                                                                                |

| LSP_RESET_n | IN          | 14                    | F4                     | Local Scan Port Reset Input.  Active low resets AS91L1003U to "Wait-for-Selection" state and pulses all LSP TRST output pins to low. This resets all devices with TRST function; typically this signal would be connected to a power-on-reset function. |                                                                                |

| PIN NAME                  | PIN<br>TYPE | PIN<br>NUMBER<br>LQFP                             | PIN<br>NUMBER<br>FPBGA                                            | DESCRIPTION                                                                                                                                                                                                                                  | Stable signals states, with device unselected and active outputs on the device |

|---------------------------|-------------|---------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| AS91L1003U_<br>SELECTED   | OUT         | 25                                                |                                                                   | AS91L1003U_Selected Output.  Active low when AS91L1003U is selected; typically used to control off board buffering.                                                                                                                          |                                                                                |

| LSP_ENABLE                | OUT         | 24                                                |                                                                   | Local Scan Port Enable Output.  Active low output when AS91L1003U is selected; typically used to set IEEE1149.1 compliance enable pins on devices.                                                                                           |                                                                                |

| USERCODE<br>[15:0]        | IN          | ,69,70,71,7<br>2,75,76,77,                        | ,D9,D10,D8,C<br>9,C10,B10,B9<br>,A9,A8,B8,A7,<br>B7 (MSB-<br>LSB) | Used to establish board type and revision so as to ensure correct IEEE1149.1 test vector sets are applied.                                                                                                                                   |                                                                                |

| USER_STATUS<br>_BYTE[7:0] | IN          | 84, 85, 92,<br>93, 94, 96,<br>97, 98<br>(MSB-LSB) | B4,A4,B3,A3(<br>MSB-LSB)                                          | USER_Status_Byte Inputs.  Used to provide status information of the PCB under test back to the test master via the IEEE1149.1 bus. Eight signals levels can be monitored and then reported via the IEEE1149.1 bus in a non intrusive manner. |                                                                                |

| SELF_TEST                 | OUT         | 27                                                | K2                                                                | Provides a low going output pulse under command from the IEEE1149.1 bus, which can be used to start self-test functions on a PCB.                                                                                                            | Logic '1'                                                                      |

| PASS_THRU_<br>ENABLE      | IN          | 9                                                 |                                                                   | PASS_THRU Enable Input.  Active high disables Pass-Through mode.  Active low enables Pass-Through mode.                                                                                                                                      |                                                                                |

| PASS_THRU_<br>SEL[1:0]    | IN          | 12,10                                             |                                                                   | PASS_THRU Select Inputs.  Used to select active routing of Pass-Through ports enabled by active low on PASS_THRU_ENABLE pin.  00 = LSP1 01 = LSP 10 = LSP3                                                                                   |                                                                                |

| PIN NAME         | PIN<br>TYPE | PIN<br>NUMBER<br>LQFP                                  | PIN<br>NUMBER<br>FPBGA     | DESCRIPTION                                                      | Stable signals states, with device unselected and active outputs on the device |

|------------------|-------------|--------------------------------------------------------|----------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------|

| GND              | POWER       | 38, 86, 11,<br>26, 43, 59,<br>74, 95, 2,<br>17, 54, 90 | D7, E5, F6,<br>G4,H8, H9,  | Ground Pins.                                                     |                                                                                |

| VCC              | POWER       | 18, 34, 51,                                            |                            | ·                                                                |                                                                                |

| ASIC_TEST_<br>EN | IN          | 89                                                     |                            | Factory Test_Enable Input.  This pin should be left unconnected. |                                                                                |

| ASIC_TCK         | IN          | 62                                                     | F8                         | IEEE1149.1 ASIC Test Clock Input.                                |                                                                                |

| ASIC_TMS         | IN          | 15                                                     |                            | IEEE1149.1 ASIC Test Mode Select Input.                          |                                                                                |

| ASIC_TDO         | OUT         | 73                                                     | A10                        | IEEE1149.1 ASIC Test Clock Output.                               |                                                                                |

| ASIC_TDI         | IN          | 4                                                      | A1                         | IEEE1149.1 ASIC Test Clock Input.                                |                                                                                |

| No Connects      |             | 1,13,63,61,<br>60,58,57                                | C1,E2,F7,F10<br>,F9,G8,G10 |                                                                  |                                                                                |

Table 10 - AS91L0003U Signal Description

# **Absolute Maximum Ratings**

| Parameter                                      | Maximum Range        |

|------------------------------------------------|----------------------|

| Supply Voltage (Vcc)                           | -0.3V to 5.5V        |

| DC Input Voltage (Vi)                          | -0.5V to Vcc +0.5V   |

| Max sink current when Vi = -0.5V               | -20mA                |

| Max source current when Vi = Vcc + 0.5V        | +20mA                |

| Max Junction Temperature with power applied Tj | +125 degrees C       |

| Max Storage temperature                        | -55 to +150 degree C |

**Table 11 - Absolute Maximum Ratings**

Note: Stress above the stated maximum values may cause irreparable damage to the device. Correct operation of the device at these values is not guaranteed.

# **Recommended Operating Conditions**

| Parameter                             | Operating Range                       |

|---------------------------------------|---------------------------------------|

| Supply Voltage (Vcc)                  | 3.0V to 3.6V                          |

| Input Voltage (Vi)                    | 0V to Vcc                             |

| Output Voltage (Vo)                   | 0V to Vcc                             |

| Operating Temperature (Ta) Commercial | 0 C to 70 C                           |

| Industrial (Ta)                       | -40 deg C to +85 deg C, 3.00V to 3.6V |

**Table 12 - Recommended Operating Conditions**

# **AC Electrical Characteristics**

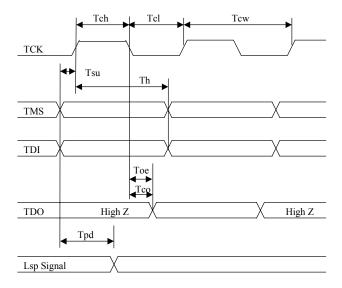

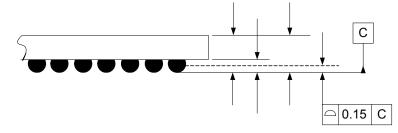

Figure 4 - AS91L1003U AC Timing Diagram

| SYMBOL | Parameter                           | MIN | MAX | UNITS |

|--------|-------------------------------------|-----|-----|-------|

| Tcw    | TCK clock pulse width               | 100 | -   | ns    |

| Tch    | TCK pulse width high                | 50  | -   | ns    |

| Tcl    | TCK pulse width low                 | 50  | -   | ns    |

| Tsu    | TCK Setup time                      | 30  | -   | ns    |

| Th     | TCK Hold time                       | 40  | -   | ns    |

| Toe    | Neg Edge TCK to valid data enable   | 20  | -   | ns    |

| Tco    | Neg Edge TCK to valid data          | 15  | -   | ns    |

| Tpd    | Pass through Mode Primary/LSP Delay | -   | 10  | ns    |

Table 9 - AS91L1003U AC Timing Information

# **DC Electrical Characteristics**

| Symbol           | Parameter                        | Min   | Max          | Condition                            |

|------------------|----------------------------------|-------|--------------|--------------------------------------|

| V <sub>IH</sub>  | Minimum High Input<br>Voltage    | 2.0   | 5.25         |                                      |

| V <sub>IL</sub>  | Maximum Low Input<br>Voltage     | -0.3V | 0.8V         |                                      |

|                  |                                  |       |              |                                      |

| Symbol           | Parameter                        |       | Value        | Condition                            |

| V <sub>OH</sub>  | Minimum High Output<br>Voltage   |       |              | loh=24mA or 8mA as<br>defined by pin |

| V <sub>OL</sub>  | Minimum Low Output<br>Voltage    |       |              | lol=24mA or 8mA as<br>defined by pin |

| l <sub>oz</sub>  | Tristate output leakage          |       | -10 or 10 mA |                                      |

| I <sub>cc</sub>  | Maximum quiecennt supply current |       | 2mA          |                                      |

| I <sub>ccd</sub> | Maximum dynamic supply current   |       | 80mA         | TCK freq equal to 10 MHz             |

Table 13 - AS91L1003U DC Electrical Characteristics

# **AC Timing Information**

| From         | То           | Туре       | Value  |

|--------------|--------------|------------|--------|

| Prim_TCK     | Prim inputs  | Setup      | 3ns    |

| Prim_TCK     | Prim inputs  | Hold       | 2ns    |

| LSP[1:3]_TCK | LSP inputs   | Setup      | 7ns    |

| LSP[1:3]_TCK | LSP inputs   | Hold       | 0ns    |

| Prim inputs  | LSP outputs  | Comb Delay | 11.5ns |

| LSP inputs   | Prim outputs | Comb Delay | 10ns   |

| Prim_TCK     | LSP_TCK      | Comb Delay | 8.5ns  |

| Prim_TCK     | Prim outputs | Delay      | 10ns   |

| LSP_TCK      | LSP outputs  | Delay      | 5ns    |

| Prim_TCK     |              | Freq       | 40MHz  |

Table 14 - AS91L1003U AC Timing Information

# **Packaging Information**

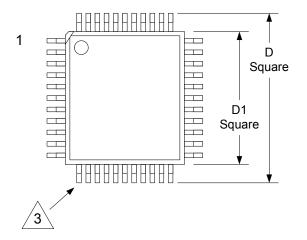

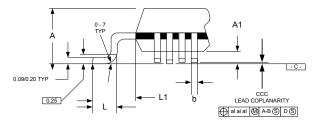

The AS91L1003U is available in a 100-pin LQFP or a 100-pin FPBGA lead free package.

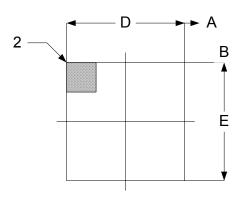

| SYMBOL | LEADS<br>TOL. | 100 LEAD       |

|--------|---------------|----------------|

| А      | MAX.          | 1 .6 0         |

| A 1    | M IN M A X    | 0.05 0.15      |

| A 2    | MINNOMMAX     | 1.35 1.40 1.45 |

| D      | BASIC         | 16.00          |

| D 1    | BASIC         | 1 4 .0 0       |

| L      | ±0.15         | 0 .6 0         |

| L 1    | REF           | 1.00           |

| b      | M IN M A X    | 0.17 0.27      |

| е      | BASIC         | 0.50           |

| ссс    | MAX           | 0.08           |

| d d d  | NOM           | 0.08           |

| JEC    | DEC REF#      | M S - 0 2 6    |

- NOTES:

1. ALL LINEAR DIMENSIONS ARE IN MILLIMETERS.

2. PLASTIC BODY DIMENSIONS DO NOT INCLUDE FLASH OR PROTUSION.

MAX ALLOWABLE 0.25 PER SIDE.

3. LEAD COUNT ON DRAWING NOT REPRESENTATIVE OF ACTUAL PACKAGE.

Figure 5 - LQFP-100

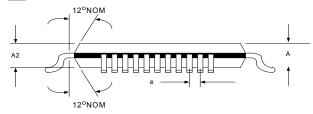

|      | Revisions                                              |       |          |  |  |

|------|--------------------------------------------------------|-------|----------|--|--|

| REV. | DESCRIPTION                                            | ECN   | DATE     |  |  |

| Α    | Initial document release.                              | 91253 | 12-04-01 |  |  |

| В    | Updated ball coplanarity limits from 0.20mm to 0.15mm. |       |          |  |  |

|      |                                                        |       |          |  |  |

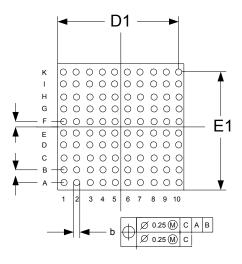

| DIMENSIONS     |                   |      |      |  |

|----------------|-------------------|------|------|--|

| SYMBOL         | MIN.              | NOM. | MAX. |  |

| A              |                   |      | 1.70 |  |

| A1             | 0.30              |      |      |  |

| A2             | 0.25              |      | 1.10 |  |

| b              | 0.50              | 0.60 | 0.70 |  |

| D              | 11.00 BSC         |      |      |  |

| D1             | 9.00 BSC          |      |      |  |

| E              | 11.00 BSC         |      |      |  |

| E1             | 9.00 BSC          |      |      |  |

| е              | 1.00              |      |      |  |

| PACKAGE NUMBER | FBGA0100-11F      |      |      |  |

| JEDEC REF#     | MO-192 VAR. AAC-1 |      |      |  |

Figure 6 - FPBGA-100

Clock speed

10 = Low Frequency

40 = High Frequency

Device Selector Guide and Ordering Information **AS91L** XXXX UU - CC PP - TEMP - L Aliance Semiconductor system solution Blank = leaded F = lead free G = green Device family ◀ 1001 C = Commercial (0 to 70 degrees C) 1002 I = Industrial (-40 to 85 degrees C) 1003 1006 Package L100 = 100 pin LQFP F100 = 100 pin FPBGA Product version S = standard

Figure 7 - Part Numbering Guide

U = 16-bit user code

E = enhanced

BU = 8-bit status/user code

| Part Number            | Description                                                                      | Availability                                |

|------------------------|----------------------------------------------------------------------------------|---------------------------------------------|

| AS91L1003U - 10L100-C  | 3-Port JTAG Gateway, 100-pin LQFP package, commercial                            | now                                         |

| AS91L1003U - 10L100-I  | 3-Port JTAG Gateway, 100-pin LQFP package, industrial                            | now                                         |

| AS91L1003U - 10F100-C  | 3-Port JTAG Gateway, 100-pin FPBGA package, commercial                           | Please Contact<br>Alliance<br>Semiconductor |

| AS91L1003U - 10F100-I  | 3-Port JTAG Gateway, 100-pin FPBGA package, industrial                           | Please Contact<br>Alliance<br>Semiconductor |

| AS91L1003U - 40L100-C  | 3-Port JTAG Gateway, 100-pin LQFP package, commercial, High Frequency            | Please Contact<br>Alliance<br>Semiconductor |

| AS91L1003U - 40L100-CF | 3-Port JTAG Gateway, 100-pin LQFP package, commercial, lead free, High Frequency | now                                         |

| AS91L1003U - 40L100-I  | 3-Port JTAG Gateway, 100-pin LQFP package, industrial, High Frequency            | Please Contact<br>Alliance<br>Semiconductor |

| AS91L1003U - 40L100-IF | 3-Port JTAG Gateway, 100-pin LQFP package, industrial, lead free, High Frequency | now                                         |

| AS91L1003U - 40F100-C  | 3-Port JTAG Gateway, 100-pin FPBGA, commercial, High Frequency                   | Please Contact<br>Alliance<br>Semiconductor |

| AS91L1003U – 40F100-CG | 3-Port JTAG Gateway, 100-pin FPBGA, commercial, green package, High Frequency    | Please Contact<br>Alliance<br>Semiconductor |

| AS91L1003U – 40F100-I  | 3-Port JTAG Gateway, 100-pin FPBGA, industrial, High Frequency                   | Please Contact<br>Alliance<br>Semiconductor |

| AS91L1003U – 40F100-IG | 3-Port JTAG Gateway, 100-pin FPBGA, industrial, green package, High Frequency    | Please Contact<br>Alliance<br>Semiconductor |

**Table 15 - Valid Part Number Combinations**

| Device<br>Master | Description          | Package Options          |          |

|------------------|----------------------|--------------------------|----------|

|                  |                      | FPBGA-100<br>(1mm pitch) | LQFP-100 |

| AS91L1001        | JTAG Test Controller | Х                        | Х        |

| AS91L1002        | JTAG Test Sequencer  | х                        | Х        |

| AS91L1003U       | 3-Port Gateway       | х                        | Х        |

| AS91L1006BU      | 6-Port Gateway       | Х                        | Х        |

**Table 16 - JTAG Controller Product Family**