32 Bit Driver August 1996

#### **Features**

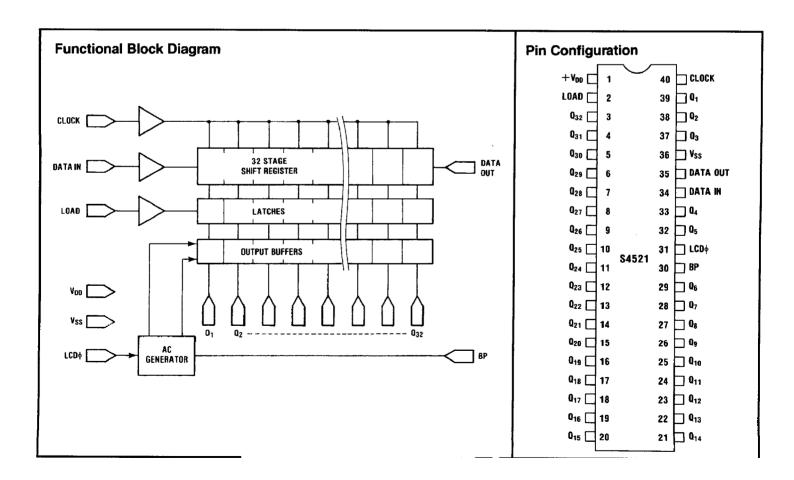

- · Drives Up to 32 Devices

- Cascadable

- On Chip Oscillator

- Requires Only 3 Control Lines

- CMOS Construction For: Wide Supply Range High Noise Immunity Wide Temperature Range

### **Applications:**

- Liquid Crystal Displays

- LED and Incandescent Displays

- Solenoids

- Print Head Drives

- . DC and Stepping Motors

- Relays

### **General Description**

The S4521 is an MOS/LSI circuit that drives a variety of output devices, usually under microprocessor control. This device requires only three control lines due to its serial input construction. It latches the data to be output, relieving the microprocessor from the task of generating the required waveform, or it may be used to bring data directly to the drivers. The part acts as a versatile peripheral to drive displays, motors, relays and solenoids within its output limitations. It is especially well suited to driving liquid crystal displays. with a backplane A.C. signal option that is provided. The A.C. frequency of the backplane output that can be user supplied or generated by attaching a capacitor to the LCD, input, which controls the frequency of the internal oscillator. One circuit will drive up to 32 devices and more can be driven by cascading several drivers together.

August 1996 32 Bit Driver

## **Absolute Maximum Ratings**

| V <sub>DD</sub>                  | 0.3 to + 17V |

|----------------------------------|--------------|

| Inputs (CLK, DATA IN, LOAD, LCD) |              |

| Power Dissipation                |              |

| Storage Temperature              |              |

| Operating Temperature            |              |

# **Electrical Characteristics:** $3V \le V_{DD} \le 13V$ , unless otherwise noted

| Symbol                               | Parameter                                      | Min.                                       | Max.                | Units    | Test Condition                                                                                                 |

|--------------------------------------|------------------------------------------------|--------------------------------------------|---------------------|----------|----------------------------------------------------------------------------------------------------------------|

| $V_{DD}$                             | Supply Voltage                                 | 3                                          | 13                  | V        |                                                                                                                |

|                                      | Supply Current                                 |                                            |                     |          |                                                                                                                |

| I <sub>DD1</sub><br>I <sub>DD2</sub> | Operating<br>Quiescent                         |                                            | 200<br>200          | μA<br>μA | $f_{BP} = 120$ Hz, No Load, $V_{DD} = 5$ V LCD $\phi$ High or Low, $f_{BP} = 0$ Load @ Logic 0, $V_{DD} = 5$ V |

|                                      | Inputs (CLK, DATA IN, LOAD)                    |                                            |                     |          |                                                                                                                |

| $V_{iH}$                             | High Level                                     | 0.6 V <sub>DD</sub><br>0.5 V <sub>DD</sub> | V <sub>DD</sub>     | V<br>V   | 3V≤V <sub>DD</sub> <5V<br>5V≤V <sub>DD</sub> ≤13V                                                              |

| V <sub>IL</sub><br>Iլ                | Low Level<br>Input Current                     | V <sub>SS</sub>                            | 0.2 V <sub>DD</sub> | V<br>μA  |                                                                                                                |

| IL<br>CI                             | Input Capacitance                              |                                            | 5                   | pF       |                                                                                                                |

| f <sub>CLK</sub>                     | CLK Rate                                       | DC                                         | 2                   | MHz      | 50% Duty Cycle                                                                                                 |

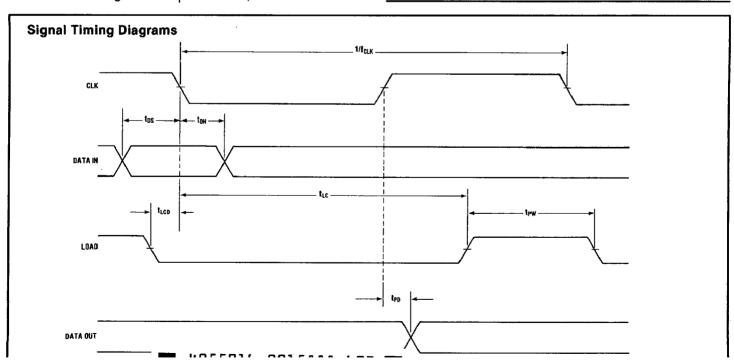

| t <sub>DS</sub>                      | Data Set-Up Time                               | 100                                        |                     | ns       | Data Change to CLK Falling Edge                                                                                |

| t <sub>DH</sub>                      | Data Hold Time                                 | 10                                         |                     | ns       | Falling CLK Edge to Data Change                                                                                |

| t <sub>PW</sub>                      | Load Pulse Width                               | 200                                        |                     | ns       |                                                                                                                |

| t <sub>PD</sub>                      | Data Out Prop. Delay                           |                                            | 220                 | ns       | $C_L = 30 pF$ , From Rising CLK Edge                                                                           |

| t <sub>LC</sub>                      | Load Pulse Set-Up                              | 300                                        |                     | ns       | Falling CLK Edge to Rising Load<br>Pulse                                                                       |

| t <sub>LCD</sub>                     | Load Pulse Delay                               | 0                                          |                     | ns       | Falling Load Pulse to Falling CLK<br>Edge                                                                      |

| V <sub>OAVG</sub>                    | DC Bias (Average) Any Q<br>Output to Backplane |                                            | ± 25                | mV       | $f_{BP} = 120Hz$                                                                                               |

| V <sub>IH</sub>                      | LCDφ Input High Level                          | .9 V <sub>DD</sub>                         | V <sub>DD</sub>     | ٧        | Externally Driven                                                                                              |

| V <sub>IL</sub>                      | LCDø Input Low Level                           | V <sub>SS</sub>                            | .1 V <sub>DD</sub>  | ٧        | Externally Driven                                                                                              |

|                                      | Capacitance Loads                              |                                            |                     |          |                                                                                                                |

| $C_{LQ}$                             | Q Output<br>Backplane                          |                                            | 50,000<br>1.5       | pF<br>μF | $f_{BP} = 120$ Hz<br>$f_{BP} = 120$ Hz, See Note 8                                                             |

| R <sub>ON</sub>                      | Q Output Impedance                             |                                            | 3.0                 | KΩ       | $I_{L} = 10 \mu A, V_{DD} = 5 V$                                                                               |

| R <sub>ON</sub>                      | Backplane Output Impedance                     |                                            | 100                 | Ω        | $I_{L} = 10 \mu A, \ V_{DD} = 5 V$                                                                             |

| R <sub>ON</sub>                      | Data Out Output Impedance                      |                                            | 3.0                 | KΩ       | $I_{L} = 10 \mu A, V_{DD} = 5 V$                                                                               |

32 Bit Driver August 1996

## **Operating Notes**

- 1. The shift register shifts on the falling edge of CLK. It outputs on the rising edge of the CLK.

- 2. The buffer number corresponds to how many clock pulses have occurred since its data was present at the input (e.g., the data on Q10 was input 10 clock pulses earlier).

- 3. A logic 1 on Data In causes a Q output to be out of phase with the Backplane.

- A logic 1 on Load causes a parallel load of the data in the shift register, into the latches that control the Q output drivers.

- 5. To cascade units, (a) connect the Data Out of one chip to Data In of next chip, and (b) either connect Backplane of one chip to LCDφ of all other chips (thus one RC provides frequency control for all chips) or connect LCDφ of all chips to a common driving signal. If the former is chosen, the Backplane that is tied to the LCDφ inputs of the other chips should not also be connected to the Backplanes of those chips.

- 6. If LCD is driven, it is in phase with the Backplane output.

- 7. The LCD\$\phi\$ pin can be used in two modes, driven or self-oscillating. If LCD\$\phi\$ is driven, the circuit will

- sense this condition. If the LCD $\phi$  pin is allowed to oscillate, its frequency is determined by an external capacitor. The Backplane frequency is a divide by 32 of the LCD $\phi$  frequency, in the self-oscillating mode.

- 8. In the self-oscillating mode, the backplane frequency is approximately defined by the relationship  $f_{BP}(Hz) = 0.2 \div C(in \mu F)$  at  $V_{DD} = 5V$ .

- 9. If the total display capacitance is greater than 100,000 pF, a decoupling capacitor of  $1\mu$ F is required across the power supply (pins 1 and 36).

### **Pin Description**

| Pin #           | Name            | Description                                                     |

|-----------------|-----------------|-----------------------------------------------------------------|

| 1               | V <sub>DD</sub> | Logic and Q Output Supply Voltage                               |

| 2               | LOAD            | Signal to Latch Data from Registers                             |

| 30              | BP              | Backplane Drive Output                                          |

| 31              | LCD <b>∳</b>    | Backplane Drive Input                                           |

| 34              | DATA IN         | Data Input to Shift Register                                    |

| 35              | DATA OUT        | Data Output from Shift Register-<br>primarily used in cascading |

| 36              | $V_{SS}$        | Ground Connection                                               |

| 40              | CLOCK           | System Clock Input                                              |

| 3-29,           |                 | ·                                                               |

| 32-33,<br>37-39 | $Q_1 - Q_{32}$  | Direct Drive Outputs                                            |