# CDP1883, CDP1883C

# CMOS 7-Bit Latch and Decoder Memory Interfaces

March 1997

### Features

- Performs Memory Address Latch and Decoder Functions Multiplexed or Non-Multiplexed

- Interfaces Directly with the CDP1800-Series Microprocessors

- · Allows Decoding for Systems Up to 32K Bytes

# **Ordering Information**

| 5V        | 10V      | TEMP.<br>RANGE                              | PACKAGE | PKG.<br>NO. |

|-----------|----------|---------------------------------------------|---------|-------------|

| CDP1883CE | CDP1883E | -40 <sup>o</sup> C to<br>+85 <sup>o</sup> C | PDIP    | E20.3       |

# Description

The CDP1883 is a CMOS 7-bit memory latch and decoder circuit intended for use in CDP1800-series microprocessor systems. It can serve as a direct interface between the multiplexed address bus of this system and up to four 8K x 8-bit memories to implement a 32K-byte memory system. With four 4K x 8-bit memories, a 16K-byte system can be decoded.

The device is also compatible with non-multiplexed address bus microprocessors. By connecting the clock input to  $V_{DD}$ , the latches are in the data-following mode and the decoded outputs can be used in general-purpose memory-system applications.

The CDP1833 is compatible with CDP1800-series microprocessors operating at maximum clock frequency.

The CDP1883 and CDP1883C are functionally identical. They differ in that the CDP1883 has a recommended operating voltage range of 4V to 10.5V and the C version has a recommended operating voltage range of 4V to 6.5V.

The CDP1883 and CDP1883C are supplied in 20 lead dual-in-line plastic packages (E Suffix).

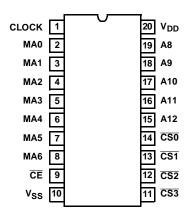

### **Pinout**

CDP1883, CDP1883C (PDIP) TOP VIEW

# CDP1883, CDP1883C

## **Absolute Maximum Ratings**

### DC Supply Voltage Range, (V<sub>DD</sub>) (All Voltages Referenced to V<sub>SS</sub> Terminal) CDP1883 . . . . . -0.5V to +11V CDP1883C.....--0.5V to +7V Input Voltage Range, All Inputs . . . . . . . . -0.5V to $V_{\mbox{DD}}$ +0.5V

## **Thermal Information**

| Thermal Resistance (Typical)                                 | $\theta_{JA}$ (°C/W)                 |

|--------------------------------------------------------------|--------------------------------------|

| PDIP Package                                                 | 80                                   |

| Device Dissipation Per Output Transistor                     |                                      |

| T <sub>A</sub> = Full Package Temperature Range              | 100mW                                |

| Operating Temperature Range (T <sub>A</sub> )                |                                      |

| Package Type E40                                             | <sup>o</sup> C to +85 <sup>o</sup> C |

| Storage Temperature Range (T <sub>STG</sub> )65 <sup>o</sup> | C to +150°C                          |

| Lead Temperature (During Soldering)                          |                                      |

| At distance 1/16  ± 1/32 In. (1.59 ± 0.79mm)                 |                                      |

| from case for 10s max                                        | +265 <sup>0</sup> C                  |

CAUTION: Stresses above those listed in the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operation section of this specification is not implied.

**Recommended Operating Conditions** At T<sub>A</sub> = Full Package Temperature Range. For maximum reliability, operating conditions should be selected so that operation is always within the following ranges:

|                            |        | CDP             | 1883     | CDP1            |          |       |

|----------------------------|--------|-----------------|----------|-----------------|----------|-------|

| PARAMETER                  | SYMBOL | MIN             | MAX      | MIN             | MAX      | UNITS |

| DC Operating Voltage Range |        | 4               | 10.5     | 4               | 6.5      | V     |

| Input Voltage Range        |        | V <sub>SS</sub> | $V_{DD}$ | V <sub>SS</sub> | $V_{DD}$ | V     |

# $\textbf{Static Electrical Specifications} \quad \text{At T}_{A} = -40^{o}\text{C to } +85^{o}\text{C}, \text{ V}_{DD} \pm 5\%, \text{ Except as Noted:}$

|                       |                  | CONDITIONS         |                        |                        |       | CDP1883      |     |       | CDP1883C     |     |       |  |

|-----------------------|------------------|--------------------|------------------------|------------------------|-------|--------------|-----|-------|--------------|-----|-------|--|

| PARAMETER             | SYMBOL           | V <sub>O</sub> (V) | V <sub>IN</sub><br>(V) | V <sub>DD</sub><br>(V) | MIN   | (NOTE 1) TYP | MAX | MIN   | (NOTE 1) TYP | MAX | UNITS |  |

| Quiescent Device      | I <sub>DD</sub>  | -                  | 0, 5                   | 5                      | -     | 1            | 10  | -     | 5            | 50  | μΑ    |  |

| Current               |                  | -                  | 0, 10                  | 10                     | -     | 10           | 100 | -     | -            | -   | μΑ    |  |

| Output Low Drive      | l <sub>OL</sub>  | 0.4                | 0, 5                   | 5                      | 1.6   | 3.2          | -   | 1.6   | 3.2          | -   | mA    |  |

| (SINK) Current        | Current          | 0.5                | 0, 10                  | 10                     | 3.2   | 6.4          | -   | -     | -            | -   | mA    |  |

| Output High Drive     | ІОН              | 4.6                | 0, 5                   | 5                      | -1.15 | -2.3         | -   | -1.15 | -2.3         | -   | mA    |  |

| (Source) Current      |                  | 9.5                | 0, 10                  | 10                     | -2.3  | -4.6         | -   | -     | -            | -   | mA    |  |

| Output Voltage        | V <sub>OL</sub>  | -                  | 0, 5                   | 5                      | -     | 0            | 0.1 | -     | 0            | 0.1 | V     |  |

| Low-Level (Note 2)    |                  | -                  | 0, 10                  | 10                     | -     | 0            | 0.1 | -     | -            | -   | V     |  |

| Output Voltage        | V <sub>OH</sub>  | -                  | 0, 5                   | 5                      | 4.9   | 5            | -   | 4.9   | 5            | -   | V     |  |

| High-Level (Note 2)   |                  | -                  | 0, 10                  | 10                     | 9.9   | 10           | -   | -     | -            | -   | V     |  |

| Input Low Voltage     | V <sub>IL</sub>  | 0.5, 4.5           | -                      | 5                      | -     | -            | 1.5 | -     | -            | 1.5 | V     |  |

|                       |                  | 0.5, 9.5           | -                      | 10                     | -     | =            | 3   | -     | -            | -   | V     |  |

| Input High Voltage    | V <sub>IH</sub>  | 0.5, 4.5           | -                      | 5                      | 3.5   | -            | -   | 3.5   | -            | -   | V     |  |

|                       |                  | 0.5, 9.5           | -                      | 10                     | 7     | -            | -   | -     | -            | -   | V     |  |

| Input Leakage Current | I <sub>IN</sub>  | Any                | 0, 5                   | 5                      | -     | -            | ±1  | -     | -            | ±1  | μΑ    |  |

|                       |                  | Input              | 0, 10                  | 10                     | -     | -            | ±2  | -     | -            | -   | μΑ    |  |

| Operating Current     | I <sub>DD1</sub> | 0, 5               | 0, 5                   | 5                      | -     | -            | 2   | -     | -            | 2   | mA    |  |

| (Note 3)              |                  | 0, 10              | 0, 10                  | 10                     | -     | -            | 4   | -     | -            | -   | mA    |  |

Static Electrical Specifications At  $T_A = -40^{\circ}C$  to +85°C,  $V_{DD} \pm 5\%$ , Except as Noted: (Continued)

|                                   |                  | CONDITIONS            |                        |                        |     | CDP1883         |     |     | CDP1883C        |     |       |

|-----------------------------------|------------------|-----------------------|------------------------|------------------------|-----|-----------------|-----|-----|-----------------|-----|-------|

| PARAMETER                         | SYMBOL           | ν <sub>ο</sub><br>(۷) | V <sub>IN</sub><br>(V) | V <sub>DD</sub><br>(V) | MIN | (NOTE 1)<br>TYP | MAX | MIN | (NOTE 1)<br>TYP | MAX | UNITS |

| Minimum Data<br>Retention Voltage | V <sub>DR</sub>  | \                     | $V_{DD} = V_{DR}$      |                        |     | 2               | 2.4 | -   | 2               | 2.4 | V     |

| Data Retention Current            | I <sub>DR</sub>  | \                     | V <sub>DD</sub> = 2.4V |                        |     | 0.01            | 1   | -   | 0.5             | 5   | μΑ    |

| Input Capacitance                 | C <sub>IN</sub>  | -                     | -                      | -                      | -   | 5               | 7.5 | -   | 5               | 7.5 | pF    |

| Output Capacitance                | C <sub>OUT</sub> | -                     | -                      | -                      | -   | 10              | 15  | -   | 10              | 15  | pF    |

### NOTES:

- 1. Typical values are for  $T_A = +25^{\circ}C$ .

- 2.  $I_{OL} = I_{OH} = \mu A$

- 3. Operating current measured at 200kHz for  $V_{DD}$  = 5V and 400kHz for  $V_{DD}$  = 10V, with outputs open circuit.

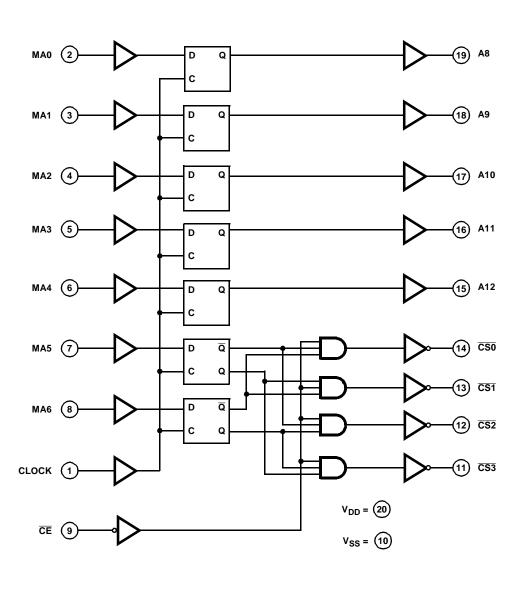

# **Functional Diagram**

# Signal Descriptions/Pin Functions

**CLOCK:** Latch Input Control - a high on the clock input will allow data to pass through the latch to the output pin. Data is latched on the high-to-low transition of the clock input. This pin is connected to TPA in CDP1800-series systems and tied to  $V_{DD}$  for other applications.

**MA0 - MA4:** Address inputs to the high-byte address latches.

**MA5 - MA6:** High byte address inputs decoded to produce chip selects  $\overline{\text{CS0}}$  -  $\overline{\text{CS3}}$ .

CE: CHIP ENABLE input - A low on this pin will enable the chip select decoder. A high on this pin forces CS0, CS1, CS2, and CS3 outputs to a high (false) state.

A8 - A12: Latched high-byte address outputs.

**CS0** - **CS3**: One of four latched and decoded Chip Select outputs.

V<sub>DD</sub>, V<sub>SS</sub>: Power and ground pins, respectively.

### **TRUTH TABLE**

|    | INP | UTS |     | OUTPUTS        |     |     |     |  |  |

|----|-----|-----|-----|----------------|-----|-----|-----|--|--|

| CE | CLK | MA5 | MA6 | CS0            | CS1 | CS2 | CS3 |  |  |

| 0  | 1   | 0   | 0   | 0              | 1   | 1   | 1   |  |  |

| 0  | 1   | 1   | 0   | 1              | 0   | 1   | 1   |  |  |

| 0  | 1   | 0   | 1   | 1              | 1   | 0   | 1   |  |  |

| 0  | 1   | 1   | 1   | 1              | 1   | 1   | 0   |  |  |

| 0  | 0   | Х   | Х   | Previous State |     |     |     |  |  |

| 1  | Х   | Х   | Х   | 1              | 1   | 1   | 1   |  |  |

### **TRUTH TABLE**

|    | INPUTS |         | OUTPUTS        |

|----|--------|---------|----------------|

| CE | CLK    | MA0 - 4 | A8 - A12       |

| Х  | 1      | 1       | 1              |

| Х  | 1      | 0       | 0              |

| X  | 0      | X       | Previous State |

X = Don't Care

# Application Information

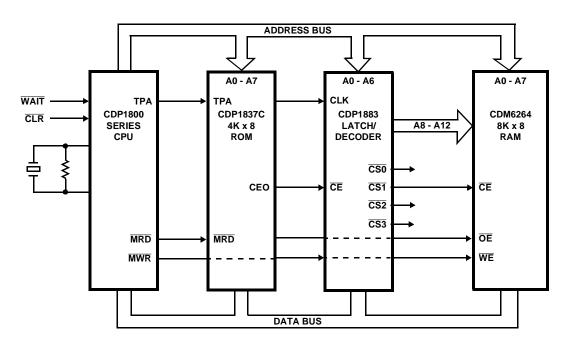

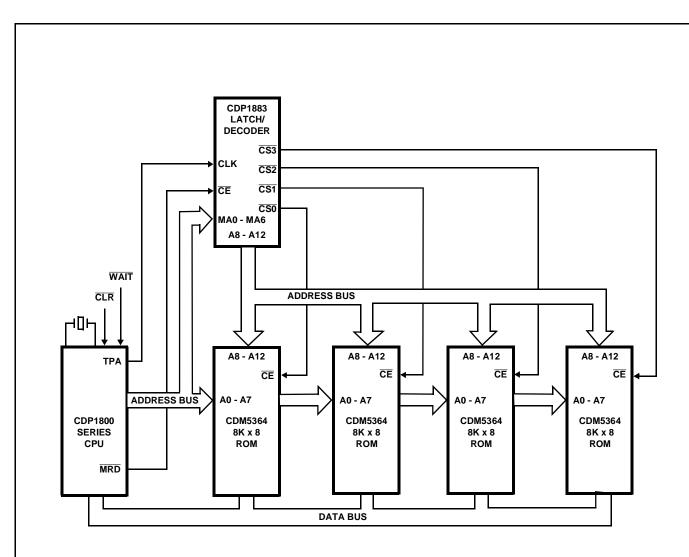

The CDP1883 and CDP1883C can be interfaced, without external components, with CDP1800-series microprocessor systems. These microprocessors feature a multiplexed address bus and provide an address latch signal (TPA) that is used as the clock input of the CDP1883. See Figure 2 and Figure 3.

This signal is used to latch 7 bits of the high-order address. The lower five high-order address inputs are latched and held to be used with the eight lower-order address inputs to access an 8K x 8-bit memory. The two upper high-order address inputs are latched and decoded for use as chip selects.

The latched address and decoding functions of the CDP1883 and CDP1883C allow them to operate with 32K-byte memory systems. In addition, smaller memory systems can be configured with 4K x 8-bit or smaller memories, or a mix of memory sizes up to 8K x 8-bit.

# CDP1883, CDP1883C

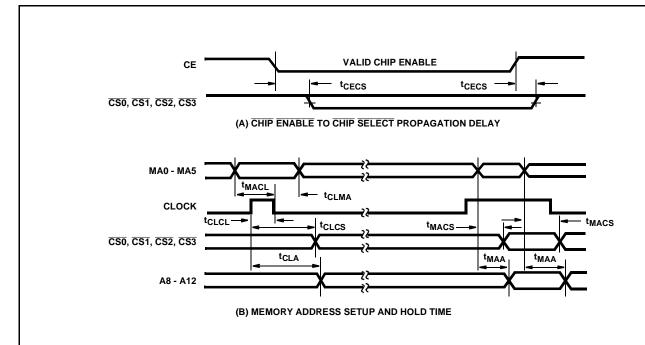

**Dynamic Electrical Specifications**  $T_A = -40^{o}C$  to  $+85^{o}C$ ,  $V_{DD} \pm 5\%$ ,  $t_R$ ,  $t_F = 20$ ns,  $V_{IH} = 0.7$   $V_{DD}$ ,  $V_{IL} = 0.3$   $V_{DD}$ ,  $C_L = 100$ pF. See Figure 1

|                               |                   |                        |     | CDP1883      | 3               |     | CDP1883C        |                 |       |  |  |

|-------------------------------|-------------------|------------------------|-----|--------------|-----------------|-----|-----------------|-----------------|-------|--|--|

| PARAMETER                     |                   | V <sub>DD</sub><br>(V) | MIN | (NOTE 1) TYP | (NOTE 2)<br>MAX | MIN | (NOTE 1)<br>TYP | (NOTE 2)<br>MAX | UNITS |  |  |

| Minimum Setup Time,           | <sup>t</sup> MACL | 5                      | -   | 10           | 35              | -   | 10              | 35              | ns    |  |  |

| Memory Address to CLOCK       |                   | 10                     | -   | 8            | 25              | -   | -               | -               | ns    |  |  |

| Minimum Hold Time,            | <sup>t</sup> CLMA | 5                      | -   | 8            | 25              | -   | 8               | 25              | ns    |  |  |

| Memory Address After CLOCK    |                   | 10                     | -   | 8            | 25              | -   | -               | -               | ns    |  |  |

| Minimum CLOCK Pulse Width     | <sup>t</sup> CLCL | 5                      | -   | 50           | 75              | -   | 50              | 75              | ns    |  |  |

|                               |                   | 10                     | -   | 25           | 40              | -   | -               | -               | ns    |  |  |

| PROPAGATION DELAY TIMES       |                   |                        |     |              |                 |     |                 |                 |       |  |  |

| Chip Enable to Chip Select    | tCECS             | 5                      | -   | 75           | 150             | -   | 75              | 150             | ns    |  |  |

|                               |                   | 10                     | -   | 45           | 100             | -   | -               | -               | ns    |  |  |

| CLOCK to Chip Select          | tCLCS             | 5                      | -   | 100          | 175             | -   | 100             | 175             | ns    |  |  |

|                               |                   | 10                     | -   | 65           | 125             | -   | -               | -               | ns    |  |  |

| CLOCK to Address              | <sup>t</sup> CLA  | 5                      | -   | 100          | 175             | -   | 100             | 175             | ns    |  |  |

|                               |                   | 10                     | -   | 65           | 125             | -   | -               | -               | ns    |  |  |

| Memory Address to Chip Select | †MACS             | 5                      | -   | 100          | 175             | -   | 100             | 175             | ns    |  |  |

|                               |                   | 10                     | -   | 75           | 125             | -   | -               | -               | ns    |  |  |

| Memory Address to Address     | t <sub>MAA</sub>  | 5                      | -   | 80           | 125             | -   | 80              | 125             | ns    |  |  |

|                               |                   | 10                     | -   | 40           | 60              | -   | -               | -               | ns    |  |  |

### NOTES:

- 1. Typical values are for  $T_A = 25^{\circ}C$ .

- 2. Maximum limits of minimum characteristics are the values above which all devices function.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time withou notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FIGURE 1. CDP1883 TIMING WAVEFORMS

FIGURE 2. MINIMUM CDP1800-SYSTEM USING THE CDP1883 INTERFACE WITH AN 8K X 8-BIT MEMORY

FIGURE 3. 32K-BYTE ROM SYSTEM USING THE CDP1883