#### **General Description**

The MAX5079 ORing MOSFET controller replaces ORing diodes in high-reliability redundant, parallel-connected power supplies. Despite their low forward-voltage drop, ORing Schottky diodes cause excessive power dissipation at high currents. The MAX5079 allows for the use of low-on-resistance n-channel power MOSFETs to replace the Schottky diodes. This results in low power dissipation, smaller size, and elimination of heatsinks in high-power applications.

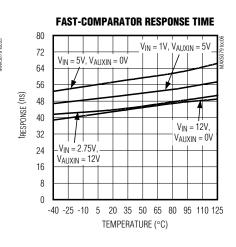

The MAX5079 operates from 2.75V to 13.2V and includes a charge pump to drive the high-side n-channel MOSFET. Operation down to 1V is possible if an auxiliary voltage of at least 2.75V is available. When the controller detects a positive voltage difference between IN and BUS, the n-channel MOSFET is turned on. The MOSFET is turned off as soon as the MAX5079 sees a negative potential at IN with respect to the BUS voltage, and is automatically turned back on when the positive potential is restored. Under fault conditions, the ORing MOSFET's gate is pulled down with a 1A current, providing an ultra-fast 200ns turn-off. The reverse voltage turn-off threshold is externally adjustable to avoid unintentional turn-off of the ORing MOSFET due to glitches at IN or BUS caused by hot plugging the power supply.

Additional features include an OVP flag to facilitate shutdown of a failed power supply due to an overvoltage condition, and a PGOOD signal that indicates if VIN is either below the undervoltage lockout or V<sub>BUS</sub> is in an overvoltage condition. The MAX5079 operates over the -40°C to +85°C temperature range and is available in a space-saving 14-pin TSSOP package.

#### **Applications**

Paralleled DC-DC Converter Modules

N+1 Redundant Power Systems

Servers

Base-Station Line Cards

**RAID**

Networking Line Cards

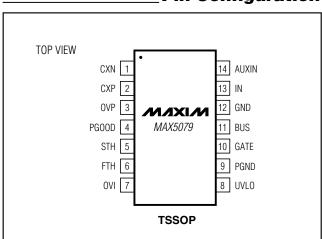

Pin Configuration appears at end of data sheet.

#### **Features**

- ♦ 2.75V to 13.2V Input ORing Voltage

- ♦ 1V to 13.2V Input ORing Voltage with 2.75V Aux **Voltage Present**

- ♦ 2A MOSFET Gate Pulldown Current During Fault Condition

- ♦ Ultra-Fast 200ns, MOSFET Turn-Off During Fault Condition

- Supply Undervoltage and Bus Overvoltage Detection

- **♦** Power-Good (PGOOD) and Overvoltage (OVP) **Outputs for Fault Detection**

- ♦ Space-Saving 14-Pin TSSOP Package

- ♦ -40°C to +85°C Operating Temperature Range

#### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX5079EUD | -40°C to +85°C | 14 TSSOP    |

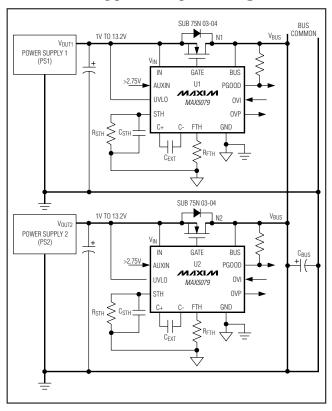

#### Typical Operating Circuit

#### **ABSOLUTE MAXIMUM RATINGS**

| GATE to GND                                        | 0.3V to (V <sub>IN</sub> + 8.5V) |

|----------------------------------------------------|----------------------------------|

| All Other Pins to GND                              |                                  |

| Continuous Current Into Any Pin                    | ±50mA                            |

| Continuous Power Dissipation ( $T_A = +70^{\circ}$ |                                  |

| 14-Pin TSSOP (derate 9.1mW/°C above                | e +70°C)727.3mW                  |

| 40°C to +85°C |

|---------------|

| +150°C        |

| 5°C to +150°C |

| +300°C        |

|               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

( $(V_{IN} = 2.75V \text{ to } 13.2V \text{ and } V_{AUXIN} = 0V)$  or ( $V_{IN} = 1V \text{ and } V_{AUXIN} = 2.75V \text{ to } 13.2V$ ),  $R_{STH} = \text{open}$ ,  $R_{FTH} = 0$ ,  $V_{UVLO} = 1V$ ,  $V_{OVI} = 0V$ ,  $V_{IN} = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_{IN} = 12V$  and  $V_$

| PARAMETER                                                                                                    | SYMBOL                            | CONDITIONS                                                                                                                       | MIN   | TYP  | MAX   | UNITS |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| POWER SUPPLIES                                                                                               |                                   |                                                                                                                                  | •     |      |       |       |

| IN Input Voltage Range                                                                                       | VIN                               |                                                                                                                                  | 2.75  |      | 13.20 | V     |

|                                                                                                              |                                   | V <sub>AUXIN</sub> ≥ 2.75V                                                                                                       | 1.0   |      | 13.2  | V     |

| AUXIN Input Voltage Range                                                                                    | Vauxin                            |                                                                                                                                  | 0     |      | 13.2  | V     |

| (V <sub>AUXIN</sub> - V <sub>IN</sub> ) High Threshold<br>(When GATE Connects Directly<br>to AUXIN) (Note 2) | V <sub>AUXIN</sub> _<br>THRESHOLD | V <sub>AUXIN</sub> rising, I <sub>GATE</sub> = 10μA                                                                              | 4.3   | 4.9  | 5.4   | ٧     |

| (V <sub>AUXIN</sub> - V <sub>IN</sub> ) Hysteresis (When GATE Connects Directly To AUXIN)                    | Vauxin_<br>Hysteresis             |                                                                                                                                  |       | 40   |       | mV    |

| IN Supply Current                                                                                            | IIN                               | V <sub>UVLO</sub> = 1V, V <sub>IN</sub> > V <sub>BUS</sub>                                                                       |       |      | 4     | mA    |

| AUXIN Leakage Current                                                                                        | ILEAK_AUX                         | V <sub>AUXIN</sub> = 0V                                                                                                          |       |      | 20    | μΑ    |

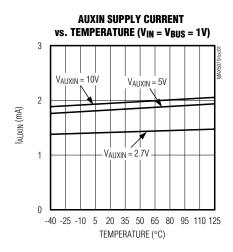

| AUXIN Supply Current                                                                                         | lauxin                            | V <sub>UVLO</sub> = 1V, V <sub>AUXIN</sub> = 13.2V, V <sub>AUXIN</sub> ≥ V <sub>IN</sub> , V <sub>AUXIN</sub> ≥ V <sub>BUS</sub> |       |      | 4     | mA    |

| BUS Leakage Current                                                                                          | ILEAK_BUS                         | V <sub>IN</sub> = 13.2V, V <sub>BUS</sub> = 0V                                                                                   |       |      | 1     | mA    |

| BUS Supply Current                                                                                           | I <sub>BUS</sub>                  | V <sub>BUS</sub> = 13.2V, V <sub>BUS</sub> > V <sub>IN</sub> , V <sub>BUS</sub> > V <sub>AUXIN</sub>                             |       |      | 3     | mA    |

| IN TO AUXIN SWITCHOVER                                                                                       |                                   |                                                                                                                                  |       |      |       |       |

| Switchover High Threshold                                                                                    | Vauxin_high                       | (VIN - VAUXIN), VAUXIN falling                                                                                                   | -60   | +25  | +200  | mV    |

| Switchover Low Threshold                                                                                     | V <sub>AUXIN</sub> LOW            | (VIN - VAUXIN), VAUXIN rising                                                                                                    | -200  | -25  | +50   | mV    |

| IN UNDERVOLTAGE LOCKOUT                                                                                      | _                                 |                                                                                                                                  |       |      |       |       |

| Internal UVLO High Threshold                                                                                 | VINTUVLO_HIGH                     | $V_{IN}$ rising, $V_{AUXIN} = 0V$ or $V_{AUXIN}$ rising, $V_{IN} = 0V$                                                           | 2.0   | 2.25 | 2.5   | V     |

| Internal UVLO Hysteresis                                                                                     | VINTUVLO_HYST                     | $V_{IN}$ falling, $V_{AUXIN} = 0V$ or $V_{AUXIN}$ falling, $V_{IN} = 0V$                                                         |       | 30   |       | mV    |

| External UVLO Threshold                                                                                      | V <sub>UVLO</sub>                 | V <sub>UVLO</sub> falling                                                                                                        | 0.568 | 0.6  | 0.632 | V     |

| External UVLO Hysteresis                                                                                     | Vuvlo_HYST                        |                                                                                                                                  |       | 60   |       | mV    |

| External UVLO Input Bias                                                                                     | luvlo                             |                                                                                                                                  |       |      | 500   | nA    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$((V_{IN}=2.75V\ to\ 13.2V\ and\ V_{AUXIN}=0V)\ or\ (V_{IN}=1V\ and\ V_{AUXIN}=2.75V\ to\ 13.2V),\ R_{STH}=open,\ R_{FTH}=0,\ V_{UVLO}=1V,\ V_{OVI}=0V,\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless otherwise\ noted.$  Typical values are at  $V_{IN}=12V\ and\ T_A=+25^{\circ}C.$  See the *Typical Operating Circuit.*) (Note 1)

| PARAMETER                                                                                                                           | SYMBOL                | CONDITIONS                                                                            | MIN  | TYP  | MAX   | UNITS |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------|------|------|-------|-------|

| ORing MOSFET CONTROL                                                                                                                | 0202                  |                                                                                       |      |      | ,     | 1 39  |

| ORing MOSFET Turn-On Time                                                                                                           | t <sub>ON</sub>       | CGATE = 10nF, C <sub>EXT</sub> = 100nF,<br>MOSFET gate threshold = 2V                 |      | 10   | 25    | μs    |

| ORing MOSFET Forward Voltage<br>Threshold (Fast Comparator)                                                                         | V <sub>DTH</sub>      | (V <sub>IN</sub> - V <sub>BUS</sub> ) rising                                          | 5    | 12.5 | 20    | mV    |

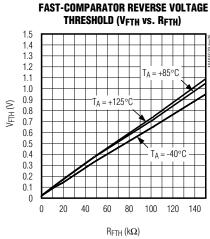

| ORing MOSFET Reverse Voltage                                                                                                        | V <sub>FTH</sub>      | R <sub>FTH</sub> = 0                                                                  | -12  | -24  | -31   |       |

| Turn-Off Threshold (Fast                                                                                                            |                       | $R_{\text{FTH}} = 12k\Omega$                                                          | -63  | -104 | -150  | mV    |

| Comparator (V <sub>IN</sub> - V <sub>BUS</sub> ))                                                                                   |                       | $R_{FTH} = 27k\Omega$ , $V_{IN} \ge 3.5V$                                             | -126 | -204 | -300  |       |

| ORing MOSFET Reverse Voltage<br>Blanking Time (Fast Comparator)                                                                     | t <sub>FBL</sub>      | $V_{BUS} = 2.8V, R_{FTH} = 0, V_{BUS} - V_{IN} = 0.3V$                                |      | 50   |       | ns    |

| Slow-Comparator Output Voltage<br>Threshold on STH                                                                                  | Vo_sth                |                                                                                       | 0.95 | 1    | 1.05  | V     |

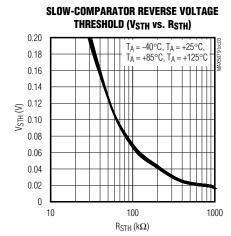

| ORing MOSFET Reverse Voltage                                                                                                        |                       | R <sub>STH</sub> open                                                                 | -0.1 | -12  | -24.0 |       |

| Turn-Off Threshold (Slow                                                                                                            | Vsth                  | $R_{STH} = 500k\Omega$                                                                |      | -25  |       | mV    |

| Comparator (V <sub>IN</sub> - V <sub>BUS</sub> ))                                                                                   |                       | $R_{STH} = 64k\Omega$                                                                 |      | -100 |       |       |

| (V <sub>IN</sub> - V <sub>BUS</sub> ) to I <sub>STH</sub><br>Transconductance (Slow<br>Comparator)                                  | G <sub>M_STH</sub>    | V <sub>STH</sub> = 0V                                                                 |      | 0.17 |       | mS    |

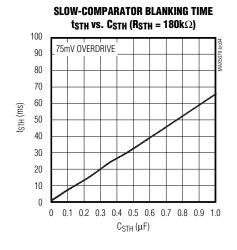

| ORing MOSFET Reverse Voltage                                                                                                        | tsbl                  | STH floating                                                                          | 0.5  | 0.9  | 1.5   |       |

| Blanking Time (Slow                                                                                                                 |                       | C <sub>STH</sub> = 0.047µF                                                            |      | 5    |       | ms    |

| Comparator)                                                                                                                         |                       | C <sub>STH</sub> = 0.22µF                                                             |      | 14   |       |       |

| ORing MOSFET DRIVER                                                                                                                 |                       |                                                                                       |      |      |       |       |

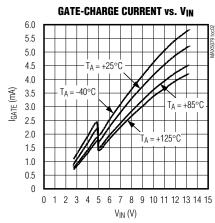

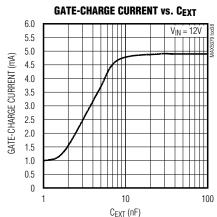

| Gate-Charge Current                                                                                                                 | IGATE                 | C <sub>EXT</sub> = 100nF                                                              | 0.7  | 2    |       | mA    |

|                                                                                                                                     | IGATE.DIS_MIN         | VGATE ≥ VIN, VIN = 5V, VBUS = 5V                                                      | 0.9  | 2    | 5.0   |       |

| Gate Discharge Current (Note 3)                                                                                                     |                       | $V_{GATE} \ge V_{IN}$ , $V_{IN} = 2.75V$ , $V_{BUS} = 3.5V$                           |      | 1.3  |       | A     |

|                                                                                                                                     |                       | V <sub>GATE</sub> ≥ V <sub>IN</sub> , V <sub>IN</sub> = 12V, V <sub>BUS</sub> = 13.2V |      | 3.2  |       |       |

| Gate Fall Time                                                                                                                      | tFGATE                | V <sub>BUS</sub> = 3.5V, C <sub>GATE</sub> = 0.1μF                                    |      | 600  |       | ns    |

|                                                                                                                                     |                       | V <sub>BUS</sub> = 3.5V, C <sub>GATE</sub> = 0.01μF                                   |      | 200  |       |       |

| Gate Discharge Current Delay<br>Time (Time from V <sub>IN</sub> Falling from<br>3.7V to 3V to V <sub>GATE</sub> = V <sub>IN</sub> ) | tdis_gate             | V <sub>BUS</sub> = 3.5V, V <sub>FTH</sub> = 0V,<br>C <sub>GATE</sub> = 0.1nF          |      | 70   | 200   | ns    |

| Gate to IN Resistance                                                                                                               | RGATE_IN              | (VGATE - VIN) = 100mV                                                                 |      |      | 900   | Ω     |

| Gate to IN Clamp Voltage                                                                                                            | VGATE_IN_CLAMP        | IGATE = 10mA, V <sub>IN</sub> ≥ V <sub>BUS</sub>                                      | 8.5  |      | 11    | V     |

| Gate-Drive Voltage (Measured                                                                                                        |                       | 2.7V < V <sub>IN</sub> < 13.2V                                                        | 3.8  |      |       |       |

|                                                                                                                                     |                       | V <sub>IN</sub> = 13.2V                                                               | 6.5  | 7    | 7.6   | V     |

| with Respect to V <sub>IN</sub> )                                                                                                   |                       | V <sub>IN</sub> = 2.75V                                                               | 4.5  | 5    | 5.5   |       |

| V <sub>IN</sub> Switchover Threshold to<br>Higher GATE Voltage (Note 4)                                                             | V <sub>IN_SOTH+</sub> |                                                                                       | 7.4  | 8    | 8.5   | V     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$((V_{IN} = 2.75V \text{ to } 13.2V \text{ and } V_{AUXIN} = 0V) \text{ or } (V_{IN} = 1V \text{ and } V_{AUXIN} = 2.75V \text{ to } 13.2V), R_{STH} = \text{open}, R_{FTH} = 0, V_{UVLO} = 1V, V_{OVI} = 0V, T_{A} = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_{IN} = 12V$  and  $T_{A} = +25^{\circ}\text{C}$ . See the *Typical Operating Circuit*.) (Note 1)

| PARAMETER                                      | SYMBOL               | CONDITIONS                                              | MIN   | TYP  | MAX   | UNITS |  |

|------------------------------------------------|----------------------|---------------------------------------------------------|-------|------|-------|-------|--|

| V <sub>IN</sub> Switchover Hysteresis (Note 4) | VIN_SOHYS            |                                                         |       | 40   |       | mV    |  |

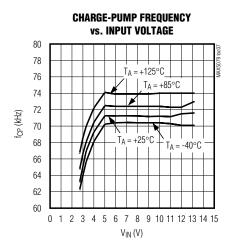

| Charge-Pump Frequency                          | f <sub>CP</sub>      | External                                                |       | 70   |       | kHz   |  |

|                                                |                      | Internal, V <sub>IN</sub> < 5V, V <sub>AUXIN</sub> < 5V |       | 1100 |       |       |  |

| PROTECTION                                     | PROTECTION           |                                                         |       |      |       |       |  |

| OVI Input Bias Current                         | I <sub>OVI</sub>     |                                                         |       |      | 500   | nA    |  |

| OVI Threshold                                  | V <sub>O</sub> VI_TH | OVI rising                                              | 0.568 | 0.6  | 0.632 | V     |  |

| OVP Output Low Voltage                         | Vovp_low             | V <sub>OVI</sub> = 1V, I <sub>SINK</sub> = 10mA         |       | 0.2  | 0.4   | V     |  |

| OVP Leakage Current                            | IOVP_LEAK            | $V_{IN} = 2.75V, V_{OVP} = 13.2V$                       |       |      | 1     | μΑ    |  |

| PGOOD Leakage Current                          | lpg_leak             | V <sub>PGOOD</sub> = 13.2V                              |       |      | 1     | μA    |  |

| PGOOD Output Low Voltage                       | V <sub>PG_LOW</sub>  | ISINK = 2mA                                             |       | 0.2  | 0.4   | V     |  |

- Note 1: All devices are production tested at +25°C. Limits over temperature are guaranteed by design.

- Note 2: Threshold is reached when charge pump turns off.

- Note 3: Gate discharge current is guaranteed through the testing of gate fall time.

- Note 4: V<sub>IN</sub> switchover threshold is V<sub>IN</sub> at which the gate-drive voltage (V<sub>GATE</sub> V<sub>IN</sub>) goes from 5V to 7V, V<sub>IN</sub> rising and (V<sub>IN</sub> ≥ V<sub>BUS</sub>).

# Typical Operating Characteristics

(T<sub>A</sub> = +25°C, unless otherwise noted. See the *Typical Operating Circuit*.)

#### Typical Operating Characteristics (continued)

(T<sub>A</sub> = +25°C, unless otherwise noted. See the *Typical Operating Circuit*.)

#### Typical Operating Characteristics (continued)

(T<sub>A</sub> = +25°C, unless otherwise noted. See the *Typical Operating Circuit*.)

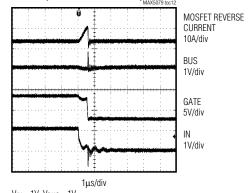

$V_{IN} = 2.75V$ ,  $V_{BUS} = 2.75V$ ,  $V_{AUXIN} = 0V$ ,  $C_{STH} = 0\mu F$ ,  $R_{STH} = 0PEN$ ,  $R_{FTH} = 0$ , UVLO = IN

$$\begin{split} &V_{IN}=12V,\,V_{BUS}=12V,\\ &V_{AUXIN}=0V,\,C_{STH}=0\mu F,\\ &R_{STH}=0PEN,\,R_{FTH}=0,\\ &UVL0=IN \end{split}$$

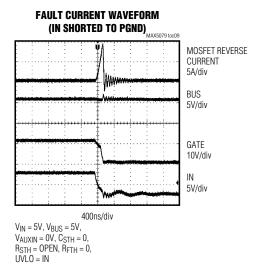

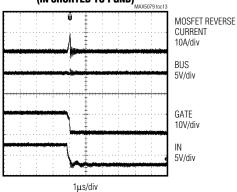

#### FAULT CURRENT WAVEFORM (IN SHORTED TO PGND)

$\begin{array}{l} V_{IN}=1V,\ V_{BUS}=1V,\\ V_{AUXIN}=5V,\ C_{STH}=0\mu F,\\ R_{STH}=0PEN,\ R_{FTH}=0,\\ UVL0=IN \end{array}$

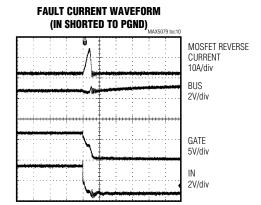

#### FAULT CURRENT WAVEFORM (IN SHORTED TO PGND)

$V_{IN} = 5V, V_{BUS} = 5V, \\ V_{AUXIN} = 5V, C_{STH} = 0\mu F, \\ R_{STH} = 0PEN, R_{FTH} = 0, \\ UVL0 = IN$

### Typical Operating Characteristics (continued)

(T<sub>A</sub> = +25°C, unless otherwise noted. See the *Typical Operating Circuit*.)

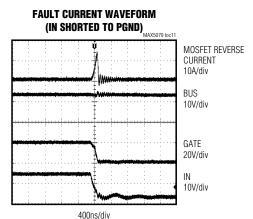

# FAULT CURRENT WAVEFORM (IN SHORTED TO PGND) MOSFET REVERSE CURRENT 10A/div BUS 10V/div IN 10V/div

V<sub>IN</sub> = 12V, V<sub>BUS</sub> = 12V, V<sub>AUXIN</sub> = 5V, C<sub>STH</sub> = 0, R<sub>STH</sub> = 0PEN, R<sub>FTH</sub> = 0, UVL0 = IN

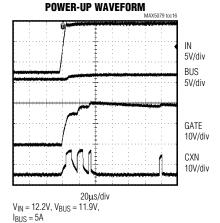

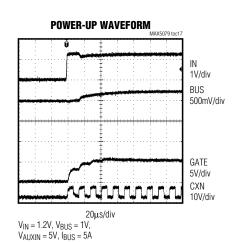

V<sub>IN</sub> = 5.2V, V<sub>BUS</sub> = 4.9V, I<sub>BUS</sub> = 5A

# **Pin Description**

| PIN | NAME                                                                                                                                                                                                             | FUNCTION                                                                                                                                                                                                                                                                                                    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CXN                                                                                                                                                                                                              | Negative Terminal of External Flying Charge-Pump Capacitor                                                                                                                                                                                                                                                  |

| 2   | CXP                                                                                                                                                                                                              | Positive Terminal of External Flying Charge-Pump Capacitor                                                                                                                                                                                                                                                  |

| 3   | Open-Drain Active-Low Output. OVP sinks up to 10mA when V <sub>OVI</sub> ≥ 0.6V and V <sub>IN</sub> ≥ V <sub>BUS</sub> . OV used to drive an optodiode. Cycle power or pull UVLO low and then high to reset OVP. |                                                                                                                                                                                                                                                                                                             |

| 4   | PGOOD                                                                                                                                                                                                            | Open-Drain Active-Low Output. PGOOD pulls low when $V_{UVLO} \le 0.6V$ or $V_{OVI} \ge 0.6V$ .                                                                                                                                                                                                              |

| 5   | STH                                                                                                                                                                                                              | ORing MOSFET Slow-Comparator Reverse Voltage Threshold and Blanking Time Setting Input. Connect a resistor from STH to GND to set the threshold. Connect a capacitor from STH to GND to set the blanking time. Leave STH floating to set the internal threshold (-12mV) and internal blanking time (0.9ms). |

| 6   | FTH                                                                                                                                                                                                              | Fast-Comparator Reverse Threshold Setting. Connect a resistor from FTH to GND to set the fast-comparator reverse voltage threshold from -24mV to -400mV.                                                                                                                                                    |

| 7   | OVI                                                                                                                                                                                                              | Overvoltage Comparator Input. Connect OVI to BUS through a resistive divider.                                                                                                                                                                                                                               |

| 8   | UVLO                                                                                                                                                                                                             | Undervoltage Lockout Comparator Input. Connect UVLO to IN through a resistive divider. The MAX5079 remains off until V <sub>UVLO</sub> rises above 0.66V. When V <sub>UVLO</sub> rises above 0.664V, V <sub>GATE</sub> is raised to V <sub>IN</sub> .                                                       |

| 9   | PGND                                                                                                                                                                                                             | Power Ground. Ground discharge path of the 2A GATE pulldown. Connect to external power ground plane.                                                                                                                                                                                                        |

| 10  | GATE                                                                                                                                                                                                             | Gate-Driver Output for n-Channel ORing MOSFET                                                                                                                                                                                                                                                               |

| 11  | BUS                                                                                                                                                                                                              | Bus Voltage-Sense Input. Connect BUS to the drain of the ORing MOSFET to sense the polarity of the Bus Current. The MAX5079 receives its power from BUS when V <sub>IN</sub> and V <sub>AUXIN</sub> are not present.                                                                                        |

| 12  | GND                                                                                                                                                                                                              | Signal Ground. Connect to the low-level signal or analog ground.                                                                                                                                                                                                                                            |

| 13  | IN                                                                                                                                                                                                               | Source Connection for ORing MOSFET and Supply Input for the MAX5079. Connect IN directly to the power-supply voltage of 2.75V to 13.2V or 1V to 13.2V with V <sub>AUXIN</sub> ≥ 2.75V.                                                                                                                      |

| 14  | AUXIN                                                                                                                                                                                                            | Auxiliary Power-Supply Input. AUXIN supplies power to the IC when $1V \le V_{IN} \le 2.75V$ . Connect AUXIN to 2.75V or higher if $V_{IN}$ is less than 2.75V.                                                                                                                                              |

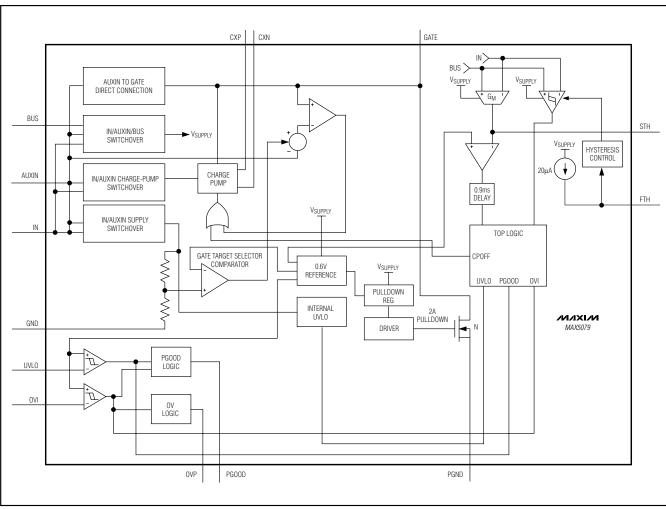

## Block Diagram

Figure 1. Block Diagram

#### Detailed Description

The MAX5079 ORing MOSFET controller drives an external n-channel MOSFET and replaces ORing diodes in high-reliability redundant power-management systems or multiple paralleled power supplies. The device has an internal charge pump to drive the high-side n-channel ORing MOSFET. Additional features include an adjustable undervoltage lockout threshold (UVLO), output overvoltage detector (OVI/OVP), input power-good detector (PGOOD), and two programmable reverse voltage detectors to detect both fast and slow rises in the reverse voltage across the ORing MOSFET. The input power-supply range is from 2.75V to 13.2V or down to 1V when an auxiliary supply of at least 2.75V is available.

#### **Operational Description**

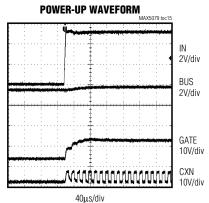

This section describes a detailed startup sequence and behavior of the MAX5079 under different conditions of V<sub>BUS</sub> and V<sub>IN</sub>. The MAX5079 powers up whenever V<sub>IN</sub> is equal to or greater than 2.75V and V<sub>UVLO</sub> exceeds the UVLO threshold of 0.66V. Operation with V<sub>IN</sub> down to 1V is possible as long as V<sub>UVLO</sub>  $\geq$  0.6V and V<sub>AUXIN</sub>  $\geq$  2.75V.

When  $V_{UVLO}$  crosses the UVLO threshold,  $V_{GATE}$  rises to  $V_{IN}$  and the charge pump turns on. The charge pump delivers 2mA to charge the gate capacitance of the external MOSFET connected to GATE. The constant gate-charge current prevents large inrush currents from the input supply. During turn-on, the MAX5079 will ignore the reverse voltage at IN with respect to BUS. This is necessary to avoid the unintentional turn-off of the ORing MOSFET as the momentary inrush current causes  $V_{IN}$  to dip.

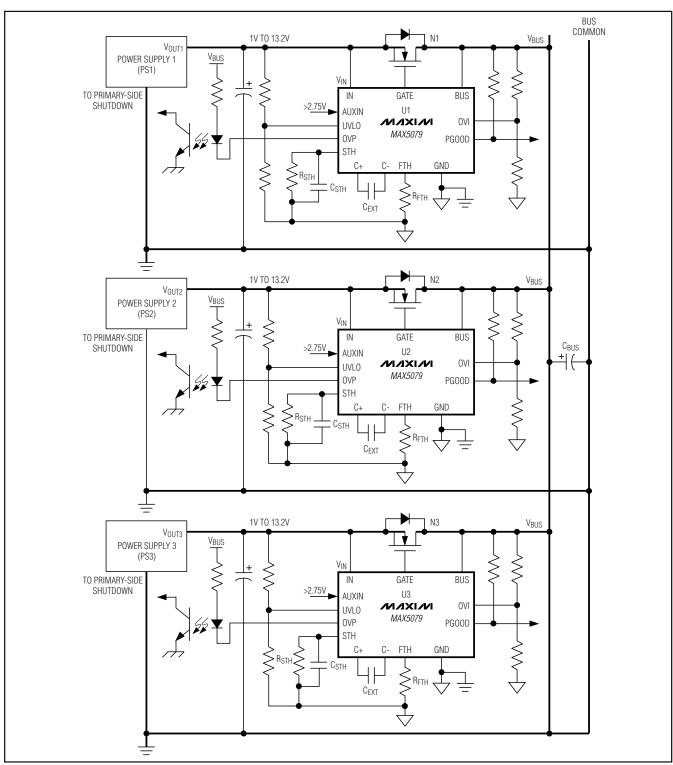

Figure 2 shows the MAX5079 in an ORing configuration with three parallel power supplies (PS1, PS2, and PS3) and three MAX5079s (U1, U2, and U3) provided by outputs VOUT1, VOUT2, and VOUT3. The following events must be carefully considered to ensure proper functionality of the MAX5079 ICs.

- VBUS is zero with a discharged capacitor (CBUS). All three power supplies are turned ON simultaneously. VOUT1 comes up before VOUT2 and VOUT3.

- a. When V<sub>OUT1</sub> turns on, the bus capacitors (C<sub>BUS</sub>) begin charging from V<sub>OUT1</sub> through N1's body diode. When V<sub>UVLO</sub> (U1) rises above the UVLO threshold, the MAX5079 (U1) charge pump turns on, and U1 monitors the positive potential from V<sub>OUT1</sub> to V<sub>BUS</sub>. When V<sub>OUT1</sub> ≥ V<sub>BUS</sub> the charge pump brings GATE (U1) to 5.5V above V<sub>IN</sub> (U1) (or 7.5V above V<sub>IN</sub> depending on the magnitude of

V<sub>IN</sub>), by sourcing 2mA into N1's gate capacitance. This results in a less than 10µs turn-on time for the FDB7045L used in the MAX5079 evaluation kit. The fast turn-on is needed to assure that N1 is ON before the rising Vout1 reaches its steady-state value. If the MOSFET is not turned on before VOUT1 reaches its steady state, VBUS may overshoot due to the shorting of the 0.7V (forward drop) of N1's body diode. A higher V<sub>IN</sub> (U1) can more quickly charge the charge-pump capacitor to 5V (or 7V), while a lower V<sub>IN</sub> (U1) will take longer. Typically the MOSFET turns on at VGS = 2.5V. Ensure that the soft-start time of the power supply is large enough (> 5ms) to avoid VOUT1 racing ahead and causing VBUS to overshoot. Care must be taken to avoid the overloading of VOUT1 by either limiting the source current (using the current-sharing circuit) or delay the loading of the BUS until all three power supplies are up and running.

- b. VOUT2 turns on and begins increasing the voltage at IN (U2). VUVLO (U2) crosses the UVLO threshold, the MAX5079 (U2) charge pump turns on and U2 monitors the VOUT2 to VBUS voltage. When this voltage difference becomes positive, GATE (U2) begins sourcing 2mA into N2's gate capacitance. During turn-on, the reverse voltage turn-off circuit is momentarily disabled. If VOUT2 is lower than VOUT1, the external load-sharing controller circuit of PS2 will try to increase VOUT2 to source current from VOUT2. Assume VOUT2's rise time is slow enough not to cause any overshoot before N2 turns on and starts sharing the current.

- c. V<sub>OUT3</sub> turns on and U3 follows the same sequence as U2. Eventually V<sub>OUT1</sub>, V<sub>OUT2</sub>, and V<sub>OUT3</sub> reach to equilibrium and sharing equal currents.

- PS1 and PS2 are on and sharing the load when PS3 is hot-inserted. PS3 will take the same course as discussed in 1b above.

- a. If V<sub>OUT3</sub> is higher than V<sub>BUS</sub>, the BUS voltage will increase to the new level determined by V<sub>OUT3</sub>. The external load-sharing controller circuit of PS1 and PS2 will increase V<sub>OUT1</sub> and V<sub>OUT2</sub> to force current sharing.

- b. If V<sub>OUT3</sub> is lower than V<sub>BUS</sub>, the load-sharing circuit of PS3 will increase V<sub>OUT3</sub> to force the sharing of current. This causes V<sub>OUT3</sub> to increases above V<sub>BUS</sub>. When this voltage difference becomes positive, GATE (U3) begins sourcing 2mA into N3's gate capacitance. Again, the reverse voltage turnoff circuit is disabled momentarily, as discussed before. The load-sharing circuit of PS3's controller will adjust V<sub>OUT3</sub> so as to share the load current.

- c. During the hot insertion, a voltage spike can occur at N1 and N2 and cause the (Vout1 to VBUS) or (VOUT2 to VBUS) voltage to go negative. If the reverse voltage is below the fast-comparator reverse voltage threshold (VFTH) but above the programmed slow-comparator reverse voltage threshold (VSTH), the spike is ignored for the programmed blanking time (tSTH). If the spike is longer than 50ns (the fast-comparator internal blanking time, tFBL) and larger than VFTH, then U1 and U2 will turn off N1 and N2 quickly. If the magnitude of the voltage spike is above V<sub>STH</sub> but less than VFTH, and longer than the slow-comparator blanking time (tsth), U1 and U2 will turn off their respective ORing MOSFETs (N1 and N2) by discharging their GATE pins to PGND. The external load-sharing circuit of PS1 and PS2 will force VOUT1, VOUT2 above VBUS and N1, N2 will turn back on through the 2mA current sourcing from the GATE pins of U1 and U2. To avoid this situation the user can set the slow-comparator threshold and blanking time depending on the magnitude and duration of the voltage spikes.

- d. PS3 fails to start. V<sub>UVLO</sub> (U3) threshold is not crossed and U3 keeps N3 off.

- e. PS3 goes into an overvoltage condition (no feedback). This causes VBUS to go into an overvoltage condition increasing the loading on PS3 (provided PS3 is able to supply all the required BUS current). The current-sharing circuit will force the outputs of PS1 and PS2 to increase and eventually saturate at their current-sharing voltage range. Eventually only PS3 will have a positive voltage at IN (U3) with respect to BUS. PS1 and PS2 will have a negative voltage at VOUT1 and VOUT2 with respect to BUS. All overvoltage inputs OVI (U1), OVI (U2), and OVI (U3) sense the overvoltage, but only OVP (U3) is asserted and latched low. GATE (U3) is pulled to PGND and remains low as long as  $V_{OVI} \ge 0.6V$ . When  $V_{OVI}$  drops below 0.6V, OVP remains low. However, U3 tries to turn on N3 unless Vout3 is actively kept below the undervoltage lockout. Use OVP (U3) to either drive the cathode of the optocoupler to shutdown PS3 from the primary side or use OVP (U3) to fire an SCR connected between Vout3 and PGND.

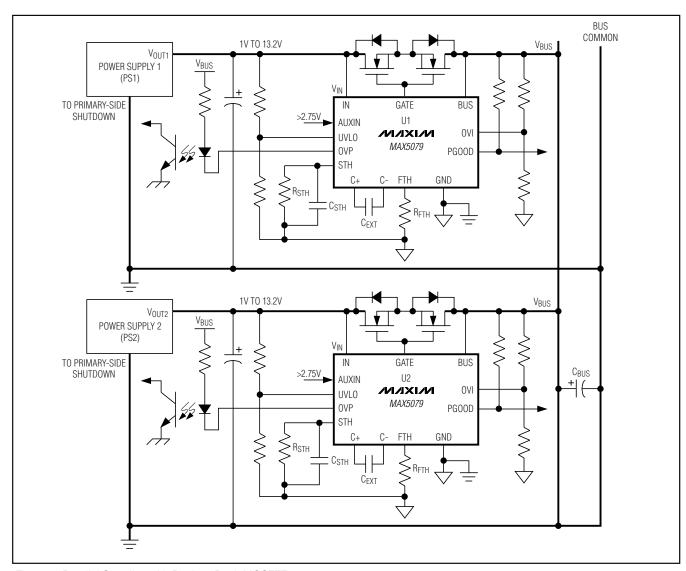

#### 3) PS1, PS2, PS3 are turned on with a shorted BUS.

Body diodes of N1, N2, and N3 conduct and short the outputs of PS1, PS2, and PS3 to PGND. The power supplies go into current limit (either in foldback or in hiccup mode). The MAX5079s remain in undervoltage

lockout and keep all ORing MOSFETs off. The average current sourced by PS1, PS2, or PS3 must be low enough so as not to exceed the MOSFETs power dissipation ( $P_D = V_F \times I_{SHORT}$ ).

- a. Use additional n-channel MOSFETs in series with N1, N2, and N3 in the reverse direction to isolate the power supplies from a shorted bus (Figure 3). When power is turned on with a shorted bus, VIN (U1, U2, U3) increases and VUVLO rises above the UVLO threshold. The MAX5079's GATE outputs start charging the back-to-back ORing MOSFET gates. The short-circuit condition at BUS collapses V<sub>IN</sub> (U1), V<sub>IN</sub> (U2), and V<sub>IN</sub> (U3) sending the MAX5079s into undervoltage lockout. This turns off the MAX5079s entirely, including discharging of the charge-pump storage capacitors. The IN voltages come back up again crossing UVLO (UVLO has 60mV hysteresis). A new cycle starts and the time required to charge the chargepump capacitor and the turn-on time of the device serves as a dead time. However, the dead time may not be enough to reduce the dissipation in the MOSFETs to an acceptable level. We advise in keeping the short-circuit current low and providing hiccup current-limit protection to the power supplies (PS1, PS2, and PS3).

- b. Any other overload condition that would sustain the IN voltage above UVLO, will keep the MOSFETs ON continuously. Ensure the MOSFETs' current rating is higher than the maximum short-circuit source current of the power supplies (PS1, PS2, and PS3) to avoid damage to the ORing MOSFETs.

# 4) PS1, PS2, and PS3 are present and PS1 is shorted to GND.

$V_{OUT1}$  drops below  $V_{BUS}$ . The negative potential from  $V_{IN}$  (U1) to  $V_{BUS}$  increases above the fast-comparator threshold and lasts longer than the 50ns blanking time. The MAX5079 (U1) takes its power from the voltage at BUS (U1). Connect BUS close to  $C_{BUS}$ , away from N1 so that U1 can receive power from BUS for a few microseconds until N1 isolates BUS from IN. N1 is discharged with 2A pulldown current, turning off N1 and isolating PS1 from the BUS. The load-sharing circuit of PS2 and PS3 will increase PS2 and PS3's load current until the total bus current requirement is satisfied.

For  $V_{IN}$  (U1) < 2.75V,  $V_{AUXIN}$  (U1) must come from an independent source or remain on for some time (a few microseconds) after  $V_{IN}$  (U1) has failed. This minimum on-time is needed to discharge the gate of the ORing MOSFET and isolate PS1 from the BUS.

#### 5) PS1, PS2, PS3 are present and PS1 goes open.

PS1's output capacitors discharge and V<sub>OUT1</sub> drops below V<sub>BUS</sub>. The MAX5079 (U1) senses a negative potential from V<sub>OUT1</sub> to V<sub>BUS</sub>. Depending upon how fast PS1's output capacitor discharges, N1 is turned off due to the crossing of the fast- or slow-comparator reverse voltage threshold. N1's gate is discharged with a 2A sink current into GATE (U1), turning off N1 and isolating PS1 from the BUS. The load-sharing circuit of PS2 and PS3 will increase PS2 and PS3's load current until the total BUS current requirement is satisfied.

# 6) PS1, PS2, PS3 are present and providing BUS current. PS1 loses its feedback signal and goes into an overvoltage condition.

VBUS increases and PS1 is loaded heavily. The current share circuit forces  $V_{OUT2}$  and  $V_{OUT3}$  higher and they will eventually saturate at their current-sharing voltage range. Now only PS1 has a positive voltage at IN (U1) with respect to BUS. All OVI inputs will sense the overvoltage, but only OVP (U1) will be asserted and latched low. GATE (U1) is pulled to PGND and remains low as long as  $V_{OVI} \ge 0.6V$ . When  $V_{OVI}$  drops below 0.6V, OVP remains low, however, U1 tries to turn on N1 unless  $V_{OUT1}$  is actively kept below the undervoltage lockout. Use OVP (U1) to either drive the cathode of an optocoupler to shutdown PS1 from the primary, or fire an SCR connected between IN (U1) and PGND.

#### Internal and External Undervoltage Lockout

The internal undervoltage lockout monitors  $V_{IN}$  and  $V_{AUXIN}$  and keeps the MAX5079 off until either voltage reaches 2.75V. Once powered and  $V_{IN}$  and/or  $V_{AUXIN}$  increase above 2.75V, the external UVLO is monitored. The external undervoltage lockout feature monitors the UVLO input and keeps the MAX5079 off (GATE shorted to PGND) until  $V_{UVLO}$  is greater than 0.66V. Connect a resistive divider from IN to UVLO to GND or from AUXIN to UVLO to GND to set the external undervoltage lockout threshold. We advise setting the external UVLO  $\geq$  2.75V when AUXIN is not present.

#### **Charge Pump**

The MAX5079 has an internal charge pump that pumps the gate-drive voltage ( $V_{GATE}$ ) high enough to fully enhance the n-channel ORing MOSFET. The charge

pump is divided into two stages, a voltage doubler running at 70kHz using an external charge-pump capacitor (CEXT), and a voltage tripler running at 1MHz using an internal capacitor.

Connect an external capacitor (CEXT) between C+ and C-. CEXT is charged from the higher of VIN or VAUXIN. When the rising V<sub>IN</sub> becomes greater then V<sub>BUS</sub> (V<sub>UVLO</sub> > 0.66V), CEXT is discharged through GATE into the external MOSFET's gate capacitance. The chargepump output is controlled by an internal regulator. The charge-pump output at GATE sources typically 2mA. This provides enough current drive to turn on a typical ORing MOSFET in less than 10µs. When (VGATE - VIN) reaches the target value (depending on VIN) the charge pump is switched off (see the Electrical Characteristics table). Choose CEXT equal to 10 times the ORing MOSFET gate capacitance. Too low of a capacitance will delay the turn-on of the ORing MOSFET, while too high of a capacitance can cause excessive ripple at VIN. Bypass IN to GND with a 1µF ceramic capacitor to avoid ripple at IN caused by the charge-pump switching. A clamp is placed internally between GATE and IN to prevent (VGATE - VIN) from exceeding 11V. When VIN is less than 5V, the charge pump (tripler) will increase VGATE to 3x's VIN to further reduce the RDSON of the ORing MOSFET. The internal charge-pump booster (voltage tripler) section is operational only when V<sub>IN</sub> and VAUXIN are low and is turned off when VIN exceeds 5V.

When an additional supply is connected to AUXIN and  $(V_{AUXIN} - V_{IN}) > 5V$ , both charge pumps are completely disabled. In this case, the charging of the ORing gate comes entirely from  $V_{AUXIN}$ . In this case, the charge-pump flying capacitor can be eliminated and C+, C-can be left floating.

#### **GATE Drive and Gate Pulldown**

The MAX5079's charge pump provides bias to charge the ORing MOSFET gate above IN (the MOSFET's source). GATE source current and the turn-on speed depends upon the value of CEXT (connected between C+ and C-). Typically GATE can source up to 2mA with CEXT = 0.1 $\mu$ F. This enables VGATE to rise to over 2V above V<sub>IN</sub> in less than 10 $\mu$ s for an ORing MOSFET gate capacitance of up to 10nF. With V<sub>IN</sub> < 5V, 12V MOSFETs can be used for better RDSON characteristics. The MAX5079 automatically selects the gate-drive voltage for

$V_{IN}$  = 5V or  $V_{IN}$  = 12V. For  $V_{IN}$  ≤ 8V, the gate drive is 5V above  $V_{IN}$  and for  $V_{IN}$  > 8V, the gate drive is 7V above  $V_{IN}$ . Lower gate drive means faster turn-off during faults, while higher gatedrive means lower  $R_{DSON}$ .

A fast and slow comparator monitor the voltage from IN to BUS. When this voltage crosses the negative fast- or slow-comparator threshold voltage for the blanking time duration, GATE is pulled low by an internal 2A current sink. Both comparators have an adjustable threshold voltage. GATE is pulled low if any of the following conditions are met.

- 1)  $V_{UVLO} < 0.6V$ .

- 2)  $V_{AUXIN} < 2.25V$  and  $V_{IN} < 2.25V$ .

- 3)  $V_{OVI} \ge 0.6V$ .

- 4) VIN ≤ (VBUS VFTH) or VIN ≤ (VBUS VSTH) and (VGATE VIN) ≥ 1.8V.

When the above conditions are not true and  $V_{IN} \le V_{BUS}$ , GATE is shorted to IN. To insure that the external MOSFET is quickly turned off, given the above conditions, the GATE pulldown circuitry is powered by either  $V_{IN}$ ,  $V_{AUXIN}$ , or  $V_{BUS}$  as long as any one is greater then 2.75V.

#### Fast Comparator (FTH)

The fast comparator has a 50ns blanking time to avoid unintentional turn-off of the ORing MOSFET during fast transients. Additionally, the fast-comparator reverse voltage threshold (VFTH) is programmable to suit the need of an individual application. Higher VFTH threshold allows for a larger glitch at BUS during a fault, but improves the noise immunity. Lower VFTH reduces glitches at BUS during a fault, however, with lower VFTH spikes at BUS or glitches at IN can be read as faults, unintentionally turning off the ORing MOSFET. Program VFTH by connecting a resistor from FTH to GND. Adjust VFTH to optimize the system performance using the following equation:

$$R_{FTH} = \frac{V_{FTH} - 24mV}{6.67\mu A}$$

VFTH can be chosen from 24mV to 400mV. Connect FTH to GND to choose the default 24mV threshold.

#### Slow Comparator (STH)

The MAX5079 includes a slow comparator to provide glitch immunity during the hot insertion or removal of paralleled power supplies. During the hot insertion, BUS can see voltage spikes. These spikes can be interpreted as a reverse voltage across the ORing MOSFET. The amplitude of the spikes is proportional to the load step seen by the parallel power supply while the duration of the spikes depends on the loop response of the load share and PWM controller.

The slow comparator has a programmable reverse voltage threshold (V<sub>STH</sub>) as well as a programmable blanking time (t<sub>STH</sub>). An internal transconductance amplifier converts the IN to BUS differential voltage to a current and applies it to a parallel combination of resistor and capacitor (R<sub>STH</sub> and C<sub>STH</sub>) from STH to GND. The reverse threshold voltage (V<sub>STH</sub>) for the slow comparator is adjusted through R<sub>STH</sub>. Use the following equation to calculate the R<sub>STH</sub> for a required V<sub>STH</sub>.

$$R_{STH} = \frac{1V}{\left(V_{STH} - 12mV\right) \times G_{M\_STH}}$$

where  $G_{M}$  STH = 0.17mS.

The internal 500k $\Omega$  resistance from the output of the transconductance to GND can change the actual V<sub>STH</sub> if R<sub>STH</sub> is above 50k $\Omega$ . In this case, see the *Typical Operating Circuit* to select R<sub>STH</sub>. Once R<sub>STH</sub> is chosen, the blanking time can be adjusted by C<sub>STH</sub>. The delay time is:

$$t_{DELAY} = R_{STH} \times C_{STH} \times \left[ -ln \left( 1 - \frac{V_{STH}}{V_{STH} + V_{DD}} \right) \right] + t_{SBL}$$

where  $t_{SBL} = 0.9 ms$  and is the default blanking time generated by an internal digital delay. Leaving STH floating results in a 12mV threshold voltage and a 0.9ms blanking time.  $V_{OD}$  (overdrive) is the difference between actual reverse voltage ( $V_{BUS} - V_{IN}$ ) and  $V_{STH}$  threshold.

#### Overvoltage Protection Latch (OVI/OVP)

OVI is the negative input to the overvoltage comparator. The positive input of this comparator is connected to the internal 0.6V reference and an open-drain output is provided at OVP. The overvoltage sensing for overvoltage protection is done at either IN or BUS. OVP

latches low and the internal GATE pulldown circuitry is activated and pulls GATE low only when both of the conditions are satisfied:

- 1)  $V_{OVI} \ge 0.6V$ .

- 2) V<sub>IN</sub> ≥ V<sub>BUS</sub>.

OVP can sink 10mA maximum. Cycle power or pull UVLO low and then high again to reset the OVP latch. GATE is pulled to PGND and remains low as long as  $V_{OVI} \geq 0.6V$ . When  $V_{OVI}$  drops below 0.6V, OVP remains low. However, the MAX5079 tries to turn on the ORing MOSFET unless  $V_{IN}$  is actively kept below the undervoltage lockout. Use OVP to drive the cathode of an optocoupler to shut down the respective power supply from the primary side (see the *Typical Application Circuit* of Figure 2) or fire an SCR connected from IN to PGND.

#### **Power-Good Comparator (PGOOD)**

PGOOD output pulls low when V<sub>UVLO</sub> falls below 0.6V or V<sub>OVI</sub> goes above 0.6V. PGOOD can sink a maximum of 2mA.

#### **Layout Guidelines**

- 1) Place a 1µF ceramic input bypass capacitor physically close to IN and PGND. Connect IN as close as possible to the source of the ORing MOSFET.

- 2) Sense the VBUS close to the bulk capacitor, away from the drain of the ORing MOSFET. When IN is shorted to ground during a fault, BUS is also pulled low through the ORing MOSFET. In the absence of VAUXIN, the MAX5079 loses both power inputs VIN and VBUS. This can cause a delayed pulldown of the gate. Sensing the BUS away from the ORing MOSFET drain, close to the BUS bulk capacitor provides power to the MAX5079 for a few microseconds, long enough to pull down the ORing MOSFET gate and isolate BUS from a shorted IN.

- 3) Place the charge-pump capacitor (C<sub>EXT</sub>) and the slow-comparator blanking time adjustment capacitor (C<sub>STH</sub>) as close as possible to the MAX5079.

- 4) Run a thick trace from the gate of the ORing MOSFET to GATE.

Figure 2. Typical Application Circuit

Figure 3. Parallel Supplies with Back-to-Back MOSFET

# **Pin Configuration**

\_Chip Information

TRANSISTOR COUNT: 2,911 PROCESS: BICMOS

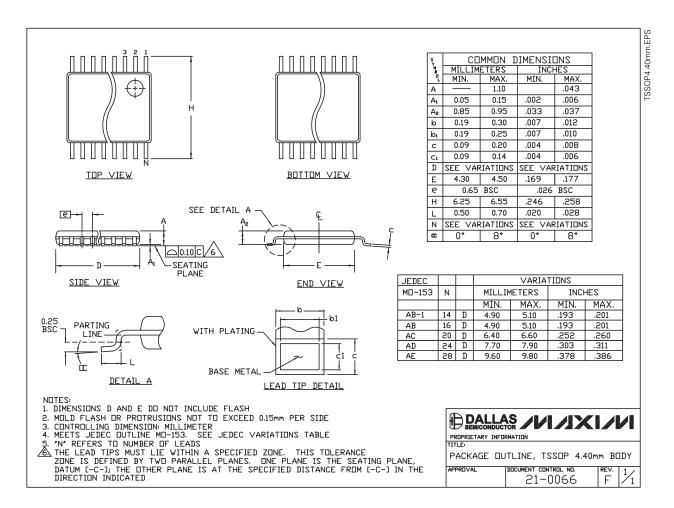

#### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.