## Data Sheet

## December 12, 2006

# FN7464.2

# Light-to-Digital Output Sensor with High Sensitivity, Gain Selection, Interrupt Function and I<sup>2</sup>C Interface

The ISL29003 is an integrated light sensors with a 16-bit integrating type ADC,  $l^2C$  user programmable Lux range select for optimized counts/Lux, and  $l^2C$  multi-function control and monitoring capabilities. The internal ADC provides 16-bit resolution while rejecting 50Hz and 60Hz flicker caused by artificial light sources.

In normal operation, power consumption is less than  $300\mu$ A. Furthermore, an available software power-down mode controlled via the I<sup>2</sup>C interface reduces power consumption to less than  $1\mu$ A.

The ISL29003 supports a hardware interrupt that remains asserted low until the host clears it through  $I^2C$  interface.

Designed to operate on supplies from 2.5V to 3.3V, the ISL29003 is specified for operation over the -40°C to +85°C ambient temperature range.

# **Ordering Information**

| PART NUMBER               | TAPE &<br>REEL             | PACKAGE                | PKG.<br>DWG. # |

|---------------------------|----------------------------|------------------------|----------------|

| ISL29003IROZ-T7<br>(Note) | 7"                         | 6 Ld ODFN<br>(Pb-free) | L6.2X2.1       |

| ISL29003IROZ-EVAL         | Evaluation Board (Pb-free) |                        |                |

NOTE: Intersil Pb-free ODFN products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

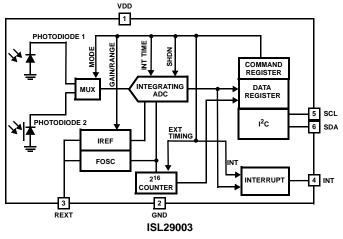

# Block Diagram

## Features

- Range select via I<sup>2</sup>C

- Range 1 = 0Lux to 1000Lux

- Range 2 = 0Lux to 4000Lux

- Range 3 = 0Lux to 16,000Lux

- Range 4 = 0Lux to 64,000Lux

- Human eye response (540nm peak sensitivity)

- Temperature compensated

- 16-bit resolution

- Adjustable resolution: up to 65 counts per Lux

- User-programmable upper and lower threshold interrupt

- · Simple output code, directly proportional to Lux

- IR + UV rejection

- 50Hz/60Hz rejection

- 2.5V to 3.3V supply

- 6 Ld ODFN (2.1mm x 2mm)

- Pb-free available (RoHS compliant)

## Applications

- Ambient light sensing

- Backlight control

- Temperature control systems

- Contrast control

- Camera light meters

- Lighting controls

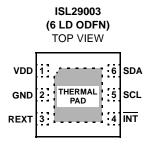

# Pinout

## **Absolute Maximum Ratings** (T<sub>A</sub> = +25°C)

| V <sub>DD</sub> Supply Voltage between V <sub>DD</sub> and GND | Maximum Die Temperature+125°C |

|----------------------------------------------------------------|-------------------------------|

| I <sup>2</sup> C Bus Pin Voltage (SCL, SDA)                    | Storage Temperature           |

| I <sup>2</sup> C Bus Pin Current (SCL, SDA)                    | Operating Temperature         |

| R <sub>ext</sub> Pin Voltage0.2V to 3.6V                       | ESD, Human Body Model2kV      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

#

| PARAMETER         | DESCRIPTION                                |          | CONDITION                                        | MIN   | TYP   | MAX   | UNIT   |

|-------------------|--------------------------------------------|----------|--------------------------------------------------|-------|-------|-------|--------|

| V <sub>DD</sub>   | Power Supply Range                         |          |                                                  | 2.25  |       | 3.63  | V      |

| I <sub>DD</sub>   | Supply Current                             |          |                                                  |       | 0.29  | 0.33  | mA     |

| I <sub>DD1</sub>  | Supply Current Disabled                    | Software | disabled                                         |       | 0.1   | 1     | μA     |

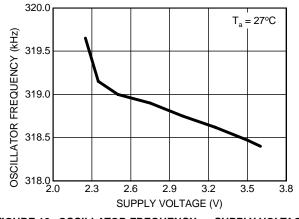

| F <sub>OSC1</sub> | Internal Oscillator Frequency              | Gain/Ra  | nge = 1 or 2                                     | 290   | 327   | 360   | kHz    |

| F <sub>OSC2</sub> | Internal Oscillator Frequency              | Gain/Ra  | nge = 3 or 4                                     | 580   | 655   | 720   | kHz    |

| FI <sup>2</sup> C | I <sup>2</sup> C Clock Rate                | Note 2   |                                                  | 1     |       | 400   | kHz    |

| DATA0             | Diode1 Dark ADC Code                       | E = 0Lux | k, Mode1, Gain/Range = 1                         |       |       | 5     | Counts |

| DATA1             | Full Scale ADC Code                        |          |                                                  |       |       | 65535 | Counts |

| DATA2             | Diode1 ADC Code Gain/Range = 1<br>accuracy | Mode1    | E = 300Lux, fluorescent light,<br>Gain/Range = 1 | 15760 | 20200 | 24440 | Counts |

| DATA3             | Diode2 ADC Code Gain/Range = 1<br>accuracy | Mode2    | (Note 1)                                         |       | 2020  |       | Counts |

| DATA4             | Diode1 ADC Code Gain/Range = 2<br>accuracy | Mode1    | E = 300Lux, fluorescent light,<br>Gain/Range = 2 |       | 5050  |       | Counts |

| DATA5             | Diode2 ADC Code Gain/Range = 2<br>accuracy | Mode2    | (Note 1)                                         |       | 505   |       | Counts |

| DATA6             | Diode1 ADC Code Gain/Range = 3<br>accuracy | Mode1    | E = 300Lux, fluorescent light,<br>Gain/Range = 3 |       | 1262  |       | Counts |

| DATA5             | Diode2 ADC Code Gain/Range = 3<br>accuracy | Mode2    | (Note 1)                                         |       | 126   |       | Counts |

| DATA6             | Diode1 ADC Code Gain/Range = 4<br>accuracy | Mode1    | E = 300Lux, fluorescent light,<br>Gain/Range = 4 |       | 316   |       | Counts |

| DATA6             | Diode2 ADC Code Gain/Range = 4<br>accuracy | Mode2    | (Note 1)                                         |       | 32    |       | Counts |

| V <sub>REF</sub>  | Voltage of R <sub>EXT</sub> Pin            |          |                                                  | 0.485 | 0.51  | 0.535 | V      |

| V <sub>TL</sub>   | SCL & SDA Threshold LO                     | (Note 3) |                                                  |       | 1.05  |       | V      |

| V <sub>TH</sub>   | SCL & SDA Threshold HI                     | (Note 3) |                                                  |       | 1.95  |       | V      |

| I <sub>SDA</sub>  | SDA Current Sinking Capability             | Note 4   |                                                  | 3     | 5     |       | mA     |

| IINT              | INT Current Sinking Capability             |          |                                                  | 3     | 5     |       | mA     |

NOTES:

1. Fluorescent light is substituted by a white LED during production.

2

2. Minimum  $I^2C$  Clock Rate is guaranteed by design.

3. The voltage threshold levels of the SDA and SCL pins are VDD dependent:  $V_{TL} = 0.35^*V_{DD}$ .  $V_{TH} = 0.65^*V_{DD}$ .

4. Sinking capability is guaranteed by design.

| Pin Descrip | otions   |                                                                                                               |                                                                      |  |  |

|-------------|----------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| PIN NUMBER  | PIN NAME | DESCRIPTION                                                                                                   |                                                                      |  |  |

| 1           | VDD      | Positive supply; connect this pin to                                                                          | Positive supply; connect this pin to a regulated 2.5V to 3.3V supply |  |  |

| 2           | GND      | Ground pin. The thermal pad is connected to the GND pin                                                       |                                                                      |  |  |

| 3           | REXT     | External resistor pin for ADC reference; connect this pin to ground through a (nominal) $100k\Omega$ resistor |                                                                      |  |  |

| 4           | INT      | Interrupt pin; LO for interrupt/alarmi                                                                        | ng. The INT pin is an open drain.                                    |  |  |

| 5           | SCL      | I <sup>2</sup> C serial clock                                                                                 | The I <sup>2</sup> C bus lines can pulled above VDD, 5.5V max.       |  |  |

| 6           | SDA      | I <sup>2</sup> C serial data                                                                                  |                                                                      |  |  |

# Pii

# Principles of Operation

## **Photodiodes**

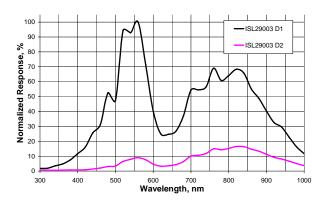

The ISL29003 contains two photodiodes. Diode1 is sensitive to both visible and infrared light, while Diode2 is mostly sensitive to infrared light. The spectral response of the two diodes are independent from one another. See Figure 7 Spectral Response vs Wavelength in the performance curves section. The photodiodes convert light to current. Then, the diodes' current outputs are converted to digital by a single built-in integrating type 16-bit Analog-to-Digital Converter (ADC). An I<sup>2</sup>C command mode determines which photodiode will be converted to a digital signal. Mode1 is Diode1 only. Mode2 is Diode2 only. Mode3 is a sequential Mode1 and Mode2 with an internal subtract function (Diode1 - Diode2). Analog-to-Digital Converter (ADC)

The converter is a charge-balancing integrating type 16-bit ADC. The chosen method for conversion is best for converting small current signals in the presence of an AC periodic noise. A 100ms integration time, for instance, highly rejects 50Hz and 60Hz power line noise simultaneously. See Integration Time and Noise Rejection section.

The built-in ADC offers user flexibility in integration time or conversion time. Two timing modes are available. Internal Timing Mode and External Timing Mode. In Internal Timing Mode, integration time is determined by an internal dual speed oscillator (fosc), and the n-bit (n = 4, 8, 12, 16) counter inside the ADC. In External Timing Mode, integration time is determined by the time between two consecutive I<sup>2</sup>C External Timing Mode commands. See External Timing Mode example. A good balancing act of integration time and resolution depending on the application is required for optimal results.

The ADC has four I<sup>2</sup>C programmable range select to dynamically accommodate various lighting conditions. For very dim conditions, the ADC can be configured at its lowest range. For very bright conditions, the ADC can be configured at its highest range.

# Interrupt Function

The active low interrupt pin is an open drain pull-down configuration. The interrupt pin serves as an alarm or monitoring function to determine whether the ambient light exceeds the upper threshold or goes below the lower threshold. The user can also configure the persistency of the interrupt pin. This eliminates any false triggers such as noise or sudden spikes in ambient light conditions. An unexpected camera flash for example can be ignored by setting the persistency to 8 integration cycles.

# I<sup>2</sup>C Interface

There are eight (8) 8-bit registers available inside the ISL29003. The command and control registers define the operation of the device. The command and control registers do not change until the registers are overwritten. There are two 8-bit registers that set the high and low interrupt thresholds. There are four 8-bit data Read Only registers. Two bytes for the sensor reading and another two bytes for the timer counts. The data registers contain the ADC's latest digital output, and the number of clock cycles in the previous integration period.

The ISL29003's I<sup>2</sup>C interface slave address is hardwired internally as 44(hex).

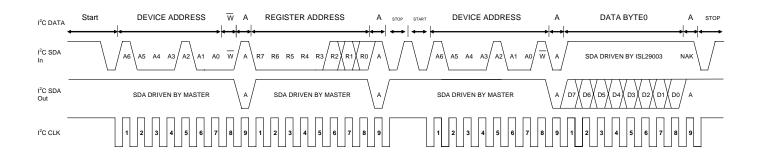

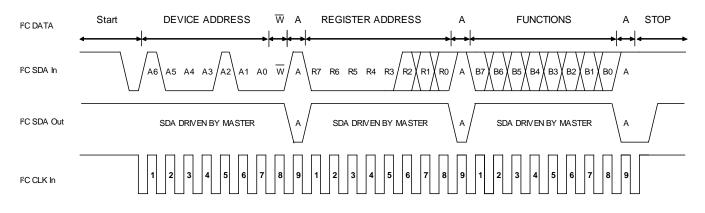

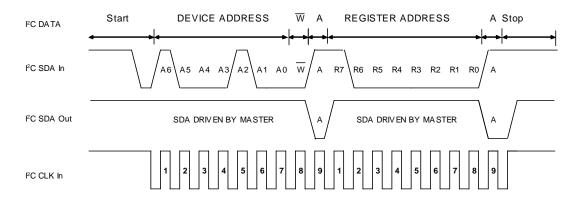

Figure 1 shows a sample one-byte read. Figure 2 shows a sample one-byte write. Figure 3 shows a sync\_iic timing diagram sample for externally controlled integration time. The I<sup>2</sup>C bus master always drives the SCL (clock) line, while either the master or the slave can drive the SDA (data) line. Figure 2 shows a sample write. Every I<sup>2</sup>C transaction begins with the master asserting a start condition (SDA falling while SCL remains high). The following byte is driven by the master, and includes the slave address and read/write bit. The receiving device is responsible for pulling SDA low during the acknowledgement period.

Every I<sup>2</sup>C transaction ends with the master asserting a stop condition (SDA rising while SCL remains high).

For more information about the I<sup>2</sup>C standard, please consult the Philips<sup>®</sup> I<sup>2</sup>C specification documents.

FIGURE 1. I<sup>2</sup>C READ TIMING DIAGRAM SAMPLE

FIGURE 2. I<sup>2</sup>C WRITE TIMING DIAGRAM SAMPLE

FIGURE 3. I<sup>2</sup>C sync\_iic TIMING DIAGRAM SAMPLE

# Register Set

There are eight registers that are available in the ISL29003. Table 1 summarizes the available registers and their functions.

| ADDR<br>(HEX) | REGISTER<br>NAME          | Bit(s) | FUNCTION NAME             | FUNCTIONS/<br>DESCRIPTION                                                                                                                                                                          |

|---------------|---------------------------|--------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00            | Command                   | 7      | enable                    | 0: disable adc-core<br>1: enable adc-core                                                                                                                                                          |

|               |                           | 6      | adcPD                     | 0: Normal operation<br>1: Power Down Mode                                                                                                                                                          |

|               |                           | 5      | Timing_Mode               | 0: Integration is internally timed<br>1: Integration is externally sync/controlled by I <sup>2</sup> C host                                                                                        |

|               |                           | 4      | reserved                  |                                                                                                                                                                                                    |

|               |                           | 3:2    | mode<1:0>                 | Selects ADC work mode<br>0: Diode1's current to unsigned 16-bit data<br>1: Diode2's current to unsigned 16-bit data<br>2: Difference between diodes (I1 - I2) to signed 15-bit data<br>3: reserved |

|               |                           | 1:0    | width<1:0>                | number of clock cycles; n-bit resolution<br>0: $2^{16}$ cycles<br>1: $2^{12}$ cycles<br>2: $2^8$ cycles<br>3: $2^4$ cycles                                                                         |

| 01            | Control                   | 7      | ext_mode                  | Always set to logic 0. Factory use only.                                                                                                                                                           |

|               |                           | 6      | test_mode                 | Always set to logic 0                                                                                                                                                                              |

|               |                           | 5      | int_flag                  | 0: Interrupt is cleared or not yet triggered<br>1: Interrupt is triggered                                                                                                                          |

|               |                           | 4      | reserved                  | Always set to logic 0. Factory use only.                                                                                                                                                           |

|               |                           | 3:2    | gain<1:0>                 | Selects the gain so range is<br>0: 0 - 1000Lux<br>1: 0 - 4000Lux<br>2: 0 - 16000Lux<br>3: 0 - 64000Lux                                                                                             |

|               |                           | 1:0    | int_persist<br><1:0>      | Interrupt is triggered after<br>0: 1 integration cycle<br>1: 4 integration cycles<br>2: 8 integration cycles<br>3: 16 integration cycles                                                           |

| 02            | Interrupt threshold<br>HI | 7:0    | Interrupt threshold<br>HI | High byte of HI interrupt threshold. Default is 0xFF                                                                                                                                               |

| 03            | Interrupt threshold<br>LO | 7:0    | Interrupt threshold<br>LO | High byte of the LO interrupt threshold. Default is 0x00                                                                                                                                           |

| 04            | LSB_sensor                | 7:0    | LSB_sensor                | Read-Only data register that contains the least significant byte of the latest sensor reading                                                                                                      |

| 05            | MSB_sensor                | 7:0    | MSB_sensor                | Read-Only data register that contains the most significant byte of the latest sensor reading                                                                                                       |

| 06            | LSB_timer                 | 7:0    | LSB_timer                 | Read-Only data register that contains the least significant byte of the timer counter value corresponding to the latest sensor reading.                                                            |

| 07            | MSB_timer                 | 7:0    | MSB_timer                 | Read-Only data register that contains the most significant byte of the timer counter value corresponding to the latest sensor reading.                                                             |

TABLE 1. REGISTER SET

#### TABLE 2. WRITE ONLY REGISTERS

| ADDRESS    | REGISTER<br>NAME | FUNCTIONS/<br>DESCRIPTION                                                                                                                |

|------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| b1xxx_xxxx | sync_iic         | Writing a logic 1 to this address bit<br>ends the current adc-integration and<br>starts another. Used only with<br>External Timing Mode. |

| bx1xx_xxxx | clar_int         | Writing a logic 1 to this address bit clears the interrupt.                                                                              |

## Command Register 00(hex)

The Read/Write command register has five functions:

(1) Enable; Bit 7.This function either resets the ADC or enables the ADC in normal operation. A logic 0 disables ADC to reset-mode. A logic 1 enables adc to normal operation.

#### TABLE 3. ENABLE

| BIT 7 | OPERATION                                |  |

|-------|------------------------------------------|--|

| 0     | disable ADC-core to reset-mode (default) |  |

| 1     | enable ADC-core to normal operation      |  |

(2) AdcPD; Bit 6. This function puts the device in a power down mode. A logic 0 puts the device in normal operation. A logic 1 powers down the device.

| TABLE | 4. | adcPD |  |

|-------|----|-------|--|

|       |    |       |  |

| BIT 6 | OPERATION                  |  |

|-------|----------------------------|--|

| 0     | Normal operation (default) |  |

| 1     | Power Down                 |  |

(3) Timing Mode; Bit 5. This function determines whether the integration time is done internally or externally. In Internal Timing Mode, integration time is determined by an internal dual speed oscillator (fosc), and the n-bit (n = 4, 8, 12, 16) counter inside the ADC. In External Timing Mode, integration time is determined by the time between two consecutive external-sync sync\_iic pules commands.

| BIT 5 | OPERATION                                                                                                        |

|-------|------------------------------------------------------------------------------------------------------------------|

| 0     | Internal Timing Mode. Integration time is internally timed determined by fosc, REXT, and number of clock cycles. |

| 1     | External Timing Mode. Integration time is externally timed by the I2C host.                                      |

(4) Photodiode Select Mode; Bits 3 and 2. This function controls the mux attached to the two photodiodes. At Mode1, the mux directs the current of Diode1 to the ADC. At Mode2, the mux directs the current of Diode2 only to the ADC.

Mode3 is a sequential Mode1 and Mode2 with an internal subtract function (Diode1 - Diode2).

| TABLE 6. | PHOTODIODE | SELECT | MODE; | BITS 2 | AND 3 |

|----------|------------|--------|-------|--------|-------|

|          |            |        |       |        |       |

| BITS 3:2 | MODE                                                                                                   |

|----------|--------------------------------------------------------------------------------------------------------|

| 0:0      | MODE1. ADC integrates or converts Diode1 only.<br>Current is converted to an n-bit unsigned data.*     |

| 0:1      | MODE2. ADC integrates or coverts Diode2 only.<br>Current is converted to an n-bit unsigned data.*      |

| 1:0      | MODE3. A sequential MODE1 then MODE2<br>operation. The difference current is an (n-1) signed<br>data.* |

| 1:1      | No operation.                                                                                          |

\* n = 4, 8, 12,16 depending on the number of clock cycles function.

(5) Width; Bits 1 and 0. This function determines the number of clock cycles per conversion. Changing the number of clock cycles does more than just change the resolution of the device. It also changes the integration time, which is the period the device's analog-to-digital (A/D) converter samples the photodiode current signal for a Lux measurement.

| IADLE 7. WIDTH |                        |  |

|----------------|------------------------|--|

| BITS 1:0       | NUMBER OF CLOCK CYCLES |  |

| 0:0            | 2^16 = 65,536          |  |

| 0:1            | 2^12 = 4,096           |  |

| 1:0            | 2^8 = 256              |  |

| 1:1            | 2^4 = 16               |  |

TABLE 7. WIDTH

# Control Register 01(hex)

The Read/Write control register has three functions:

(1) Interrupt flag; Bit 5. This is the status bit of the interrupt. The bit is set to logic high when the interrupt thresholds have been triggered, and logic low when not yet triggered. Writing a logic low clears/resets the status bit.

#### TABLE 8. INTERRUPT FLAG

| BIT 5 | OPERATION                                 |  |

|-------|-------------------------------------------|--|

| 0     | Interrupt is cleared or not triggered yet |  |

| 1     | Interrupt is triggered                    |  |

(2) Range/Gain; Bits 3 and 2. The Full Scale Range can be adjusted by an external resistor Rext and/or it can be adjusted via  $I^2C$  using the Gain/Range function. Gain/Range has four possible values, Range(k) where k is 1 through 4. Table 9 lists the possible values of Range(k) and the resulting FSR for some typical value R<sub>EXT</sub> resistors.

| BITS<br>3:2 | k | RANGE(k) | FSR LUX<br>RANGE@<br>R <sub>EXT</sub> = 100k | FSR LUX<br>RANGE@<br>R <sub>EXT</sub> = 50k | FSR LUX<br>RANGE@<br>R <sub>EXT</sub> = 500k |

|-------------|---|----------|----------------------------------------------|---------------------------------------------|----------------------------------------------|

| 0:0         | 1 | 973      | 973                                          | 1946                                        | 195                                          |

| 0:1         | 2 | 3892     | 3892                                         | 7784                                        | 778                                          |

| 1:0         | 3 | 15,568   | 15,568                                       | 31,136                                      | 3114                                         |

| 1:1         | 4 | 62,272   | 62,272                                       | 124,544                                     | 12,454                                       |

#### TABLE 9. RANGE/GAIN TYPICAL FSR LUX RANGES

Interrupt persist; Bits 1 and 0. The interrupt pin and the interrupt flag is triggered/set when the data sensor reading is out of the interrupt threshold window after m consecutive number of integration cycles. The interrupt persist bits determine m.

#### TABLE 10. INTERRUPT PERSIST

| BITS 1:0 | NUMBER OF INTEGRATION CYCLES |

|----------|------------------------------|

| 0:0      | 1                            |

| 0:1      | 4                            |

| 1:0      | 8                            |

| 1:1      | 16                           |

#### Interrupt Threshold HI Register 02(hex)

This register sets the HI threshold for the interrupt pin and the interrupt flag. By default the Interrupt threshold HI is FF(hex). The 8-bit data written to the register represents the upper MSB of a 16-bit value. The LSB is always 00(hex).

## Interrupt Threshold LO Register 03(hex)

This register sets the LO threshold for the interrupt pin and the interrupt flag. By default the Interrupt threshold LO is 00(hex). The 8-bit data written to the register represents the upper MSB of a 16-bit value. The LSB is always 00(hex).

#### Sensor Data Register 04(hex) and 05(hex)

When the device is configured to output a 16-bit data, the most significant byte is accessed at 04(hex), and the least significant byte can be accessed at 05(hex). The sensor data register is refreshed after very integration cycle.

## Timer Data Register 06(hex) and 07(hex)

Note that the timer counter value is only available when using the External Timing Mode. The 06(hex) and 07(hex) are the LSB and MSB respectively of a 16-bit timer counter value corresponding to the most recent sensor reading. Each clock cycle increments the counter. At the end of each integration period, the value of this counter is made available over the I<sup>2</sup>C. This value can be used to eliminate noise introduced by slight timing errors caused by imprecise external timing. Microcontrollers, for example, often cannot provide high-accuracy command-to-command timing, and the timer counter value can be used to eliminate the resulting noise.

#### TABLE 11. DATA REGISTERS

| ADDRESS<br>(hex) | CONTENTS                                                                                   |

|------------------|--------------------------------------------------------------------------------------------|

| 04               | Least-significant byte of most recent sensor reading.                                      |

| 05               | Most-significant byte of most recent sensor reading.                                       |

| 06               | Least-significant byte of timer counter value corresponding to most recent sensor reading. |

| 07               | Most-significant byte of timer counter value corresponding to most recent sensor reading.  |

# **Calculating Lux**

The ISL29003's output codes, DATA, are directly proportional to Lux.

$$E = \alpha \times DATA$$

(EQ. 1)

The proportionality constant  $\alpha$  is determined by the Full Scale Range, FSR, and the n-bit ADC which is user defined in the command register. The proportionality constant can also be viewed as the resolution; The smallest Lux measurement the device can measure is  $\alpha$ .

$$\alpha = \frac{\text{FSR}}{2^n}$$

(EQ. 2)

Full Scale Range, FSR, is determined by the software programmable Range/Gain, Range(k), in the command register and an external scaling resistor  $R_{EXT}$  which is referenced to  $100 k\Omega$ .

$$FSR = Range(k) \times \frac{100 k\Omega}{R_{EXT}}$$

(EQ. 3)

The transfer function effectively for each timing mode becomes:

#### INTERNAL TIMING MODE

$$E = \frac{Range(k) \times \frac{100 k\Omega}{R_{EXT}}}{2^{n}} \times DATA$$

(EQ. 4)

#### EXTERNAL TIMING MODE

$$E = \frac{Range(k) \times \frac{100 k\Omega}{R_{EXT}}}{COUNTER} \times DATA$$

(EQ. 5)

n = 4, 8, 12, or 16. This is the number of clock cycles programmed in the command register.

Range(k) is the user defined range in the Gain/Range bit in the command register.

$\mathsf{R}_{\mathsf{EXT}}$  is an external scaling resistor hardwired to the  $\mathsf{R}_{\mathsf{EXT}}$  pin.

DATA is the output sensor reading in number of counts available at the data register.

2<sup>n</sup> represents the maximum number of counts possible in Internal Timing Mode. For the External Timing Mode the maximum number of counts is stored in the data register named COUNTER

COUNTER is the number increments accrued for between integration time for External Timing Mode.

## Gain/Range, Range(k)

The Gain/Range can be programmed in the control register to give Range (k) determining the FSR. Note that Range(k) is not the FSR. See Equation 3. Range(k) provides four constants depending on programmed k that will be scaled by  $R_{EXT}$ . See Table 9. Unlike  $R_{EXT}$ , Range(k) dynamically adjusts the FSR. This function is especially useful when light conditions are varying drastically while maintaining excellent resolution.

# Number of Clock Cycles, n-bit ADC

The number of clock cycles determines "n" in the n-bit ADC;  $2^n$  clock cycles is a n-bit ADC. n is programmable in the command register in the width function. Depending on the application, a good balance of speed, and resolution has to be considered when deciding for n. For fast and quick measurement, choose the smallest n = 4. For maximum resolution without regard of time, choose n = 16. Table 12 compares the trade-off between integration time and resolution. See Equations 10 and 11 for the relation between integration time and n. See Equation 3 for the relation of n and resolution.

# TABLE 12. RESOLUTION AND INTEGRATION TIME SELECTION

|    | RANGE1<br>fosc = 327kHz |                         | RANGE4<br>fosc = 655kHz |                           |

|----|-------------------------|-------------------------|-------------------------|---------------------------|

| n  | TINT<br>(ms)            | RESOLUTION<br>LUX/COUNT | TINT<br>(ms)            | RESOLUTION<br>(LUX/COUNT) |

| 16 | 200                     | 0.01                    | 100                     | 1                         |

| 12 | 12.8                    | 0.24                    | 6.4                     | 16                        |

| 8  | 0.8                     | 3.90                    | 0.4                     | 250                       |

| 4  | 0.05                    | 62.5                    | 0.025                   | 4000                      |

$R_{EXT} = 100 k\Omega$

# External Scaling Resistor R<sub>EXT</sub> and fosc

The ISL29003 uses an external resistor  $R_{EXT}$  to fix its internal oscillator frequency,  $f_{OSC}$ . Consequently,  $R_{EXT}$  determines the fosc, integration time and the FSR of the device. Fosc, a dual speed mode oscillator, is inversely proportional to  $R_{EXT}$ . For user simplicity, the proportionality constant is referenced to fixed constants  $100 \ensuremath{\Omega\Omega}$  and  $655 \ensuremath{\text{KHz}}$ :

$$fosc1 = \frac{1}{2} \times \frac{100 k\Omega}{R_{EXT}} \times 655 kHz$$

(EQ. 6)

$$fosc2 = \frac{100k\Omega}{R_{EXT}} \times 655kHz$$

(EQ. 7)

fosc1 is oscillator frequency when Range1 or Range2 are set. This is nominally 327kHz when  $R_{EXT}$  is  $100 k \Omega.$

fosc2 is the oscillator frequency when Range3 or Range4 are set. This is nominally 655kHz when  $R_{FXT}$  is 100k $\Omega$ .

When the Range/Gain bits are set to Range1 or Range2, fosc runs at half speed compared to when Range/Gain bits are set to Range3 and Range4.

$$f_{osc}1 = \frac{1}{2}(f_{osc}2) \tag{EQ. 8}$$

The automatic fosc adjustment feature allows significant improvement of signal-to-noise ratio when detecting very low Lux signals.

## Integration Time or Conversion Time

Integration time is the period during which the device's analog-to-digital ADC converter samples the photodiode current signal for a Lux measurement. Integration time, in other words, is the time to complete the conversion of analog photodiode current into a digital signal--number of counts.

Integration time affects the measurement resolution. For better resolution, use a longer integration time. For short and fast conversions use a shorter integration time.

The ISL29003 offers user flexibility in the integration time to balance resolution, speed and noise rejection. Integration time can be set internally or externally and can be programmed in the command register 00(hex) bit 5.

## INTEGRATION TIME IN INTERNAL TIMING MODE

This timing mode is programmed in the command register 00(hex) bit 5. Most applications will be using this timing mode. When using the Internal Timing Mode,  $f_{osc}$  and n-bits resolution determine the integration time.  $T_{int}$  is a function of the number of clock cycles and fosc.

$$T_{int} = 2^{n} \times \frac{1}{f_{osc}}$$

for Internal Timing Mode only (EQ. 9)

n = 4, 8, 12, and 16. n is the number of bits of resolution.

2<sup>n</sup> therefore is the number of clock cycles. n can be programmed at the command register 00(hex) bits 1 and 0.

Since fosc is dual speed depending on the Gain/Range bit,  $T_{int}$  is dual time. The integration time as a function of  $R_{EXT}$  and n is:

$$T_{int}1 = 2^{n} \times \frac{R_{EXT}}{327 \text{kHz} \times 100 \text{k}\Omega}$$

(EQ. 10)

T<sub>int1</sub> is the integration time when the device is configured for Internal Timing Mode and Gain/Range is set to Range1 or Range2.

$$T_{int}^{2} = 2^{n} \times \frac{R_{EXT}}{655 \text{kHz} \times 100 \text{k}\Omega}$$

(EQ. 11)

$T_{int2}$  is the integration time when the device is configured for Internal Timing Mode and Gain/Range is set to Range3 or Range4.

#### TABLE 13. INTEGRATION TIMES FOR TYPICAL $\mathsf{R}_{\mathsf{EXT}}$ values

| R <sub>EXT</sub> | RANGE1<br>RANGE2 |            | RANGE3<br>RANGE4 |       |

|------------------|------------------|------------|------------------|-------|

| (kΩ)             | n = 16-BIT       | n = 12-BIT | n = 12-BIT       | n = 4 |

| 50               | 100              | 6.4        | 3.2              | 0.013 |

| 100**            | 200              | 13         | 6.5              | 0.025 |

| 200              | 400              | 26         | 13               | 0.050 |

| 500              | 1000             | 64         | 32               | 0.125 |

\*Integration time in milliseconds

\*\*Recommended REXT resistor value

#### INTEGRATION TIME IN EXTERNAL TIMING MODE

This timing mode is programmed in the command register 00(hex) bit 5. External Timing Mode is recommended when integration time can be synchronized to an external signal such as a PWM to eliminate noise.

For Mode1 or Mode2 operation, the integration starts when the sync\_iic command is sent over the  $I^2C$  lines. The device needs two sync\_iic commands to complete a photodiode conversion. The integration then stops when another sync\_iic command is received. Writing a logic 1 to the sync\_iic bit ends the current adc integration and starts another one.

For Mode3, the operation is a sequential Mode1 and Mode2. The device needs three sync\_iic commands to complete two photodiode measurements. The 1st sync\_iic command starts the conversion of the diode1. The 2nd sync\_iic completes the conversion of diode1 and starts the conversion of diode2. The 3rd sync\_iic pules ends the conversion of diode2 and starts over again to commence conversion of diode1.

The integration time, T<sub>int</sub>, is determined by Equation 12:

$$T_{int} = \frac{i_{12C}}{f_{12C}}$$

(EQ. 12)

$i_{I2C}$  is the number of I<sup>2</sup>C clock cycles to obtain the T<sub>int.</sub>  $f_{I2C}$  is the I<sup>2</sup>C operating frequency

The internal oscillator,  $f_{OSC}$ , operates identically in both the internal and external timing modes, with the same dependence on  $R_{EXT}$ . However, in External Timing Mode, the number of clock cycles per integration is no longer fixed at  $2^n$ . The number of clock cycles varies with the chosen integration time, and is limited to  $2^{16} = 65,536$ . In order to avoid erroneous Lux readings the integration time must be short enough not to allow an overflow in the counter register.

$$T_{int} < \frac{65,535}{f_{OSC}}$$

(EQ. 13)

9

$f_{OSC} = 327 \text{kHz}^{*}100 \text{k}\Omega/\text{R}_{EXT}$ . When Range/Gain is set to Range1 or Range2.

$f_{OSC} = 655 \text{kHz}^{*}100 \text{k}\Omega/\text{R}_{EXT}$ . When Range/Gain is set to Range3 or Range4.

#### Noise Rejection

In general, integrating type ADC's have an excellent noiserejection characteristics for periodic noise sources whose frequency is an integer multiple of the integration time. For instance, a 60Hz AC unwanted signal's sum from 0ms to k\*16.66ms (k = 1,2...k<sub>i</sub>) is zero. Similarly, setting the device's integration time to be an integer multiple of the periodic noise signal, greatly improves the light sensor output signal in the presence of noise.

#### Design Example 1

The ISI29003 will be designed in a portable system. The ambient light conditions that the device will be exposed to is at most 500Lux which is a good office lighting. The light source has a 50/60Hz power line noise which is not visible by the human eye. The  $I^2C$  clock is 10kHz.

Solution 1 - Using Internal Timing Mode

In order to achieve both 60Hz and 50Hz AC noise rejection, the integration time needs to be adjusted to coincide with an integer multiple of the AC noise cycle times.

$$T_{int} = i(1/60Hz) = j(1/50Hz).$$

The first instance of integer values at which  $T_{int}$  rejects both 60Hz and 50Hz is when i = 6, and j= 5.

T<sub>int</sub> = 100ms

Next, the Gain/Range needs to be determined. Based on the application condition given, Lux(max) = 500Lux, a range of 1000Lux is desirable. This corresponds to a Gain/Range Range1 mode. Also impose a resolution of n = 16-bit. Hence we choose Equation 10 to determine  $R_{FXT}$ .

$$R_{EXT} = \frac{T_{int} \times 327 kHz \times 100 k\Omega}{2^{n}}$$

$R_{EXT} = 50 k\Omega$

for Internal Timing Mode and Gain/Range is set to Range3 or Range4 only

The Full Scale Range, FSR, needs to be determined. From Equation 3:

$$\mathsf{FSR} = 1000 \mathsf{Lux} \frac{100 \mathrm{k}\Omega}{50 \mathrm{k}\Omega}$$

FSR = 2000Lux

The effective transfer function becomes:

$$\mathsf{E} = \frac{\mathsf{data}}{2^{16}} \times 2000 \mathsf{Lux}$$

#### TABLE 14. SOLUTION1 SUMMARY TO EXAMPLE DESIGN PROBLEM

| DESIGN PARAMETER  | VALUE                                    |

|-------------------|------------------------------------------|

| T <sub>int</sub>  | 100ms                                    |

| R <sub>EXT</sub>  | 50kΩ                                     |

| Gain/Range Mode   | Range1 = 1000Lux                         |

| FSR               | 2000Lux                                  |

| # of clock cycles | 2 <sup>16</sup>                          |

| Transfer Function | $E = \frac{DATA}{2^{16}} \times 2000Lux$ |

#### Solution 2 - Using External Timing Mode

From solution 1, the desired integration time is 100ms. Note that the  $R_{EXT}$  resistor only determines the inter oscillator frequency when using external timing mode. Instead the integration time is the time between two sync\_iic commands sent through the  $I^2C$ . The programmer determines how many  $I^2C$  clock cycles to wait between two external timing commands.

$i_{I2C} = f_{I2C} * T_{int} =$  number of I<sup>2</sup>C clock cycles

i<sub>I2C</sub> = 10kHz \*100ms

$i_{I2C}$  = 1,000 I<sup>2</sup>C clock cycles. An external sync\_iic command sent 1,000 cycles after another sync\_iic command rejects both 60Hz and 50Hz AC noise signals.

Next is to pick an arbitrary  $R_{EXT} = 100 k\Omega$  and to choose the Gain/Range Mode. For a maximum 500Lux, Range1 is adequate. From Equation 3:

$FSR = 1000Lux \frac{100k\Omega}{100k\Omega}$

FSR = 1000|ux|

The effective transfer function becomes:

$\mathbf{E} = \frac{\mathsf{DATA}}{\mathsf{COUNTER}} \times \mathbf{1000}\mathsf{Lux}$

DATA is the sensor reading data located in data registers 04(hex) and 05(hex)

COUNTER is the timer counter value data located in data registers 06(hex) and 07(hex). In this sample problem, COUNTER = 1000.

# TABLE 15. SOLUTION2 SUMMARY TO EXAMPLE DESIGN PROBLEM

| DESIGN PARAMETER  | VALUE                                      |

|-------------------|--------------------------------------------|

| T <sub>int</sub>  | 100ms                                      |

| R <sub>EXT</sub>  | 100kΩ                                      |

| Gain/Range Mode   | Range1 = 1000Lux                           |

| FSR               | 1000Lux                                    |

| # of clock cycles | COUNTER = 1000                             |

| Transfer Function | $E = \frac{DATA}{COUNTER} \times 1000 Lux$ |

## **IR Rejection**

Any filament type light source has a high presence of infrared component invisible to the human eye. A white fluorescent lamp, on the other hand has a low IR content. As a result, output sensitivity may vary depending on the light source. Maximum attenuation of IR can be achieved by properly scaling the readings of Diode1 and Diode2. The user obtains data reading from sensor diode 1, D1, which is sensitive to visible and IR, then reading from sensor diode 2, D2 which is mostly sensitive from IR. The graph on Figure 7 shows the effective spectral response after applying Equation 14 of the ISL29003 from 400nm to 1000nm. The equation below describes the method of cancelling IR in internal timing mode.

$$D3 = n(D1 - kD2)$$

(EQ. 14)

Where:

data = lux amount in number of counts less IR presence

D1 = data reading of Diode 1

D2 = data reading of Diode 2

n = 1.85. This is a fudge factor to scale back the sensitivity up to ensure Equation 4 is valid.

k = 7.5. This is a scaling factor for the IR sensitive Diode 2.

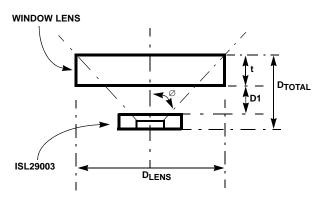

## Flat Window Lens Design

A window lens will surely limit the viewing angle of the ISL29003. The window lens should be placed directly on top of the device. The thickness of the lens should be kept at minimum to minimize loss of power due to reflection and also to minimize loss of loss due to absorption of energy in the plastic material. A thickness of t = 1mm is recommended for a window lens design. The bigger the diameter of the window lens the wider the viewing angle is of the ISL29003. Table 16 shows the recommended dimensions of the optical window to ensure both 35° and 45° viewing angle. These dimensions are based on a window lens thickness of 1.0mm and a refractive index of 1.59.

$\emptyset$  = Viewing angle

FIGURE 4. FLAT WINDOW LENS

#### TABLE 16. RECOMMENDED DIMENSIONS FOR A FLAT WINDOW DESIGN

| D <sub>TOTAL</sub> | D1   | D <sub>LENS</sub> @ 35<br>VIEWING ANGLE | D <sub>LENS</sub> @ 45<br>VIEWING ANGLE |

|--------------------|------|-----------------------------------------|-----------------------------------------|

| 1.5                | 0.50 | 2.25                                    | 3.75                                    |

| 2.0                | 1.00 | 3.00                                    | 4.75                                    |

| 2.5                | 1.50 | 3.75                                    | 5.75                                    |

| 3.0                | 2.00 | 4.30                                    | 6.75                                    |

| 3.5                | 2.50 | 5.00                                    | 7.75                                    |

t = 1 Thickness of lens

D1 Distance between ISL29001 and inner edge of lens DLENS Diameter of lens

D<sub>TOTAL</sub> Distance constraint between the ISL29001 and lens outer edge

\* All dimensions are in mm.

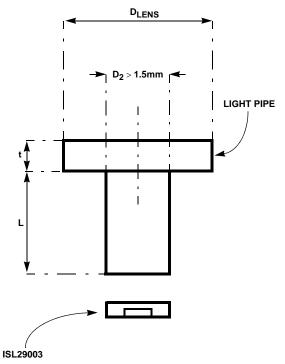

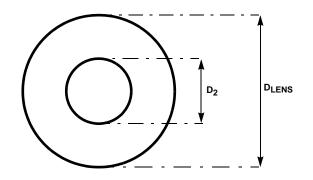

## Window with Light Guide Design

If a smaller window is desired while maintaining a wide effective viewing angle of the ISL29003, a cylindrical piece of transparent plastic is needed to trap the light and then focus and guide the light on to the device. Hence the name light guide or also known as light pipe. The pipe should be placed directly on top of the device with a distance of D1 = 0.5mm to achieve peak performance. The light pipe should have minimum of 1.5mm in diameter to ensure that whole area of the sensor will be exposed. See Figure 5.

FIGURE 5. WINDOW WITH LIGHT GUIDE/PIPE

# Suggested PCB Footprint

Footprint pads should be a nominal 1-to-1 correspondence with package pads. The large, exposed central die-mounting paddle in the center of the package requires neither thermal nor electrical connection to the PCB, and such connection should be avoided.

# Layout Considerations

The ISL29003 is relatively insensitive to layout. Like other  $I^2C$  devices, it is intended to provide excellent performance even in significantly noisy environments. There are only a few considerations that will ensure best performance.

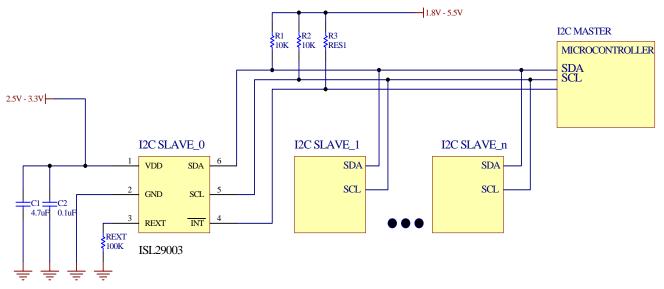

Route the supply and I<sup>2</sup>C traces as far as possible from all sources of noise. Use two power-supply decoupling capacitors,  $4.7\mu$ F and  $0.1\mu$ F, placed close to the device.

# Typical Circuit

A typical application for the ISL29003 is shown in Figure 6. The ISL29003's  $I^2C$  address is internally hardwired as 44(hex). The device can be tied onto a system's  $I^2C$  bus together with other  $I^2C$  compliant devices.

# Soldering Considerations

Convection heating is recommended for reflow soldering; direct-infrared heating is not recommended. The plastic ODFN package does not require a custom reflow soldering profile, and is qualified to +260°C. A standard reflow soldering profile with a +260°C maximum is recommended

FIGURE 6. ISL29003 TYPICAL CIRCUIT

# Typical Performance Curves (R<sub>EXT</sub> = 100kΩ)

FIGURE 7. SPECTRAL RESPONSE

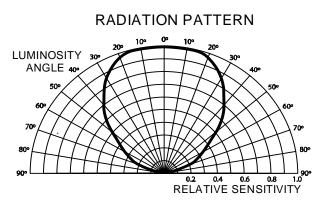

FIGURE 8. RADIATION PATTERN

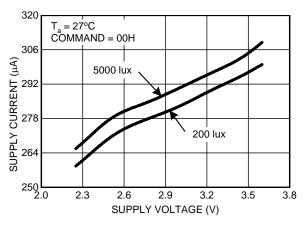

FIGURE 9. SUPPLY CURRENT vs SUPPLY VOLTAGE

13

intersil

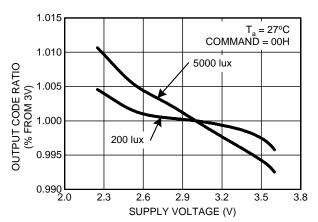

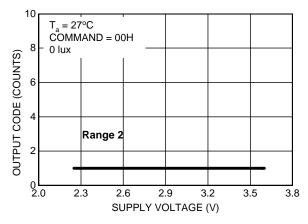

FIGURE 10. OUTPUT CODE FOR 0 LUX vs SUPPLY VOLTAGE

# **Typical Performance Curves** (*R*<sub>EXT</sub> = 100*k*Ω) (Continued)

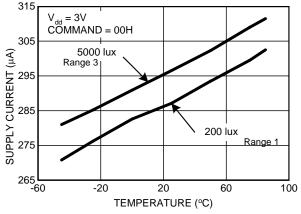

FIGURE 13. SUPPLY CURRENT vs TEMPERATURE

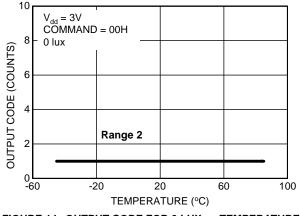

FIGURE 14. OUTPUT CODE FOR 0 LUX vs TEMPERATURE

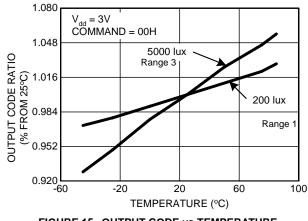

FIGURE 15. OUTPUT CODE vs TEMPERATURE

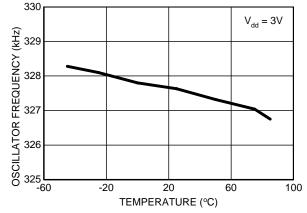

FIGURE 16. OSCILLATOR FREQUENCY vs TEMPERATURE

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

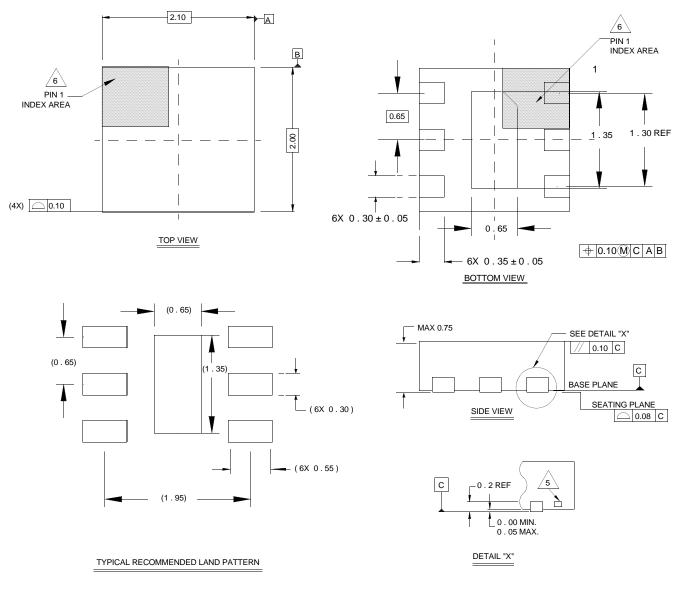

# Package Outline Drawing

# L6.2x2.1

6 LEAD OPTICAL DUAL FLAT NO-LEAD PLASTIC PACKAGE (ODFN) Rev 0, 9/06

NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 indentifier may be either a mold or mark feature.