# MB86933H

# 930 Series 32-BIT RISC EMBEDDED PROCESSOR

ADVANCE INFORMATION SEPTEMBER 1996

#### **FEATURES**

- 25 MHz (40ns/cycle) operating frequency

- SPARC V8 high-performance RISC architecture

- 1 KByte, direct mapped instruction cache

- Flexible locking mechanism for instruction cache

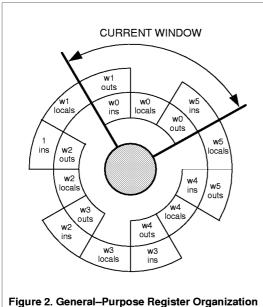

- 6 window, 104 word register file

- Fast interrupt response time

- 16 address spaces, 256 MByte each

- · User and supervisor modes

- Data write buffer and instruction prefetch buffer

- On-chip programmable chip selects and wait-state generators

- Support for 8–, 16–, and 32–bit wide external memory

- On-chip DRAM controller for glue-less connection to DRAM

- On-chip interrupt controller

- On-chip clock generator circuit

- JTAG test interface

- Single vector trapping

- 0.8 micron gate, 3–level metal CMOS technology

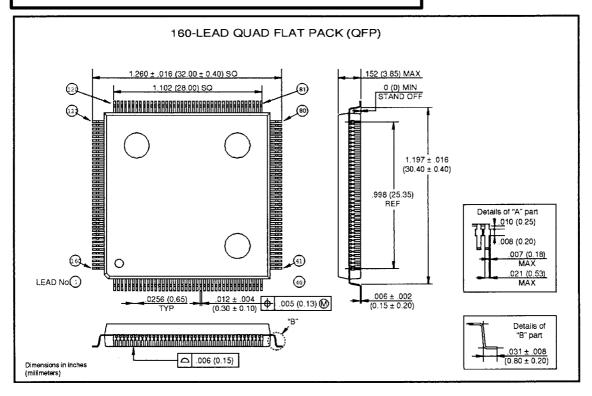

- 160-pin QFP MB86933-compatible pinout

# **GENERAL DESCRIPTION**

The MB86933H is targeted toward applications which require a high-performance, low-cost processor with high integration. The CPU is based on the SPARC V8 architecture, is code compatible with previous implementations, and is pin compatible with the MB86933. At 25 MHz, the processor executes at 25 MIPs peak and 22.5 MIPs sustained performance.

Included to maximize the performance of the system are a large register file, a 1 KB yte instruction cache, a data write buffer, and an instruction prefetch buffer.

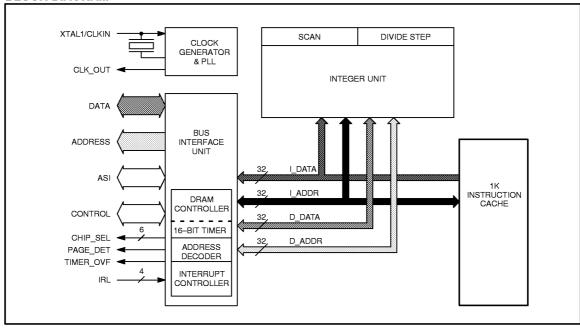

Included to minimize external glue logic are chip—select outputs, programmable wait—state generators, an interrupt controller, and a complete DRAM controller. Also included is the ability to program each chip select region for different external data bus widths (8/16/32–bit). See MB86933H block diagram on page 3.

These features combine to allow the MB86933H to offer high performance and SPARC compatibility at a low cost to make it the right choice for a wide range of cost–sensitive, performance–oriented embedded designs.

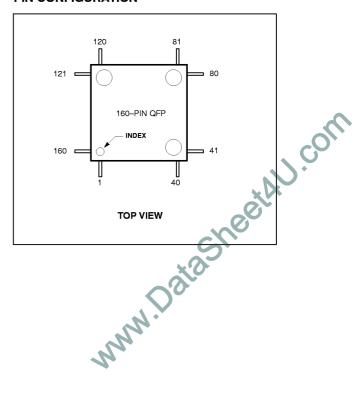

# **PIN CONFIGURATION**

# PIN ASSIGNMENT — 160-PIN QFP

| FIN ASSIGNMENT — TOO-FIN QI F |            |      |            |          |      |            |            |      |            |           |      |

|-------------------------------|------------|------|------------|----------|------|------------|------------|------|------------|-----------|------|

| PIN<br>NO.                    | PIN NAME   | TYPE | PIN<br>NO. | PIN NAME | TYPE | PIN<br>NO. | PIN NAME   | TYPE | PIN<br>NO. | PIN NAME  | TYPE |

| 1                             | ADR < 8 >  | 0    | 41         | D < 27 > | I/O  | 81         | D < 4 >    | I/O  | 121        | -BE < 0 > | 0    |

| 2                             | ADR <9>    | 0    | 42         | N.C.     | _    | 82         | D <3>      | I/O  | 122        | N.C.      | _    |

| 3                             | ADR < 10 > | 0    | 43         | D < 26 > | I/O  | 83         | D <2>      | I/O  | 123        | –BE <1>   | 0    |

| 4                             | ADR < 11 > | 0    | 44         | D < 25 > | I/O  | 84         | D <1>      | I/O  | 124        | –BE <2>   | 0    |

| 5                             | ADR < 12 > | 0    | 45         | D < 24 > | I/O  | 85         | D < 0 >    | I/O  | 125        | –BE <3>   | 0    |

| 6                             | VDD        | _    | 46         | D < 23 > | I/O  | 86         | VSS        |      | 126        | ASI < 0 > | 0    |

| 7                             | VSS        | _    | 47         | D < 22 > | I/O  | 87         | VDD        | _    | 127        | ASI < 1 > | 0    |

| 8                             | ADR < 13 > | О    | 48         | VSS      | _    | 88         | -MEXC      | I    | 128        | ASI <2>   | 0    |

| 9                             | ADR < 14 > | О    | 49         | VDD      | _    | 89         | -READY     | I    | 129        | ASI < 3 > | 0    |

| 10                            | ADR < 15 > | 0    | 50         | D < 21 > | I/O  | 90         | -BREQ      | - 1  | 130        | -RAS1     | _    |

| 11                            | ADR < 16 > | 0    | 51         | VSS      |      | 91         | -AS        | 0    | 131        | VSS       | _    |

| 12                            | -CAS0      | _    | 52         | VDD      |      | 92         | –RD/WR     | 0    | 132        | VDD       | _    |

| 13                            | ADR < 17 > | 0    | 53         | D < 20 > | I/O  | 93         | -LOCK      | 0    | 133        | -TRST     | ı    |

| 14                            | ADR < 18 > | 0    | 54         | D < 19 > | I/O  | 94         | -BGRNT     | О    | 134        | -RESET    | 1    |

| 15                            | -CAS1      | _    | 55         | D < 18 > | I/O  | 95         | -DWE       |      | 135        | VDD       | _    |

| 16                            | ADR < 19 > | 0    | 56         | VSS      |      | 96         | -ERROR     | 0    | 136        | VSS       | _    |

| 17                            | ADR < 20 > | 0    | 57         | N.C.     |      | 97         | VSS        | _    | 137        | -BMODE8   | 1    |

| 18                            | -CAS2      | _    | 58         | D < 17 > | I/O  | 98         | VDD        | _    | 138        | VSS       | _    |

| 19                            | ADR < 21 > | 0    | 59         | D < 16 > | I/O  | 99         | -SAME_PAGE | 0    | 139        | VDD       | _    |

| 20                            | VDD        | _    | 60         | N.C.     | -    | 100        | -CS < 0 >  | 0    | 140        | -BMODE16  | ı    |

| 21                            | VSS        | _    | 61         | D < 15 > | I/O  | 101        | VDD        | _    | 141        | N.C.      | _    |

| 22                            | ADR < 22 > | 0    | 62         | D < 14 > | I/O  | 102        | -CS <1>    | 0    | 142        | TDI       | 1    |

| 23                            | -CAS3      | _    | 63         | VDD      | _    | 103        | -CS <2>    | 0    | 143        | TMS       | ı    |

| 24                            | ADR < 23 > | 0    | 64         | D < 13 > | I/O  | 104        | -CS < 3 >  | 0    | 144        | VDD       | _    |

| 25                            | ADR < 24 > | О    | 65         | D < 12 > | I/O  | 105        | VSS        | _    | 145        | VSS       | -    |

| 26                            | ADR < 25 > | О    | 66         | VDD      | _    | 106        | -CS < 4 >  | О    | 146        | IRL < 0 > | 1    |

| 27                            | VSS        | _    | 67         | VSS      | _    | 107        | -CS < 5 >  | О    | 147        | IRL < 1 > | ı    |

| 28                            | VDD        | _    | 68         | -RAS0    | _    | 108        | TCK        | ı    | 148        | IRL <2>   | 1    |

| 29                            | ADR < 26 > | О    | 69         | D < 11 > | I/O  | 109        | VDD        | _    | 149        | IRL <3>   | ı    |

| 30                            | ADR < 27 > | О    | 70         | D < 10 > | I/O  | 110        | VSS        | _    | 150        | VSS       | -    |

| 31                            | D < 31 >   | I/O  | 71         | D < 9 >  | I/O  | 111        | VDD        | _    | 151        | VDD       | _    |

| 32                            | VDD        | _    | 72         | D < 8 >  | I/O  | 112        | XTAL2      | О    | 152        | TDO       | 0    |

| 33                            | VSS        | _    | 73         | D <7>    | I/O  | 113        | CLK_ECB    | ı    | 153        | VSS       | -    |

| 34                            | D < 30 >   | I/O  | 74         | VDD      | _    | 114        | VSS        | _    | 154        | VDD       | _    |

| 35                            | D < 29 >   | I/O  | 75         | VSS      | _    | 115        | XTAL1      | I    | 155        | ADR <2>   | 0    |

| 36                            | VSS        | _    | 76         | VDD      | _    | 116        | CLKOUT1    | О    | 156        | ADR < 3 > | 0    |

| 37                            | VDD        | _    | 77         | VSS      | _    | 117        | CLKOUT2    | 0    | 157        | ADR < 4 > | 0    |

| 38                            | VDD        | _    | 78         | D < 6 >  | I/O  | 118        | VDD        | _    | 158        | ADR <5>   | 0    |

| 39                            | VSS        | _    | 79         | VSS      | _    | 119        | VSS        | _    | 159        | ADR < 6 > | 0    |

| 40                            | D < 28 >   | I/O  | 80         | D <5>    | I/O  | 120        | -TIMER_OVF | 0    | 160        | ADR < 7 > | 0    |

## **ORDERING CODE**

| Clock Frequency (MHz) | Ordering Code     | Package Type    |

|-----------------------|-------------------|-----------------|

| 25                    | MB86933H-25PF-G-B | Plastic QFP 160 |

Note: The ordering code for production level product. Early shipments of this device may be marked with "ES" to indicate that the part is not yet at full production status. Contact your local Fujitsu representative for additional information on "ES" level products.

# **BLOCK DIAGRAM**

# SIGNAL DESCRIPTIONS

| SYMBOL                      | TYPE                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

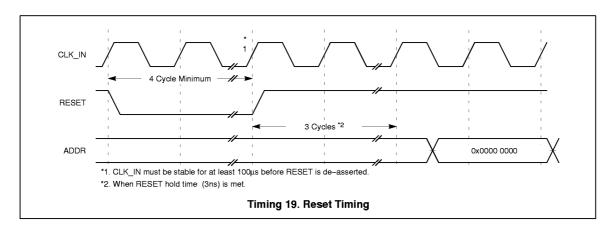

| -RESET                      | l<br>A (L)                   | SYSTEM RESET: Asserting reset for at least 4 processor cycles after the clock has stabilized, causes the MB86933 to be initialized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| XTAL1,<br>(CLK_IN)<br>XTAL2 | I/O<br>O<br>G (Q)<br>I (Q)   | EXTERNAL OSCILLATOR: The crystal inputs determine execution rate and timing of the MB86933H processor. Connecting a crystal to these pins forms a complete crystal oscillator circuit. The crystal oscillator frequency is the same as the processor operating frequency. When driving the processor with an external clock, XTAL2 pin should be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

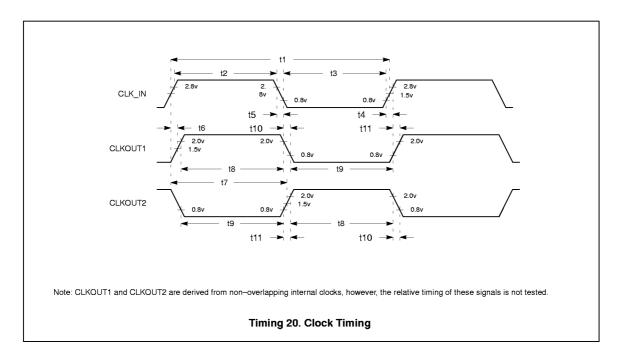

| CLKOUT1                     | O<br>G (Q)<br>I (Q)          | CLOCK OUTPUT 1: This is an output signal against which MB86933H bus transactions can be referenced. The CLKOUT1 frequency is the same as the frequency applied to XTAL1 and is the same as the processor operating frequency. CLKOUT1 is in phase with CLK_IN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CLKOUT2                     | O<br>G (Q)<br>I (Q)          | CLOCK OUTPUT 2: This is an output signal against which MB86933H bus transactions can be referenced. The CLKOUT2 frequency is the same as the frequency applied to XTAL1 and is the same as the processor operating frequency. CLKOUT2 is out of phase with CLK_IN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

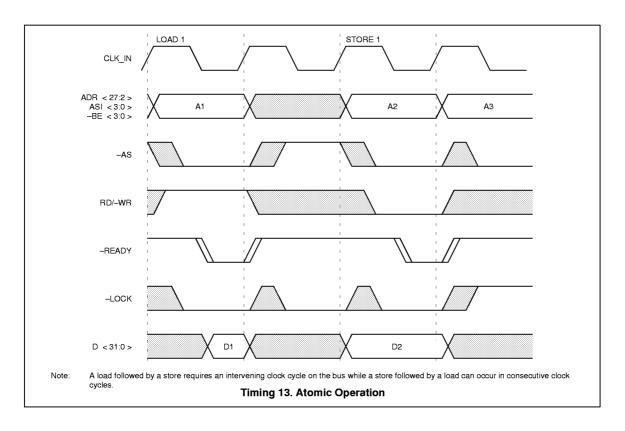

| -LOCK                       | O<br>S (L)<br>G (Z)<br>I (1) | BUS LOCK: This is a control signal asserted by the processor to indicate to the system that the current bus transaction requires more than one transfer on the bus. The Atomic Load Store instruction for example requires contiguous bus transactions which cause the assertion of the bus lock signal. The bus may not be granted to another bus owner as long as –LOCK is active. –LOCK is asserted with the assertion of –AS and remains active until –READY is asserted at the end of the locked transaction.                                                                                                                                                                                                                                                                                                                                                              |

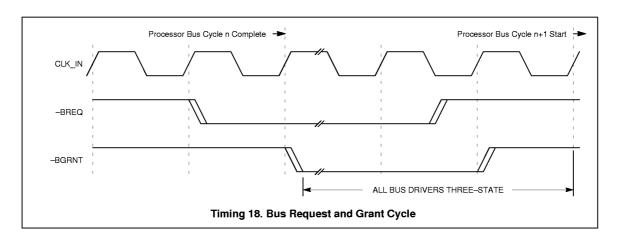

| -BREQ                       | I<br>S (L)                   | BUS REQUEST: Asserted by another device on the bus to indicate that it wants ownership of the bus. The request must be answered with a bus grant (-BGRNT) from the MB86933H before the device can proceed by driving the bus. Once the bus has been granted, the device has ownership of the bus until it de-asserts -BREQ. The user should ensure that devices on the bus cannot monopolize the bus to the exclusion of the CPU. Inputs to -BREQ while -RESET is active are valid and cause Bus Grant to be asserted.                                                                                                                                                                                                                                                                                                                                                          |

| -BGRNT                      | O<br>S (L)<br>G (0)<br>I (Q) | BUS GRANT: Asserted by the CPU in response to a request from a device wanting ownership of the bus. The CPU grants the bus to other devices only after all transfers for the current transaction are completed. All bus drivers are three–stated with the assertion of the bus grant signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| -ERROR                      | O<br>A (L)<br>G (Q)<br>I (Q) | ERROR SIGNAL: Asserted by the CPU to indicate that it has halted in an error state as a result of encountering a synchronous trap while traps are disabled. In this situation the CPU saves the PC and nPC registers, sets the tt value in the TBR, enters into an error state and asserts the –ERROR signal. The system can monitor the –ERROR pin and initiate a reset under the error condition. This pin is high on reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

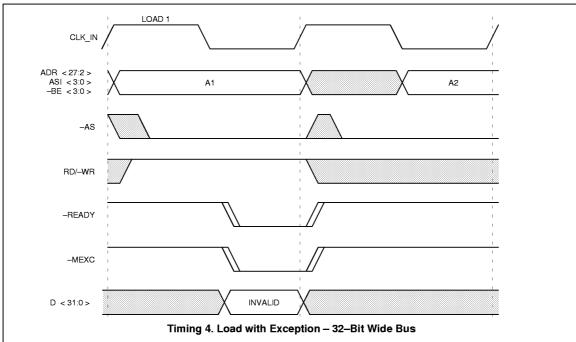

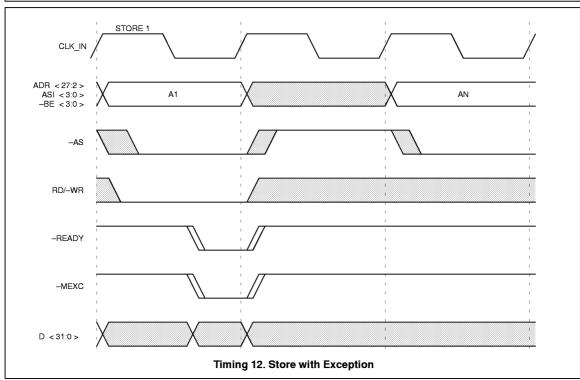

| -MEXC                       | I<br>S (L)                   | MEMORY EXCEPTION: Asserted by the memory system to indicate a memory error on either a data or instruction access. Assertion of this signal initiates either a data or instruction access exception trap in the IU. The current bus access is invalidated by asserting the –MEXC in the same cycle as the –READY signal. Assertion in any other bus cycle give indeterminate results. The IU ignores the contents of the data bus in cycles where –MEXC is asserted.                                                                                                                                                                                                                                                                                                                                                                                                            |

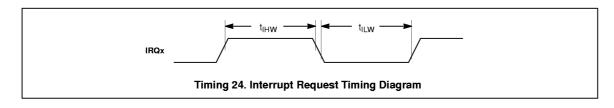

| IRL< 3:0 > /<br>IRQ<15:12>  | l<br>A (L)                   | INTERRUPT REQUEST BUS: Based on the mode selected in the on—chip interrupt controller, these pins are defined in two ways. In one mode (IRL) the value on these pins defines an external interrupt vector. IRL <3:0>=1111 forces a non—maskable interrupt. IRL value of 0000 indicates no pending interrupts. All other values indicate maskable interrupts as enabled in the PIL field of the processor status register (PSR). In this mode, interrupts should be latched and prioritized by external logic and should be held pending until acknowledged by the processor. In the other mode (IRQ), each pin represents a decoded interrupt source. When active, the values on pins IRQ<15:12> will cause the processor to vector to interrupts 15 through 12, respectively. The trigger for each IRQ pin can be set for high—level, low—level, rising edge, or falling edge. |

<sup>1.</sup> In the following descriptions, signal names preceded by a minus sign (–) indicate an active low state. Dual function pins have two names separated by a slash (/).

| SYMBOL                                   | TYPE                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| -TIMER_OVF                               | O<br>S (L)<br>G (Q)<br>I (Q) | TIMER UNDERFLOW: Asserted by the processor to indicate that the internal 16-bit timer has underflowed. This signal can be used to initiate a DRAM refresh cycle for the on-chip DRAM controller or can be used to generate periodic waveforms. The timer overflow signal can be programmed to be active for a single cycle or for three cycles after each underflow. On reset, the timer is turned off and -TIMER_OVF is high.                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

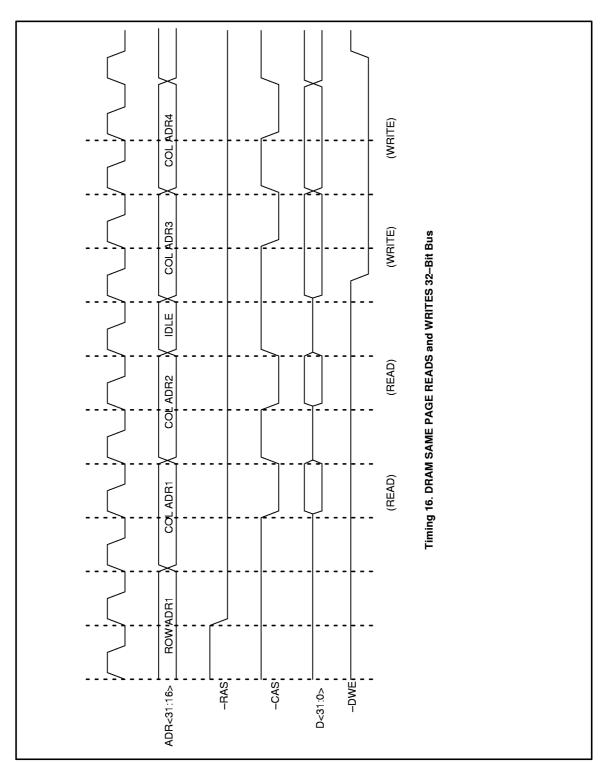

| -SAME_PAGE                               | O<br>S (L)<br>G (1)<br>I (1) | SAME-PAGE DETECT: The -SAME_PAGE is used to take advantage of fast consecutive accesses within Fast Page Mode DRAM page boundaries. This signal is an output but also goes internally to the on-chip DRAM controller. It is asserted by the processor when the current address is within the chip select 4 region and is also within the same page as the previous memory access The -SAME_PAGE signal is asserted with -AS and remains active for one processor cycleSAME_PAGE is never asserted in the first transaction following a transaction by another device on the bus. The page size is specified by writing the SAME-PAGE MASK register.                                       |  |  |  |  |  |  |

| -CS0, -CS1,<br>-CS2, -CS3,<br>-CS4, -CS5 | O<br>S (L)<br>G (1)<br>I (1) | CHIP SELECTS: These outputs are asserted when the value on the address bus matches the address range in one of the corresponding ADDRESS RANGE registers. The signals are used to decode the current address into one of six address ranges. Address ranges should not overlap. Each address range has a corresponding wait specifier which is used to automatically assert the —READY signal after a user defined number of processor clock cycles. This allows a variety of memory and I/O devices with different access times to be connected to the MB86933H without the need for additional logic. On the MB86933H, chip select 4 is defined to support the on—chip DRAM controller. |  |  |  |  |  |  |

| ADR < 27:2 >                             | O<br>S (L)<br>G (Z)<br>I (1) | ADDRESS BUS: The 26-bit ADDRESS BUS (ADR27-ADR2) is an output which identifies the data or instruction address of a 32-bit word. Reads are always one word in size while byte, half-word, or word transaction sizes for writes are identified by separate byte-enable signals (-BE0-3). The address bus is valid for the duration of the bus transaction. ADR27-ADR16 (MA<11:0>) are also used for the DRAM address. The value on these pins when RAS_falls is the DRAM row address. The value on these pins when CAS_falls is the DRAM column address.                                                                                                                                   |  |  |  |  |  |  |

| ASI < 3:0 >                              | O<br>S (L)<br>G (Z)<br>I (1) | ADDRESS SPACE IDENTIFIERS: The ADDRESS SPACE IDENTIFIERS are outputs which indicate to which of 16 available spaces the current ADDRESS BUS value corresponds. The ASI values are defined as follows:    ASI                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| SYMBOL   | TYPE                           |                                                                                                                                                                                                                                                                                                                                                       | DESC                                                                                                                               | RIPTION                                                                                                                                                                                 |                                                                                                                                                                                   |                                                                                                                                                                                         |  |  |

|----------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

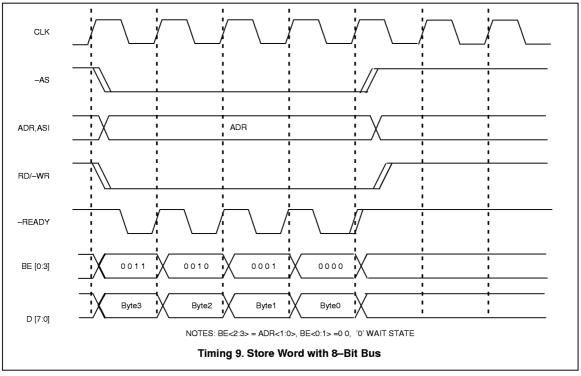

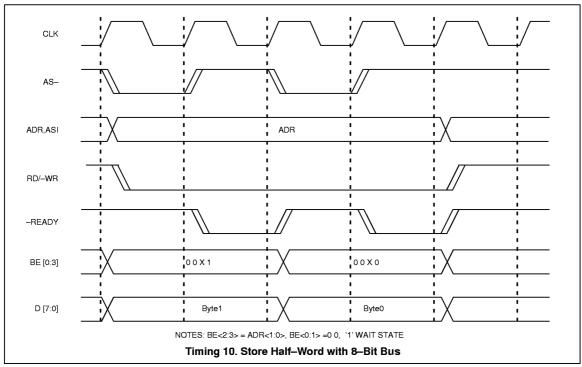

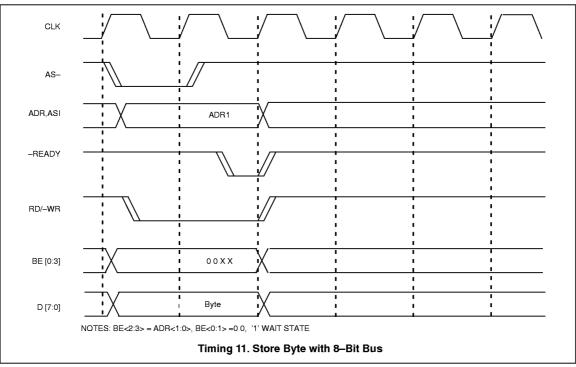

| -BE3-0   | O<br>S (L)<br>S G (Z)<br>I (O) | half–word or word transaction corresponding address value the bus transaction. This bus transactions all sub–word required the appropriate byte or half–v Possible values for –BE3–0 a Byte Writes Half–Word Writes Word Writes BE < 2:3 > are also used in 8                                                                                         | Half–Word Writes 1 1 0 0 0 0 1 1                                                                                                   |                                                                                                                                                                                         |                                                                                                                                                                                   |                                                                                                                                                                                         |  |  |

|          |                                | ſ                                                                                                                                                                                                                                                                                                                                                     | Due Mede                                                                                                                           | Duto                                                                                                                                                                                    | DE 40:0                                                                                                                                                                           | 1                                                                                                                                                                                       |  |  |

|          |                                |                                                                                                                                                                                                                                                                                                                                                       | Bus Mode<br>8-bit                                                                                                                  | Byte<br>0                                                                                                                                                                               | BE < 2:3 >                                                                                                                                                                        | -                                                                                                                                                                                       |  |  |

|          |                                |                                                                                                                                                                                                                                                                                                                                                       | 5 5                                                                                                                                | 1                                                                                                                                                                                       | 0.1                                                                                                                                                                               |                                                                                                                                                                                         |  |  |

|          |                                |                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                    | 2<br>3                                                                                                                                                                                  | 1 0<br>1 1                                                                                                                                                                        |                                                                                                                                                                                         |  |  |

|          |                                |                                                                                                                                                                                                                                                                                                                                                       | 16-bit                                                                                                                             | 0 & 1<br>2 & 3                                                                                                                                                                          | 0 0<br>1 0                                                                                                                                                                        |                                                                                                                                                                                         |  |  |

| D <31:0> | 1/O<br>S (L)<br>G (Z)<br>I (Z) | DATA BUS: The bus interfact thirty—two bit quantities. D (31 double word is aligned on an 8-half—word is aligned on a 2—by properly aligned, a Not Aligne In write bus cycles, the point a preceding cycle. If the preced following the cycle in which—R driven one cycle after the cycle between the processor and the when the 8—bit wide bus is us | ) corresponds –byte boundary, ed Trap will oc t which data is ing cycle was EADY was as e in which –RI e system. For sed and D[15: | s to the most s<br>ry, a word is ali<br>If a load or sto<br>ccur in the pro<br>s driven onto ti<br>a write, data<br>serted. If the p<br>EADY was ass<br>a given chip s<br>o] are used w | ignificant bit o<br>gned on a 4-b<br>re of any of the<br>ocessor.<br>ne bus depend<br>is driven in the<br>receding cycle<br>serted to minin<br>select region, p<br>when 16-bit wi | f the 32-bit word. A yte boundary, and a ese quantities is not ds on the type of the ecycle immediately e was a read, data is nize bus contention bins D[7:0] are used ide bus is used. |  |  |

| -AS      | O<br>S (L)<br>G (Z)<br>I (1)   | ADDRESS STROBE: A cont indicate the start of a new bust and ends with the assertion cycles in which neither the proand –AS remains de–asserte                                                                                                                                                                                                         | ransaction. Al<br>of -READY<br>cessornorand                                                                                        | bus transactio<br>AS remains a                                                                                                                                                          | n begins with t<br>sserted for 1                                                                                                                                                  | the assertion of –AS clock cycle. During                                                                                                                                                |  |  |

| RD/–WR   | O<br>S (L)<br>G (Z)<br>I (1)   | READ/BUS TRANSACTION read or a write operation. Witransaction is a write. With AS RD/–WR remains active for the assertion of –READY.                                                                                                                                                                                                                  | hen -AS is a<br>Sassertedand                                                                                                       | sserted and f<br>IRD/-WRhigl                                                                                                                                                            | RD/-WR is lo                                                                                                                                                                      | w, then the current ransaction is a read.                                                                                                                                               |  |  |

| SYMBOL                        | TYPE       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -READY                        | S (L)      | READY: This is a control signal asserted by the external memory system to indicate that the current bus transaction is being completed and that it is ready to start with the next bus transaction in the following cycle. In case of a fetch from memory, the processor will strobe the value on the data bus at the rising edge of CLK_IN following the assertion of —READY. For the case of a write, the memory system will assert—READY when the appropriate access time has been met.  In most cases, no additional logic is required to generate the —READY signal. On—chip circuitry can be programmed to assert—READY based on the address of the current transaction. The external system can override the internal ready generator to terminate the current bus cycle early. Up to 6 address ranges each with different transaction times can be programmed. |

| CLK_ECB                       | I          | <b>EXTERNAL CLOCK BYPASS:</b> Tying this signal high causes the CLK_IN signal to bypass the Phases Lock Loop (PLL). This signal is used for testing of the chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

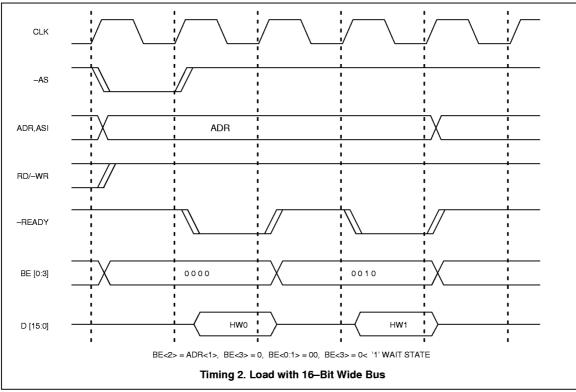

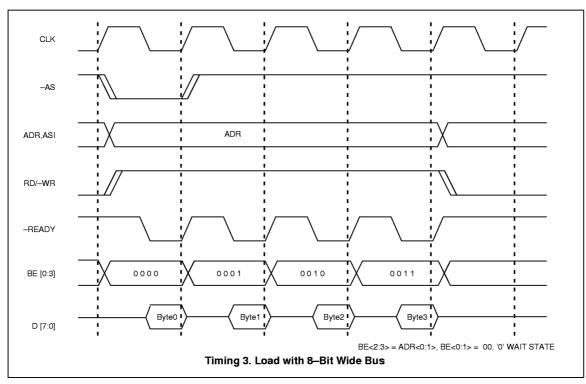

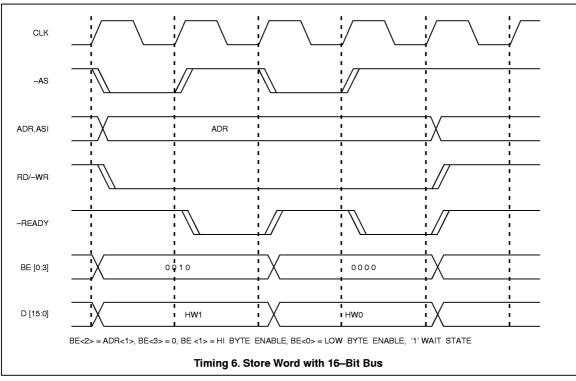

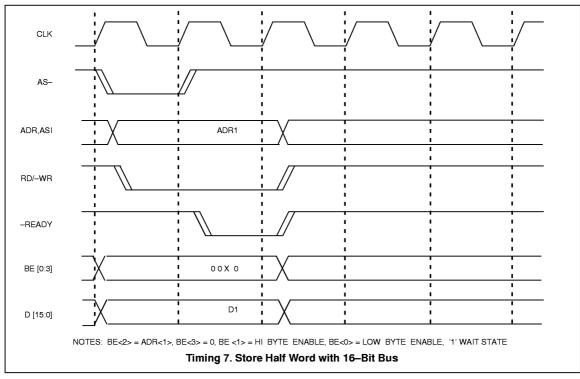

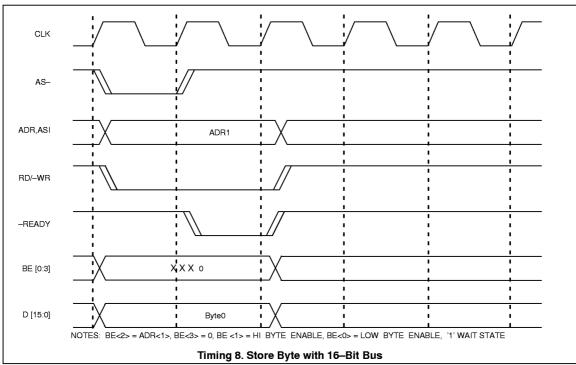

| -BMODE8                       | I<br>S (L) | <b>8–BIT BOOT MODE:</b> This signal is sampled during reset and causes read accesses memory mapped to –CS0 to assume 8–bit ROM memory. The MB86933H generates four sequential fetches to assemble a complete instruction or data word before continuing. Bytes are fetched in sequence (0,1,2,3) as encoded by –BE[2] and –BE[3] (00,01,02,03). If left unconnected, a weak pull–up on this pin (and –BMODE16 pin) causes the processor to default to 32–bit mode.                                                                                                                                                                                                                                                                                                                                                                                                     |

| -BMODE16                      | I<br>S (L) | <b>16–BIT BOOT MODE:</b> This signal is sampled during reset and causes read accesses memory mapped to –CS0 to assume 16–bit ROM memory. The MB86933H generates two sequential fetches to assemble a complete instruction or data word before continuing. Half words are fetched in sequence (0,1) as encoded by –BE[2]. If left unconnected, a weak pull–up on this pin (and –BMODE8 pin) causes the processor to default to 32–bit mode.                                                                                                                                                                                                                                                                                                                                                                                                                             |

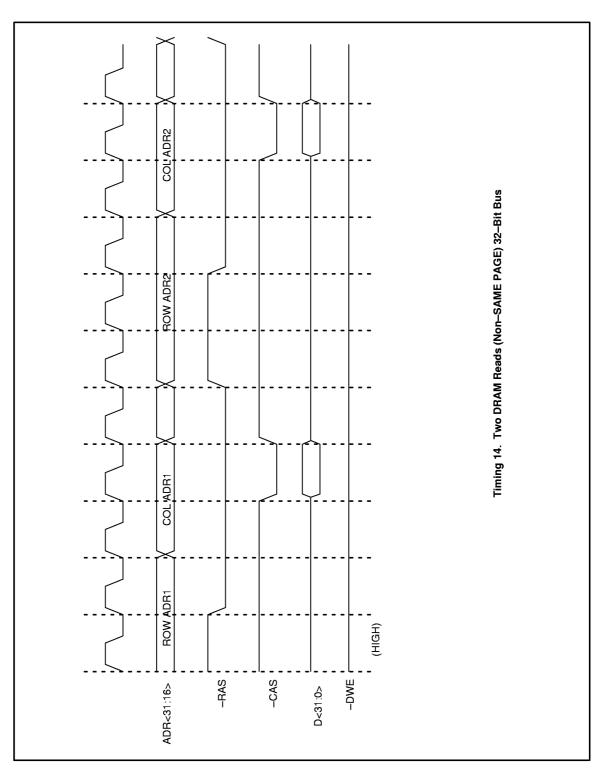

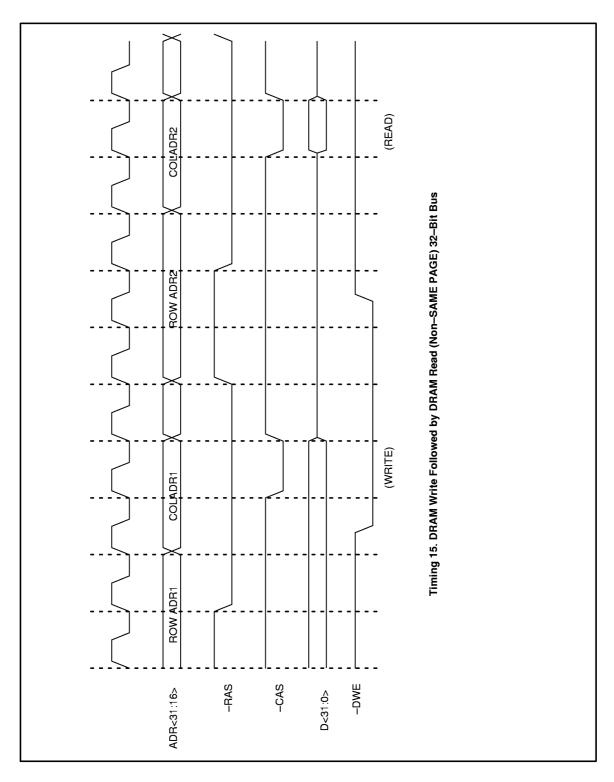

| -RAS0, -RAS1                  | 0          | <b>DRAM ROW ADDRESS STROBES:</b> The MB86933H can support up to two banks of DRAM. –RAS0 is the row address strobe for bank0. –RAS1 is the row address strobe for bank1. Note that the row address for the DRAM appears on pins ADR[27:16].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -CAS0, -CAS1,<br>-CAS2, -CAS3 | 0          | DRAM COLUMN ADDRESS STROBES: The MB86933H supports byte, half—word, and word accesses to DRAM.—CAS0 is used for accesses to byte0,—CAS1 is used for accesses to byte1,—CAS2 is used for accesses to byte2,—CAS3 is used for accesses to byte3. Note that the column address for the DRAM appears on pins ADR[27:16].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| -DWE                          | 0          | <b>DRAM WRITE ENABLE:</b> When this signal is deasserted (high) an access to DRAM is a read. When asserted (low), an access to DRAM is a write.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

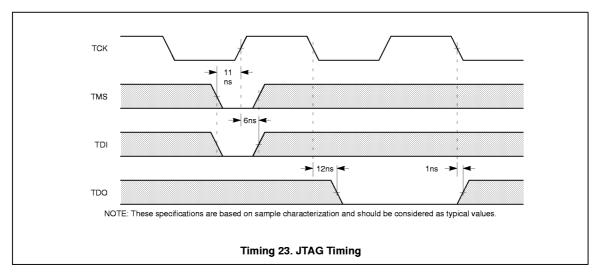

| TCK                           | I          | TEST CLOCK: JTAG compatible test clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TMS                           | I          | TEST MODE: JTAG compatible test mode select pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TDI                           | ı          | TEST DATA IN: JTAG compatible test data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TDO                           | 0          | TEST DATA OUT: JTAG compatible test data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| -TRST                         | I          | <b>TEST RESET:</b> Asynchronous reset for JTAG logic. If not using JTAG, this signal must be pulled low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

NOTE:

- I = Input Only Pin

- O = Output Only Pin

- I/O = Either Input or Output Pin

- = Pins "must be" connected as described

- A (L) =

Asynchronous: Inputs may be asynchronous to CLKOUT1.

S (L) =

Synchronous: Inputs must meet

setup and hold times relative to

CLK\_IN Outputs are Synchronous to

CLK\_IN

- G (...) = While the bus is granted to another bus master (-BGRNT=asserted), the pin is

- G (1) is driven to V<sub>CC</sub> G (0) is driven to V<sub>SS</sub> G (Z) floats G (Q) is a valid output

- I (...) = While the bus is between bus cycles (or being reset) and is not granted to another bus master, the pin is

- I (1) is driven to V<sub>CC</sub> (0) is driven to V<sub>SS</sub> (Z) floats (Q) is a valid output

#### **OVERVIEW**

The Fujitsu MB86933H is a high–performance, 32–bit RISC processor which executes at 25 MIPs peak and 22.5 MIPs sustained performance with 25 MHz clock frequency. Like its predecessors, the MB86933H is based on the SPARC V8 architecture and is upward code compatible with previous implementations. More importantly, the MB86933H has been developed specifically with the needs of embedded applications in mind and offers high performance and low cost for these applications.

The MB86933H instruction set is streamlined and hardwired for fast execution with most instructions executing in a single cycle. The Integer Unit (IU) features a 5–stage pipeline which has been designed to handle data interlocks, has an optimized branch handler for efficient control transfers, and a bus interface to handle single cycle bus accesses to on–chip memory.

#### **KEY FEATURES**

**Fast Instruction Execution:** Simple functions make up the bulk of instructions in most programs so that execution speed can be greatly improved by designing these instructions to execute in as short a time as possible. The majority of instructions execute in one cycle with only a few of the more complex, such as integer multiply, taking additional cycles.

**On-chip Instruction Cache:** To decouple the speed of the processor from the memory subsystem a 1 KByte direct mapped instruction cache is included on chip. It is possible to individually lock lines in the cache to ensure deterministic response and higher performance for critical or frequently recurring routines.

Large Register Set: The large register set (104 registers) reduces the number of required accesses to data memory. The registers are organized into six overlapping groups called register windows which allows registers to be reserved for high priority tasks, such as interrupts, or for recurring requirements such as operating system working registers. The overlapping windows also simplify parameter passing during procedure linkage and reduce code in most programs.

Hardware Multiplier: The MB86933H also includes hardware for integer multiply. The hardware support significantly improves the performance of these operations with 32–bit integer multiplies executing in 5 clock cycles, 16–bit integer multiplies in 3 cycles, 8–bit integer multiplies in 2 cycles, and a multiply by zero can complete in a single cycle.

**Interrupt Controller:** An on-chip interrupt controller is provided on the MB86933H. Four interrupt pins can

either be programmed to act as an encoded external interrupt vector providing for up to 15 interrupts or as four individual interrupt lines.

**Bus Interface:** The requirement for glue logic between the MB86933H and the system is removed by providing programmable chip selects and programmable wait—state circuitry. Each chip select region can be programmed to support either 8–bit, 16–bit, or 32–bit wide memory. Multiple bus masters are supported through a simple handshake protocol.

**Instruction Prefetch Buffer:** A one—word prefetch buffer is provided to increase performance when instruction cache misses occur.

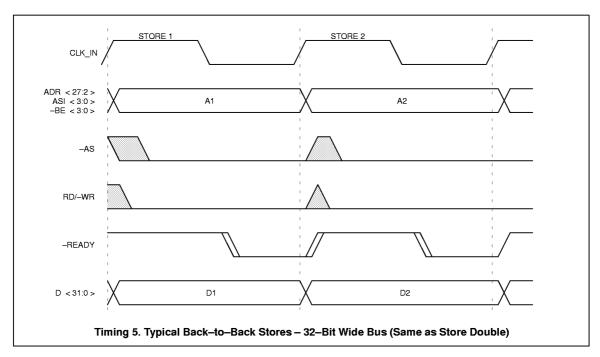

**Data Write Buffer:** A one—word write buffer is provided to decouple writes from internal instruction execution. Data can be posted to the write buffer and execution from internal cache can continue in parallel while the store completes to external memory.

**DRAM** Controller: Present on the MB86933H is a complete DRAM controller which provides glueless connection to up to two banks of DRAM memory. Support for either 16-bit or 32-bit wide DRAM memory banks is provided.

Clock Generator: To simplify the clock design a crystal can be connected directly to the on–chip oscillator or an external clock source can be used. A built–in phase–locked loop minimizes the skew between on– and off–chip clocks.

**Enhanced Instruction Set:** An integer divide—step instruction cuts divide times by a factor of 10 over previous SPARC implementations. A scan instruction supports a single cycle search for the most significant 1 or 0 in a word.

Fully Static Circuit Design: Embedded applications that need a means to reduce power consumption can take advantage of the MB86933H's fully static design. The processor clock can be slowed or stopped for arbitrary periods of time to reduce operating current with no loss of internal state. Noise immunity is improved as well. (Note: stopping the clock will result in the Phase–Locked Loop losing lock. Lock must be re–established before normal operation can be resumed.)

**Test and Debug Interface:** The MB86933H supports production test through industry standard JTAG boundary scan.

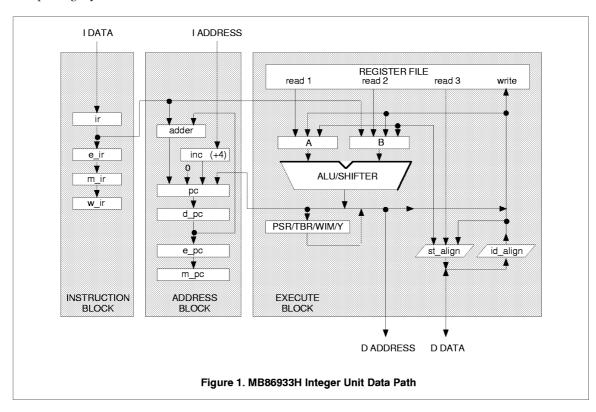

#### **CPU**

The MB86933H core is a high–performance full–custom implementation of the SPARC V8 architecture. The core is compact to leave room for peripheral integration and yet is designed in a way to allow the major blocks to be customized for varying application requirements. The core is made up of three functional units: the Instruction block, the Address block and the Execute block. (See Figure 1.)

A five–stage instruction pipeline is responsible for decoding all instructions and generating the control signals to the other blocks. The 5–stage pipeline consists of Fetch (F), Decode (D), Execute (E), Memory (M) and Writeback (W). Instruction memory is addressed and returns instructions in the (F) stage, the register file is addressed and returns operands in the (D) stage, the ALU computes results in the (E) stage, external memory is addressed in the (M) stage, and the register file is written back in the (W) stage.

#### **ADDRESS SPACE**

The MB86933H offers a large addressing range and

allows separate user and supervisor spaces to be defined. In addition to 28 address lines, 4 alternate address space identifiers (ASIs) distinguish between protected and unprotected space. Of the 16 possible ASI values, two define accesses to user data and user instruction space while the remaining ASI values define supervisor space.

Anytime a reset, synchronous trap or asynchronous trap occurs, the processor is placed into the supervisor mode. In this mode, the processor executes instructions and moves data out of supervisor space. While in supervisor mode, the processor also has access to the remaining ASI values. Except for those mentioned and those reserved for control register space, the remaining ASI values can be used to access other alternate data spaces defined by the application.

The distinction of user versus supervisor space allows the hardware to protect against accidental or un–authorized access to system resources. For real–time operating system (RTOS) development for example, the separate spaces provide a mechanism for effectively partitioning RTOS space from user space.

TABLE 1. MB86933H Instruction Set

| LOGICAL                                                                                                                                           | ARITHMETIC/SHIFT                                                                                                                                                                                                                                                         | DATA MOVEMENT                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONDITION CODES UNCHANGED  AND OR XOR AND NOT OR NOT XNOR                                                                                         | CONDITION CODES UNCHANGED ADD SUBTRACT MULTIPLY (SIGNED/UNSIGNED) SCAN SETHI SHIFT LEFT LOGICAL SHIFT RIGHT LOGICAL SHIFT RIGHT ARITHMETIC                                                                                                                               | TO USER/SUPERVISOR SPACE SIGNED LOAD BYTE LOAD HALF-WORD LOAD WORD LOAD DOUBLE WORD STORE BYTE STORE HALF-WORD STORE WORD STORE WORD STORE DOUBLE WORD                                                                                                                                                        |

| CONDITION CODES SET  AND OR XOR AND NOT OR NOT XNOR  CONTROL TRANSFER  CONDITIONAL BRANCH CONDITIONAL TRAP CALL RETURN SAVE RESTORE JUMP AND LINK | CONDITION CODES SET ADD SUBTRACT MULTIPLY (SIGNED/UNSIGNED) MULTIPLY STEP DIVIDE STEP  EXTENDED AND CONDITION CODES UNCHANGED ADD SUBTRACT EXTENDED AND CONDITION CODES SET ADD SUBTRACT TAGGED AND CONDITION CODES SET (WITH AND WITHOUT TRAP ON OVERFLOW) ADD SUBTRACT | TO USER SPACE UNSIGNED LOAD BYTE LOAD HALF-WORD  TO ALTERNATE SPACE SIGNED LOAD BYTE LOAD HALF-WORD LOAD WORD LOAD DOUBLE WORD STORE BYTE STORE HALF-WORD STORE WORD STORE DOUBLEWORD TO ALTERNATE SPACE UNSIGNED LOAD BYTE LOAD HALF-WORD  ATOMIC OPERATION IN USER SPACE SWAP WORD LOAD/STORE UNSIGNED BYTE |

|                                                                                                                                                   | NTROL REGISTER  D WIM RDASR E WIM WRASR                                                                                                                                                                                                                                  | ATOMIC OPERATION IN ALTERNATE SPACE SWAP WORD                                                                                                                                                                                                                                                                 |

|                                                                                                                                                   | AD Y                                                                                                                                                                                                                                                                     | LOAD/STORE UNSIGNED BYTE                                                                                                                                                                                                                                                                                      |

#### **REGISTERS**

The MB86933H register set is divided into those used for general—purpose functions and those used for control and status.

The 104 general—purpose registers are divided into 6 global registers and 6 overlapping blocks or "windows". Each window contains 24 registers. Of these, 8 are local to the window, 8 "out" registers overlap with the next window and 8 "in" registers overlap with the previous window. (See Figure 2.)

This organization makes it easy to pass parameters to subroutines. Parameters that are to be passed along are written to the "out" registers and the subsequent procedure call decrements the window pointer to make a new set of registers available. The passed parameters are now available to the subroutine in the current window's "in" registers.

Register windows improve performance in embedded applications because they function as local variable caches which retain either interrupt, subroutine, context or operating system variables with no additional

overhead. In addition, code can be reduced by exploiting the efficient execution of procedure linkage by preventing in–lining compiler optimizations.

The registers that make up the register file each have three read—only and one write—only port. The use of a four—port register file allows even store instructions, which may require that three operands be read out of the register file, to proceed at one instruction per cycle.

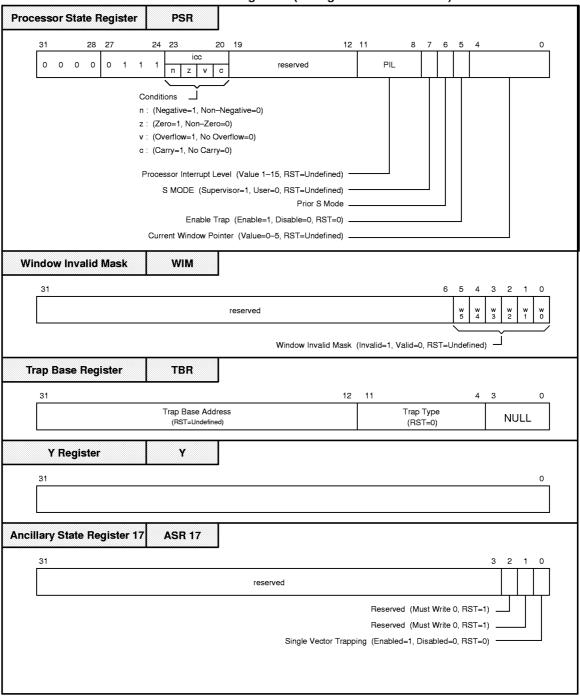

The control and status registers include those defined by the SPARC architecture (see Table 1) and those mapped into alternate address space to control peripheral functions (see Table 2).

#### **INSTRUCTION SET**

The MB86933H is upward code compatible with other SPARC V8 processors. Additional instructions, previously not directly supported, have been added to improve performance in embedded applications. Integer multiply, integer divide step, and scan for first changed bit have been added to the already powerful SPARC instruction set. See Table 1 for a list of supported instructions.

#### **INTERRUPTS**

A key measure of a processor's suitability for use in embedded application is in its ability to handle interrupts with a minimum of delay and in a deterministic fashion. The MB86933H implementation has been tailored to insure not only low average latency but low maximum latency as well.

Interrupt response time is made up of the sum of the times it takes the processor to finish its current task after recognizing an interrupt, and the time it takes to begin executing interrupt service routine instructions. The MB86933H implements numerous features to minimize both factors.

To minimize the time it takes to finish the current task, the MB86933H is designed so that tasks can either be interrupted or completed in a minimum number of cycles. Implementation details that accomplish this aim include an integer divide operation that is interruptible through the use of a divide step instruction and a fast multiply operation to minimize non–interruptible instruction execution.

To minimize the time required to start executing the interrupt service routine the processor switches to a new register window when an interrupt is detected. This feature allows the service routine to be executed without first requiring that the current registers be saved.

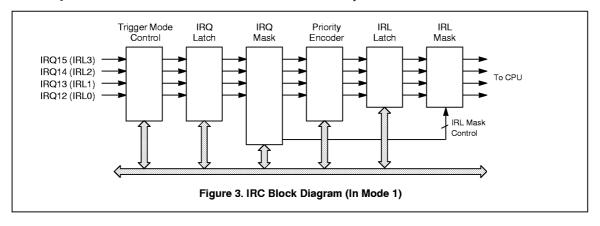

#### INTERRUPT CONTROLLER

The SPARC V8 architecture, and the MB86933H in particular, provides for up to 15 separate external interrupt sources. The MB86933H has four external

interrupt pins and an on-chip interrupt controller (IRC) which can support two modes of operation.

Mode 0 (IRL mode): In mode 0 the input on the four external pins is interpreted as an encoded interrupt vector. This mode allows for external logic to generate any one of the 15 possible interrupts ("0" represents "no interrupt request"). In this mode of operation it is assumed that the external interrupt source maintains the interrupt vector on the pins until it is explicitly cleared by writing to an external memory mapped location. Note that this mode is the same as that on the MB86930/932/933 and is compatible with the MB86940 companion chip.

Mode 1 (IRQ mode): In the mode 1 the four pins are considered to be four separate interrupt sources mapping to interrupts 12 through 15. Note this mode is the same as that on the MB86931

Figure 3 shows a block diagram of the IRC in mode 1.

The Trigger Mode Control logic selects one of four trigger modes for each of the four channels: high level, low level, rising edge, or falling edge. The processor controls the triggers by writing to the Trigger Mode register.

The IRQ latch captures each of the four interrupt requests. The system processor reads the latch via the Request Sense register and clears the latch by writing to the Request Clear register. The example assembly language program below shows the code sequence for writing to the Request Clear register of channel 12.

The IRQ Mask logic allows selective masking of the interrupts. The processor controls masking by writing to the Mask register.

```

! define Request Clear Register #define rqc 0x20c

! define a valid memory location #define rqs_loc 0x1000

! define control register ASI address space #define casi 0x1

...

! Request Clear;

set rqc, %10

set 0x1000, %17

set rqs_loc, %16 !memory location defined in main prog %g0, [%16]

sta %17, [%10] casi !write to Request Clear register

...

...

```

A write to Request Clear register must be preceded by the store of 0x0 to any valid memory location to prevent the previous high value bits on the data bus from unintentionally setting other bits of the Clear Request register.

The Priority Encoder prioritizes the interrupt requests and encodes the highest priority pending interrupt that is not masked. pin IRL3 maps to interrupt 15, IRL2 maps to interrupt 14, IRL1 maps to interrupt 13 and IRL0 maps to interrupt 12.

The IRL latch captures the encoded interrupt level number that is generated by the priority encod-

er.

**INSTRUCTION CACHE**

The MB86933H has an on-chip, 1KByte, direct-mapped, sectored instruction cache. The line length of the cache is 16 bytes. Lines are subdivided into four sub-blocks, each four bytes wide. On a cache miss, the cache is updated in sub-block increments. Also, on a

cache miss the instruction prefetch buffer fetches the next sequential anticipating that it will be needed to fill then next instruction cache miss.

The cache can be used in either normal mode or one of two lock modes.

Global locking allows the entire content of the instruction cache to be frozen. A bit in the cache control register enables or disables global locking.

Local locking makes it possible to dynamically lock selected instructions on a line—by—line basis. This feature gives the flexibility, for example, to assure deterministic response for certain critical routines by locking the routine's code into the cache while still allowing other locations to be used as a cache. Note, however, that because the cache is direct—mapped, code which would normally map into the locked cache locations will not be cached.

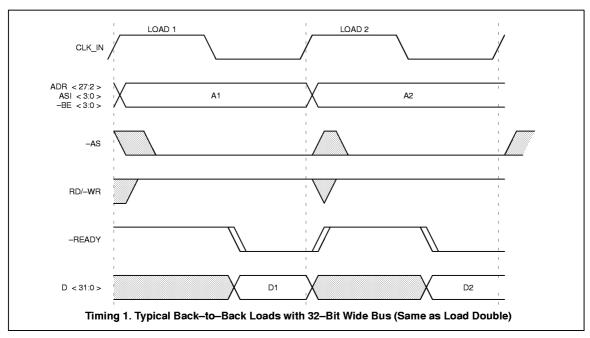

#### **BUS INTERFACE**

The Bus Interface Unit (BIU) is designed to simplify the interface between the MB86933H and the rest of the system. Separate address and data buses make de–multiplexing unnecessary. Simple control signals make it easy to build fast systems.

The BIU includes two features to increase performance when accessing external memory — an instruction prefetch buffer to support efficient instruction fetches and a write buffer to support data writes.

A key measure of a processor's suitability for use in embedded application is in its ability to handle interrupts with a minimum of delay and in a deterministic fashion. The MB86933H implementation has been tailored to insure not only low average latency but low maximum latency as well.

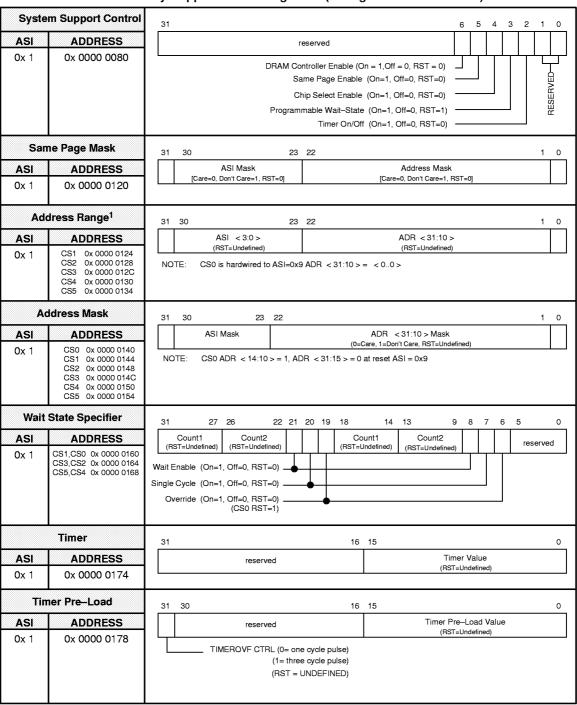

The BIU also includes circuitry to enable the design of complex systems with a minimum requirement for external glue logic. The bus interface unit supports up to six regions of memory – each region with independently programmable wait–state generation, chip select generation, and programmable bus widths. This allows for the support of multiple width memories within a single system. There is also included a complete DRAM controller for glueless connection to DRAM.

#### Prefetch Buffer

Associated with the instruction cache and the BIU is a one—word prefetch buffer. After an instruction fetch which misses in the cache has been satisfied, the prefetch buffer willimmediately initiate another instruction access to the next sequential address. Instructions are prefetched only when the BIU does not have another pending request for a bus transaction (eg. a write to memory).

#### Write Buffer

Also associated with the BIU is a one—word write buffer. For stores this buffer effectively hides the external memory latency. When a store occurs the data is posted to the write buffer. The IU can then continue to execute from internal cache while the write buffer completes the store to external memory.

# Chip Selects

As on the other 930 Series chips, there are six chip selects. Each chip select can be associated with a region of memory and will determine the characteristics for that region. Associated with each chip select is a wait state generator which can be set to internally terminate an external memory access after a preprogrammed number of cycles. Also associated with each chip select (except chip select 0) are control bits which determine the external bus width. The bus width for each memory region can be set to 8-bit, 16-bit or 32-bit.

Chip select 0 is dedicated for boot code. It can be programmed to be 8-bit, 16-bit, or 32-bit wide based on two external pins: BMODE8\_ and BMODE16\_. When the DRAM controller is used, chip select 4 is dedicated for the DRAM controller support. It should be noted that while on previous 930 Series family members the "samepage" circuitry could be associated with any chip select, on the MB86933H "samepage" is specifically associated with chip select 4.

Byte, halfword, and word operations are supported on all bus widths (8–, 16–, and 32–bit). It should be noted that all loads (byte, halfword, word) return a total of 32 bits (possibly with multiple accesses) regardless of the width of the bus. This is done to be compatible with other 930

Series family member where the minimum granularity of the on-chip data cache is one word.

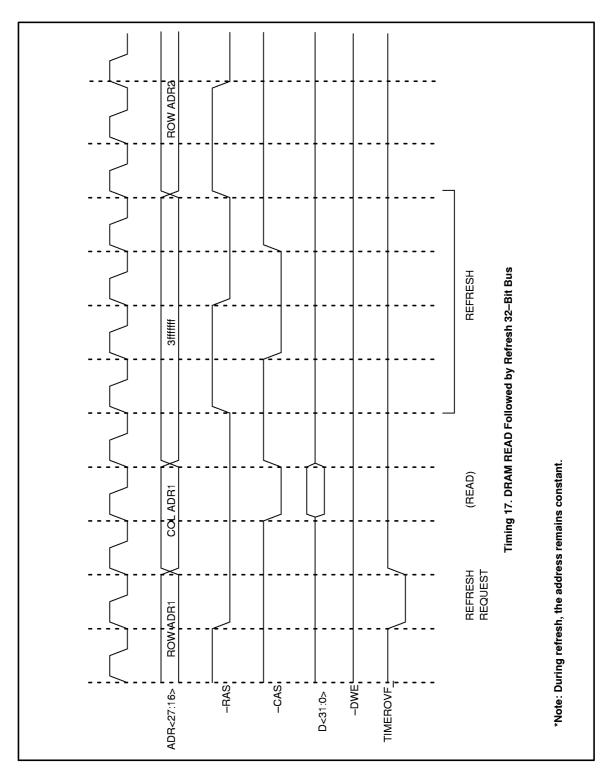

#### DRAM Controller

The MB86933H provides all the necessary logic to directly connect up to 16 MB of fast page-mode DRAM without external glue logic (or 128 MB with external buffers). Address multiplexing is performed internally and the DRAM row and column addresses (MA<11:0>) are output on the ADR<27:16> pins. Two -RAS lines allow access to up to two banks of memory. Each -RAS signal controls a bank of memory. Each bank is configurable in both depth and width. The width can be programmed to be either 32-bit wide or, for low cost systems, 16-bit wide. Four -CAS signals allow for byte, halfword, and word stores to memory. Each -CAS signal controls a byte in a 32 bit word. -CAS0 controls accesses to byte 0, etc. Internal "samepage" detect logic is provided to allow for a minimum 2-cycle samepage access to the DRAM. An internal refresh timer is used to generate a -CAS before -RAS refresh cycles automatically at programmable intervals. The -DWE (DRAM Write Enable) pins determines whether a read or write access is being made to DRAM.

DRAM configurations supported by the MB86933H:

| DRAM Size | (RAS bits x CAS bits) |

|-----------|-----------------------|

| 256Kxn    | (9x9)                 |

| 512Kxn    | (10x9)                |

| 1Mxn      | (10x10)               |

| 2Mxn      | (11x10)               |

| 2Mxn      | (12x9)                |

| 4Mxn      | (11x11)               |

| 4Mxn      | (12x10)               |

| 16Mxn     | (12x12)               |

where n = 1, 4, 8, 16

#### **CLOCK GENERATOR**

The on-chip clock generator provides a means to directly connect the MB86933H to either a crystal oscillator or an external clock source. For either case, the external frequency is the same as the chip operating frequency.

A clock output signal provides the system with a reference by which external timing can be synchronized when not using an external clock source. The skew between the internal clock and an external input clock source is minimized by the inclusion of an on—chip phase lock loop circuit.

TABLE 1. MB86933H Control and Status Registers (All registers are read/write)

TABLE 2. MB86933H Memory Mapped Control Registers (All registers are read/write)

<sup>1.</sup> This register is Write Only

TABLE 2. MB86933H Memory Mapped Control Registers (All registers are read/write) (Continued)

|                    | Bus Width                                    | 31                                                           |                          |       | 1        | 2 11  | 10               | 9 8             | 7 6                                              | 5 4                                      | 3 2        | 1 0  | _ |

|--------------------|----------------------------------------------|--------------------------------------------------------------|--------------------------|-------|----------|-------|------------------|-----------------|--------------------------------------------------|------------------------------------------|------------|------|---|

| ASI                | ADDRESS                                      |                                                              | reserved                 |       |          | C     | S5               | CS4             | CS3                                              | CS2                                      | CS1        | RSVD |   |

| 0x 1               | 0x 0000 016C                                 | BUS WIDTH FOR DIF<br>NOTE THAT CS0 IS I<br>PINS, BMODE16 AND | PROGRAMMED (<br>D BMODE8 | JSING |          | 0)    | 1<br>1<br>0<br>0 | 1 0 1 0 0       | RE<br>16<br>8–                                   | S WIDTH ESERVED BIT BUS BIT BUS* BIT BUS |            |      | J |

| Tr                 | igger Mode 0                                 | 31                                                           | 16 15 14                 | 13    | 12       | 11    | 10               | 9               | 8                                                | 7                                        |            | 0    |   |

| <b>ASI</b> 0x 1    | ADDRESS<br>0x 0000 0200                      | reserved                                                     | MD15                     |       | )14      |       | D13              | MD1             |                                                  |                                          | erved      |      |   |

| Re                 | quest Sense <sup>2</sup>                     | 31                                                           | 16                       | 15    | 14       | 13    | 12               | 11              |                                                  |                                          |            | 0    |   |

| <b>ASI</b> 0x 1    | <b>ADDRESS</b> 0x 0000 0208                  | reser                                                        |                          |       |          |       |                  |                 |                                                  | reserve                                  | d          |      |   |

| Re                 | equest Clear <sup>1</sup>                    | 31                                                           | 16                       | 15    | 14       | 13    | 12               | 11              |                                                  |                                          |            | 0    |   |

| <b>ASI</b> 0x 1    | ADDRESS<br>0x 0000 020C                      | reser                                                        |                          |       |          |       |                  |                 |                                                  | reserve                                  | d          | -    |   |

|                    |                                              |                                                              |                          |       | (1 =     | clear | )                |                 |                                                  |                                          |            |      |   |

|                    | Mask                                         | 31                                                           | 16                       | 15    | 14       | 13    | 12               | 11              |                                                  |                                          |            | 1 0  |   |