# VT6306 PCI 1394a Integrated **Host Controller**

1394a OHCI Link Layer Controller with Integrated 400 Mbit 3-Port PHY for the PCI Bus

Revision 1.16

July 19, 2002

VIA TECHNOLOGIES, INC.

## **Copyright Notice:**

Copyright © 2000, 2001, 2002 VIA Technologies Incorporated. Printed in the United States. ALL RIGHTS RESERVED.

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise without the prior written permission of VIA Technologies Incorporated.

VT6304, VT6305, and VT6306 may only be used to identify a product of VIA Technologies, Inc.

is a registered trademark of VIA Technologies, Incorporated.

Windows 98<sup>TM</sup>, Windows NT<sup>TM</sup>, Windows 2000<sup>TM</sup>, and Plug and Play<sup>TM</sup> are registered trademarks of Microsoft Corp. PCI<sup>TM</sup> is a registered trademark of the PCI Special Interest Group.

All trademarks are the properties of their respective owners.

## **Disclaimer Notice:**

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies. VIA Technologies makes no warranties, implied or otherwise, in regard to this document and to the products described in this document. The information provided by this document is believed to be accurate and reliable to the publication date of this document. However, VIA Technologies assumes no responsibility for any errors in this document. Furthermore, VIA Technologies assumes no responsibility for the use or misuse of the information in this document and for any patent infringements that may arise from the use of this document. The information and product specifications within this document are subject to change at any time, without notice and without obligation to notify any person of such change.

## Offices:

**USA Office:** 940 Mission Court Fremont, CA 94539 USA

Tel: (510) 683-3300

Fax: (510) 683-3301 or (510) 687-4654 Home Page: <u>http://www.viatech.com</u> Taipei Office:

8<sup>th</sup> Floor, No. 533 Chung-Cheng Road, Hsin-Tien Taipei, Taiwan ROC

Tel: (886-2) 2218-5452 Fax: (886-2) 2218-5453 Home Page: http://www.via.com.tw

## **REVISION HISTORY**

| Document Release | Date     | Revision                                                                         | Initials |  |  |  |  |  |

|------------------|----------|----------------------------------------------------------------------------------|----------|--|--|--|--|--|

| 1.0              | 11/1/00  | Initial public release (no technical changes from internal 8/29/00 revision 0.4) |          |  |  |  |  |  |

| 1.11             | 10/30/01 | Updated Application Schematics Diagram from VT5350C to VT5471B                   | AT       |  |  |  |  |  |

|                  |          | Fixed cross reference links and Functional Description heading levels            | / DH     |  |  |  |  |  |

|                  |          | Fixed formatting of revision number cross reference in page footer               |          |  |  |  |  |  |

| 1.12             | 06/19/02 | Updated Cover logo, Header logo, Format, Copyright and Address                   | BL       |  |  |  |  |  |

|                  |          | Information                                                                      |          |  |  |  |  |  |

|                  |          | Added Watermark                                                                  |          |  |  |  |  |  |

|                  |          | Fixed information                                                                |          |  |  |  |  |  |

| 1.13             | 06/20/02 | Updated electrical specification on page 49 and removed watermark                | BL       |  |  |  |  |  |

| 1.14             | 07/18/02 | Updated Power and Ground table of Pin Description on page 12                     | BL       |  |  |  |  |  |

| 1.15             | 07/18/02 | Modified table of Power and Ground on page 12                                    | BL       |  |  |  |  |  |

| 1.16             | 07/18/02 | Edited Power and Ground table of Pin Description into Digital Power, Analog      |          |  |  |  |  |  |

|                  |          | Power and Ground tables.                                                         |          |  |  |  |  |  |

|                  |          | Deleted Power column in Digital Power, Analog Power and Ground tables on         |          |  |  |  |  |  |

|                  |          | page 11 and 12 and added I/O columns.                                            |          |  |  |  |  |  |

## TABLE OF CONTENTS

| REVISION HISTORY                                           | ]  |

|------------------------------------------------------------|----|

| TABLE OF CONTENTS                                          | II |

| LIST OF FIGURES AND TABLES                                 | IV |

| OVERVIEW                                                   | 3  |

| PINOUTS                                                    | 5  |

| PIN DIAGRAM                                                | 5  |

| PIN LIST                                                   | 6  |

| PIN DESCRIPTIONS                                           | 7  |

| REGISTERS                                                  | 12 |

| REGISTER OVERVIEW                                          | 12 |

| PCI Function 0 Registers - Link Controller                 |    |

| Memory-Space Registers – Link Controller                   |    |

| PHY Registers                                              |    |

| REGISTER DESCRIPTIONS                                      |    |

| Link Controller Configuration Registers (PCI Function 0)   |    |

| Configuration Space Header                                 |    |

| Controller-Specific Configuration Registers.               |    |

| Power Management Registers                                 |    |

| Link Controller Memory-Space Registers                     |    |

| Autonomous CSR Resources                                   |    |

| Bus Management CSR Registers                               |    |

| HC Control Registers                                       |    |

| Self-ID Control Registers                                  |    |

| Channel Mask Registers                                     |    |

| Interrupt Registers                                        |    |

| Link Control Registers                                     |    |

| PHY Control Registers                                      | 28 |

| Cycle Timer Registers                                      |    |

| Filter Registers                                           |    |

| Asynchronous Transmit & Receive Context Registers          |    |

| Isochronous Transmit Context Registers                     | 32 |

| PHY Registers                                              |    |

| PHY Register Overview                                      |    |

| PHY Register Overview  PHY Register Bit Field Descriptions |    |

| PHY Register Page 0 - Port Status.                         |    |

| PHY Register Page 1 - Vendor Identification                |    |

| PHY Register Page 7 - Vendor-Dependent                     |    |

| FUNCTIONAL DESCRIPTIONS                                    | 38 |

| PHY GENERAL DESCRIPTION                                    | 38 |

| Cable Interface                                            | 38 |

| PHY CIRCUIT DESCRIPTION                                    |    |

| Pinless PLL and Clock Generation                           |    |

| Power Down and Auto Power Save                             | 39 |

| Pinless PHY RESET                                          | 39 |

| Data Transmission                                          | 39 |

| Data Reception                                     | 39 |

|----------------------------------------------------|----|

| TPBIAS                                             |    |

| Bias-Detector / Connect-Detector / Bias-Discharger |    |

| Twisted-Pair TPA and TPB                           |    |

| Bandgap Current Generation                         |    |

| Power Off                                          |    |

| Unimplemented Ports                                |    |

| CMC, PC0, PC1, PC2 Strapping                       |    |

| Support to PHY Packet                              |    |

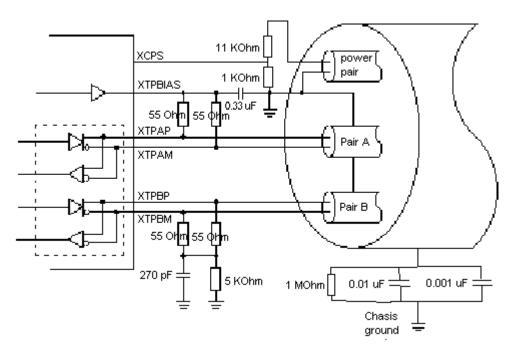

| Self-ID Packet                                     |    |

| Link-On Packet                                     | 41 |

| PHY-Configuration Packet                           | 42 |

| Ping Packet                                        | 42 |

| Remote Access and Reply Packets                    |    |

| Remote Command and Confirmation Packet             |    |

| Resume Packet                                      | 45 |

| APPLICATION SCHEMATICS                             | 46 |

| ELECTRICAL SPECIFICATIONS                          | 50 |

| ABSOLUTE MAXIMUM RATINGS                           | 50 |

| DC CHARACTERISTICS                                 | 50 |

| POWER CHARACTERISTICS                              | 50 |

| RECOMMENDED OPERATING CONDITIONS - PHY             | 51 |

| ANALOG SIGNAL CHARACTERISTICS                      | 52 |

| TPA/TPB Driver Characteristics                     | 52 |

| TPA/TPB Receiver Characteristics                   |    |

| PHY Characteristics                                |    |

|                                                    |    |

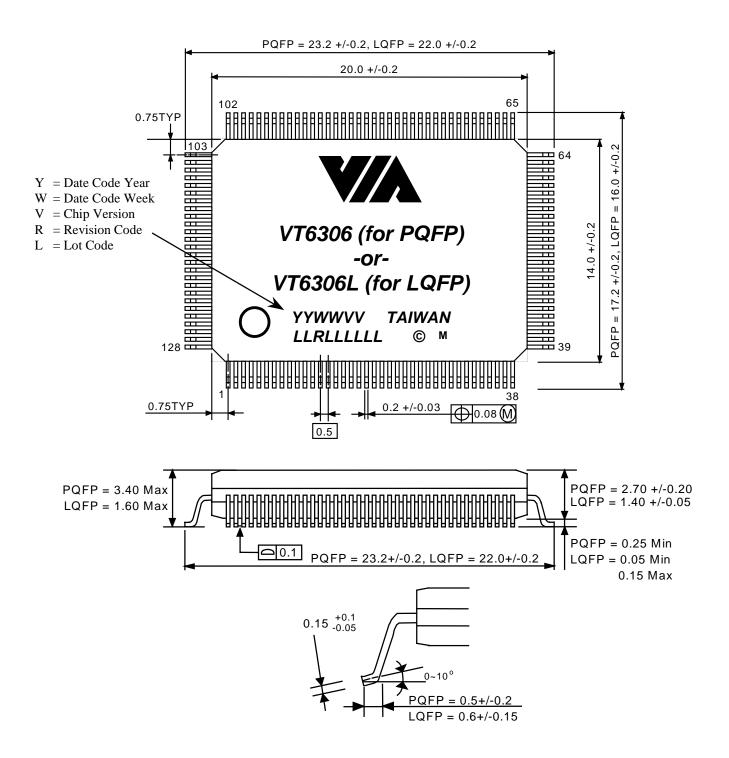

| PACKAGE MECHANICAL SPECIFICATIONS                  | 53 |

## LIST OF FIGURES AND TABLES

| FIGURE 1. VT6306 CHIP BLOCK DIAGRAM                                | 3          |

|--------------------------------------------------------------------|------------|

| FIGURE 2. VT6306 INTERNAL PHY BLOCK DIAGRAM                        |            |

| FIGURE 3. VT6306 PIN DIAGRAM (TOP VIEW)                            | 5          |

| FIGURE 4. VT6306 PIN LIST (ALPHABETICAL ORDER)                     | 6          |

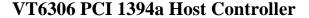

| FIGURE 5. CABLE INTERFACE                                          | 38         |

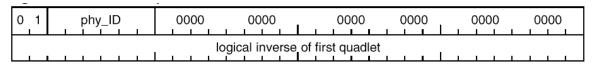

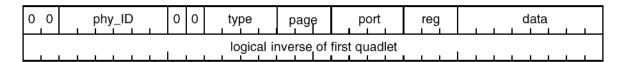

| FIGURE 6. SELF-ID PACKET FORMAT                                    | 41         |

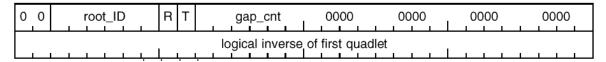

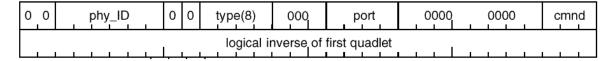

| FIGURE 7. LINK_ON PACKET FORMAT                                    | <b>4</b> 1 |

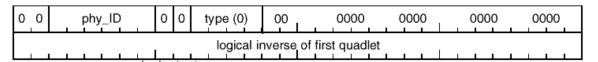

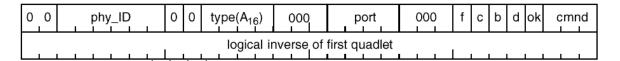

| FIGURE 8. CONFIGURATION PACKET FORMAT                              | 42         |

| FIGURE 9. PING PACKET FORMAT                                       |            |

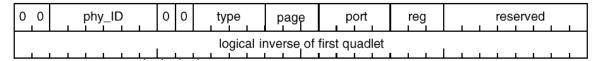

| FIGURE 10. REMOTE ACCESS PACKET FORMAT                             | 43         |

| FIGURE 11. REMOTE REPLY PACKET FORMAT                              | 43         |

| FIGURE 12. REMOTE COMMAND PACKETS FORMAT                           | 4          |

| FIGURE 13. REMOTE CONFIRMATION PACKETS FORMAT                      | 4          |

| FIGURE 14. RESUME PACKET FORMAT                                    |            |

| FIGURE 15. MECHANICAL SPECIFICATIONS – 128 PIN PQFP / LQFP PACKAGE | 53         |

|                                                                    |            |

| TABLE 1. PIN DESCRIPTIONS                                          | 7          |

| TABLE 2. REGISTERS                                                 | 12         |

| TABLE 3. PHY REGISTER MAP                                          |            |

| TABLE 4. PACKET EVENT CODES                                        | 31         |

| TABLE 5. PHY REGISTER PAGE 0 BIT FIELD DESCRIPTIONS                | 36         |

| TABLE 6. PHY REGISTER PAGE 1 BIT FIELD DESCRIPTIONS                |            |

| TABLE 7. POWER CLASS PIN STRAPPING                                 |            |

| TABLE 8. SELF ID PACKET FIELDS                                     |            |

| TABLE 9. PHY CONFIGURATION PACKET FIELDS                           |            |

| TABLE 10. REMOTE ACCESS AND REMOTE REPLY PACKET FIELDS             |            |

| TABLE 11. REMOTE COMMAND AND CONFIRMATION PACKET FIELDS            | 4          |

| TABLE 12. RESUME PACKET FIELDS                                     | 45         |

## VT6306 PCI 1394a Integrated Host Controller

## 1394A OHCI HOST CONTROLLER WITH INTEGRATED 3-PORT 400 MBIT PHY FOR THE PCI BUS

- Single Chip PCI Host Controller for IEEE 1394-1995 and IEEE 1394a Draft 4.0

- Embedded 1394 Link Core

- 32 bit CRC generator and checker for receive and transmit data

- On-chip isochronous and asynchronous receive and transmit FIFOs for packets (2K for general receive plus 2K for isochronous transmit plus 2K for asynchronous transmit)

- 8 isochronous transmit / receive contexts

- 3-deep physical post-write queue

- 2-deep physical response queue

- Dual buffer mode enhancements

- Skip Processing enhancements

- Block Read Request handling

- Ack\_tardy processing

### OHCI Compliant Programming Interface

- Compliant with 1394 Open HCI Specifications v1.0 and v1.1

- Descriptor based isochronous and asynchronous DMA channels for receive / transmit packets

### • 32-Bit Power-Managed PCI Bus Interface

- Compliant with PCI specification v2.2

- High-performance bus mastering support

- Byte alignment to run in little-endian (x86/PCI) environment

- Compliant with PCI Bus Power Management Specification v1.1

- Supports power states D0, D1, D2, D3hot, and D3cold

- Supports CardBus interface

- Supports I2C EEPROM and 4-Wire Serial ROM with GUID PROM Shadow to EEPROM

-1-

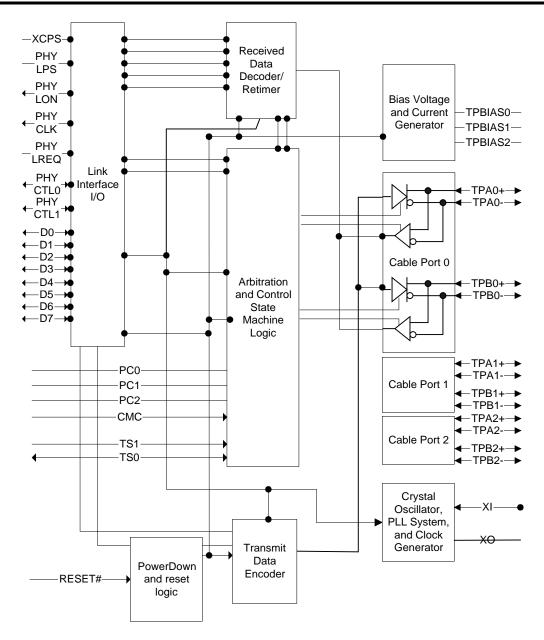

### Integrated 400 Mbit 3-Port PHY

- Supports provisions of IEEE 1394-1995 Standard for High Performance Serial Bus and the P1394a Supplement 4.0.

- Fully interoperable with IEEE Std 1394-1995 devices

- Full P1394a Supplement Support includes:

- Arbitrated short reset,

- Enhanced priority arbitration,

- Connection debounce,

- Multispeed packet concatenation,

- Ack accelerated arbitration,

- Fly-by concatenation,

- Per port disable, suspend, resume, through register write and remote command packet,

- Remote access packet

- Boundary node short reset

- No phy\_ID wrap past 63

- Provides three 1394a fully compliant cable ports at 100/200/400 Mbit per second

- Host notification of PHY LinkOn events

- Logic performs bus initialization and arbitration functions

- Encode and decode functions included for data-strobe bit-level encoding

- Incoming data resynchronized to local clock.

- 24.576 MHz crystal oscillator and PLL provide TX/RX data at 100/200/400 Mbps and Link-Layer Controller clock at 49.152 MHz.

- Cable power presence monitoring.

- Programmable node power class information for system power management

- Fully Compliant P1394a 4.0 PHY register map

- Separate TPBIAS for each port

- Cable ports monitor line conditions for active connection to remote node

- Automatic power down inactive circuit and logic for low power application

- Self power up reset and pinless PLL to reduce passive component counts on system

- Automatic configuration to single-port, two-port, and three-port applications; unused ports power down automatically

- Dedicated power supply pins separate from link core

- 2KV ESD protection

### • 3.3V Power Supply with 5V Tolerant Inputs

- 0.35um, Low Power CMOS Process

- 128-Pin PQFP Package (VT6306) and 128-Pin LQFP Package (VT6306L) Available

- PCB Reference Designs & Schematics Available

## **OVERVIEW**

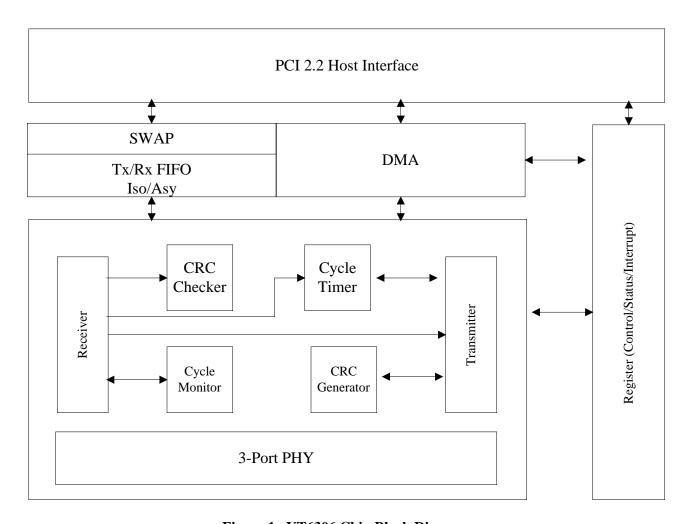

The VT6306 IEEE 1394 OHCI Host Controller provides high performance serial connectivity. It implements the Link and Phy layers for IEEE 1394-1995 High Performance Serial Bus and 1394a Draft 4.0. It is compliant with 1394 Open HCI 1.0 and 1.1 with DMA engine support for high performance data transfer via a 32-bit bus master PCI host bus interface.

The VT6306 supports 100, 200 and 400 Mbit/sec transmission via an integrated 3-port PHY. The VT6306 services two types of data packets: asynchronous and isochronous (real time). The 1394 link core performs arbitration requesting, packet generation and checking, and bus cycle master operations. It also has root node capability and performs retry operations.

The VT6306 is ready to provide industry-standard IEEE 1394 peripheral connections for desktop and mobile PC platforms. Support for the VT6306 is built into Microsoft Windows 98, Windows ME, and Windows 2000.

Figure 1. VT6306 Chip Block Diagram

Figure 2. VT6306 Internal PHY Block Diagram

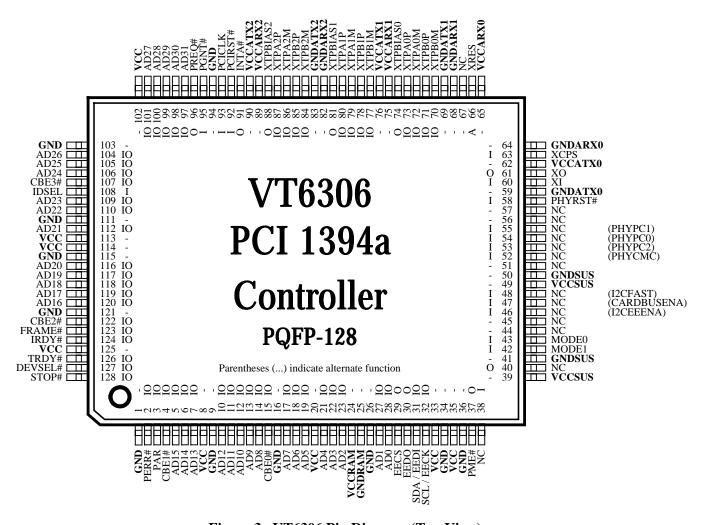

## **PINOUTS**

### Pin Diagram

Figure 3. VT6306 Pin Diagram (Top View)

## Pin List

Figure 4. VT6306 Pin List (Alphabetical Order)

| Pin |    | Pin Name | Pin | Pin Pin Name |                     | Pin |    | Pin Name | Pin |    | Pin Name |

|-----|----|----------|-----|--------------|---------------------|-----|----|----------|-----|----|----------|

| 28  | IO | AD00     | 47  | I            | CARDBUSENA          | 48  | I  | I2CFAST  | 102 | P  | VCC      |

| 27  | IO | AD01     | 15  | IO           | CBE0#               | 108 | I  | IDSEL    | 113 | P  | VCC      |

| 23  | IO | AD02     | 4   | IO           | CBE1#               | 91  | О  | INTA#    | 114 | P  | VCC      |

| 22  | IO | AD03     | 122 | IO           | CBE2#               | 124 | IO | IRDY#    | 125 | P  | VCC      |

| 21  | IO | AD04     | 107 | IO           | CBE3#               | 43  | I  | MODE0    | 65  | P  | VCCARX0  |

| 19  | IO | AD05     | 127 | IO           | DEVSEL#             | 42  | I  | MODE1    | 75  | P  | VCCARX1  |

| 18  | IO | AD06     | 32  | IO           | EECK / SCL / EEFAST | 38  | -  | NC       | 89  | P  | VCCARX2  |

| 17  | IO | AD07     | 29  | O            | EECS / EEAUTO#      | 40  | -  | NC       | 62  | P  | VCCATX0  |

| 14  | IO | AD08     | 31  | IO           | EEDI / SDA          | 44  | -  | NC       | 76  | P  | VCCATX1  |

| 13  | IO | AD09     | 30  | О            | EEDO                | 45  | -  | NC       | 90  | P  | VCCATX2  |

| 12  | IO | AD10     | 123 | IO           | FRAME#              | 51  | -  | NC       | 24  | P  | VCCRAM   |

| 11  | IO | AD11     | 1   | P            | GND                 | 56  | -  | NC       | 39  | P  | VCCSUS   |

| 10  | IO | AD12     | 9   | P            | GND                 | 57  | -  | NC       | 49  | P  | VCCSUS   |

| 7   | IO | AD13     | 16  | P            | GND                 | 67  | -  | NC       | 63  | I  | XCPS     |

| 6   | IO | AD14     | 26  | P            | GND                 | 3   | IO | PAR      | 60  | I  | XI       |

| 5   | IO | AD15     | 34  | P            | GND                 | 93  | I  | PCICLK   | 61  | 0  | XO       |

| 120 | IO | AD16     | 36  | P            | GND                 | 92  | I  | PCIRST#  | 66  | A  | XRES     |

| 119 | IO | AD17     | 94  | P            | GND                 | 2   | О  | PERR#    | 72  | IO | XTPA0M   |

| 118 | IO | AD18     | 103 | P            | GND                 | 95  | I  | PGNT#    | 73  | IO | XTPA0P   |

| 117 | IO | AD19     | 111 | P            | GND                 | 52  | I  | PHYCMC   | 79  | IO | XTPA1M   |

| 116 | IO | AD20     | 115 | P            | GND                 | 54  | I  | PHYPC0   | 80  | IO | XTPA1P   |

| 112 | IO | AD21     | 121 | P            | GND                 | 55  | I  | PHYPC1   | 86  | IO | XTPA2M   |

| 110 | IO | AD22     | 64  | P            | GNDARX0             | 53  | I  | PHYPC2   | 87  | IO | XTPA2P   |

| 109 | IO | AD23     | 68  | P            | GNDARX1             | 58  | I  | PHYRST#  | 70  | IO | XTPB0M   |

| 106 | IO | AD24     | 82  | P            | GNDARX2             | 37  | О  | PME#     | 71  | IO | XTPB0P   |

| 105 | IO | AD25     | 59  | P            | GNDATX0             | 96  | О  | PREQ#    | 77  | IO | XTPB1M   |

| 104 | IO | AD26     | 69  | P            | GNDATX1             | 128 | Ю  | STOP#    | 78  | IO | XTPB1P   |

| 101 | IO | AD27     | 83  | P            | GNDATX2             | 126 | IO | TRDY#    | 84  | IO | XTPB2M   |

| 100 | IO | AD28     | 25  | P            | GNDRAM              | 8   | P  | VCC      | 85  | IO | XTPB2P   |

| 99  | IO | AD29     | 41  | P            | GNDSUS              | 20  | P  | VCC      | 74  | О  | XTPBIAS0 |

| 98  | IO | AD30     | 50  | P            | GNDSUS              | 33  | P  | VCC      | 81  | О  | XTPBIAS1 |

| 97  | Ю  | AD31     | 46  | I            | 12CEEENA            | 35  | P  | VCC      | 88  | О  | XTPBIAS2 |

## **Pin Descriptions**

**Table 1. Pin Descriptions**

|             | PCI Bus Interface                                                                   |     |                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Signal Name | Pin#                                                                                | I/O | Signal Description                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| AD[31:0]    | 97-101, 104-106,<br>109-110, 112,<br>116-120, 5-7,<br>10-14, 17-19,<br>21-23, 27-28 | IO  | Address / Data Bus. The standard PCI address and data lines. The address is driven with FRAME# assertion and data is driven or received in following cycles.                                                                                                                               |  |  |  |  |  |  |

| CBE[3:0]#   | 107, 122, 4, 15                                                                     | IO  | <b>Command / Byte Enable.</b> The command is driven with FRAME# assertion. Byte enables corresponding to supplied or requested data are driven on following clocks.                                                                                                                        |  |  |  |  |  |  |

| FRAME#      | 123                                                                                 | Ю   | <b>Frame.</b> Assertion indicates the address phase of a PCI transfer. Negation indicates that one more data transfer is desired by the cycle initiator.                                                                                                                                   |  |  |  |  |  |  |

| DEVSEL#     | 127                                                                                 | Ю   | <b>Device Select.</b> As an output, this signal is asserted to claim PCI transactions through positive or subtractive decoding. As an input, DEVSEL# indicates the response to a VT6306-initiated transaction and is also sampled when decoding whether to subtractively decode the cycle. |  |  |  |  |  |  |

| TRDY#       | 126                                                                                 | IO  | <b>Target Ready.</b> Asserted when the target is ready for data transfer.                                                                                                                                                                                                                  |  |  |  |  |  |  |

| IRDY#       | 124                                                                                 | IO  | <b>Initiator Ready.</b> Asserted when the initiator is ready for data transfer.                                                                                                                                                                                                            |  |  |  |  |  |  |

| PREQ#       | 96                                                                                  | О   | <b>PCI Bus Request.</b> Asserted by the bus master to indicate to the bus arbiter that it wants to use the bus.                                                                                                                                                                            |  |  |  |  |  |  |

| PGNT#       | 95                                                                                  | I   | <b>PCI Bus Grant.</b> Asserted to indicate that access to the bus is granted.                                                                                                                                                                                                              |  |  |  |  |  |  |

| IDSEL       | 108                                                                                 | I   | <b>Initialization Device Select.</b> IDSEL is used as a chip select during configuration read and write cycles.                                                                                                                                                                            |  |  |  |  |  |  |

| INTA#       | 91                                                                                  | 0   | <b>Interrupt.</b> An asynchronous signal used to request an interrupt.                                                                                                                                                                                                                     |  |  |  |  |  |  |

| PCICLK      | 93                                                                                  | I   | PCI Clock. Timing reference for all transactions on the PCI Bus.                                                                                                                                                                                                                           |  |  |  |  |  |  |

| PCIRST#     | 92                                                                                  | Ι   | <b>Reset.</b> When detected low, an internal hardware reset is performed. PCIRST# assertion or deassertion may be asynchronous to PCLK, however, it is recommended that deassertion be synchronous to guarantee a clean and bounce free edge.                                              |  |  |  |  |  |  |

| PAR         | 3                                                                                   | IO  | <b>Parity.</b> A single parity bit is provided over AD[31:0] and C/BE[3:0]#.                                                                                                                                                                                                               |  |  |  |  |  |  |

| PERR#       | 2                                                                                   | О   | Parity Error. Parity error is asserted when a data parity error is detected.                                                                                                                                                                                                               |  |  |  |  |  |  |

| STOP#       | 128                                                                                 | IO  | <b>Stop.</b> Asserted by the target to request the master to stop the current transaction.                                                                                                                                                                                                 |  |  |  |  |  |  |

| 1394 PHY Interface |      |     |                                                                                                                                                                                                                                     |  |  |  |  |  |

|--------------------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Signal Name        | Pin# | I/O | Signal Description                                                                                                                                                                                                                  |  |  |  |  |  |

| PHYRST#            | 58   | I   | <b>PHY Reset.</b> Used to reset the PHY logic. This pin can be left unconnected as there is an internal RC network that creates a 0.5 ms to 2 ms power-on reset interval. This pin can also be driven by an open-drain type driver. |  |  |  |  |  |

| Configuration Straps |               |     |         |                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|----------------------|---------------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Signal Name          | Pin #         | I/O | Default | Signal Description                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| I2CEEENA             | 46            | I   | Low     | I2C EEPROM. Low = Disable (4-wire EEPROM interface), High = Enable (2-wire I2C EEPROM interface using SCL / SDA)                                                                                                                                                                                                                   |  |  |  |  |  |

| I2CFAST              | 48            | I   | Low     | I2C EEPROM Fast Mode. Low = Disable, High = Enable                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| CARDBUSENA           | 47            | I   | Low     | CardBus Mode. Low = Disable (PCI), High = Enable                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| PHYPC[2:0]           | 53,<br>55, 54 | Ι   |         | <b>Power Class.</b> Used to set the three POWER_CLASS bits in the Self-ID packet. These bits describe the power consumption and source characteristics of the node. PC0, 1, and 2 are reflected in Self-ID packet bits 21, 22, and 23 respectively. See Table 7 "Power Class Pin Strapping" on page 40 for additional information. |  |  |  |  |  |

| РНҮСМС               | 52            | I   | High    | <b>Programmable Contender / Bus Manager Capable.</b> High specifies that the node is capable of being a bus manager.                                                                                                                                                                                                               |  |  |  |  |  |

|             | Cable Interface and PHY Signals |     |                                                                                                                                                                                                                     |  |  |  |  |  |  |

|-------------|---------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Signal Name | Pin #                           | I/O | Signal Description                                                                                                                                                                                                  |  |  |  |  |  |  |

| XTPA0P      | 73                              | IO  | Port 0 Twisted Pair A Positive.                                                                                                                                                                                     |  |  |  |  |  |  |

| XTPA0M      | 72                              | IO  | Port 0 Twisted Pair A Negative.                                                                                                                                                                                     |  |  |  |  |  |  |

| XTPB0P      | 71                              | IO  | Port 0 Twisted Pair B Positive.                                                                                                                                                                                     |  |  |  |  |  |  |

| XTPB0M      | 70                              | IO  | Port 0 Twisted Pair B Negative.                                                                                                                                                                                     |  |  |  |  |  |  |

| XTPA1P      | 80                              | IO  | Port 1 Twisted Pair A Positive.                                                                                                                                                                                     |  |  |  |  |  |  |

| XTPA1M      | 79                              | IO  | Port 1 Twisted Pair A Negative.                                                                                                                                                                                     |  |  |  |  |  |  |

| XTPB1P      | 78                              | IO  | Port 1 Twisted Pair B Positive.                                                                                                                                                                                     |  |  |  |  |  |  |

| XTPB1M      | 77                              | IO  | Port 1 Twisted Pair B Negative.                                                                                                                                                                                     |  |  |  |  |  |  |

| XTPA2P      | 87                              | IO  | Port 2 Twisted Pair A Positive.                                                                                                                                                                                     |  |  |  |  |  |  |

| XTPA2M      | 86                              | IO  | Port 2 Twisted Pair A Negative.                                                                                                                                                                                     |  |  |  |  |  |  |

| XTPB2P      | 85                              | IO  | Port 2 Twisted Pair B Positive.                                                                                                                                                                                     |  |  |  |  |  |  |

| XTPB2M      | 84                              | IO  | Port 2 Twisted Pair B Negative.                                                                                                                                                                                     |  |  |  |  |  |  |

| XTPBIAS0    | 74                              | 0   | Port 2-0 Twisted Pair Bias Voltages. Provides 1.85V (typical) nominal bias for proper                                                                                                                               |  |  |  |  |  |  |

| XTPBIAS1    | 81                              |     | operation of the twisted-pair cable drivers and receivers, and for signaling to the remote nodes                                                                                                                    |  |  |  |  |  |  |

| XTPBIAS2    | 88                              |     | that the cable connections are active. High-impedance during chip reset or power down. Can be disabled via remote packets or via software. Each of these pins must be decoupled with a 0.33-uF capacitor to ground. |  |  |  |  |  |  |

| XCPS        | 63                              | I   | <b>Cable Power Status.</b> This pin is normally connected to the cable power through an 11K Ohm / 1K Ohm voltage divider. An internal comparator is used to detect the presence of cable power.                     |  |  |  |  |  |  |

| XRES        | 66                              | A   | <b>External Resistor.</b> A 6.34K Ohm $\pm 1\%$ resistor to ground is required for internal current source operation.                                                                                               |  |  |  |  |  |  |

| XI          | 60                              | I   | <b>Crystal Input.</b> These pins must be connected to a 24.576 MHz parallel resonant fundamental mode crystal.                                                                                                      |  |  |  |  |  |  |

| XO          | 61                              | O   | Crystal Output.                                                                                                                                                                                                     |  |  |  |  |  |  |

| Serial Configuration Memory / I2C Interface |    |        |                                                                                                            |  |  |  |  |  |

|---------------------------------------------|----|--------|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Signal Name Pin # I/O Signal Description    |    |        |                                                                                                            |  |  |  |  |  |

| EECS                                        | 29 | О      | <b>EEPROM Chip Select.</b> Chip select for external serial EEPROM when used to provide configuration data. |  |  |  |  |  |

| EEDO                                        | 30 | 0      | EEPROM Data Out.                                                                                           |  |  |  |  |  |

| EEDI / SDA                                  | 31 | I / IO | EEPROM Data In / I2C Data.                                                                                 |  |  |  |  |  |

| EECK / SCL                                  | 32 | O / IO | EEPROM Clock / I2C Clock.                                                                                  |  |  |  |  |  |

|             | Miscellaneous                   |     |                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|-------------|---------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Signal Name | Pin #                           | I/O | Signal Description                                                                                                                                                                                                                           |  |  |  |  |  |  |

| PME#        | 37                              | О   | Power Management Event.                                                                                                                                                                                                                      |  |  |  |  |  |  |

| MODE[1-0]   | 42-43                           | I   | Operation Select.  00 Normal Mode (all PHY / Link signals are disabled)  01 PHY Test Mode  10 Link Test Mode  11 Watch Mode (all PHY / Link signals are outputs)  Internal pull-down for default 00.  These pins are normally not connected. |  |  |  |  |  |  |

| NC          | 38, 40, 44-<br>48, 51-57,<br>67 | -   | <b>No Connect.</b> Reserved for future use. Some of these pins are used for power-on straps and some are used for test functions. Except for strap options, these pins should remain unconnected.                                            |  |  |  |  |  |  |

| Digital Power |                                          |   |                                  |  |  |  |  |  |

|---------------|------------------------------------------|---|----------------------------------|--|--|--|--|--|

| Signal Name   | Signal Name Pin # I/O Signal Description |   |                                  |  |  |  |  |  |

| VCC           | 8, 20, 33, 35,<br>102, 113, 114, 125     | P | <b>Power.</b> 3.3V ±0.3V.        |  |  |  |  |  |

| VCCRAM        | 24                                       | P | Internal SRAM Power. 3.3V ±0.3V. |  |  |  |  |  |

| Analog Power |        |     |                                                              |  |

|--------------|--------|-----|--------------------------------------------------------------|--|

| Signal Name  | Pin #  | I/O | Signal Description                                           |  |

| VCCSUS       | 39, 49 | P   | Suspend Power. 3.3V ±0.3V.                                   |  |

| VCCARX0      | 65     | P   | <b>Analog Power for 1394 Receive Channel 0.</b> 3.3V ±0.3V.  |  |

| VCCATX0      | 62     | P   | <b>Analog Power for 1394 Transmit Channel 0.</b> 3.3V ±0.3V. |  |

| VCCARX1      | 75     | P   | <b>Analog Power for 1394 Receive Channel 1.</b> 3.3V ±0.3V.  |  |

| VCCATX1      | 76     | P   | <b>Analog Power for 1394 Transmit Channel 1.</b> 3.3V ±0.3V. |  |

| VCCARX2      | 89     | P   | <b>Analog Power for 1394 Receive Channel 2.</b> 3.3V ±0.3V.  |  |

| VCCATX2      | 90     | P   | <b>Analog Power for 1394 Transmit Channel 2.</b> 3.3V ±0.3V. |  |

| Ground      |                                                 |     |                                            |  |

|-------------|-------------------------------------------------|-----|--------------------------------------------|--|

| Signal Name | Pin #                                           | I/O | Signal Description                         |  |

| GND         | 1, 9, 16, 26, 34, 36, 94,<br>103, 111, 115, 121 | P   | Ground.                                    |  |

| GNDRAM      | 25                                              | P   | Internal SRAM Ground.                      |  |

| GNDSUS      | 41, 50                                          | P   | Suspend Ground.                            |  |

| GNDARX0     | 64                                              | P   | Analog Ground for 1394 Receive Channel 0.  |  |

| GNDATX0     | 59                                              | P   | Analog Ground for 1394 Transmit Channel 0. |  |

| GNDARX1     | 68                                              | P   | Analog Ground for 1394 Receive Channel 1.  |  |

| GNDATX1     | 69                                              | P   | Analog Ground for 1394 Transmit Channel 1. |  |

| GNDARX2     | 82                                              | P   | Analog Ground for 1394 Receive Channel 2.  |  |

| GNDATX2     | 83                                              | P   | Analog Ground for 1394 Transmit Channel 2. |  |

Note 1: A combination of high frequency decoupling capacitors is suggested on all analog power / ground pairs.

Note 2: All grounds should be connected to the primary circuit board ground plane (i.e., to the lowest impedance point available).

Note 3: VCCRAM should be connected to VCC power plane.

## **REGISTERS**

### **Register Overview**

The following tables summarize the configuration and I/O registers of the VT6306. These tables also document the power-on default value ("Default") and access type ("Acc") for each register. Access type definitions used are RW (Read/Write), RO (Read/Only), "—" for reserved / used (essentially the same as RO), and RWC (or just WC) (Read / Write 1's to Clear individual bits). Registers indicated as RW may have some read/only bits that always read back a fixed value (usually 0 if unused); registers designated as RWC or WC may have some read-only or read write bits (see individual register descriptions for details).

Detailed register descriptions are provided in the following section of this document. All offset and default values are shown in hexadecimal unless otherwise indicated

### Table 2. Registers

### PCI Function 0 Registers – Link Controller

### **Configuration Space Header Registers**

| Offset | PCI Configuration Space Header      | Default   | Acc                    |

|--------|-------------------------------------|-----------|------------------------|

| 1-0    | Vendor ID                           | 1106      | RO                     |

| 3-2    | Device ID                           | 3044      | RO                     |

| 5-4    | Command                             | 0000      | RW                     |

| 7-6    | Status                              | 0280      | WC                     |

| 8      | Revision ID                         | nn        | RO                     |

| 9      | Programming Interface               | 10        | RO                     |

| Α      | Sub Class Code                      | 00        | RO                     |

| В      | Base Class Code                     | 0C        | RO                     |

| C      | -reserved- (cache line size)        | 00        |                        |

| D      | Latency Timer                       | 00        | $\mathbf{R}\mathbf{W}$ |

| Е      | Header Type                         | 00        | RO                     |

| F      | -reserved- (Built In Self Test)     | 00        |                        |

| 13-10  | OHCI CSR MMIO Base Address          | 0000 0000 | RW                     |

| 17-14  | VIO I/O Base Address                | 0000 0001 | RW                     |

| 1B-18  | CIS Base Address (PCI Mode)         | 0000 0000 | RO                     |

|        | CIS Base Address (Cardbus Mode)     | 0000 0000 | RW                     |

| 1C-27  | -reserved- (base address registers) | 00        | _                      |

| 28-2B  | CIS Pointer (PCI Mode)              | 0000 0000 | RO                     |

|        | CIS Pointer (Cardbus Mode)          | 0000 0083 | RO                     |

| 2F-2C  | Subsystem ID Read                   | Nnnn nnnn | RO                     |

| 30-33  | -reserved- (expan. ROM base addr)   | 00        |                        |

| 34     | Capabilities Pointer                | 50        | RO                     |

| 35-3B  | -reserved- (unassigned)             | 00        | _                      |

| 3C     | Interrupt Line                      | 00        | RW                     |

| 3D     | Interrupt Pin                       | 01        | RO                     |

| 3E     | Minimum Grant                       | 00        | RO                     |

| 3F     | Maximum Latency                     | 20        | RO                     |

### **Controller-Specific Configuration Registers**

| Offset | <b>Configuration Registers</b> | Default   | Acc |

|--------|--------------------------------|-----------|-----|

| 43-40  | PCI HCI Control                | 0000 0000 | RO  |

| 44-4F  | -reserved-                     | 00        | _   |

### **Power Management Registers**

| Offset | Power Management Register Block  | <u>Default</u> | Acc |

|--------|----------------------------------|----------------|-----|

| 50     | Power Management Capabilities ID | 01             | RO  |

| 51     | Next Pointer                     | 00             | RO  |

| 53-52  | Power Management Capabilities    | E002           | RO  |

| 55-54  | Power Management CSR             | 0000           | WC  |

| 56     | Power Management CSR BSE         | 00             | RO  |

| 57     | Power Management Data            | 00             | RO  |

| 58-FF  | -reserved-                       | 00             | _   |

## <u>Memory-Space Registers – Link Controller</u>

| Offset | Heading                          | Default   | Acc |

|--------|----------------------------------|-----------|-----|

| 0      | Version (OHCI 1.0 Mode)          | 0001 0000 | RO  |

|        | Version (OHCI 1.1 Mode)          | 0001 0010 | RO  |

| 4      | -reserved- (GUID ROM)            | 0000 0000 | _   |

| 8      | Asynchronous Transmit Retries    | 0000 0000 | RW  |

| С      | CSR Data                         | 0000 0000 | RW  |

| 10     | CSR Compare Data                 | 0000 0000 | RW  |

| 14     | CSR Control                      | 8000 0000 | RW  |

| 18     | Configuration ROM Header         | 0000 0000 | RW  |

| 1C     | 1394 Bus ID                      | 3133 3934 | RO  |

| 20     | 1394 Bus Options                 | F000 0002 | RW  |

| 24     | Global Unique ID High            | 0000 0000 | RW  |

| 28     | Global Unique ID Low             | 0000 0000 | RW  |

| 2C-33  | -reserved-                       | 00        | _   |

| 34     | Configuration ROM Map            | 0000 0000 | RW  |

| 38     | Posted Write Address Low         | 0000 0000 | RO  |

| 3C     | Posted Write Address High        | 0000 0000 | RO  |

| 40     | Vendor ID                        | 0000 0000 | RO  |

| 44-4F  | -reserved-                       | 00        |     |

| 50     | HC Control Set                   | 0000 0000 | RW  |

| 54     | HC Control Clear                 | 0000 0000 | RW  |

| 58-5F  | -reserved-                       | 00        | _   |

| 60-63  | -reserved-                       | 00        | _   |

| 64     | Self-ID Buffer Pointer           | 0000 0000 | RW  |

| 68     | Self-ID Count                    | 0000 0000 | RO  |

| 6C-6F  | -reserved-                       | 00        |     |

| 70     | Isoch Rcv Channel Mask High Set  | 0000 0000 | RW  |

| 74     | Isoch Rcv Channel Mask High Clr  | 0000 0000 | RW  |

| 78     | Isoch Rcv Channel Mask Low Set   | 0000 0000 | RW  |

| 7C     | Isoch Rcv Channel Mask Low Clr   | 0000 0000 | RW  |

| 80     | Interrupt Event Set              | 0000 0000 | RW  |

| 84     | Interrupt Event Clear            | 0000 0000 | RW  |

| 88     | Interrupt Mask Set               | 0000 0000 | RW  |

| 8C     | Interrupt Mask Clear             | 0000 0000 |     |

| 90     | Isoch Xmit Interrupt Event Set   | 0000 0000 | RW  |

| 94     | Isoch Xmit Interrupt Event Clear | 0000 0000 | RW  |

| 98     | Isoch Xmit Interrupt Mask Set    | 0000 0000 | RW  |

| 9C     | Isoch Xmit Interrupt Mask Clear  | 0000 0000 | RW  |

| A0     | Isoch Rcv Interrupt Event Set    | 0000 0000 | RW  |

| A4     | Isoch Rcv Interrupt Event Clear  | 0000 0000 | RW  |

| A8     | Isoch Rcv Interrupt Mask Set     | 0000 0000 | RW  |

| AC     | Isoch Rcv Interrupt Mask Clear   | 0000 0000 | RW  |

| Offset  | Heading                            | <u>Default</u> | <u>Acc</u> |

|---------|------------------------------------|----------------|------------|

| B3-B0   | Initial Bandwidth Available        | 0000 1333      | RW         |

| B7-B4   | Initial Channels Available Hi      | FFFFFFF        | RW         |

| BB-B8   | Initial Channels Available Lo      | FFFFFFF        | RW         |

| BC-DB   | -reserved-                         | 00             |            |

| DC      | Fairness Control                   | 0000 0000      |            |

| E0      | Link Control Set                   | 0000 0000      | RW         |

| E4      | Link Control Clear                 | 0000 0000      | RW         |

| E8      | Node ID                            | 0000 0000      | RW         |

| EC      | PHY Control                        | 0000 0000      | RW         |

| F0      | Isochronous Cycle Timer            | 0000 0000      | RW         |

| F4-FF   | -reserved-                         | 00             | —          |

| 100     | Async Request Filter High Set      | 0000 0000      | RW         |

| 104     | Async Request Filter High Clear    | 0000 0000      | RW         |

| 108     | Async Request Filter Low Set       | 0000 0000      | RW         |

| 10C     | Async Request Filter Low Clear     | 0000 0000      | RW         |

| 110     | Physical Request Filter High Set   | 0000 0000      | RW         |

| 114     | Physical Request Filter High Clear | 0000 0000      | RW         |

| 118     | Physical Request Filter Low Set    | 0000 0000      | RW         |

| 11C     | Physical Request Filter Low Clear  | 0000 0000      | RW         |

| 120-123 | Physical Upper Bound               | 0000 0000      | RW         |

| 124-17F | -reserved-                         | 00             | —          |

| 180     | Async Request Xmit Context Set     | 0000 0000      |            |

| 184     | Async Request Xmit Context Clr     | 0000 0000      | RW         |

| 18C     | Async Request Xmit Command Ptr     | 0000 0000      | RW         |

| 1A0     | Async Response Xmit Context Set    | 0000 0000      | RW         |

| 1A4     | Async Response Xmit Context Clr    | 0000 0000      | RW         |

| 1AC     | Async Response Xmit Cmd Ptr        | 0000 0000      | RW         |

| 1C0     | Async Request Rcv Context Set      | 0000 0000      | RW         |

| 1C4     | Async Request Rcv Context Clr      | 0000 0000      | RW         |

| 1CC     | Async Request Rcv Command Ptr      | 0000 0000      | RW         |

| 1E0     | Async Response Rcv Context Set     | 0000 0000      | RW         |

| 1E4     | Async Response Rcv Context Clr     | 0000 0000      | RW         |

| 1EC     | Async Response Rcv Command Ptr     | 0000 0000      | RW         |

| Offset  | Heading                      | <u>Default</u> | Acc |

|---------|------------------------------|----------------|-----|

| 200     | Isoch Xmit Context 0 Set     | 0000 0000      | RW  |

| 204     | Isoch Xmit Context 0 Clr     | 0000 0000      | RW  |

| 20C     | Isoch Xmit Context 0 Cmd Ptr | 0000 0000      | RW  |

| 210     | Isoch Xmit Context 1 Set     | 0000 0000      | RW  |

| 214     | Isoch Xmit Context 1 Clr     | 0000 0000      | RW  |

| 21C     | Isoch Xmit Context 1 Cmd Ptr | 0000 0000      | RW  |

| 220     | Isoch Xmit Context 2 Set     | 0000 0000      | RW  |

| 224     | Isoch Xmit Context 2 Clr     | 0000 0000      | RW  |

| 22C     | Isoch Xmit Context 2 Cmd Ptr | 0000 0000      | RW  |

| 230     | Isoch Xmit Context 3 Set     | 0000 0000      | RW  |

| 234     | Isoch Xmit Context 3 Clr     | 0000 0000      | RW  |

| 23C     | Isoch Xmit Context 3 Cmd Ptr | 0000 0000      | RW  |

| 240     | Isoch Xmit Context 4 Set     | 0000 0000      | RW  |

| 244     | Isoch Xmit Context 4 Clr     | 0000 0000      | RW  |

| 24C     | Isoch Xmit Context 4 Cmd Ptr | 0000 0000      | RW  |

| 250     | Isoch Xmit Context 5 Set     | 0000 0000      | RW  |

| 254     | Isoch Xmit Context 5 Clr     | 0000 0000      | RW  |

| 25C     | Isoch Xmit Context 5 Cmd Ptr | 0000 0000      | RW  |

| 260     | Isoch Xmit Context 6 Set     | 0000 0000      | RW  |

| 264     | Isoch Xmit Context 6 Clr     | 0000 0000      | RW  |

| 26C     | Isoch Xmit Context 6 Cmd Ptr | 0000 0000      | RW  |

| 270     | Isoch Xmit Context 7 Set     | 0000 0000      | RW  |

| 274     | Isoch Xmit Context 7 Clr     | 0000 0000      | RW  |

| 27C     | Isoch Xmit Context 7 Cmd Ptr | 0000 0000      | RW  |

| 280-3FF | -reserved-                   | 00             |     |

| Offset  | Heading                         | <u>Default</u> | Acc |

|---------|---------------------------------|----------------|-----|

| 400     | Isoch Rcv Context 0 Set         | 0000 0000      | RW  |

| 404     | Isoch Rcv Context 0 Clr         | 0000 0000      | RW  |

| 40C     | Isoch Rcv Context 0 Command Ptr | 0000 0000      | RW  |

| 410     | Isoch Rcv Context 0 Match       | 0000 0000      | RW  |

| 420     | Isoch Rcv Context 1 Set         | 0000 0000      | RW  |

| 424     | Isoch Rcv Context 1 Clr         | 0000 0000      | RW  |

| 42C     | Isoch Rcv Context 1 Command Ptr | 0000 0000      | RW  |

| 430     | Isoch Rcv Context 1 Match       | 0000 0000      | RW  |

| 440     | Isoch Rcv Context 2 Set         | 0000 0000      | RW  |

| 444     | Isoch Rcv Context 2 Clr         | 0000 0000      | RW  |

| 44C     | Isoch Rcv Context 2 Command Ptr | 0000 0000      | RW  |

| 450     | Isoch Rcv Context 2 Match       | 0000 0000      | RW  |

| 460     | Isoch Rcv Context 3 Set         | 0000 0000      | RW  |

| 464     | Isoch Rcv Context 3 Clr         | 0000 0000      | RW  |

| 46C     | Isoch Rcv Context 3 Command Ptr | 0000 0000      | RW  |

| 470     | Isoch Rcv Context 3 Match       | 0000 0000      | RW  |

| 480     | Isoch Rcv Context 4 Set         | 0000 0000      | RW  |

| 484     | Isoch Rcv Context 4 Clr         | 0000 0000      | RW  |

| 48C     | Isoch Rcv Context 4 Command Ptr | 0000 0000      | RW  |

| 490     | Isoch Rcv Context 4 Match       | 0000 0000      | RW  |

| 4A0     | Isoch Rcv Context 5 Set         | 0000 0000      | RW  |

| 4A4     | Isoch Rcv Context 5 Clr         | 0000 0000      | RW  |

| 4AC     | Isoch Rcv Context 5 Command Ptr | 0000 0000      | RW  |

| 4B0     | Isoch Rcv Context 5 Match       | 0000 0000      | RW  |

| 4C0     | Isoch Rcv Context 6 Set         | 0000 0000      | RW  |

| 4C4     | Isoch Rcv Context 6 Clr         | 0000 0000      | RW  |

| 4CC     | Isoch Rcv Context 6 Command Ptr | 0000 0000      | RW  |

| 4D0     | Isoch Rcv Context 6 Match       | 0000 0000      | RW  |

| 4E0     | Isoch Rcv Context 7 Set         | 0000 0000      | RW  |

| 4E4     | Isoch Rcv Context 7 Clr         | 0000 0000      | RW  |

| 4EC     | Isoch Rcv Context 7 Command Ptr | 0000 0000      | RW  |

| 4F0     | Isoch Rcv Context 7 Match       | 0000 0000      | RW  |

| 500-7FF | -reserved-                      | 00             |     |

### **PHY Registers**

Table 3. PHY Register Map

| Offset | 7                         | 6                        | 5     | 4         | 3       | 2      | 1       | 0   |

|--------|---------------------------|--------------------------|-------|-----------|---------|--------|---------|-----|

| 0000b  | PS                        | R                        |       |           | Physi   | cal ID |         |     |

| 0001b  |                           |                          | Gap ( | Count     |         |        | IBR     | RHB |

| 0010b  |                           | Total                    | Ports |           | -       | alv    | ways 11 | 1b  |

| 0011b  |                           | De                       | lay   |           | -       | M      | ax Spe  | ed  |

| 0100b  | Po                        | wer Cla                  | iss   |           | Jitter  |        | Cont    | LC  |

| 0101b  | Multi                     | Accel                    | PE    | Tout      | PF      | Loop   | ISBR    | WT  |

| 0110b  | -reserved-                |                          |       |           |         |        |         |     |

| 0111b  | Port Select - Page Select |                          |       |           | ect     |        |         |     |

| 1000b  |                           | Register 0 (Page Select) |       |           |         |        |         |     |

| 1001b  |                           | Register 1 (Page Select) |       |           |         |        |         |     |

| 1010b  |                           |                          | Regi  | ster 2 (1 | Page Se | elect) |         |     |

| 1011b  |                           |                          | Regi  | ster 3 (1 | Page Se | elect) |         |     |

| 1100b  |                           | Register 4 (Page Select) |       |           |         |        |         |     |

| 1101b  | Register 5 (Page Select)  |                          |       |           |         |        |         |     |

| 1110b  |                           | Register 6 (Page Select) |       |           |         |        |         |     |

| 1111b  |                           |                          | Regi  | ster 7 (1 | Page Se | elect) |         |     |

Physical ID = Address of This Node

R = Root Node

PS = Cable Power Status

RHB = Root Hold-Off

IBR = Initiate Bus Reset

Gap Count = For Gap Time Optimization

Total Ports = 3

Max Speed = Supports 98.304, 196.608, & 393.216 Mbit/s

Delay = Worst Case Repeater Delay

LC = Link Control

Cont = Contender

Jitter = Repeater Delay Variation

WT = Watchdog Timer Enable

ISBR = Initiate Short (Arbitrated) Bus Reset

Loop = Loop Detect

PF = Cable Power Fail Detect

Tout = Arbitration State Machine Timeout

PE = Port Event Detect

Accel = Arbitration Acceleration Enable

Multi = Multispeed Packet Concatenation Enable

### **Register Descriptions**

### <u>Link Controller Configuration Registers (PCI Function 0)</u>

The 1394 host controller interface follows the Open HCI (OHCI) interface specification. There are two sets of software accessible registers: configuration registers and memory registers. The configuration registers are located in the function 0 PCI configuration space. The memory registers are located in system memory space at offsets from the address stored in the Base Address Register.

### **Configuration Space Header**

| Offset 1 | -0 - Vendor IDRO                                   |

|----------|----------------------------------------------------|

| 0-7      | <b>Vendor ID</b> (1106h = VIA Technologies)        |

| Offset 3 | -2 - Device IDRO                                   |

| 0-7      | <b>Device ID</b> (3044h = VT6306 1394a Controller) |

| Offset 5 | -4 - Command RW                                    |

| 15-10    | <b>Reserved</b> always reads 0                     |

| 9        | Fast Back-to-Back Enable fixed at 0 (disabled)     |

| 8        | SERR# Enable fixed at 0 (disabled)                 |

| 7        | Wait Cycle Control fixed at 0 (disabled)           |

| 6        | Parity Error Response fixed at 0 (disabled)        |

| 5        | VGA Palette Snoop fixed at 0 (disabled)            |

| 4        | Postable Memory Write Enablefixed at 0 (disabled)  |

| 3        | Special Cycle Enable fixed at 0 (disabled)         |

| 2        | Bus Master Enable                                  |

|          | 0 Disabledefault                                   |

|          | 1 Enable                                           |

| 1        | Memory Space Enable                                |

|          | 0 Disabledefault                                   |

|          | 1 Enable Access to 1394 Memory Registers           |

| 0        | I/O Space Enable fixed at 0 (disabled)             |

| Offset 7 | 7-6 - StatusRWC                                                                                       |

|----------|-------------------------------------------------------------------------------------------------------|

| 15       | <b>Detected Parity Error</b> always reads 0                                                           |

| 14       | Signaled System Erroralways reads 0                                                                   |

| 13       | Received Master Abort                                                                                 |

|          | 0 No Master Abort Generateddefault                                                                    |

|          | 1 Master Abort Generated by 1394 Controller.                                                          |

|          | Set by the 1394 interface logic if it generates a                                                     |

|          | master abort while acting as a master. This bit                                                       |

|          | may be cleared by software by writing a one to                                                        |

|          | this bit position.                                                                                    |

| 12       | Received Target Abort                                                                                 |

|          | 0 No Target Abort Receiveddefault                                                                     |

|          | 1 Target Abort Received by 1394 Controller.                                                           |

|          | Set by the 1394 interface logic if it receives a                                                      |

|          | target abort while acting as a master. This bit                                                       |

|          | may be cleared by software by writing a one to                                                        |

|          | this bit position.                                                                                    |

| 11       | <b>Signaled Target Abort</b> always reads 0                                                           |

| 10-9     | DEVSEL# Timing                                                                                        |

|          | 00 Fast                                                                                               |

|          | 01 Mediumfixed                                                                                        |

|          | 10 Slow                                                                                               |

|          | 11 Reserved                                                                                           |

| 8        | <b>Data Parity Error Detected</b> always reads 0                                                      |

| 7        | Fast Back-to-Back Capablealways reads 1                                                               |

| 6        | User Definable Featuresalways reads 0                                                                 |

| 5        | 66 MHz Capablealways reads 0                                                                          |

| 4-0      | <b>Reserved</b> always reads 0                                                                        |

| Offset 8 | B - Revision ID (nnh)RO                                                                               |

| 7-0      | Silicon Revision Code (0 indicates first silicon)                                                     |

| 7-0      | Sincon Revision Code (6 indicates first sincon)                                                       |

| Offset 9 | - Programming Interface (10h=OHCI)RO                                                                  |

|          |                                                                                                       |

| Offset A | <b>A - Sub Class Code</b> (00h=1394 Serial Bus) <b>RO</b>                                             |

| O.00 4 T |                                                                                                       |

| Offset I | B - Base Class Code (0Ch=Serial Bus Controller)RO                                                     |

| Offcot I | O - Latency Timer (00h)RW                                                                             |

|          |                                                                                                       |

| 7-4      | Latency Timer Count  DCI hurst avales generated by the VT6306 can lest                                |

|          | PCI burst cycles generated by the VT6306 can last indefinitely as long as PCI GNT# remains active. If |

|          | indefinitely as long as PCI GNT# remains active. If GNT# is negated after the burst is initiated, the |

|          | VT6306 limits the duration of the burst to the number                                                 |

|          | of PCI Bus clocks specified in this field.                                                            |

| 3-0      | Reservedalways reads 0                                                                                |

| 3-0      | always leads 0                                                                                        |

| Offset I | E - Header Type (00h)RO                                                                               |

| Offset 1   | 3-10 - OHCI CSR MMIO Base (0000 0000h) RW            | Offset 3C - Interrupt Line (00h)             | RO          |

|------------|------------------------------------------------------|----------------------------------------------|-------------|

| 31-11      | <b>Base Address (2048-Byte Space)</b> default = 0    | 000 (00 )                                    | <b>D</b> .0 |

| 10-4       | <b>Reserved</b> always reads 0                       | Offset 3D - Interrupt Pin (01h=Drives INTA#) | RO          |

| 3          | Prefetechable always reads 0                         |                                              |             |

|            | Reads 0 to indicate that the register space is not   |                                              |             |

|            | prefetchable.                                        | Offset 3E - Minimum Grant (00h)              | RO          |

| 2-1        | <b>Type</b> always reads 0                           | Office 32 Minimum Office (00th)              |             |

|            | Reads 0 to indicate that the register space may be   | Offset 3F - Maximum Latency (20h)            | RO          |

|            | located anywhere in the 32-bit memory address space. |                                              |             |

| 0          | Resource Type always reads 0                         |                                              |             |

|            | Reads 0 to indicate a request for memory space.      |                                              |             |

|            |                                                      |                                              |             |

|            |                                                      |                                              |             |

|            | 7-14 – VIO I/O Base Address (0000 0001h) RW          |                                              |             |

| 31-7       | <b>Base Address (128-Byte Space)</b> default = $0$   |                                              |             |

| 6-4        | <b>Reserved</b> always reads 0                       |                                              |             |

| 3          | Prefetechable always reads 0                         |                                              |             |

|            | Reads 0 to indicate that the register space is not   |                                              |             |

|            | prefetchable.                                        |                                              |             |

| 2-1        | <b>Type</b> always reads 0                           |                                              |             |

|            | Reads 0 to indicate that the register space may be   |                                              |             |

|            | located anywhere in the 16-bit I/O address space.    |                                              |             |

| 0          | Resource Typealways reads 1                          |                                              |             |

|            | Reads 1 to indicate a request for I/O space.         |                                              |             |

|            |                                                      |                                              |             |

|            |                                                      |                                              |             |

| Offset 1   | B-18 – CIS Base (0000 0000h)RO (PCI Mode)            |                                              |             |

|            |                                                      |                                              |             |

|            | Base Address (256-Byte Space) default = 0            |                                              |             |

|            | Reservedalways reads 0                               |                                              |             |

| 3          | Prefetechable always reads 0                         |                                              |             |

| 3          | Reads 0 to indicate that the register space is not   |                                              |             |

|            | prefetchable.                                        |                                              |             |

| 2-1        | Typealways reads 0                                   |                                              |             |

| <b>4-1</b> | Reads 0 to indicate that the register space may be   |                                              |             |

|            | located anywhere in the 32-bit memory address space. |                                              |             |

| 0          | Resource Typealways reads 0                          |                                              |             |

| U          | Reads 0 to indicate a request for memory space.      |                                              |             |

|            | Reads o to indicate a request for memory space.      |                                              |             |

|            |                                                      |                                              |             |

| Offset 2   | 2B-28 – CIS Pointer RO                               |                                              |             |

|            | CIS Pointer (PCI Mode)reads 0000 0000h               |                                              |             |

| 31-0       | CIS Pointer (Cardbus Mode)reads 0000 000011          |                                              |             |

|            | CIS I Officer (Carabus Mode) leads 0000 008511       |                                              |             |

|            |                                                      |                                              |             |

| Off 13     | A C 1997 B 4 (FOL)                                   |                                              |             |

| Uliset 3   | 34 – Capabilities Pointer (50h)RO                    |                                              |             |

### **Controller-Specific Configuration Registers**

Offset 43-40 -PCI HCI Control.....RO

insert bit definitions here

### **Power Management Registers**

| Offset : | 50 – Capabilities ID (01h)RO                            | Offset:  | 55-54 – Pwr Mgmt Control / Status (PMCSR) RWC          |

|----------|---------------------------------------------------------|----------|--------------------------------------------------------|