# OKI semiconductor

# **MSM6950B**

### ANALOG FRONT END LSI

### GENERAL DESCRIPTION

The MSM6950B is an analog front-end LSI which is fabricated by OKI's low power consumption CMOS silicon gate technology for modem chip set based on Bell 212A. CCITT V. 22 and CCITT V. 22 bis standard. The MSM6950B consists of two BPFs, for low band and high band, an A/D converter with 8-bit parallel output, a D/A converter with 8-bit parallel input, an AGC circuit controlled by external digital signals, a guard tone generator (550 Hz/1800 Hz selectable) and some analogue signal control switches for various applications.

The MSM6950B communicates with a modulator and a demodulator via each 8 bits parallel digital line.

This chip does not contain a carrier detect function but it will be performed with a digital signal processor dedicated to implement a demodulator by using digital signals from the A/D converter.

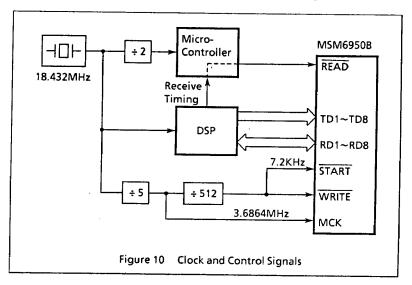

This device provides an analog signal input, an analog signal output and some signal-loop control inputs, and requires a 3.6864 MHz clock input to generate the operating time-base.

### **FEATURES**

- Conforms to bell 212A, 103 and CCITT V. 22 and V. 22 bis.

- 8-bit parallel output A/D converter and 8-bit parallel input D/A converter on chip.

- On-chip voltage reference.

- On-chip AGC circuit controlled by 8-bit external digital signal, over the received signal level range of 48 dB with 0.19 dB step.

- Dynamic range, 70 dB.

- Guard tone mixing function, 550 Hz or 1800 Hz.

- On-chip multi-purpose LPF for tone transmitting and call progress detection.

- Provides AC loop test function, a transmitting analog signal can be looped back as a receive analog signal within the chip.

- Supply voltage, ±5V.

- Low power dissipation, 115 mW.

- 3.6864 MHz external clock for operation.

- 42-pin plastic DIP . . . . MSM6950BRS 56-pin plastic FLAT

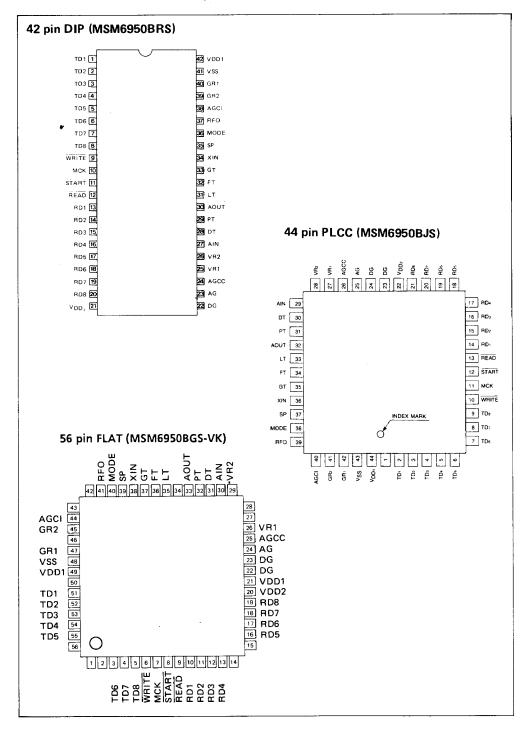

# PIN CONFIGURATION (Top view)

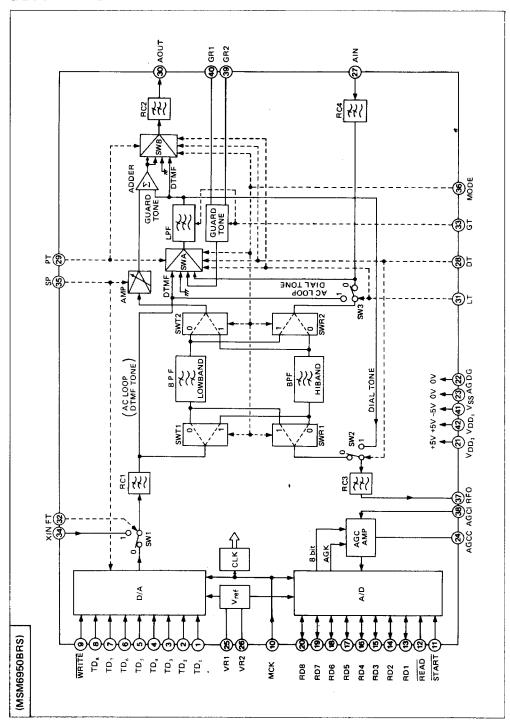

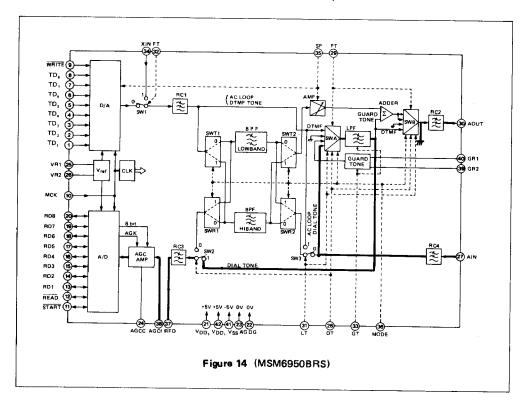

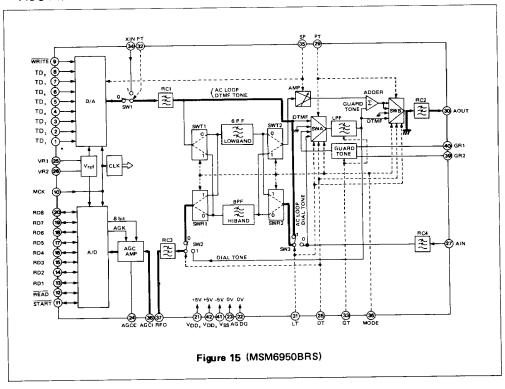

# **BLOCK DIAGRAM**

# Pin Assignment

| Pin Name  RS GS JS In/Out  TD1 1 51 2 Input Transmit signal digital data input to DA (LSB)  TD2 2 52 3 Input Transmit signal digital data input to DA  TD3 3 53 4 Input Transmit signal digital data input to DA  TD4 4 54 5 Input Transmit signal digital data input to DA  TD5 5 55 6 Input Transmit signal digital data input to DA  TD6 6 3 7 Input Transmit signal digital data input to DA  TD7 7 4 8 Input Transmit signal digital data input to DA  TD8 8 5 9 Input Transmit signal digital data input to DA  TD8 8 5 9 Input Transmit signal digital data input to DA  TD8 TOB |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TD2 2 52 3 Input Transmit signal digital data input to DA TD3 3 53 4 Input Transmit signal digital data input to DA TD4 4 54 5 Input Transmit signal digital data input to DA TD5 5 55 6 Input Transmit signal digital data input to DA TD6 6 3 7 Input Transmit signal digital data input to DA TD7 7 4 8 Input Transmit signal digital data input to DA TD8 8 5 9 Input Transmit signal digital data input to DA TD8 TD8 8 5 9 Input Transmit signal digital data input to DA TD8 TD8 TD8 TD8 TD8 TD8 TD9 TO9 TO9 TO9 TO9 TO9 TO9 TO9 TO9 TO9 TO                                                                          |     |

| TD3 3 53 4 Input Transmit signal digital data input to DA TD4 4 54 5 Input Transmit signal digital data input to DA TD5 5 55 6 Input Transmit signal digital data input to DA TD6 6 3 7 Input Transmit signal digital data input to DA TD7 7 4 8 Input Transmit signal digital data input to DA TD8 8 5 9 Input Transmit signal digital data input to DA TD8 8 5 10 Input Transmit signal digital data input to DA (MSB) WRITE 9 6 10 Input TD writing control signal for DA                                                                                                                                                |     |

| TD4 4 54 5 Input Transmit signal digital data input to DA  TD5 5 55 6 Input Transmit signal digital data input to DA  TD6 6 3 7 Input Transmit signal digital data input to DA  TD7 7 4 8 Input Transmit signal digital data input to DA  TD8 8 5 9 Input Transmit signal digital data input to DA  TD8 8 5 10 Input Transmit signal digital data input to DA (MSB)  WRITE 9 6 10 Input TD writing control signal for DA                                                                                                                                                                                                    |     |

| TD5 5 55 6 Input Transmit signal digital data input to DA TD6 6 3 7 Input Transmit signal digital data input to DA TD7 7 4 8 Input Transmit signal digital data input to DA TD8 8 5 9 Input Transmit signal digital data input to DA (MSB) WRITE 9 6 10 Input TD writing control signal for DA                                                                                                                                                                                                                                                                                                                              |     |

| TD6 6 3 7 Input Transmit signal digital data input to DA  TD7 7 4 8 Input Transmit signal digital data input to DA  TD8 8 5 9 Input Transmit signal digital data input to DA (MSB)  WRITE 9 6 10 Input TD writing control signal for DA                                                                                                                                                                                                                                                                                                                                                                                     |     |

| TD7 7 4 8 Input Transmit signal digital data input to DA TD8 8 5 9 Input Transmit signal digital data input to DA (MSB) WRITE 9 6 10 Input TD writing control signal for DA                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| TD8 8 5 9 Input Transmit signal digital data input to DA (MSB)  WRITE 9 6 10 Input TD writing control signal for DA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| WRITE 9 6 10 Input TD writing control signal for DA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| MCK 10 7 11 Input Master clock input 3 6864 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 10   7   11   input   master crock input 0.0004 init                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| START 11 8 12 Input Control signal for starting of AD conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| READ 12 9 13 Input RD reading control signal for AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| RD1 13 10 14 In/Out Receive signal digital data output from AD (LSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | )   |

| RD2 14 11 15 In/Out Receive signal digital data output from AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| RD3 15 12 16 In/Out Receive signal digital data output from AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 111 |

| RD4 16 13 17 In/Out Receive signal digital data output from AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ,   |

| RD5 17 16 18 In/Out Receive signal digital data output from AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| RD6 18 17 19 In/Out Receive signal digital data output from AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| RD7 19 18 20 In/Out Receive signal digital data output from AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| RD8 20 19 21 In/Out Receive signal sigital data output from AD (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | )   |

| VDD2 21 20 22 Positive power supply (+5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| DG 22 22, 23 23, 24 Digital ground (0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| AG 23 24 25 Analog ground (0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| AGCC 24 25 26 External capacitor terminal for AGC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| VR1 25 26 27 Input External resistor terminal for reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| VR2 26 29 28 Output External resistor terminal for reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| AIN 27 30 29 Input Receive analog signal input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| DT 28 31 30 Input Dial tone detecting loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| PT 29 32 31 Input DTMF signal transmitting loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| AOUT 30 33 32 Output Transmit analog signal output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| LT 31 35 33 Input AC loop test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| FT 32 36 34 Input XIN enable (Filter test or External input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| GT 33 37 35 Input Guard tone select (1800/550 Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| XIN 34 38 36 Input External transmit analog signal input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| SP 35 39 37 Input DA output PAM width select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| MODE 36 40 38 Input Originate/Answer mode select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| RFO 37 41 39 Output Receive filter output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| AGCI 38 44 40 Input AGC circuit input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| GR2 39 45 41 Output External resistor terminal for Guard tone level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| GR1 40 47 42 Input External resistor terminal for Guard tone level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| VSS 41 48 43 Negative power supply (-5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| VDD1 42 21,49 44 Positive power supply (+5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

# **ELECTRICAL CHARACTERISTICS**

# 1. Absolute Maximum Ratings

| Parameter             | Symbol           | Conditions                  | Ratings          | Unit |  |

|-----------------------|------------------|-----------------------------|------------------|------|--|

| Supply voltage        | VDD              |                             | -0.3 ~ +7        | ·-   |  |

| Suppry vortage        | VSS              | Ta = 25°C                   | +0.3 ~ -7        |      |  |

| Analog input voltage  | VIA              | with respect<br>to AG or DG |                  | V    |  |

| Digital input voltage | VID              |                             | -0.3 ~ VDD + 0.3 |      |  |

| Operating temperature | TOP              |                             | -40 ~ + 85       | 0 -  |  |

| Storage temperature   | T <sub>STG</sub> |                             | -55 ~ +150       | °C   |  |

# 2. Recommended Operating Conditions

| Parameter                                        | Symbol          | Condition                                                                              | Min    | Тур    | Max    | Unit       |

|--------------------------------------------------|-----------------|----------------------------------------------------------------------------------------|--------|--------|--------|------------|

|                                                  | V <sub>DD</sub> |                                                                                        | 4.75   | 5.00   | 5.25   |            |

| Power Supply Voltage                             | V <sub>SS</sub> | With Respect to<br>AG or DG                                                            | -5.25  | -5.00  | -4.75  | V          |

|                                                  | AG, DG          | _                                                                                      | _      | 0      | _      |            |

| Operating temperature                            | ТОР             | _                                                                                      | 0      | _      | 70     | °C         |

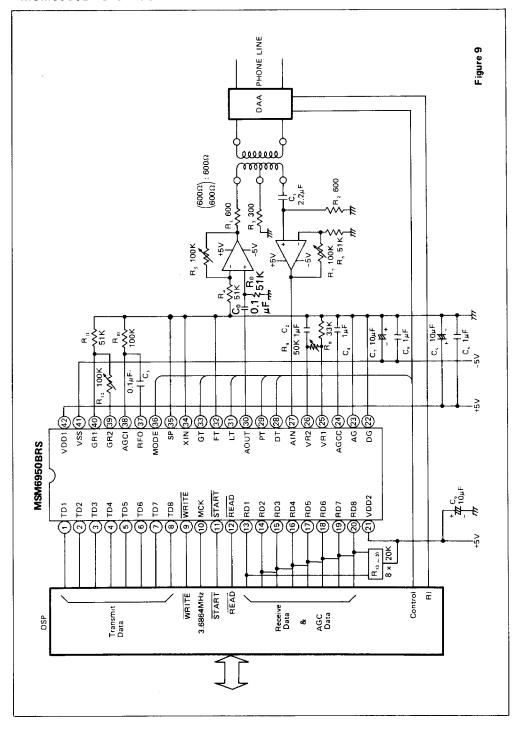

| R <sub>o</sub>                                   | _               | <del></del>                                                                            | _      | 51     | _      | ΚΩ         |

| R <sub>1</sub>                                   | -               | Transformer                                                                            | _      | 600    | _      |            |

| R <sub>2</sub>                                   | -               | Impedance (Hybrid) $ \left[ \frac{600 \ \Omega}{600 \ \Omega} \right] : 600 \ \Omega $ | -      | 600    | _      | Ω          |

| R <sub>3</sub>                                   | -               | $\left[\frac{600 \Omega}{1000000000000000000000000000000000000$                        | _      | 300    |        |            |

| R <sub>4</sub>                                   | _               | ,                                                                                      | -      | 51     | _      |            |

| R <sub>s</sub>                                   | -               |                                                                                        | _      | 51     | _      |            |

| R <sub>6</sub>                                   | -               |                                                                                        | -      | 51     | _      |            |

| R <sub>7</sub>                                   | _               |                                                                                        | -      | 51     | _      |            |

| R <sub>B</sub>                                   | _               | _                                                                                      | 10     | 33     |        | ΚΩ         |

| R,                                               | _               |                                                                                        | -      | 36     |        |            |

| R <sub>10</sub>                                  | -               |                                                                                        | -      | 100    | _      |            |

| R <sub>11</sub>                                  | _               |                                                                                        | -      | 51     | _      |            |

| R <sub>12</sub>                                  | _               |                                                                                        | _      | 51     | _      |            |

| Co                                               | _               | - 17- L-18-V-19-19-1-                                                                  | _      | 0.1    | -      |            |

| C,                                               | -               | •                                                                                      | _      | 2.2    | _      |            |

| C <sub>2</sub>                                   | -               |                                                                                        | _      | 1      | _      |            |

| C <sub>3</sub>                                   | _               |                                                                                        | _      | 0.1    | _      | _          |

| C.                                               | _               | _                                                                                      | _      | 1      | -      | μF         |

| C <sub>5</sub> , C <sub>7</sub> , C <sub>9</sub> | _               |                                                                                        | _      | 10     | -      |            |

| C <sub>6</sub> , C <sub>8</sub>                  | _               |                                                                                        | _      | 1      | _      |            |

| R <sub>13</sub> ~ R <sub>20</sub>                | _               | _                                                                                      | _      | 20     | -      | ΚΩ         |

| Reference Voltage                                | VR              | Adjusted by<br>External Resistors                                                      | _      | +2.50  |        | V          |

| Master Clock Frequency                           | FMCK            | _                                                                                      | 3.6860 | 3.6864 | 3.6867 | MHz        |

| MCK Duty Cycle                                   | РМСК            | 50% to 50%                                                                             | 30     | 50     | 70     | %          |

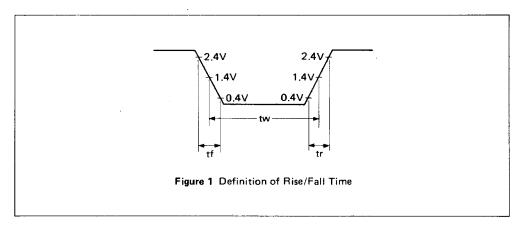

| Digital Input Rise Time                          | TR              | $T_{D_1} \sim T_{D_8}$ , WRITE,                                                        | 0      |        | 50     | nS         |

| Digital Input Fall Time                          | TF              | START, READ,<br>R <sub>D1</sub> ~R <sub>D8</sub> , See Figure 1                        | 0      | _      | 50     | n <b>S</b> |

#### ◆ MODEM · MSM6950B ◆

| Parameter                                | Symbol          | Condition       | Min  | Тур          | Max  | Unit |

|------------------------------------------|-----------------|-----------------|------|--------------|------|------|

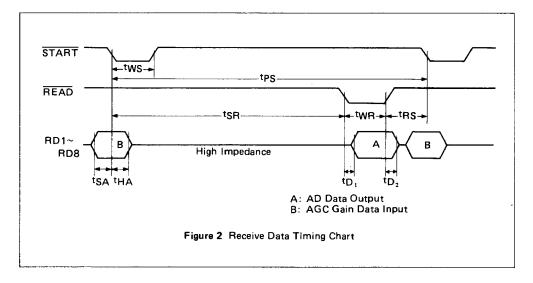

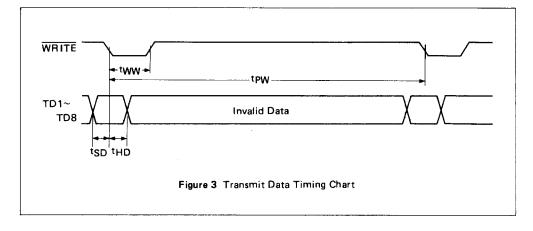

| WRITE Period *1                          | TPW             |                 | 115  | 1/<br>0.0072 | 143  | μS   |

| WRITE Width                              | Tww             |                 | 0.55 | _            | 100  | μS   |

| START Period                             | TPS             |                 | 98.2 | 1/<br>0.0072 | 143  | μS   |

| START Width                              | Tws             | See Figure 2, 3 | ,1,1 | _            | 79   | μS   |

| READ Width                               | TWR             |                 | 3.2  | _            | *    | μS   |

| START → READ<br>Timing                   | T <sub>SR</sub> |                 | 80   | _            | *    | μS   |

| READ → START<br>Timing                   | TRS             |                 | 15   | _            | *    | μS   |

| Allowable XIN Input<br>DC Offset Voltage | Vosxin          | _               | -100 | -            | +100 | mV   |

| Allowable AIN Input<br>DC Offset Voltage | VOSAIN          | _               | -100 | -            | +100 | mV   |

<sup>\*</sup> TWR MAX = TPS - TSR - TRS TSR MAX = TPS - TWR - TRS TRS MAX = TPS - TWR - TSR

### 3. Power Dissipation

(V<sub>DD</sub> = +5 V ±5%, V<sub>SS</sub> = -5 V ±5%, V<sub>R</sub> = +2.5 V,  $T_a$  = 0  $\sim$  70°C)

|                                  |        | - 00      |     |     | a   |      |

|----------------------------------|--------|-----------|-----|-----|-----|------|

| Parameter                        | Symbol | Condition | Min | Тур | Max | Unit |

| Positive Power<br>Supply Current | IDD    | _         | _   | 12  | 20  | mA   |

| Negative Power Supply Current    | ¹ss    | _         | -   | 11  | 20  | mA   |

Note:  $I_{DD} = I_{DD_1} (V_{DD_1} pin) + I_{DD_2} (V_{DD_2} pin)$ .

# 4. Digital Interface

$(V_{DD} = +5 \text{ V } \pm 5\%, V_{SS} = -5 \text{ V } \pm 5\%, T_a = 0 \sim 70^{\circ}\text{ C})$

| Parameter            | Symbol           | Condition                      | Min | Тур | Max | Unit |

|----------------------|------------------|--------------------------------|-----|-----|-----|------|

| Input Low Voltage    | VIL              | -                              | _   | _   | 0.6 | V    |

| Input High Voltage   | VIH              |                                | 2.2 | -   | _   | V    |

| Output Low Voltage   | VOL              | I <sub>OL</sub> = 0.36 mA      | -   | -   | 0.4 | V    |

| Output High Voltage  | Voн              | i <sub>OH</sub> = 20 μA        | 2.4 | _   | _   | V    |

| Input Low Current    | HL               | DG S VIN S VIL                 | -10 | _   | 10  | μА   |

| Input High Current   | ЧН               | $v_{IH} \le v_{IN} \le v_{DD}$ | -10 | -   | 10  | μΑ   |

| DA Data Set-up Time  | T <sub>SD</sub>  | See Figure 3                   | 0   |     | _   | μS   |

| DA Data Hold Time    | T <sub>HD</sub>  | See Figure 3                   | 1.1 | _   | _   | μS   |

| AGC Data Set-up Time | TSA              | Con Figure 2                   | 0   | _   | _   | μS   |

| AGC Data Hold Time   | THA              | See Figure 2                   | 2.2 | -   | -   | μS   |

| AD Data              | T <sub>D</sub> ; | Pull-up Resistor<br>= 20 KΩ    | 0.4 | -   | 3   | μS   |

| Output Delay Time    | T <sub>D2</sub>  | See Figure 2                   | 0.5 | -   | 3   | μS   |

# 5. ANALOG INTERFACE

$(VDD = +5V \pm 5\%, -5V \pm 5\%, Ta = 0 \sim 70$ °C)

# Reference Voltage (VR2)

| Parameter         | Symbol | Condition   | Min  | Тур  | Max  | Unit |

|-------------------|--------|-------------|------|------|------|------|

| Reference Voltage | VR     | R8 = Opened | 1.03 | 1.16 | 1.30 | ٧    |

# Transmit Modem Signal Characteristics (XIN, AOUT)

| P                           | arameter                   | Symbol | Conc                   | dition          | Min   | Тур           | Max           | Unit            |

|-----------------------------|----------------------------|--------|------------------------|-----------------|-------|---------------|---------------|-----------------|

| Input Resi                  | stance                     | RXIN   | XIN f <sub>XIN</sub>   | ≦ 5KHz          | 500   | , ,           |               | ΚΩ              |

| Input Volt                  | tage                       | VXIN   | XIN                    |                 |       |               | 5             | V <sub>PP</sub> |

| Output Vo                   | oltage                     | VAOUT  | RAOUT ≥ 2<br>CAOUT ≤ 1 | •               | 5     |               |               | V <sub>PP</sub> |

| Load Resis                  | stance                     | RAOUT  |                        |                 | 20    |               |               | ΚΩ              |

| Load Capa                   | citance                    | CAOUT  |                        |                 |       |               | 100           | PF              |

| DC Offset                   | Voltage                    | VOST   | AOUT, XIN              | = 0V            | - 500 | 0             | + 500         | mV              |

| *1                          | Bell 212A/<br>V.22/V.22bis | GT1    | Originate              | 1200Hz,<br>0dBm | + 0.5 | + 2.0         | + 3.5         | dB              |

| Absolute<br>Voltage<br>Gain |                            | GT2    | Answer                 | 2400Hz,<br>0dBm | + 0.5 | + 2.0         | + 3.5         | dB              |

|                             | Tone Transmit              | GT3    | GT = 1, 102            | 0Hz, 0dBm       | + 0.5 | + 2.0         | + 3.5         | dВ              |

| Gain Track                  | king                       | TGT1   | GT1 – GT2              |                 | - 1.0 | 0             | + 1.0         | dВ              |

|                             |                            | NIDLT1 | Originate              | 0.3~<br>3.4KHz  |       | ~ 60/<br>~ 55 | - 55/<br>- 50 | dBm             |

| *2<br>Idle                  | Bell 212A/<br>V.22/V.22bis | NIDLT2 | Answer                 |                 |       | - 56/<br>- 50 | - 50/<br>- 45 | dBm             |

| Channel<br>Noise            |                            | NIDLT3 | Originate              | 1.8~<br>3KHz    |       | - 76/<br>- 74 | - 65/<br>- 65 | dBm             |

|                             |                            | NIDLT4 | Answer                 | 0.6~<br>1.8KHz  |       | - 73/<br>- 71 | - 65/<br>- 65 | dBm             |

| •                           | Tone Transmit              | NIDLT5 | GT = 1                 | 0.3~<br>3.4KHz  |       | - 71/<br>- 70 | - 60/<br>- 60 | dBm             |

| Pa                                   | arameter           | Symbol | Condition            |                            | Min  | Тур  | Max  | Unit |

|--------------------------------------|--------------------|--------|----------------------|----------------------------|------|------|------|------|

| Clock Nois                           | e                  | NCLKT  | All modes,           | All modes, at 57.6KHz – 50 |      | dBm  |      |      |

| Total<br>Harmonic<br>Distor-<br>tion | Bell 212A/         | THDT1  | Originate            | 1200Hz,<br>0dBm            |      | - 55 | - 50 | dB   |

|                                      | V.22/V.22bis THDT2 | Answer | 2400Hz,<br>0dBm      |                            | - 48 | - 43 | dB   |      |

|                                      | Tone Transmit      | THDT3  | GT = 1, 1020Hz, 0dBm |                            |      | - 60 | - 55 | dB   |

<sup>\*1</sup> GT = 20 log (VAOUT/VXIN)

Note) 0dBm = 0.775Vrms

# Guard Tone (AOUT)

| Parameter                                 | Symbol | Condition                | Min    | Тур    | Max    | Unit |

|-------------------------------------------|--------|--------------------------|--------|--------|--------|------|

| Tone Frequency                            | FGT1   | GT = 0                   | 530    | 553.8  | 570    | Hz   |

|                                           | FGT2   | GT = 1                   | 1780   | 1800   | 1820   | Hz   |

| Tone Amplitude                            | VGT1   | GT = 0, R11 = Opened     | - 13.5 | - 15.0 | - 16.5 | dBm  |

|                                           | VGT2   | GT = 1, R11 = Opened     | - 13.0 | - 14.5 | - 16.0 | dBm  |

| Total Harmonic Distortion (2nd and 3rd) * | THDGT1 | GT = 0,<br>VGT1 = - 4dBm |        | - 63   | - 57   | dB   |

|                                           | THDGT2 | GT = 1,<br>VGT2 = - 4dBm |        | - 51   | - 45   | dВ   |

<sup>\*</sup> Harmonics above 3rd harmonic are negligible.

<sup>\*2</sup> Idle Channel Noise is defined with no weighted filter.

# Receive Modem Signal Characteristics (AIN, RFO)

| F                           | arameter                   | Symbol      | Cond                   | lition              | Min   | Тур           | Max           | Unit            |

|-----------------------------|----------------------------|-------------|------------------------|---------------------|-------|---------------|---------------|-----------------|

| Input Resi                  | stance                     | RAIN        | AIN f <sub>XIN</sub>   | ≦ 5KHz              | 500   |               |               | ΚΩ              |

| Input Vol                   | tage Swing                 | VAIN        | AIN                    |                     |       | <u> </u>      | 5             | V <sub>PP</sub> |

| Output Vo                   | oltage                     | VRFO        | RRFO≥ 201<br>CRFO≤ 100 |                     | 5     |               |               | V <sub>PP</sub> |

| Load Resis                  | stance                     | RRFO        | RFO                    |                     | 20    |               |               | ΚΩ              |

| Load Capa                   | acitance                   | CRFO        | RFO                    |                     |       |               | 100           | PF              |

| DC Offset                   | Voltage                    | VOSR        | RFO                    |                     | - 500 | 0             | + 500         | mV              |

| *1                          | Bell 212A/                 | GR1         | Answer                 | 1200Hz,<br>3dBm     | - 1.5 | 0             | + 1.5         | dB              |

| Absolute<br>Voltage<br>Gain | V.22/V.22bis               | GR2         | Originate              | 2400Hz,<br>3dBm     | - 1.5 | 0             | + 1.5         | dB              |

|                             | Tone Receive               | GR3         | GT = 0, 300            | GT = 0, 300Hz, 3dBm |       | 0             | + 1.5         | dB              |

| Gain Track                  | ing                        | TGR GR1-GR2 |                        |                     | - 1.0 | 0             | + 1.0         | dB              |

| *2<br>Idle                  | Bell 212A/                 | NIDLR1      | Answer                 |                     |       | - 63/<br>- 60 | - 57/<br>- 55 | dBm             |

| Channel<br>Noise            | V.22/V.22bis               | NIDLR2      | Originate              | 0.3~<br>3.4KHz      |       | - 63/<br>- 60 | - 57/<br>- 55 | dBm             |

|                             | Tone Receive               | NIDLR3      | GT = 0                 |                     |       | - 75/<br>- 73 | - 60/<br>- 60 | dBm             |

|                             |                            | NCLKR1      | All modes,             | at 57.6KHz          |       |               | - 45          | dBm             |

| Clock Nois                  | e<br>                      | NCLKR2      | GT = 0, at N           | × 14.4KHz           |       |               | - 35          | dBm             |

|                             |                            | THDR1       | Answer                 | 1200Hz,<br>+ 3dBm   |       | - 47          | - 43          | dB              |

| Total<br>Harmonic           | Bell 212A/<br>V.22/V.22bis | THDR2       | Originate              | 2400Hz,<br>+ 3dBm   |       | - 41          | - 37          | dB              |

| Distor-<br>tion             |                            | THDR3       | Originate              | 1200Hz,<br>0dBm     |       | - 58          | - 53          | dB              |

|                             | Tone Receive               | THDR4       | GT = 0, 300F<br>+ 3dBm | łz,                 |       | - 53          | - 49          | dB              |

<sup>\*1</sup> GR = 20 log (VRFO/VAIN)

① / ② ①;WRITE = 7.2KHz, ②; WRITE = 8.4KHz

<sup>\*2</sup> Idle Channel Noise is defined with no weighted filter.

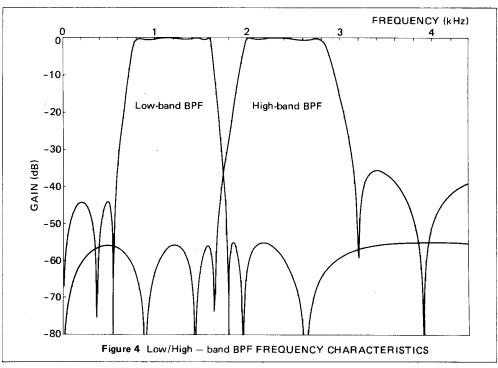

# 6. Filter Transfer Characteristics

| $(V_{DD} = +5 V \pm 5\%,$ | V <sub>SS</sub> = -5 V ±5% | , V <sub>R</sub> = +2.5 V, T | $_{\rm a}$ = 0 $\sim$ 70°C) |

|---------------------------|----------------------------|------------------------------|-----------------------------|

|---------------------------|----------------------------|------------------------------|-----------------------------|

|                                  | G <sub>FL1</sub>  | 508 Hz         | _    | -44      | -40  | dB |

|----------------------------------|-------------------|----------------|------|----------|------|----|

|                                  | G <sub>FL2</sub>  | 555 Hz         | _    | -60      | -45  | dB |

|                                  | G <sub>FL3</sub>  | 898 Hz         | -1.5 | _        | +1.5 | dB |

|                                  | G <sub>FL₄</sub>  | 1,008 Hz       | Ref  | erred Ga | in O | dB |

| Relative Voltage<br>Gain to GFL₄ | G <sub>FL</sub> s | 1,148 Hz       | -1.5 | _        | +1.5 | dB |

| Juli 13 Jr L4                    | G <sub>FL6</sub>  | 1,352 Hz       | -1.5 | _        | +1.5 | dB |

|                                  | G <sub>FL</sub> 7 | 1,508 Hz       | -2   | -        | +1   | dB |

|                                  | G <sub>FL</sub> 8 | 1,805 Hz       | _    | -65      | -45  | dB |

|                                  | G <sub>FL</sub> , | 2400 Hz        | _    | -55      | -50  | dB |

| Group Delay Distortion           | GDL               | 900 ~ 1,500 Hz | _    | _        | 100  | μS |

|                                  |                   |                |      |          |      |    |

### + MODEM · MSM6950B +----

# High-band BPF

| Parameter                                    | Symbol            | Condition        | Min  | Тур          | Max  | Unit |

|----------------------------------------------|-------------------|------------------|------|--------------|------|------|

|                                              | G <sub>FH1</sub>  | 1,195 Hz         | _    | -55          | -50  | d₿   |

|                                              | G <sub>FH₂</sub>  | 1,641 Hz         | _    | -55          | -50  | dB   |

|                                              | GFH₃              | 2,055 Hz         | -1.5 |              | +1.5 | dB   |

|                                              | G <sub>FH₄</sub>  | 2,195 Hz         | Ref  | dB           |      |      |

| Relative Voltage<br>Gain to GFH <sub>4</sub> | GFH₅              | 2,398 Hz         | -1.5 | _            | +1.5 | dB   |

|                                              | G <sub>FH6</sub>  | 2,602 Hz         | -1.5 | _            | +1.5 | dB   |

|                                              | G <sub>FH7</sub>  | 2,742 Hz         | -0.5 | <del>-</del> | +2.5 | ₫B   |

|                                              | G <sub>FH</sub>   | 3,211 Hz         |      | -43          | -38  | dB   |

|                                              | G <sub>FH</sub> , | 3,398 Hz         | _    | -35          | -29  | dB   |

| Group Delay Distortion                       | GDH               | 2,100 ~ 2,700 Hz |      | _            | 200  | μS   |

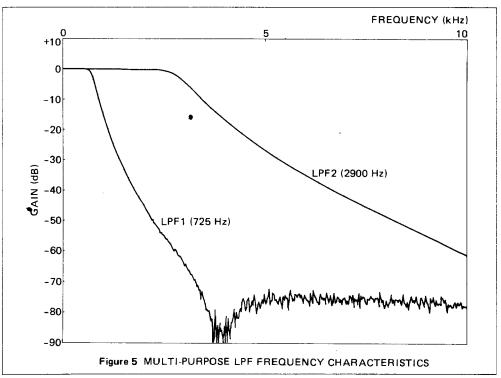

# Multi-purpose LPF

| Parameter                                     | Symbol            | Cond     | ition  | Min      | Тур             | Max | Unit |

|-----------------------------------------------|-------------------|----------|--------|----------|-----------------|-----|------|

|                                               | G <sub>FLF</sub>  | 211 Hz   |        | -1       | 0               | +1  | dB   |

| Relative Voltage<br>Gain to GFLF <sub>2</sub> | G <sub>FLF₂</sub> | 305 Hz   | 1      | Ref      | Referred Gain 0 |     |      |

|                                               | G <sub>FLF₃</sub> | 727 Hz   | GT = 0 | -4       | -3              | -2  | dB   |

|                                               | G <sub>FLF₄</sub> | 1,508 Hz |        | _        | _               | -30 | dB   |

|                                               | G <sub>FHF1</sub> | 211 Hz   | ,      | -1       | 0               | +1  | dB   |

| Relative Voltage                              | G <sub>FHF₂</sub> | 305 Hz   |        | Ref      | Referred Gain 0 |     | dB   |

| Gain to G <sub>FH</sub> F₂                    | G <sub>FHF₃</sub> | 2,906 Hz | GT = 1 | -4 -3 -2 |                 | dB  |      |

|                                               | G <sub>FHF₄</sub> | 3,898 Hz | 1      | _        | _               | -10 | dB   |

# 7. AGC Circuit and DA, AD Converters

|           | (V <sub>DD</sub> = | +5 V ±5%, V <sub>SS</sub> = -5 V ± | 5%, V <sub>R</sub> = | +2.5 V, | $T_a = 0$ | ∨ 70°C) |

|-----------|--------------------|------------------------------------|----------------------|---------|-----------|---------|

| Parameter | Symbol             | Condition                          | Min                  | Тур     | Max       | Unit    |

### **AGC Amplifier**

| Input Resistance               | RAGCI  | -          | _           | 1                | _           | MΩ          |

|--------------------------------|--------|------------|-------------|------------------|-------------|-------------|

| Variable Voltage<br>Gain Range | GAGC   | —          | -4          | _                | +43.8       | dВ          |

| Voltage Gain<br>Accuracy       | GE     | _          | -0.4        | +0.03<br>~ -0.17 | +0.4        | dB          |

| Output<br>DC Offset Voltage    | VOSAGC | AGC1 = 0 V | -60<br>(-3) | _                | +60<br>(+3) | mV<br>(LSB) |

### **Transmit Digital to Analog Converter**

| Bits of Resolu      | ution               | BREST | <del>-</del> | -             | 8      | _   | bit |

|---------------------|---------------------|-------|--------------|---------------|--------|-----|-----|

| End-point Linearity |                     | NLDA  | _            | _             | 0.36   | 0.5 | %   |

| Differential N      | Non-linearity       | DNLDA | _            | - 1/5 1/2 LSB |        |     |     |

|                     | Plus<br>Full Scale  | PFVDA | _            | _             | +2,481 | -   | mV  |

| Full Scale          | Minus<br>Full Scale | NFVDA | -            | _             | -2,500 | _   | mV  |

| DC Offset Vo        | C Offset Voltage    |       | _            | -10           | -1.5   | +10 | mV  |

### **Receive Analog to Digital Converter**

| Bits of Resolution  |                            | BRESR             | _ | _    | 8      | _    | bit |

|---------------------|----------------------------|-------------------|---|------|--------|------|-----|

| End-point Linearity |                            | NLAD              | _ | _    | 0.24   | 0.5  | %   |

| Differential N      | Differential Non-linearity |                   | _ | _    | 1/5    | 1/2  | LSB |

| Full Scale          | Plus<br>Full Scale         | PFVAD             | _ | _    | +2,481 | _    | mV  |

| ruii Scale          | Minus<br>Full Scale        | NFV <sub>AD</sub> | _ | _    | -2,500 | _    | mV  |

| DC Offset Voltage*  |                            | VOSAD             |   | -1/2 | _      | +1/2 | LSB |

<sup>\*</sup> This specification does not include the DC offset voltage at the input of the AD converter.

# PIN DESCRIPTION

| D: N      |     | Pin No            | o   |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                        |                      | _                       |                    |                 |                     |               |                            |                                      |

|-----------|-----|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------|----------------------|-------------------------|--------------------|-----------------|---------------------|---------------|----------------------------|--------------------------------------|

| Pin Name  | RS  | GS                | JS  |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                        |                      | ۲                       | unct               | ion             |                     |               |                            |                                      |

| TD1 ~ TD8 | 1~8 | 3∿5,<br>51∿<br>55 | 2~9 | Transmit signal digital data input for DA conversion. These pins are 8 bit parallel two's complement data input pins. The data is loaded to the DA converter at the falling edge of WRITE, TD1 is the LSB and TD8 is the MSB. Refer to Table 1 below.                                                                                                                                                                                            |            |                        |                      |                         |                    |                 |                     |               | ta is loaded to            |                                      |

|           |     |                   |     | D                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8          | 7                      | 6                    | 5                       | 4                  | 3               | 2                   | 1             | Total<br>Value             | Nominal<br>Output Voltage*           |

|           |     |                   |     | Plus Full Scale                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0          | 1                      | 1                    | 1                       | 1                  | 1               | 1                   | 1             | +127                       | +2,172.1 mV                          |

|           |     |                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                        |                      |                         |                    |                 |                     |               | +126                       |                                      |

|           |     |                   |     | Plus 0                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0          | 0                      | D                    | 0                       | 0                  | 0               | 0                   | 0             | 0                          | 0                                    |

|           |     |                   |     | Minus 0                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1          | 1                      | 1                    | 1                       | 1                  | 1               | 1                   | 1             | -1                         | -17.1 mV                             |

|           |     |                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                        |                      |                         | 1                  |                 | *                   |               | -2<br>~ 127                |                                      |

|           |     |                   |     | Minus Full Scale                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1          | D                      | D                    | 0                       | 0                  | 0               | 0                   | 0             | -128                       | -2,189.2 mV                          |

| WRITE     | 9   | 6                 | 10  | This signal enable. The digital input at the falling edg signal.  The analog output edge of WRITE s                                                                                                                                                                                                                                                                                                                                              | friec      | om 1<br>of <b>W</b> I  | TD1<br>RITE          | ~ TI<br>E sigi          | D8 is<br>nal, a    | s latc<br>and t | hed<br>hen<br>t 9 / | to the        | ne DA<br>verted<br>after t | converter<br>to analog<br>he falling |

| MCK       | 10  | 7                 | 11  | 115 $\mu \text{sec} \sim 143  \mu$<br>A 3.6864 MHz c<br>time base for the                                                                                                                                                                                                                                                                                                                                                                        | use<br>loc | c.<br>k sig            | ınal :               | shou                    | ld be              | e app           | lied                | to t          |                            |                                      |

| START     | 11  | 8                 | 12  | This signal enables MSM6950B to start the AD conversion. This signal is also used to latch the input data used for setting the amplitude of the AGC circuit. The input data is supplied from a demodulating chip, the general performance of which is digital signal processing. These two operations are performed at the falling edge of $\overline{START}$ . The cycle of this signal can be chosen out of 98 $\mu$ sec $\sim$ 143 $\mu$ sec. |            |                        |                      |                         |                    |                 |                     |               |                            |                                      |

| READ      | 12  | 9                 | 13  | This is a control While this pin is result of the AD While this pin is RD1 ~ RD8 bec                                                                                                                                                                                                                                                                                                                                                             | at co      | digit<br>nver<br>digit | al 0<br>sion<br>al 1 | state<br>is ou<br>state | the<br>tput<br>the | out<br>t froi   | put<br>m R          | bus i<br>D1 ^ | s activ                    | rated and the<br>terminals.          |

| Din Name         | F         | in No                               | ).              | F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|------------------|-----------|-------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin Name         | RS        | GS                                  | JS              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| RD1 ~ RD8        | 13^<br>20 | 10\(\sigma\) 23,<br>16\(\sigma\) 19 | 14\(\sigma\) 21 | These are I/O terminals controlled by START and READ terminals. When READ is set at digital 0 state, RD1 ~ RD8 become output terminals and the AD conversion result is output from these pins with 8 bit parallel two's compliment format. Refer to Table 2. When READ is set at digital 1 state, RD1 ~ RD8 become input terminals. The data input to these pins is loaded into the registers at the falling edge of START signal. In this case, this data is used at the gain setting data for AGC circuit.  Nominal absolute voltage gain of AGC circuit is described in Table 3. The dynamic range of the AGC circuit is about 48 dB as shown in Table 3.  READ = Digital 0 |  |  |  |  |  |  |

|                  |           |                                     |                 | RD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                  |           |                                     |                 | 1 1 1 1 1 1 1 0 +43.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| V <sub>DD2</sub> | 21        | 20                                  | 22              | Positive power supply, +5 V. This power supply is internally connected to the digital output logical circuitry RD1 $\sim$ RD8 to avoid the deterioration to the noise performance. Same power supply as to VDD1 should be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| DG               | 22        | 22,<br>23                           | 23,<br>24       | Digital ground, 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| AG               | 23        | 24                                  | 25              | Analog ground, 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| AGCC             | 24        | 25                                  | 26              | An external capacitor of 1 $\mu F$ should be connected between AGCC and AG. This capacitor is necessary to compensate the DC offset voltage generated in the AGC circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 25,<br>26 | 26,<br>29 | JS<br>27,<br>28  | Function  The MSM6950B provides the voltage reference which is used for AD and DA convertions.  The electrical potential is stabilized to variations of temperature or supply voltages, but tends to be different from chip to chip.                                                                                                                                                                              |

|-----------|-----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |           |                  | and DA convertions.<br>The electrical potential is stabilized to variations of temperature or                                                                                                                                                                                                                                                                                                                     |

|           |           |                  | Therefore, an external adjustment is necessary. The resistors used to adjust the reference voltage are connected to these pins as shown in Figure 6.                                                                                                                                                                                                                                                              |

| 27        | 30        | 29               | Receive analog signal input pin. The maximum input level is about +7.2 dBm (5 Vp-p).                                                                                                                                                                                                                                                                                                                              |

| 28,<br>29 | 31,<br>32 | 30,<br>31        | These pins control the transmit and receive analog signal paths for AC loop test, DTMF tone, guard tone and call progress tone. For details, refer to Table 8.                                                                                                                                                                                                                                                    |