# FMS6690 Six Channel, 6th Order SD/PS/HD Video Filter Driver

#### **Features**

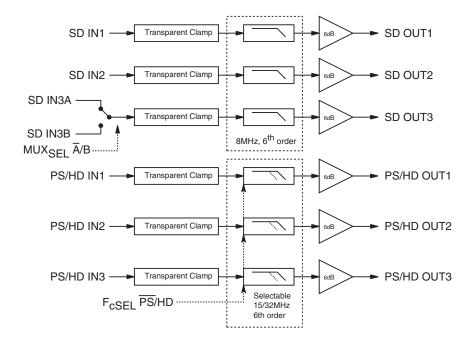

- Three selectable sixth-order 15/32MHz (PS/HD) filters

- Three fixed sixth-order 8MHz (SD) filters with muxed input

- Transparent input clamping

- Single video load drive (2Vpp, 150 $\Omega$ , A<sub>V</sub> = 6dB)

- AC or DC-coupled inputs

- AC or DC-coupled outputs

- DC-coupled outputs eliminate AC-coupling capacitors

- Low power

- 5V only

- Lead (Pb) free packages TSSOP-20

### **Applications**

- Cable and satellite set-top boxes

- DVD players

- HDTV

- Personal Video Recorders (PVR)

- Video On Demand (VOD)

### **Description**

The FMS6690 Low Cost Video Filter (LCVF) is intended to replace passive LC filters and drivers with a low-cost integrated device. Six 6th order Butterworth filters provide improved image quality compared to typical passive solutions. The combination of low power Standard Definition (SD), Progressive Scan (PS), and High Definition (HD) filters greatly simplify DVD video output circuitry. Three channels offer fixed SD filters and feature an additional muxed input, while the other three channels are selectable between PS and HD filters. The FMS6690 offers a fixed gain of 6dB.

The FMS6690 may be directly driven by a DC-coupled DAC output or an AC-coupled signal. Internal diode clamps and bias circuitry may be used if AC-coupled inputs are required (see applications section for details).

The outputs can drive AC or DC-coupled single  $(150\Omega)$  video loads. DC-coupling the outputs removes the need for output coupling capacitors. The input DC levels will be offset approximately +280mV at the output.

### **Block Diagram**

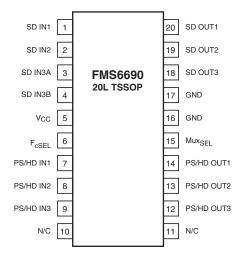

## **Pin Configuration**

## **Pin Assignments**

| Pin<br># | Pin                | Туре   | Description                                                              |  |

|----------|--------------------|--------|--------------------------------------------------------------------------|--|

| 1        | SD IN1             | Input  | SD video input, channel 1                                                |  |

| -        | SD IN1             |        | ' '                                                                      |  |

| 2        |                    | Input  | SD video input, channel 2                                                |  |

| 3        | SD IN3A            | Input  | SD video input, channel 3A                                               |  |

| 4        | SD IN3B            | Input  | SD video input, channel 3B                                               |  |

| 5        | VCC                | Input  | +5V supply                                                               |  |

| 6        | FcSEL              | Input  | Selects filter corner frequency for pins 7, 8, and 9. "0" = PS, "1" = HD |  |

| 7        | PS/HD IN1          | Input  | Selectable PS or HD video input, channel 1                               |  |

| 8        | PS/HD IN2          | Input  | Selectable PS or HD video input, channel 2                               |  |

| 9        | PS/HD IN3          | Input  | Selectable PS or HD video input, channel 3                               |  |

| 10       | N/C                | Input  | nt No Connect                                                            |  |

| 11       | N/C                | Input  | No Connect                                                               |  |

| 12       | PS/HD OUT3         | Output | Filtered PS or HD video output, channel 3                                |  |

| 13       | PS/HD OUT2         | Output | Filtered PS or HD video output, channel 2                                |  |

| 14       | PS/HD OUT1         | Output | Filtered PS or HD video output, channel 1                                |  |

| 15       | MUX <sub>SEL</sub> | Input  | Mux selects between channel 3A and 3B inputs. "0" = A, "1" = B           |  |

| 16       | GND                | Input  | Must be tied to Ground                                                   |  |

| 17       | GND                | Input  | Must be tied to Ground                                                   |  |

| 18       | SD OUT3            | Output | Filtered SD video output, channel 3                                      |  |

| 19       | SD OUT2            | Output | Filtered SD video output, channel 2                                      |  |

| 20       | SD OUT1            | Output | Filtered SD video output, channel 1                                      |  |

## **Absolute Maximum Ratings**

| Parameter                                       | Min  | Max                   | Unit |

|-------------------------------------------------|------|-----------------------|------|

| DC Supply Voltage                               | -0.3 | 6                     | V    |

| Analog and Digital I/O                          | -0.3 | V <sub>cc</sub> + 0.3 | V    |

| Output Current, Any One Channel (Do Not Exceed) |      | 50                    | mA   |

## **Reliability Information**

| Parameter                                                                                  | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Junction Temperature                                                                       |     |     | 150 | °C   |

| Storage Temperature Range                                                                  | -65 |     | 150 | °C   |

| Lead Temperature (Soldering, 10s)                                                          |     |     | 300 | °C   |

| Thermal Resistance (Theta $_{\rm JA}$ ), JEDEC Standard Multi-Layer Test Boards, Still Air |     | 74  |     | °C/W |

## **Recommended Operating Conditions**

| Parameter                   | Min  | Тур | Max  | Unit |

|-----------------------------|------|-----|------|------|

| Operating Temperature Range | 0    |     | 70   | °C   |

| Supply Voltage Range        | 4.75 | 5.0 | 5.25 | V    |

### **DC Electrical Characteristics**

$T_c$  = 25°C,  $V_{cc}$  = 5V,  $R_{source}$  = 37.5 $\Omega$ , inputs AC coupled with 0.1 $\mu$ F, all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$  loads, referenced to 400kHz; unless otherwise noted.

| Symbol          | Parameter                       | Conditions                       | Min | Тур | Max             | Units |

|-----------------|---------------------------------|----------------------------------|-----|-----|-----------------|-------|

| I <sub>CC</sub> | Supply Current <sup>1</sup>     | no load                          |     | 60  | 80              | mA    |

| V <sub>in</sub> | Video Input Voltage Range       | Referenced to GND, if DC-coupled |     | 1.4 |                 | Vpp   |

| V <sub>il</sub> | Digital Input Low <sup>1</sup>  | F <sub>cSEL</sub>                | 0   |     | 0.8             | V     |

| V <sub>ih</sub> | Digital Input High <sup>1</sup> | F <sub>cSEL</sub>                | 2.4 |     | V <sub>cc</sub> | V     |

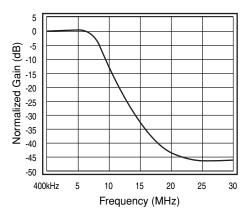

### **Standard Definition Electrical Characteristics**

$T_c$  = 25°C,  $V_{in}$  = 1 $V_{pp}$ ,  $V_{cc}$  = 5V,  $R_{source}$  = 37.5 $\Omega$ , all inputs AC coupled with 0.1 $\mu$ F, all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$  loads, referenced to 400kHz; unless otherwise noted.

| Symbol              | Parameter                                 | Conditions                         | Min | Тур  | Max | Units |

|---------------------|-------------------------------------------|------------------------------------|-----|------|-----|-------|

| AV <sub>SD</sub>    | Channel Gain <sup>1</sup>                 | All SD Channels                    | 5.6 | 6.0  | 6.4 | dB    |

| f <sub>1dBSD</sub>  | -1dB Bandwidth <sup>1</sup>               | All SD Channels                    | 5.2 | 7.15 |     | MHz   |

| f <sub>cSD</sub>    | -3dB Bandwidth <sup>1</sup>               | All SD Channels                    | 6.5 | 8.0  |     | MHz   |

| f <sub>SBSD</sub>   | Attenuation(stopband reject) <sup>1</sup> | All SD Channels at f = 27MHz       | 43  | 50   |     | dB    |

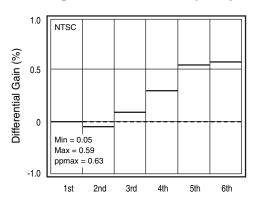

| DG                  | Differential Gain                         | All SD Channels                    |     | 0.7  |     | %     |

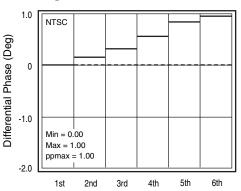

| DP                  | Differential Phase                        | All SD Channels                    |     | 1.0  |     | ۰     |

| THD                 | Output Distortion                         | $V_{OUT} = 1.4V_{pp}, 3.58MHz$     |     | 0.35 |     | %     |

| X <sub>TALKSD</sub> | Crosstalk (ch-to-ch)                      | at 1MHz                            |     | -54  |     | dB    |

| SNR                 | Signal-to-Noise Ratio <sup>2</sup>        | NTC-7 weighting, 100kHz to 4.2MHz  |     | 72   |     | dB    |

| t <sub>pdSD</sub>   | Propagation Delay                         | Delay from input to output, 4.5MHz |     | 90   |     | ns    |

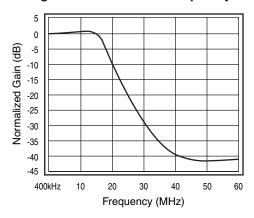

## **Progressive Scan Electrical Characteristics**

$T_c$  = 25°C,  $V_{in}$  = 1 $V_{pp}$ ,  $V_{cc}$  = 5V,  $R_{source}$  = 37.5 $\Omega$ ,  $F_{cSEL}$  = 0, all inputs AC coupled with 0.1 $\mu$ F, all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$  loads, referenced to 400kHz; unless otherwise noted.

| Symbol              | Parameter                                 | Conditions                   | Min | Тур  | Max | Units |

|---------------------|-------------------------------------------|------------------------------|-----|------|-----|-------|

| AV <sub>PS</sub>    | Channel Gain <sup>1</sup>                 | All PS Channels              | 5.6 | 6.0  | 6.4 | dB    |

| f <sub>1dBSPS</sub> | -1dB Bandwidth <sup>1</sup>               | All PS Channels              | 12  | 14   |     | MHz   |

| f <sub>cPS</sub>    | -3dB Bandwidth <sup>1</sup>               | All PS Channels              | 13  | 16   |     | MHz   |

| f <sub>SBPS</sub>   | Attenuation(stopband reject) <sup>1</sup> | All PS Channels at f = 54MHz | 37  | 45   |     | dB    |

| THD                 | Output Distortion (All PS channels)       | $V_{OUT} = 1.4V_{pp}$ , 7MHz |     | 0.35 |     | %     |

| X <sub>TALKPS</sub> | Crosstalk (ch-to-ch)                      | at 1MHz                      |     | -53  |     | dB    |

| SNR                 | Signal-to-Noise Ratio <sup>2</sup>        | unweighted; 100kHz to 15MHz  |     | 66   |     | dB    |

| t <sub>pdPS</sub>   | Propagation Delay                         | Delay from input to output   |     | 47   |     | ns    |

#### Notes:

- 1. 100% tested at 25°C

- 2. SNR = 20 \* log (714mV/rms noise)

## **High Definition Electrical Characteristics**

$T_c$  = 25°C,  $V_{in}$  = 1 $V_{pp}$ ,  $V_{cc}$  = 5V,  $R_{source}$  = 37.5 $\Omega$ ,  $F_{cSEL}$  = 1, all inputs AC coupled with 0.1 $\mu$ F, all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$  loads, referenced to 400kHz; unless otherwise noted

| Symbol              | Parameter                                 | Conditions                      | Min | Тур | Max | Units |

|---------------------|-------------------------------------------|---------------------------------|-----|-----|-----|-------|

| AV <sub>HD</sub>    | Channel Gain <sup>1</sup>                 | All HD Channels                 | 5.6 | 6.0 | 6.4 | dB    |

| f <sub>1dBHD</sub>  | -1dB Bandwidth <sup>1</sup>               | All HD Channels                 | 28  | 31  |     | MHz   |

| f <sub>cHD</sub>    | -3dB Bandwidth <sup>1</sup>               | All HD Channels                 | 30  | 34  |     | MHz   |

| f <sub>SBHD</sub>   | Attenuation(stopband reject) <sup>1</sup> | All HD Channels at f = 74.25MHz | 30  | 41  |     | dB    |

| THD                 | Output Distortion (all HD channels)       | $V_{OUT} = 1.4V_{pp}$ , 22MHz   |     | 0.9 |     | %     |

| X <sub>TALKHD</sub> | Crosstalk (ch-to-ch)                      | at 1MHz                         |     | -54 |     | dB    |

| SNR                 | Signal-to-Noise Ratio <sup>2</sup>        | unweighted, 100kHz to 30MHz     |     | 60  |     | dB    |

| t <sub>pdHD</sub>   | Propagation Delay                         | Delay from input to output      |     | 25  |     | ns    |

#### Notes:

- 1. 100% tested at 25°C

- 2. SNR = 20 \* log (714mV/rms noise)

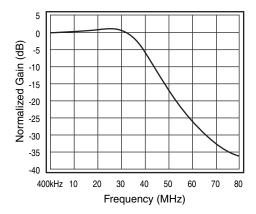

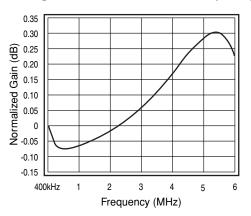

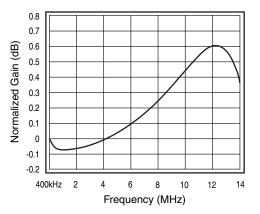

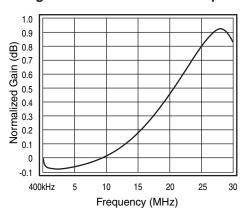

### **Typical Performance Characteristics**

$T_c$  = 25°C,  $V_{in}$  = 1 $V_{pp}$ ,  $V_{CC}$  = 5V,  $R_{source}$  = 37.5 $\Omega$ , inputs AC coupled with 0.1 $\mu$ F, all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$  loads; unless otherwise noted.

Figure 1. SD Gain vs. Frequency

Figure 3. PS Gain vs. Frequency

Figure 5. HD Gain vs. Frequency

Figure 2. SD Flatness vs. Frequency

Figure 4. PS Flatness vs. Frequency

Figure 6. HD Flatness vs. Frequency

## **Typical Performance Characteristics**

$T_c$  = 25°C,  $V_{in}$  = 1 $V_{pp}$ ,  $V_{CC}$  = 5V,  $R_{source}$  = 37.5 $\Omega$ , inputs AC coupled with 0.1 $\mu$ F, all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$  loads; unless otherwise noted.

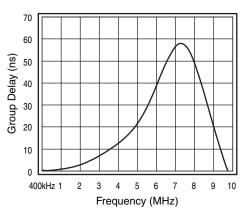

Figure 7. SD Group Delay vs. Frequency

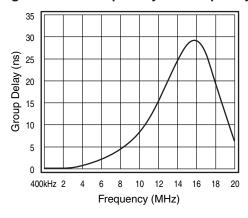

Figure 9. PS Group Delay vs. Frequency

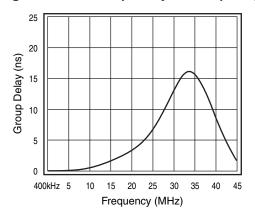

Figure 11. HD Group Delay vs. Frequency

Figure 8. Noise vs. Frequency

Figure 10. SD Differential Gain

### **Applications Information**

#### **Functional Description**

0.28V

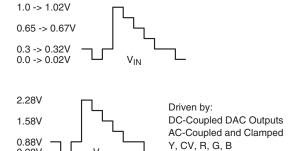

The FMS6690 Low Cost Video Filter (LCVF) provides 6dB gain (9dB optional, contact factory for further information) from input to output. In addition, the input will be slightly offset to optimize the output driver performance. The offset is held to the minimum required value to decrease the standing DC current into the load. Typical voltage levels are shown in the diagram below.

There will be a 280mV offset from the DC input level to the DC output level.  $V_{OUT}$  = 2 \*  $V_{IN}$  + 280mV

$V_{OUT}$

Figure 12. Typical Voltage Levels

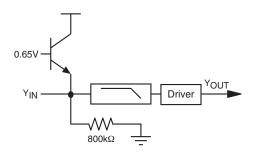

The FMS6690 provides an internal diode clamp to support AC-coupled input signals. If the input signal does not go below ground, the input clamp will not operate. This allows DAC outputs to directly drive the FMS6690 without an AC coupling capacitor. The worst-case sync tip compression due to the clamp will not exceed 7mV. The input level set by the clamp combined with the internal DC offset will keep the output within its acceptable range. When the input is AC-coupled, the diode clamp will set the sync tip (or lowest voltage) just below ground.

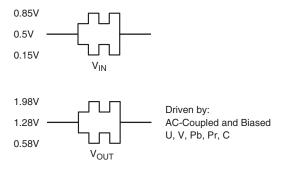

For symmetric signals like C, U, V, Cb, Cr, Pb and Pr, the average DC bias is fairly constant and the inputs can be AC-coupled with the addition of a pull-up resistor to set the DC input voltage. DAC outputs can also drive these same signals without the AC coupling capacitor. A conceptual illustration of the input clamp circuit is shown below:

Figure 13. Input Clamp Circuit

### I/O Configurations

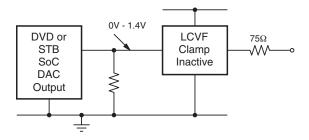

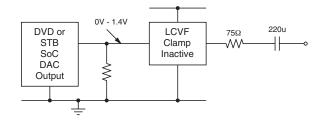

For DC-coupled DAC drive with DC-coupled outputs, use this configuration:

Figure 14. DC-coupled Inputs and Outputs

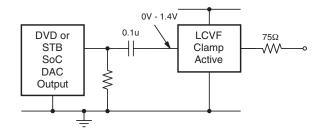

Alternatively, if the DAC's average DC output level causes the signal to exceed the range of 0V to 1.4V, it can be AC-coupled as follows:

Figure 15. AC-coupled Inputs, DC-coupled Outputs

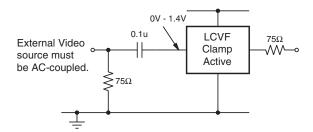

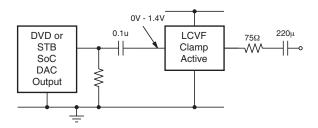

When the FMS6690 is driven by an unknown external source or a SCART switch with its own clamping circuitry, the inputs should be AC-coupled as follows:

Figure 16. SCART Configuration with DC-coupled Outputs

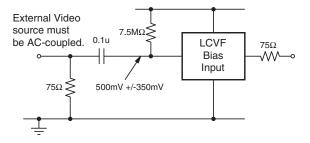

The same method can be used for biased signals with the addition of a pull-up resistor to make sure the clamp never operates. The internal pull-down resistance is  $800 k\Omega \pm 20\%$  so the external resistance should be  $7.5 M\Omega$  to set the DC level to 500mV. If a pull-up resistance less than  $7.5 M\Omega$  is desired, an external pull-down can be added such that the DC input level is set to 500mV.

Figure 17. Biased SCART with DC-coupled Outputs

The same circuits can be used with AC-coupled outputs if desired.

Figure 18. DC-coupled Inputs, AC-coupled Outputs

Figure 19. AC-coupled Inputs, AC-coupled Outputs

Figure 20. Biased SCART with AC-coupled Outputs

NOTE: The video tilt or line time distortion will be dominated by the AC-coupling capacitor. The value may need to be increased beyond  $220\mu F$  in order to obtain satisfactory operation in some applications.

#### **Power Dissipation**

The FMS6690 output drive configuration must be considered when calculating overall power dissipation. Care must be taken not to exceed the maximum die junction temperature. The following example can be used to calculate the FMS6690's power dissipation and internal temperature rise.

$$\begin{split} &T_j = T_A + P_d \bullet \Theta_{JA} \\ &\text{where } P_d = P_{CH1} + P_{CH2} + P_{CHx} \\ &\text{and } P_{CHx} = V_s \bullet I_{CH} - (V_O^2/R_L) \\ &\text{where} \\ &V_O = 2V_{in} + 0.280V \\ &I_{CH} = (I_{CC} / 6) + \ (V_O/R_L) \\ &V_{in} = RMS \ value \ of \ input \ signal \\ &I_{CC} = 60mA \end{split}$$

R<sub>L</sub> = channel load resistance

$V_s = 5V$

Board layout can also affect thermal characteristics. Refer to the *Layout Considerations* Section for more information.

#### **Layout Considerations**

General layout and supply bypassing play major roles in high frequency performance and thermal characteristics. Fairchild offers a demonstration board, FMS6690DEMO, to use as a guide for layout and to aid in device testing and characterization. The FMS6690DEMO is a 4-layer board with a full power and ground plane. Following this layout configuration will provide the optimum performance and thermal characteristics. For optimum results, follow the steps below as a basis for high frequency layout:

- Include  $10\mu F$  and  $0.1\mu F$  ceramic bypass capacitors

- Place the 10μF capacitor within 0.75 inches of the power pin

- Place the 0.1μF capacitor within 0.1 inches of the power pin

- For multi-layer boards, use a large ground plane to help dissipate heat

- For 2 layer boards, use a ground plane that extends beyond the device by at least 0.5"

- Minimize all trace lengths to reduce series inductances

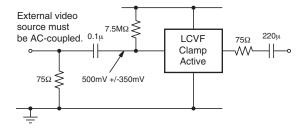

## **Typical Application Diagram**

The following circuit may be used for direct DC-coupled drive by DACs with an output voltage range of 0V to 1.4V. AC-coupled or DC-coupled outputs may be used with AC-coupled outputs offering slightly lower power dissipation.

Figure 21. Typical Application Diagram

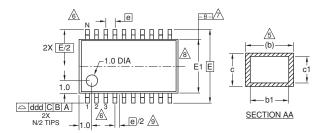

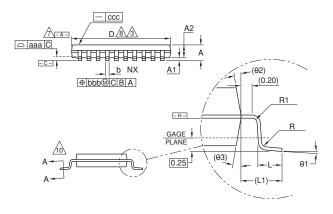

### **Mechanical Dimensions**

### 20-Lead Thin Shrink Outline Package (TSSOP)

| 133UF-20       |                |          |      |  |  |  |  |

|----------------|----------------|----------|------|--|--|--|--|

| SYMBOL         | MIN            | NOM      | MAX  |  |  |  |  |

| Α              | _              | _        | 1.10 |  |  |  |  |

| A1             | 0.05 – 0.15    |          |      |  |  |  |  |

| A2             | 0.85 0.90 0.95 |          |      |  |  |  |  |

| L              | 0.50           | 0.60     | 0.75 |  |  |  |  |

| R              | 0.09           | _        | _    |  |  |  |  |

| R1             | 0.09           | _        | _    |  |  |  |  |

| b              | 0.19           | _        | 0.30 |  |  |  |  |

| b1             | 0.19           | 0.22     | 0.25 |  |  |  |  |

| С              | 0.09           | _        | 0.20 |  |  |  |  |

| c1             | 0.09           | _        | 0.16 |  |  |  |  |

| <del>0</del> 1 | 0° – 8°        |          |      |  |  |  |  |

| L1             | 1.0 REF        |          |      |  |  |  |  |

| aaa            |                | 0.10     |      |  |  |  |  |

| bbb            |                | 0.10     |      |  |  |  |  |

| CCC            |                | 0.05     |      |  |  |  |  |

| ddd            |                | 0.20     |      |  |  |  |  |

| е              |                | 0.65 BSC |      |  |  |  |  |

| <del>0</del> 2 |                | 12° REF  |      |  |  |  |  |

| <del>0</del> 3 |                | 12° REF  |      |  |  |  |  |

| D              | 6.50           | 6.50     | 6.60 |  |  |  |  |

| E1             | 4.30           | 4.40     | 4.50 |  |  |  |  |

| Е              |                | 6.4 BSC  |      |  |  |  |  |

| е              |                | 0.65 BSC |      |  |  |  |  |

| N              |                | 20       |      |  |  |  |  |

|                |                |          |      |  |  |  |  |

TSSOP-20

#### NOTES:

- 1 All dimensions are in millimeters (angle in degrees).

- 2 Dimensioning and tolerancing per ASME Y14.5-1994.

- (a) Dimensions "D" does not include mold flash, protusions or gate burrs. Mold flash protusions or gate burrs shall not exceed 0.15 per side .

- 🛕 Dimension "E1" does not include interlead flash or protusion. Interlead flash or protusion shall not exceed 0.25 per side.

- (a) Dimension "b" does not include dambar protusion. Allowable dambar protusion shall be 0.08mm total in excess of the "b" dimension at maximum material condition. Dambar connot be located on the lower radius of the foot. Minimum space between protusion and adjacent lead is 0.07mm for 0.5mm pitch packages.

- Terminal numbers are shown for reference only.

- $\triangle$  Datums A and B to be determined at datum plane H.

- B Dimensions "D" and "E1" to be determined at datum plane —H—.

- \_\_\_\_\_\_\_ This dimensions applies only to variations with an even number of leads per side. For variation with an odd number of leads per side, the "center" lead must be coincident with the package centerline, Datum A.

- To Cross sections A A to be determined at 0.10 to 0.25mm from the leadtip.

# **Ordering Information**

| Model   | Part Number   | Lead Free | Package  | Container | Pack<br>Qty |

|---------|---------------|-----------|----------|-----------|-------------|

| FMS6690 | FMS6690MTC20  | Yes       | TSSOP-20 | Rail      | 94          |

| FMS6690 | FMS6690MTC20X | Yes       | TSSOP-20 | Reel      | 2500        |

Temperature range for all parts: 0°C to 70°C.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.