STN LCD Driver Panasonic

# MN863830EFH

# 240-Output STN Segment Driver

#### Overview

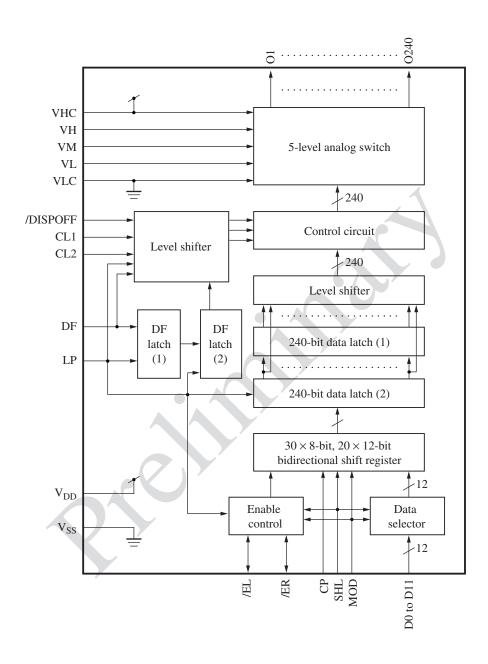

The MN863830EFH is a 240-output segment driver IC for dot matrix STN LCD panels. It latches 8-bit or 12-bit parallel data transferred from an LCD controller and generates the LCD drive signals.

In combination with an LCD common driver IC, MN8637 series, this IC is optimal for implementing low-power LCD modules. Since this IC also provides an LCD drive voltage compensation function, it can implement high-quality LCD display modules with minimal crosstalk. It supports both color and monochrome displays.

#### ■ Features

- Supports LCD drive voltages up to 6.0 V.

- Provides 240 LCD drive outputs.

- Provides an LCD drive voltage compensation function to implement high-quality LCD display modules with minimal crosstalk.

- Inverts the LCD drive voltage by signal alternation.

- Provides 5 LCD drive voltage input pins: VHC, VH, VM, VL, and VLC

- Built-in voltage conversion block (level shifter) allows interfacing with LCD controllers with supply voltages in the range from 2.5 V to 5.5 V.

- Built-in bidirectional shift register allows arbitrary direction of the output data transfer and allows easy mounting in large-screen applications.

- Supports multistage cascade connection to drive high-resolution LCD panels.

- Supports both 8-bit and 12-bit parallel input mode.

- The 8-bit and 12-bit parallel input modes allow data rates 1/8 or 1/12 of those required with conventional serial transfer devices for lower power consumption.

- Provides a power saving function, in which all but one driver are set to standby mode and disable to input display data, for even lower power consumption in LCD modules with multistage cascade connection.

#### Applications

• Word processors, PDAs, and other portable information terminals

Publication date: May 2002 SDF00016BEM 1

## ■ Block Diagram

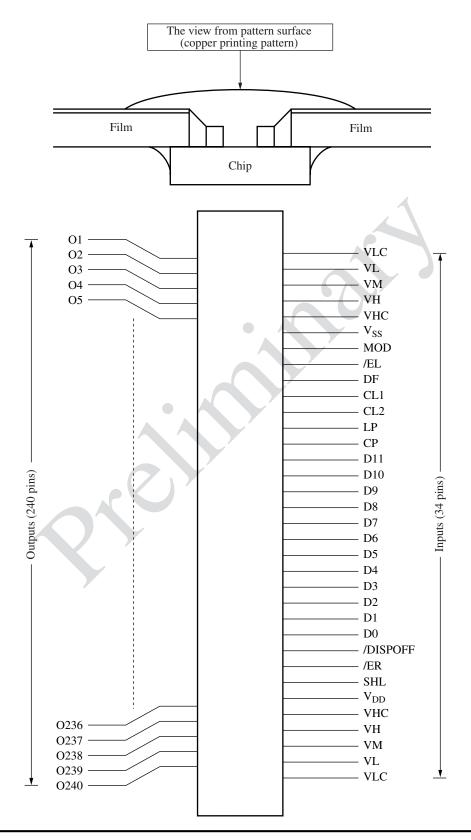

## ■ Pin Arrangement

# ■ Pin Descriptions

| Pin No.           | I/O          | Function                                          | Description                                                                                                                                                                                                                                                                                         |

|-------------------|--------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0 to D11         | I            | Display data<br>inputs<br>(12 bits)               | Parallel input of display data in 8-bit or 12-bit units.  • In 8-bit parallel input mode, the 8 pins D0 to D7 are used for data input. The 4 pins D8 to D11 should be tied to V <sub>DI</sub> or V <sub>SS</sub> .  • In 12-bit parallel input mode, the 12 pins D0 to D11 are used for data input. |

| O1 to O240        | 0            | LCD drive outputs                                 | These pins output the LCD drive voltages.                                                                                                                                                                                                                                                           |

| SHL               | I            | Shift direction selection                         | Switches the shift register data shift direction, and the /ER and /EL pin I/O mode.                                                                                                                                                                                                                 |

| СР                | I            | Shift clock input                                 | The shift register transfer clock input. The shift register operates on the falling edge of this signal.                                                                                                                                                                                            |

| LP                | I            | Latch signal input                                | The DF signal and the shift register data are latched on the falling edge of this signal, and the latched data is output.                                                                                                                                                                           |

| /DISPOFF          | I            | Display off input                                 | The LCD drive outputs output the VM level regardless of the data while this pin is low.                                                                                                                                                                                                             |

| CL1               | I            | LCD compensation voltage<br>(VHC and VLC) control | Controls the period for the LCD compensation voltage (VHC and VLC) output to the LCD drive output pins according to the display data.                                                                                                                                                               |

| CL2               | I            | LCD compensation voltage (VM) control             | Controls the period for the LCD compensation voltage (VM) output to the LCD drive output pins according to the display data.                                                                                                                                                                        |

| DF                | I            | Alternation signal input                          | Performs signal alternation for the LCD drive voltage.                                                                                                                                                                                                                                              |

| $V_{\mathrm{DD}}$ | Power supply | Logic system power supply                         | Power supply used for the logic circuits                                                                                                                                                                                                                                                            |

| V <sub>SS</sub>   | Power supply | GND                                               | GND                                                                                                                                                                                                                                                                                                 |

| VH (2 pins)       | Power supply | Drive power supply                                | LCD drive power supply                                                                                                                                                                                                                                                                              |

| VL (2 pins)       | Power supply | Drive power supply                                | LCD drive power supply                                                                                                                                                                                                                                                                              |

| VM (2 pins)       | Power supply | Drive power supply                                | LCD drive power supply, (LCD compensation power supply)                                                                                                                                                                                                                                             |

| VHC (2 pins)      | Power supply | Drive power supply                                | LCD drive power supply, (LCD compensation power supply) Used as the power supply for the LCD drive circuit.                                                                                                                                                                                         |

| VLC (2 pins)      | Power supply | Drive power supply                                | LCD drive power supply, (LCD compensation power supply) Connected internally to the $V_{SS}$ pin.                                                                                                                                                                                                   |

| /EL               | I/O          | Enable signal input and output                    | Data input/output for the chip enable signal                                                                                                                                                                                                                                                        |

| /ER               | I/O          | Enable signal input and output                    | Data input/output for the chip enable signal                                                                                                                                                                                                                                                        |

| MOD               | I            | Mode selection<br>(with a pull-up<br>resistor)    | MOD  Low 8-bit parallel input  High 12-bit parallel input                                                                                                                                                                                                                                           |

Panasonic MN863830EFH

#### ■ Function Descriptions

#### 1. Control circuit for bidirectional shift register

This IC includes two circuits, an enable control circuit and a data selector, that control the built-in bidirectional shift register.

#### 1.1 Enable control circuit

This circuit consists of a base-30 counter circuit (for 8-bit parallel input mode), a base-20 counter circuit (for 12-bit parallel input mode), and a control circuit for the chip enable I/O circuit.

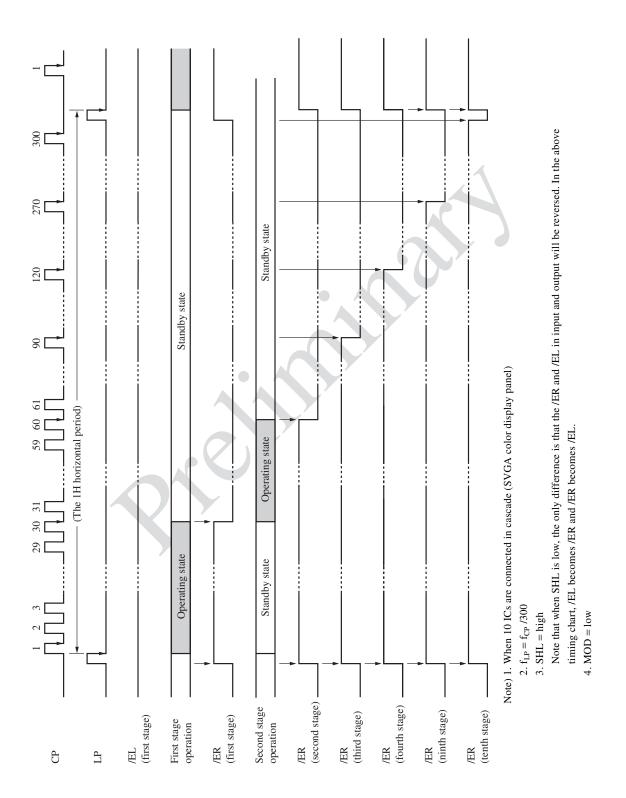

This counter counts clock pulses and outputs a carry on the falling edge of the 30th clock cycle (in 8-bit parallel input mode) or the 20th clock cycle (in 12-bit parallel input mode). This corresponds to the completion of the shift register data shift operation. This carry stops the data shift clock internally to the IC, and places the counter and the shift register in the stopped state. When LP signal goes high, the base-30 and base-20 counters are reset and set to the counter wait state (standby state).

The standby state is not cleared until the chip enable I/O signal (/EL and /ER) that corresponds to shift direction goes low. When that chip enable signal goes low, the data shift clock and counter start operating again.

When this IC is connected in the serial cascade form, the counter carry signal is used as the chip enable signal for the driver IC in the next stage. The result of this operation is that at the completion of each 30 clock cycles (in 8-bit parallel input mode) or 20 clock cycles (in 12-bit parallel input mode), the next driver IC in sequence goes to the active state and the total power consumption of the whole LCD panel is reduced.

#### 1.2 Data selector circuit

This circuit determines, based on the state of the SHL pin, the data shift direction of the internal shift register and the I/O mode of the chip enable I/O pin as shown in tables 1-a and 1-b.

2. 30 × 8-bit (8-bit parallel input mode)/20 × 12-bit (12-bit parallel input mode) bidirectional shift register The IC internal 8-bit parallel 30-stage and 12-bit parallel 20-stage bidirectional shift registers operate on the falling edge of the clock pulse.

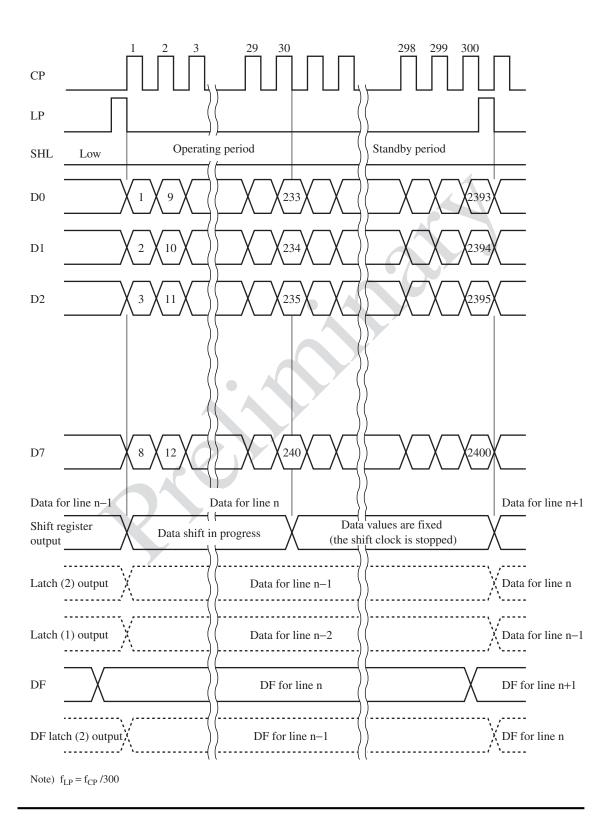

In 8-bit parallel input mode, since the input data is divided into 8-bit parallel units, the shifting of the 240 output units of data requires 30 clock cycles. (See Timing Charts 1 and 3.)

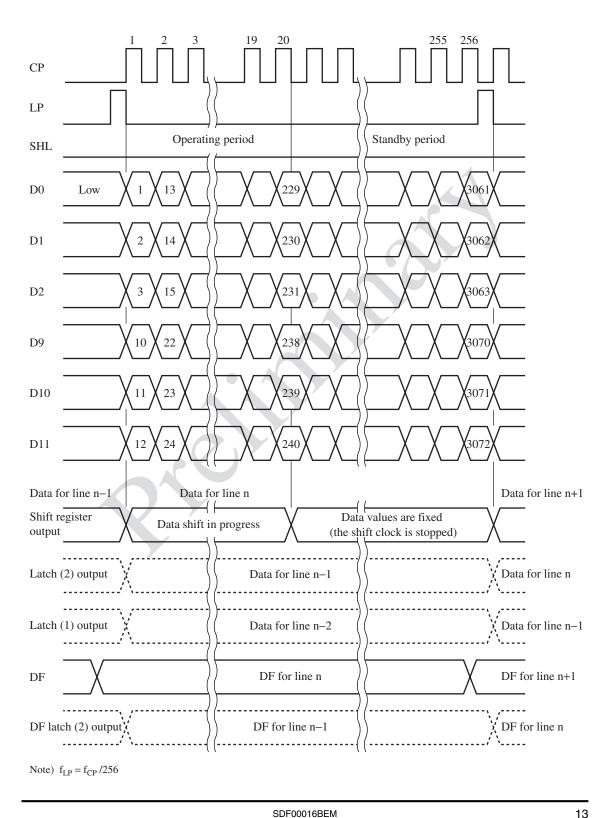

In 12-bit parallel input mode, since the input data is divided into 12-bit parallel units, the shifting of the 240 output units of data requires 20 clock cycles. (See Timing Charts 2 and 4.)

The shift direction is selected by the SHL pin as shown in tables 1-a and 1-b.

#### 3. 240-bit data Latch (2)

The 240-bit data latch (2) holds the 240 bits of data acquired by the shift register for a single horizontal scan period (1H).

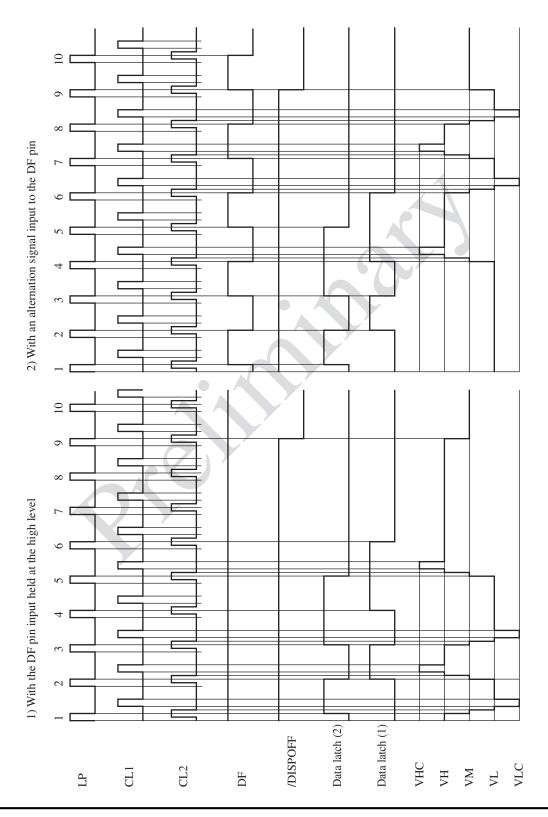

Data is latched on the falling edge of the LP signal, which is the start pulse for the horizontal scan period, held for 1H, and the next data is latched on the next falling edge on the LP signal.

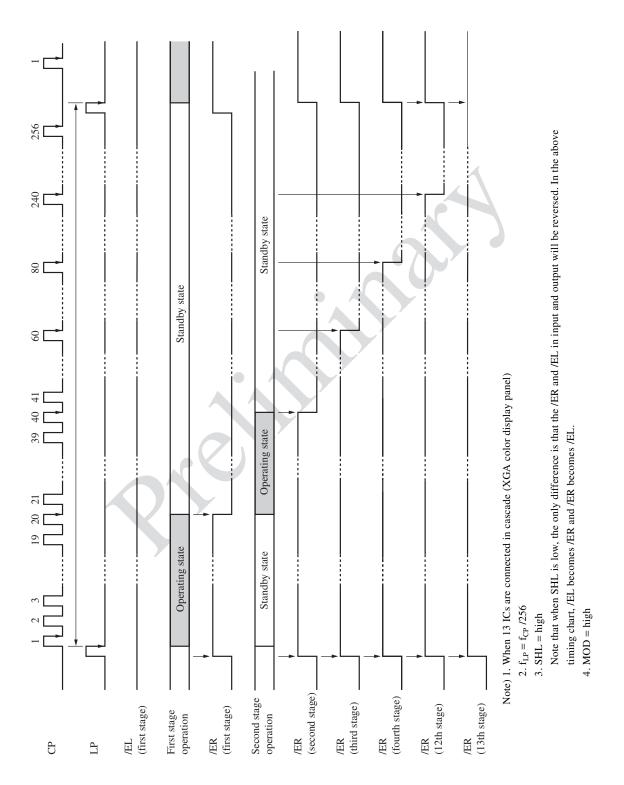

Timing Chart 3 shows the shift register and latch operation for the first stage segment driver when multiple driver ICs are connected in series and operated in 8-bit parallel mode.

Also, Timing Chart 4 shows the shift register and latch operation for the first stage segment driver when multiple driver ICs are connected in series and operated in 12-bit parallel mode.

MN863830EFH Panasonic

## ■ Function Descriptions (continued)

#### 4. Level shifters

The level shifters convert levels from the logic circuit signal levels ( $V_{DD} = high$ ,  $V_{SS} = low$ ) to the signal levels (VHC = high, VLC =  $V_{SS} = low$ ) used by the LCD drive circuits, such as the analog switches. The IC includes two types of level shifters, one is for 240 bits display data and the other is for control signals.

#### 240-bit data latch (1)

The 240-bit data latch (1) holds the 240 bits of display data acquired by the 240-bit data latch (2) for an additional 1H. Thus the 240-bit data latch (1) holds the data for the previous line from the display data currently being scanned. Data is latched on the falling edge of the LP signal, held for 1H, and the next data is latched on the next falling edge on the LP signal.

#### 5-level analog switch

The 5-level analog switch is controlled by the control circuit and selects one of the 5 drive voltages (VHC, VH, VM, VL, and VLC), and outputs the selected levels to the 240 LCD drive output pins.

#### 7. DF latch (1)

The DF latch (1) holds the DF data for a single horizontal scan period (1H).

Data is latched on the rising edge of the LP signal, which is the start pulse for the horizontal scan period, held for 1H, and the next data is latched on the next rising edge on the LP signal.

#### 8. DF latch (2)

The DF latch (2) latches the data acquired by the DF latch (1) on the falling edge of the LP signal, holds that data for 1H, and latches the next data on the next falling edge of the LP signal.

(Timing Charts 3 and 4 show this latch operation.)

#### 9. Control circuit

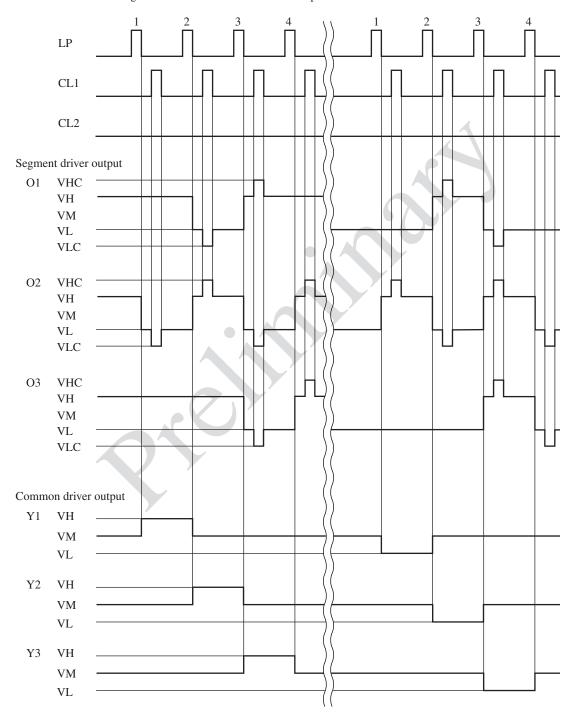

The voltage selected by the 5-level analog switch is determined by the 240-bit data latch (1), the 240-bit data latch (2), the /DISPOFF signal, the CL1 signal, the CL2 LP signal, the DF input, and DF latch (2).

When the /DISPOFF signal is low, the VM level of the LCD drive voltage is selected, regardless of the values of the data latches (1) and (2) outputs, the DF input, the DF latch (2) output, and the high/low state of the CL1 and  $CL2 \cdot \overline{LP}$  signals. When the /DISPOFF signal is low, the VM level is output from the common driver, and the voltage applied to all of the dots becomes 0 V, since the same voltage is applied. This results in a completely blank display.

When either the CL1 or CL2 $\cdot$ LP signal is high, the IC switches the LCD drive voltage and the LCD compensation voltage by comparing the data latch (1) and (2) outputs with the DF input and the DF latch (2) output.

Table 2 lists the LCD drive output pin output voltage levels according to the data latch (1) output (Qn-1), the data latch (2) output (Qn), the CL1 and  $CL2 \cdot \overline{LP}$  signals, the DF input, the DF latch (2) output (DFn-1), and the /DISPOFF signal.

Figure 1 presents examples of the LCD drive output pin waveform as driven according to table 2, which appears later. Two examples are presented, one with the DF pin held high, and the other with an LCD alternation signal input to the DF pin.

Table 1-a. Data shift control

In 8-bit parallel input mode (MOD = low)

|     | <b>(55</b> | <i>(</i> =. |    |               |      | Shift clock |     |            |  |     |    |

|-----|------------|-------------|----|---------------|------|-------------|-----|------------|--|-----|----|

| SHL | /ER        | /EL         |    |               | 1    | 2           | ••• | n          |  | 29  | 30 |

| Low | Input      | Output      | D7 | $\rightarrow$ | O240 | O232        |     | O8(30-n)+8 |  | O16 | O8 |

|     |            |             | D6 | $\rightarrow$ | O239 | O231        |     | O8(30-n)+7 |  | O15 | O7 |

|     |            |             | D5 | $\rightarrow$ | O238 | O230        |     | O8(30-n)+6 |  | O14 | O6 |

|     |            |             | D4 | $\rightarrow$ | O237 | O229        |     | O8(30-n)+5 |  | O13 | O5 |

Panasonic MN863830EFH

# ■ Function Descriptions (continued)

Table 1-a. Data shift control (continued)

In 8-bit parallel input mode (MOD = low)

|      |        |          |    |               |      |      |       | •          | •       |      |      |

|------|--------|----------|----|---------------|------|------|-------|------------|---------|------|------|

|      | (55    | <b>/</b> |    |               |      |      | Shift | clock      |         |      |      |

| SHL  | /ER    | /EL      |    |               | 1    | 2    | •••   | n          | •••     | 29   | 30   |

| Low  | Input  | Output   | D3 | $\rightarrow$ | O236 | O228 |       | O8(30-n)+4 |         | O12  | O4   |

|      |        |          | D2 | $\rightarrow$ | O235 | O227 |       | O8(30-n)+3 | •••     | O11  | O3   |

|      |        |          | D1 | $\rightarrow$ | O234 | O226 |       | O8(30-n)+2 |         | O10  | O2   |

|      |        |          | D0 | $\rightarrow$ | O233 | O225 |       | O8(30-n)+1 |         | O9   | O1   |

| High | Output | Input    | D7 | $\rightarrow$ | O1   | O9   |       | O8n-7      |         | O225 | O233 |

|      |        |          | D6 | $\rightarrow$ | O2   | O10  |       | O8n-6      | •••     | O226 | O234 |

|      |        |          | D5 | $\rightarrow$ | O3   | O11  |       | O8n-5      | •••     | O227 | O235 |

|      |        |          | D4 | $\rightarrow$ | O4   | O12  |       | O8n-4      | <b></b> | O228 | O236 |

|      |        |          | D3 | $\rightarrow$ | O5   | O13  |       | O8n-3      |         | O229 | O237 |

|      |        |          | D2 | $\rightarrow$ | O6   | O14  |       | O8n-2      |         | O230 | O238 |

|      |        |          | D1 | $\rightarrow$ | Ο7   | O15  |       | O8n-1      |         | O231 | O239 |

|      |        |          | D0 | $\rightarrow$ | O8   | O16  |       | O8n        | ,       | O232 | O240 |

|      |        |          |    |               |      |      |       |            |         |      |      |

Table 1-b. Data shift control

In 12-bit parallel input mode (MOD = high)

|      | <b>(55</b> | <i>(</i> =. |     |               |      |      | Shift | clock        |     |      |      |

|------|------------|-------------|-----|---------------|------|------|-------|--------------|-----|------|------|

| SHL  | /ER        | /EL         |     |               | 1    | 2    |       | n            | ••• | 19   | 20   |

| Low  | Input      | Output      | D11 | $\rightarrow$ | O240 | O228 |       | O12(20-n)+12 |     | O24  | O12  |

|      |            |             | D10 | $\rightarrow$ | O239 | O227 |       | O12(20-n)+11 |     | O23  | O11  |

|      |            |             | D9  | $\rightarrow$ | O238 | O226 |       | O12(20-n)+10 |     | O22  | O10  |

|      |            |             | D8  | $\rightarrow$ | O237 | O225 |       | O12(20-n)+9  |     | O21  | O9   |

|      |            |             | D7  | $\rightarrow$ | O236 | O224 |       | O12(20-n)+8  |     | O20  | O8   |

|      |            |             | D6  | $\rightarrow$ | O235 | O223 |       | O12(20-n)+7  |     | O19  | O7   |

|      |            |             | D5  | $\rightarrow$ | O234 | O222 |       | O12(20-n)+6  |     | O18  | O6   |

|      |            |             | D4  | $\rightarrow$ | O233 | O221 |       | O12(20-n)+5  |     | O17  | O5   |

|      |            |             | D3  | $\rightarrow$ | O232 | O220 |       | O12(20-n)+4  |     | O16  | O4   |

|      |            |             | D2  | $\rightarrow$ | O231 | O219 |       | O12(20-n)+3  |     | O15  | O3   |

|      |            |             | D1  | $\rightarrow$ | O230 | O218 |       | O12(20-n)+2  |     | O14  | O2   |

|      |            |             | D0  | $\rightarrow$ | O229 | O217 | •••   | O12(20-n)+1  | ••• | O13  | O1   |

| High | Output     | Input       | D11 | $\rightarrow$ | O1   | O13  |       | O12n-11      |     | O217 | O229 |

|      |            |             | D10 | $\rightarrow$ | O2   | O14  |       | O12n-10      |     | O218 | O230 |

|      |            |             | D9  | $\rightarrow$ | O3   | O15  |       | O12n-9       |     | O219 | O231 |

|      |            |             | D8  | $\rightarrow$ | O4   | O16  | •••   | O12n-8       | ••• | O220 | O232 |

|      |            |             | D7  | $\rightarrow$ | O5   | O17  | •••   | O12n-7       | ••• | O221 | O233 |

|      |            |             | D6  | $\rightarrow$ | O6   | O18  |       | O12n-6       |     | O222 | O234 |

|      |            |             | D5  | $\rightarrow$ | O7   | O19  | •••   | O12n-5       | ••• | O223 | O235 |

|      |            |             | D4  | $\rightarrow$ | O8   | O20  | •••   | O12n-4       | ••• | O224 | O236 |

|      |            |             | D3  | $\rightarrow$ | O9   | O21  |       | O12n-3       |     | O225 | O237 |

|      |            |             | D2  | $\rightarrow$ | O10  | O22  | •••   | O12n-2       | ••• | O226 | O238 |

|      |            |             | D1  | $\rightarrow$ | O11  | O23  | •••   | O12n-1       | ••• | O227 | O239 |

|      |            |             | D0  | $\rightarrow$ | O12  | O24  |       | O12n         |     | O228 | O240 |

# ■ Function Descriptions (continued)

Table 2. LCD drive output pin output voltage

| /DISPOFF | CL1  | CL2 · LP | DF latch (2) output DFn-1 | DF input | Data latch (1) output Qn-1 | Data latch (2)<br>output Qn | LCD drive output<br>O1 to O240 |

|----------|------|----------|---------------------------|----------|----------------------------|-----------------------------|--------------------------------|

| High     | High | Low      | High                      | High     | High                       | High                        | VL                             |

| C        |      |          |                           |          |                            | Low                         | VHC                            |

|          |      |          |                           |          | Low                        | High                        | VLC                            |

|          |      |          |                           |          |                            | Low                         | VH                             |

|          |      |          |                           | Low      | High                       | High                        | VHC                            |

|          |      |          |                           |          |                            | Low                         | VL                             |

|          |      |          |                           |          | Low                        | High                        | VH                             |

|          |      |          |                           |          |                            | Low                         | VLC                            |

|          |      |          | Low                       | High     | High                       | High                        | VLC                            |

|          |      |          |                           |          |                            | Low                         | VH                             |

|          |      |          |                           |          | Low                        | High                        | VL                             |

|          |      |          |                           |          |                            | Low                         | VHC                            |

|          |      |          |                           | Low      | High                       | High                        | VH                             |

|          |      |          |                           |          |                            | Low                         | VLC                            |

|          |      |          |                           | • A      | Low                        | High                        | VHC                            |

| Low      |      |          |                           |          | ,                          | Low                         | VL                             |

|          | Low  | High     | High                      | High     | High                       | High                        | VL                             |

|          |      |          |                           |          |                            | Low                         | VM                             |

|          |      |          |                           |          | Low                        | High                        | VM                             |

|          |      |          |                           |          |                            | Low                         | VH                             |

|          |      |          |                           | Low      | High                       | High                        | VM                             |

|          |      |          | <b>\</b> \                |          |                            | Low                         | VL                             |

|          |      |          |                           |          | Low                        | High                        | VH                             |

|          |      | PK       |                           |          |                            | Low                         | VM                             |

|          |      |          | Low                       | High     | High                       | High                        | VM                             |

|          |      |          |                           | _        |                            | Low                         | VH                             |

|          |      |          |                           |          | Low                        | High                        | VL                             |

|          |      |          |                           |          |                            | Low                         | VM                             |

|          | )    |          |                           | Low      | High                       | High                        | VH                             |

|          |      |          |                           |          |                            | Low                         | VM                             |

|          |      |          |                           |          | Low                        | High                        | VM                             |

|          |      |          |                           |          |                            | Low                         | VL                             |

|          |      | Low      | *                         | High     | *                          | High                        | VL                             |

|          |      |          |                           |          |                            | Low                         | VH                             |

|          |      |          |                           | Low      |                            | High                        | VH                             |

|          |      |          |                           |          |                            | Low                         | VL                             |

| Low      | *    | *        | *                         | *        | *                          | *                           | VM                             |

Note) 1. \*: Don't care

- 2. The timing charts for the IC blocks are presented on the following pages.

- 3. The IC is specified to operate as follows: when the DF input is high, the output is inverted with respect to the actual input data.

- 4. To provide correct display, either the input data must be inverted, or an input to the DF pin that is inverted with respect to that of the common driver must be provided.

# ■ Function Descriptions (continued)

Figure 1. LCD drive output waveform examples

## ■ Timing Charts

1. Counter and chip enable pins (8-bit parallel input mode)

- Timing Charts (continued)

- 2. Counter and chip enable pins (12-bit parallel input mode)

3. Shift register and latch operation (SVGA LCD panel)

4. Shift register and latch operation (XGA LCD panel)

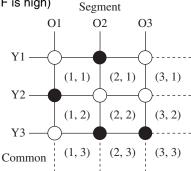

5. Segment and common driver LCD output waveforms (when /DISPOFF is high)

MN863830EFH Segment and Common Driver LCD Output Waveforms

6. LCD display and LCD applied voltage waveforms (when /DISPOFF is high)

When the drive outputs shown in section 5 are applied, if the display is normally white, the display will be shown in the right figure.

If the display is normally black, then the display will be set up for black/white reversed display. The waveforms of the voltages applied to (1,1) and (2,3) dots in the right figure are shown below.

Note that the applied voltages are referenced to the common side drive voltage VM, and therefore displayed as  $V_{COM}$ – $V_{SEG}$ .

$$VLCD = V_{COM} - V_{SEG}$$

Note) 1. When the LCD voltage applied to a dot is ±VLCD, it will be displayed as black in normally white mode and as white in normally black mode.

Since the drive waveform is dulled at the segment drive waveform transition and the actual voltage drops, this IC applies the compensation voltage at the drive waveform transition to compensate the actual voltage.

### ■ LCD Drive Voltage Names and Relationships (Reference)

The figure presents the LCD drive voltage provided by this IC and the MN8637 series common drivers, and the relationships between those voltages.

Logic supply voltage Segment LCD Segment LCD Common LCD Common LCD drive waveforms drive voltage drive waveforms Segment/common drive voltage (MN863830/MN8637) (MN863830) (MN8637) VH(= 32 V)VHC (= 4.2 V) $V_{DD}$  (= 3.0 V to 5.5 V) — VH (= 3.9 V) VM (= 2.1 V)VL = (= 0.3 V)----- VLC (=  $V_{SS} = 0 \text{ V}$ ) (/DISPOFF = high)VL(=-27.8 V)

#### ■ Electrical Characteristics

### 1. Absolute Maximum Ratings at $V_{SS} = 0 \text{ V}$ , $T_a = 25^{\circ}\text{C}$

| _                     |                |                               |      |

|-----------------------|----------------|-------------------------------|------|

| Parameter             | Symbol         | Rating                        | Unit |

| Supply voltage 1      | $V_{DD}$       | - 0.3 to +7.0                 | V    |

| Supply voltage 2      | VHC            | - 0.3 to +7.0                 | V    |

| Drive voltage         | V <sub>n</sub> | - 0.3 to VHC+0.3              | V    |

| Input voltage         | VIN            | - 0.3 to V <sub>DD</sub> +0.3 | V    |

| Operating temperature | Topr           | -20 to +75                    | °C   |

| Storage temperature   | $T_{stg}$      | -40 to +125                   | °C   |

- Note) 1. The absolute maximum ratings are limiting values for applied stresses below which the chip will not be destroyed. Operation is not guaranteed within these ranges.

- 2. These ratings are guarantees that apply when the standard Matsushita packages are used.

- 3. The term  $V_n$  above refers to VHC, VH, VM, VL, and VLC. These must be set up so that the following conditions hold:  $VHC \ge VH \ge VLC \ge V_{SS}$ .

- 4. When power is first applied, certain voltage application sequences may result in large currents flowing in this IC and permanent damage to the IC. To prevent this, always apply the logic system power supply levels ( $V_{DD}$  and  $V_{SS}$ ) first, and only after those levels are established apply the LCD drive system power supply levels. Note that the conditions in note 3 above must be met at all times during this process.

## 2. Operating Conditions at $V_{SS} = 0 \text{ V}$ , $T_a = -20 ^{\circ}\text{C}$ to $75 ^{\circ}\text{C}$

| Parameter      | Symbol          | Conditions | Min     | Тур     | Max | Unit |

|----------------|-----------------|------------|---------|---------|-----|------|

| Supply voltage | V <sub>DD</sub> |            | 2.5     | 3.3     | 5.5 | V    |

| Drive voltage  | VHC             |            | 3.0     | 4.2     | 6.0 | V    |

| Drive voltage  | VH              |            | VHC-0.7 | VHC-0.3 | VHC | V    |

| Drive voltage  | VM              |            | VL      | _       | VH  | V    |

| Drive voltage  | VL              |            | 0       | 0.3     | 0.7 | V    |

# 2. Operating Conditions at $V_{SS} = 0$ V, $T_a = -20$ °C to 75°C (continued)

| Parameter                               | Symbol                          | Conditions                                     | Min | Тур | Max  | Unit |

|-----------------------------------------|---------------------------------|------------------------------------------------|-----|-----|------|------|

| Clock frequency                         | $f_{cp}$                        | $V_{DD} = 2.5 \text{ V to } 4.5 \text{ V}$     |     | _   | 30   | MHz  |

|                                         |                                 | $V_{\rm DD} = 4.5 \text{ V to } 5.5 \text{ V}$ | _   | _   | 55   | MHz  |

| Digital signal input pin capacitance †1 | C <sub>in</sub>                 | At 1 MHz                                       | _   | 6   | _    | pF   |

| Rise and fall time for CP, LP,          | t <sub>r</sub> , t <sub>f</sub> | 2.5 V to 4.5 V                                 | _   | _   | 4 †2 | ns   |

| and D0 to D11                           |                                 | 4.5 V to 5.5 V                                 | _   | _   | 3 †2 | ns   |

Note) 1. †1: CP, D0 to D11

†2: The following condition must be met:  $t_r,\,t_f\!\!\leq\!\!1/2(1/f\!\!-\!\!2t_w)$

Here, f is the frequency used and t<sub>w</sub> is the minimum pulse width.

- 2. The VLC drive voltage is shorted to  $V_{SS}$  internally to the IC. Thus VLC =  $V_{SS}$ .

- 3. Connect directly each of the multiple drive supply pins of VHC, VH, VM, VL, and VLC.

## 3. DC Characteristics at $V_{SS} = 0$ V, $V_{DD} = 2.5$ V to 5.5 V, $T_a = -20^{\circ}\text{C}$ to $+75^{\circ}\text{C}$

| Parameter                                             | Symbol           | Conditions                                                                          | Min                  | Тур | Max                 | Unit |

|-------------------------------------------------------|------------------|-------------------------------------------------------------------------------------|----------------------|-----|---------------------|------|

| Operating supply current                              | I <sub>DD</sub>  | $f_{CP} = 20 \text{ MHz}$<br>$f_{Dn} = 10 \text{ MHz}$<br>$f_{LP} = 36 \text{ kHz}$ |                      | 2   | 6                   | mA   |

| Quiescent supply current (12-bit parallel input mode) | I <sub>SS1</sub> | In the clock stopped state with MOD = open                                          | _                    | _   | 100                 | μA   |

| Quiescent supply current (8-bit parallel input mode)  | I <sub>SS2</sub> | In the clock stopped state with MOD = low                                           | _                    | _   | 500                 | μΑ   |

| 1) Input Pins (SHL, CP, LP, CL                        | 1, CL2, D        | F, D0 to D11, /DISPOFF)                                                             |                      |     |                     |      |

| High-level input voltage                              | V <sub>IH1</sub> |                                                                                     | $0.7 \times V_{DD}$  | _   | $V_{\mathrm{DD}}$   | V    |

| Low-level input voltage                               | $V_{IL1}$        |                                                                                     | 0                    | _   | $0.3 \times V_{DD}$ | V    |

| Input leakage current                                 | $I_{LI1}$        |                                                                                     | -10                  | _   | 10                  | μΑ   |

| 2) Input with Pull-up Resistor Pi                     | ns (MOD)         | )                                                                                   |                      |     |                     |      |

| High-level input voltage                              | V <sub>IH2</sub> |                                                                                     | $0.7 \times V_{DD}$  | _   | V <sub>DD</sub>     | V    |

| Low-level input voltage                               | V <sub>IL2</sub> |                                                                                     | 0                    | _   | $0.3 \times V_{DD}$ | V    |

| Pull-up resistance                                    | R <sub>PU2</sub> | $V_{DD} = 3.3 \text{ V, MOD} = 0 \text{ V}$                                         | 30                   | 100 | 300                 | ΚΩ   |

| 3) I/O Pins (/ER, /EL)                                |                  |                                                                                     |                      |     |                     |      |

| High-level input voltage                              | V <sub>IH3</sub> |                                                                                     | $0.7 \times V_{DD}$  | _   | V <sub>DD</sub>     | V    |

| Low-level input voltage                               | V <sub>IL3</sub> |                                                                                     | 0                    | _   | $0.3 \times V_{DD}$ | V    |

| Input leakage current                                 | I <sub>LI3</sub> |                                                                                     | -10                  | _   | 10                  | μΑ   |

| High-level output voltage                             | V <sub>OH3</sub> | $I_{OH} = -0.5 \text{ mA}$                                                          | V <sub>DD</sub> -0.5 | _   | _                   | V    |

| Low-level output voltage                              | V <sub>OL3</sub> | $I_{OL} = 0.5 \text{ mA}$                                                           |                      | _   | 0.5                 | V    |

| Output leakage current                                | $I_{LO3}$        |                                                                                     | -10                  | _   | 10                  | μΑ   |

■ Electrical Characteristics at  $V_{SS} = 0$  V,  $V_{DD} = 2.5$  V to 5.5 V,  $T_a = -20$ °C to +75°C (continued) 3. DC Characteristics at  $V_{SS} = 0$  V,  $V_{DD} = 2.5$  V to 5.5 V,  $T_a = -20$ °C to +75°C (continued)

| Parameter                         | Symbol           | Condition                        | s               | Min                    | Тур        | Max                  | Unit     |

|-----------------------------------|------------------|----------------------------------|-----------------|------------------------|------------|----------------------|----------|

| 4) LCD Drive Outputs (O1 to O     | 240)             |                                  | V <sub>SS</sub> | = 0 V, V <sub>DD</sub> | = 2.5 V, T | $G_a = -20^{\circ}C$ | to +75°C |

| Output on resistance              | R <sub>ON</sub>  | VHC = 4.2 V                      | VHC             | _                      | 450        | 900                  | Ω        |

|                                   |                  | VH = 3.9 V                       | VH              | _                      | 450        | 900                  |          |

|                                   |                  | VM = 2.1 V                       | VM              | _                      | 450        | 900                  |          |

|                                   |                  | VL = 0.3 V                       | VL              | _                      | 450        | 900                  |          |

|                                   |                  | VLC = 0.0 V                      | VLC             | _                      | 450        | 900                  |          |

|                                   |                  | $V_n - V_O = 0.5 \text{ V}$      |                 |                        |            |                      |          |

|                                   |                  | V <sub>O</sub> : Applied voltage |                 |                        | 4          |                      |          |

|                                   |                  | of O1 to O240                    |                 |                        |            |                      |          |

| Output on resistance              | R <sub>ON1</sub> | VHC = 4.2 V                      |                 | _                      |            | 200                  | Ω        |

| Variations between drive voltages |                  | VH = 3.9 V                       |                 | A                      |            | \                    |          |

| Output on resistance              | R <sub>ON2</sub> | VM = 2.1 V                       |                 |                        | -          | 200                  | Ω        |

| Variations between pins           |                  | VL = 0.3 V                       |                 | 6/                     |            |                      |          |

|                                   |                  | VLC = 0.0 V                      |                 |                        |            |                      |          |

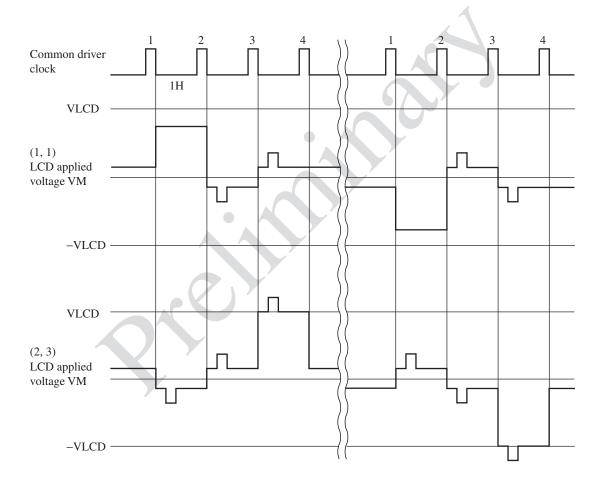

# 4. AC Characteristics at $V_{SS}=0$ V, $V_{DD}=2.5$ V to 5.5 V, $T_a=-20^{\circ}C$ to +75°C

| Parameter            | Symbol           | Condition | ons                 | Min  | Тур | Max | Unit |

|----------------------|------------------|-----------|---------------------|------|-----|-----|------|

|                      |                  |           | V <sub>DD</sub> (V) |      |     |     |      |

| CP cycle time        | t <sub>p</sub>   |           | 2.5 to 4.5          | 33.3 | _   | _   | ns   |

|                      |                  |           | 4.5 to 5.5          | 18   | _   | _   |      |

| CP high-level period | t <sub>wcH</sub> |           | 2.5 to 4.5          | 13   | _   | _   | ns   |

|                      |                  |           | 4.5 to 5.5          | 6    | _   | _   |      |

| CP low-level period  | t <sub>wcL</sub> |           | 2.5 to 4.5          | 13   | _   | _   | ns   |

|                      |                  |           | 4.5 to 5.5          | 6    | _   | _   |      |

| LP high-level period | t <sub>wlH</sub> |           | 2.5 to 5.5          | 40   | _   | _   | ns   |

| LP setup time 1      | t <sub>st1</sub> | CP-LP     | 2.5 to 4.5          | 15   | _   | _   | ns   |

|                      |                  |           | 4.5 to 5.5          | 10   | _   | _   |      |

| LP setup time 2      | t <sub>st2</sub> | CP-LP     | 2.5 to 4.5          | 10   | _   | _   | ns   |

|                      |                  |           | 4.5 to 5.5          | 10   | _   | _   |      |

| LP hold time 1       | t <sub>hd1</sub> | CP-LP     | 2.5 to 4.5          | 15   | _   | _   | ns   |

|                      |                  |           | 4.5 to 5.5          | 10   | _   | _   |      |

| LP hold time 2       | t <sub>hd2</sub> | CP-LP     | 2.5 to 4.5          | 50   | _   | _   | ns   |

|                      |                  |           | 4.5 to 5.5          | 25   | _   | _   |      |

| Data setup time      | t <sub>st3</sub> | CP-Dx     | 2.5 to 4.5          | 12   | _   | _   | ns   |

|                      |                  |           | 4.5 to 5.5          | 8    | _   | _   |      |

| Data hold time       | t <sub>hd3</sub> | CP-Dx     | 2.5 to 4.5          | 12   | _   | _   | ns   |

|                      |                  |           | 4.5 to 5.5          | 7    | _   | _   |      |

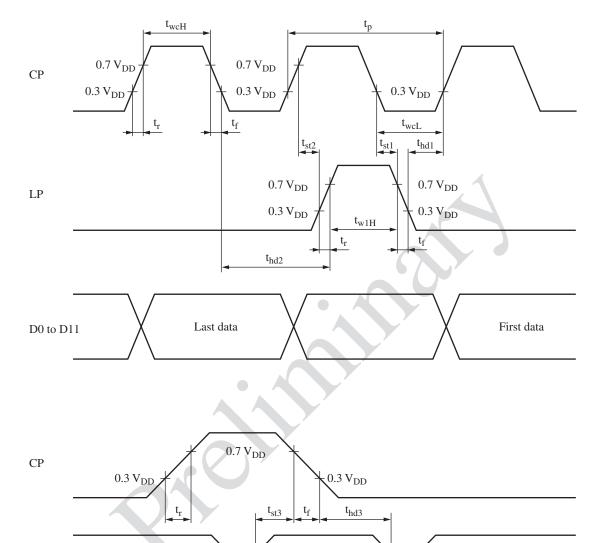

4. AC Characteristics at  $V_{SS} = 0$  V,  $V_{DD} = 2.5$  V to 5.5 V,  $T_a = -20$ °C to +75°C (continued)

| Parameter                                                   | Symbol           | Condition               | ons                 | Min | Тур | Max | Unit |

|-------------------------------------------------------------|------------------|-------------------------|---------------------|-----|-----|-----|------|

|                                                             |                  |                         | V <sub>DD</sub> (V) |     |     |     |      |

| Carry signal setup time                                     | t <sub>st4</sub> |                         | 2.5 to 4.5          | 12  | _   |     | ns   |

|                                                             |                  |                         | 4.5 to 5.5          | 6   | _   |     |      |

| Carry signal output delay time                              | t <sub>d1</sub>  |                         | 2.5 to 4.5          | _   | _   | 21  | ns   |

|                                                             |                  |                         | 4.5 to 5.5          | _   | _   | 12  |      |

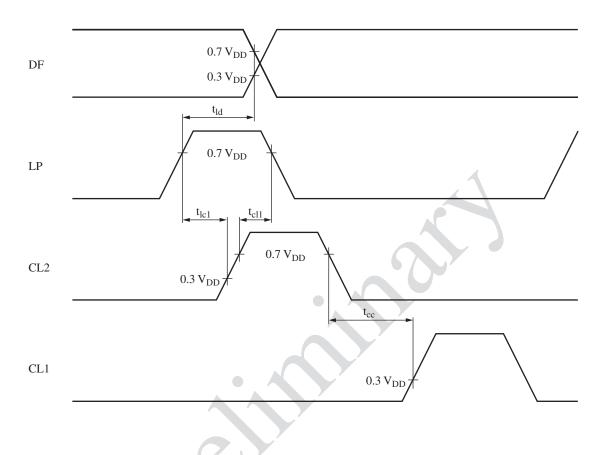

| LP rising edge to<br>CL2 rising edge time                   | t <sub>lc1</sub> |                         |                     | 18  | _   | _   | ns   |

| CL2 rising edge to LP falling edge time                     | t <sub>cl1</sub> |                         |                     | 18  | 7   | _   | ns   |

| CL2 falling edge to CL1 rising edge time                    | t <sub>cc</sub>  |                         |                     | 2   |     | _   | μs   |

| LP rising edge to DF rising edge time, DF falling edge time | t <sub>ld</sub>  |                         |                     | 40  |     | _   | ns   |

| LCD drive signal output delay time 1                        | t <sub>d2</sub>  | $LP \rightarrow O_n$    |                     | -   | _   | 250 | ns   |

| LCD drive signal output delay time 2                        | t <sub>d3</sub>  | $CL1\rightarrow O_n$    | A                   | · - | _   | 250 | ns   |

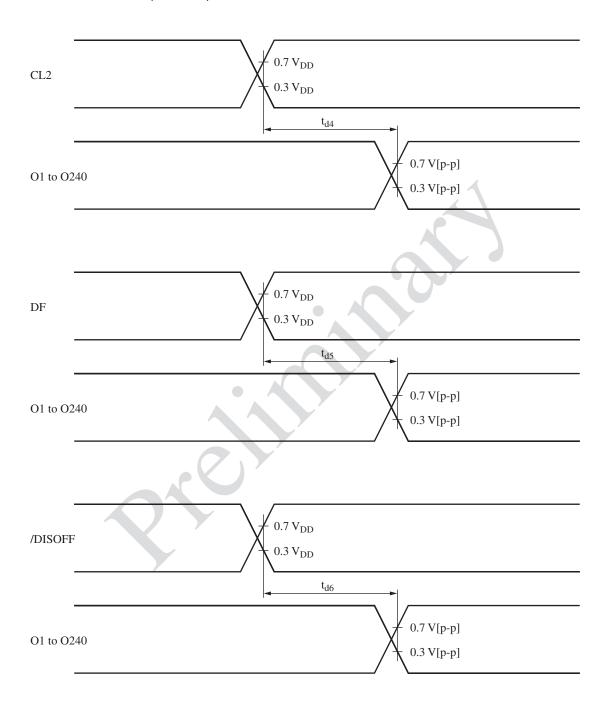

| LCD drive signal output delay time 3                        | t <sub>d4</sub>  | CL2→O <sub>n</sub>      |                     | _   | _   | 250 | ns   |

| LCD drive signal output delay time 4                        | t <sub>d5</sub>  | $DF \rightarrow O_n$    | 7                   | _   | _   | 250 | ns   |

| LCD drive signal output delay time 5                        | t <sub>d6</sub>  | /DISPOFF→O <sub>r</sub> |                     | _   | _   | 250 | ns   |

D0 to D11

# ■ Electrical Characteristics (continued)

### 4. AC Characteristics (continued)

0.7 V<sub>DD</sub>

$0.3\ V_{DD}$

$0.7\,\mathrm{V_{DD}}$

$0.3 V_{DD}$

$t_r, t_f$

## 4. AC Characteristics (continued)

## 4. AC Characteristics (continued)

4. AC Characteristics (continued)

# Request for your special attention and precautions in using the technical information and semiconductors described in this material

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this material is limited to showing representative characteristics and applied circuit examples of the products. It does not constitute the warranting of industrial property, the granting of relative rights, or the granting of any license.

- (3) The products described in this material are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this material are subject to change without notice for reasons of modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment.

Even when the products are used within the guaranteed values, redundant design is recommended, so that such equipment may not violate relevant laws or regulations because of the function of our products.

- (6) When using products for which dry packing is required, observe the conditions (including shelf life and after-unpacking standby time) agreed upon when specification sheets are individually exchanged.

- (7) No part of this material may be reprinted or reproduced by any means without written permission from our company.

## Please read the following notes before using the datasheets

- A. These materials are intended as a reference to assist customers with the selection of Panasonic semiconductor products best suited to their applications.

- Due to modification or other reasons, any information contained in this material, such as available product types, technical data, and so on, is subject to change without notice.

- Customers are advised to contact our semiconductor sales office and obtain the latest information before starting precise technical research and/or purchasing activities.

- B. Panasonic is endeavoring to continually improve the quality and reliability of these materials but there is always the possibility that further rectifications will be required in the future. Therefore, Panasonic will not assume any liability for any damages arising from any errors etc. that may appear in this material.

- C. These materials are solely intended for a customer's individual use. Therefore, without the prior written approval of Panasonic, any other use such as reproducing, selling, or distributing this material to a third party, via the Internet or in any other way, is prohibited.