## **Single-Ended Bus Transceiver**

#### **Features**

- Single-Ended Transceiver

- Survives Shorts and Transients on Automotive Bus

- Wide Power Supply Voltage Range

- Fault Detection

- ISO 9141 Compatible

#### **Description**

The Si9243EY is a monolithic bus transceiver designed to provide bidirectional serial communication in automotive diagnostic applications.

The device incorporates protection against overvoltages and short circuits to GND or  $V_B$ . The transceiver pin is protected and can be driven beyond the  $V_{BAT}$  voltage.

The Si9243EY contains temperature and short circuit fault detection circuits. In the transmit mode, load shorts and opens are generally detected by the processor monitoring RXK and TX. When the two mirror each other there is no fault, but the Si9243EY will turn off the K output in the event of over temperature or short circuit to

V<sub>BAT</sub> to protect the IC. The fault will be reset when TX toggles "high."

TX is set "high" for receive only.

The RX output is capable of driving CMOS or  $1 \times LSTTL$  load.

The Si9243EY is built on the Siliconix BiC/DMOS process. This process supports bipolar transistors, CMOS, and DMOS. An epitaxial layer prevents latchup.

The Si9243EY is available in a 8-pin SO package and operates over the automotive temperature range (-40 to  $125\,^{\circ}$ C).

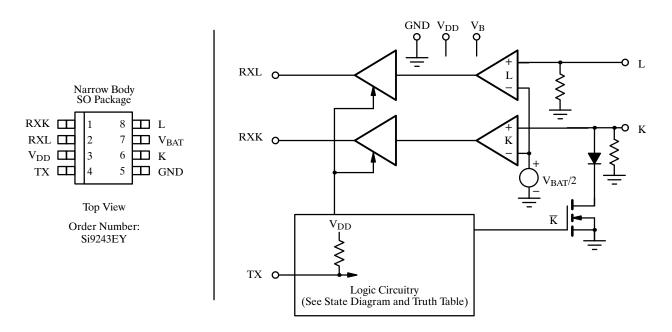

#### Pin Configuration and Functional Block Diagram

Updates to this data sheet may be obtained via facsimile by calling Siliconix FaxBack, 1-408-970-5600. Please request FaxBack document #70017. Application Note AN602 may also be obtained via FaxBack, request document #70573.

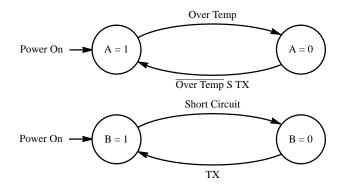

## **Output Table and State Diagrams**

Note: Over Temp is a condition and not meant to be a logic signal.

| Inputs |   | State<br>Variable |     | Output<br>Table |   |     |               |

|--------|---|-------------------|-----|-----------------|---|-----|---------------|

| TX     | A | В                 | K   | RXK             | L | RXL | Comments      |

| 0      | 1 | 1                 | 0   | 0               | 0 | 0   |               |

| 1      | 1 | 1                 | 1   | 1               | 1 | 1   |               |

| 0      | 1 | 1                 | 0   | 0               | 1 | 1   |               |

| 1      | 1 | 1                 | 1   | 1               | 0 | 0   |               |

| X      | 0 | 1                 | HiZ | K               | L | L   | Over Temp     |

| 0      | 1 | 0                 | HiZ | 1               | L | L   | Short Circuit |

|        |   |                   | 1   |                 |   |     |               |

| 1      | 1 | 1                 | 1   | 1               | 1 | 1   | Receive Mode  |

| 1      | 1 | 1                 | 0   | 0               | 0 | 0   |               |

X = "1" or "0"

HiZ = High Impedance State

## **Absolute Maximum Ratings**

| Voltage Referenced to Ground                        | Voltage |

|-----------------------------------------------------|---------|

| Voltage On V <sub>BAT</sub>                         | Short C |

| Voltage K , L                                       | Operati |

| Voltage On Any Pin (Except V <sub>BAT</sub> , K, L) | Junctio |

| or Max. Current                                     | Therma  |

## **Specifications**

|                              |                                 | Test Conditions<br>Unless Otherwise Specified                                               |       | E Suff                |                  |                      |      |  |  |  |

|------------------------------|---------------------------------|---------------------------------------------------------------------------------------------|-------|-----------------------|------------------|----------------------|------|--|--|--|

| Parameter                    | Symbol                          | $V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, V_{BAT} = 7.25 \text{ to } 35 \text{ V}$           | Tempa | Min <sup>b</sup>      | Typ <sup>c</sup> | Max <sup>b</sup>     | Unit |  |  |  |

| Transmitter and Logic Levels |                                 |                                                                                             |       |                       |                  |                      |      |  |  |  |

| TX Input Low Voltage         | V <sub>ILT</sub>                |                                                                                             | Full  |                       |                  | 1.5                  |      |  |  |  |

| TX Input High Voltage        | V <sub>IHT</sub>                |                                                                                             | Full  | 3.5                   |                  |                      |      |  |  |  |

| K Output Low Voltage         | V <sub>OLK</sub>                | $R_L = 510 \Omega, C_L = 10 \text{ nF}$<br>$V_{BAT} = 35 \text{ V}, V_{DD} = 4.5 \text{ V}$ | Full  |                       |                  | 4.9                  | V    |  |  |  |

|                              |                                 |                                                                                             | Full  |                       |                  | 0.2 V <sub>BAT</sub> |      |  |  |  |

| K Output High Voltage        | V <sub>OHK</sub>                | $R_L = 510  \Omega$ , $C_L = 10  nF$<br>See Test Circuit                                    | Full  | 0.91 V <sub>BAT</sub> |                  |                      |      |  |  |  |

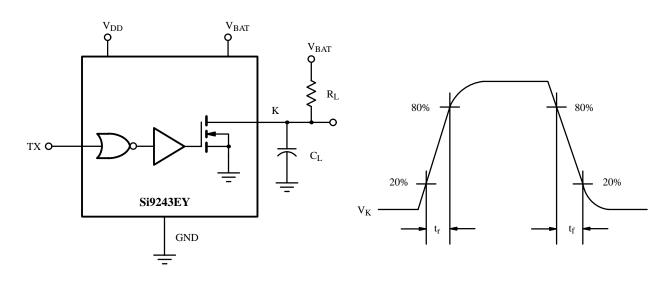

| K Rise, Fall Times           | t <sub>r</sub> , t <sub>f</sub> |                                                                                             | Full  |                       |                  | 9.6                  | μs   |  |  |  |

| K Output Sink Resistance     | Rsi                             | TV 0V                                                                                       | Full  |                       |                  | 110                  | Ω    |  |  |  |

| K Output Capacitanced        | Co                              | TX = 0 V                                                                                    | Full  |                       |                  | 20                   | F    |  |  |  |

| TX Input Capacitanced        | C <sub>INT</sub>                |                                                                                             | Full  |                       |                  | 10                   | pF   |  |  |  |

| TX Input Current             | I <sub>INT</sub>                | V <sub>DD</sub> = 5.5 V, TX = 1.5 V, 3.5 V                                                  | Full  | -60                   |                  | -4                   | μΑ   |  |  |  |

## **Specifications**

|                                        |                   | _                                                                             | Test Conditions Otherwise Specified                           |       | E Suf                |                      |                       |       |

|----------------------------------------|-------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------|-------|----------------------|----------------------|-----------------------|-------|

| Parameter                              | Symbol            | $V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, V_B = 7.25 \text{ to } 35 \text{ V}$ |                                                               | Tempa | Min <sup>b</sup>     | Typ <sup>c</sup>     | Max <sup>b</sup>      | Unit  |

| Receiver                               |                   |                                                                               |                                                               |       |                      |                      |                       |       |

| L and K Input Low Voltage              | V <sub>ILK</sub>  |                                                                               |                                                               | Full  |                      | 0.4 V <sub>BAT</sub> | 0.33 V <sub>BAT</sub> |       |

| L and K Input High Voltage             | V <sub>IHK</sub>  | TX = 4 V                                                                      |                                                               | Full  | 0.7 V <sub>BAT</sub> | $0.6 V_{BAT}$        |                       | v     |

| L and K Input Hysteresis <sup>d</sup>  | V <sub>HYS</sub>  |                                                                               |                                                               | Full  | 0.1 V <sub>BAT</sub> |                      |                       |       |

| RXL and RXK<br>Output Low Voltage      | V <sub>OLR</sub>  |                                                                               | $V_{ILK}$ , $V_{ILL} = 0.33 V_{BAT}$<br>$I_{OLR} = 1 mA$      | Full  |                      |                      | 0.4                   |       |

| RXL and RXK High Voltage               | V <sub>OHR</sub>  |                                                                               | $V_{IHK}$ , $V_{IHL} = 0.70 V_{BAT}$<br>$I_{OHR} = -40 \mu A$ | Full  | 4                    |                      |                       |       |

| L and K Input Currents                 | $I_{IHK}$         |                                                                               | $V_{IHK} = V_{B}$                                             | Full  | 1.5                  |                      | 20                    | μΑ    |

| Supplies                               |                   |                                                                               |                                                               |       |                      |                      |                       |       |

| Bat Supply Current                     | $I_{BAT}$         | TX = 1.5 V, K, L Open                                                         |                                                               | Full  |                      | 2.7                  | 5.0                   |       |

| Logic Supply Current                   | $I_{\mathrm{DD}}$ | TX = 1.5 V, K, L Open                                                         |                                                               | Full  |                      | 1                    | 3.0                   | mA    |

| Miscellaneous                          |                   |                                                                               |                                                               |       |                      |                      | •                     |       |

| Baud Rate                              | BR                | $R_L = 510 \ \Omega, \ C_L = 10 \ nF$                                         |                                                               | Full  | 10.4                 |                      |                       | kBaud |

| TX Minimum Pulse Width <sup>d, e</sup> | t <sub>TX</sub>   |                                                                               |                                                               | Full  | 1                    |                      |                       | μs    |

- a. Room = 25 °C, Cold and Hot = as determined by the operating temperature suffix.

- The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- Guaranteed by design, not subject to production test.

- Minimum pulse width to reset a fault condition.

## **Test Circuit**

# **Si9243EY**

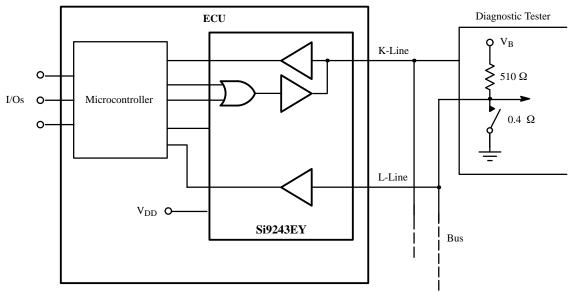

## **Application Circuit**

ECU = Electronic Control Unit