# LA-8048, LA-8049 Monolithic Log Amplifier Monolithic Antilog Amplifier

### **FEATURES**

- 1/2% Full Scale Accuracy

- Temperature Compensated 0°C to 70°C

- Scale Factor 1V/Decade, Adjustable

- 120dB Dynamic Current Range (8048)

- 60 dB Dynamic Voltage Range (8048 & 8049)

- Dual FET-Input Op-Amps

### **GENERAL DESCRIPTION**

The 8048 is a monolithic logarithmic amplifier capable of handling six decades of current input, or three decades of voltage input. It is fully temperature compensated and is nominally designed to provide 1 volt of output for each decade change of input. For increased flexibility, the scale factor, reference current and offset voltage are externally adjustable.

The 8049 is the antilogarithmic counterpart of the 8048; it nominally generates one decade of output voltage for each 1 volt change at the input.

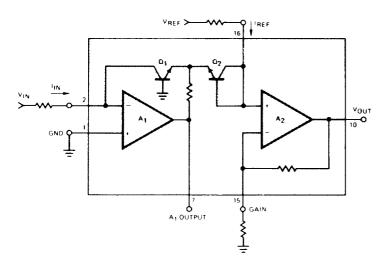

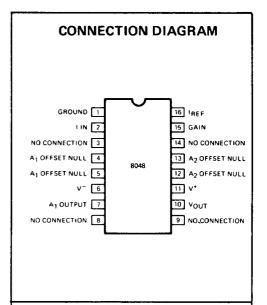

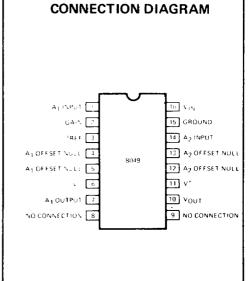

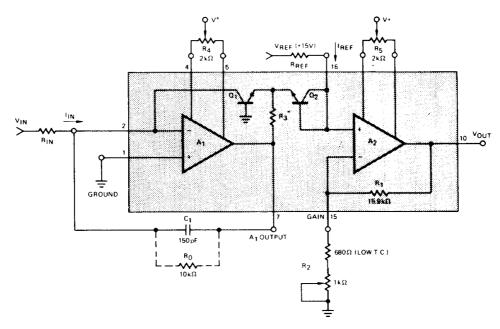

### **8048 SCHEMATIC DIAGRAM**

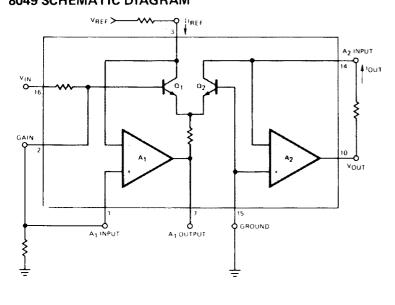

# 8049 SCHEMATIC DIAGRAM

### **MAXIMUM RATINGS**

$\begin{array}{lll} \text{Supply Voltage} & \pm 18 \, \text{V} \\ \text{I}_{\text{in}} & \text{(Input Current)} & 2 \, \text{mA} \\ \text{I}_{\text{ref}} & \text{(Reference Current)} & 2 \, \text{mA} \\ \text{Voltage between Offset Null and V}^+ & \pm 0.5 \, \text{V} \\ \text{Power Dissipation} & 750 \, \text{mW} \end{array}$

Operating Temperature Range

Output Short Circuit Duration

Storage Temperature Range

Lead Temperature (Soldering, 60 sec.)

0°C to +70°C Indefinite -65°C to +125°C 300°C

**ELECTRICAL CHARACTERISTIC (Note 1)**

|                                                   | CONDITION                                                        | LA-8048-B |      |      | LA-8048-C |      |      |         |

|---------------------------------------------------|------------------------------------------------------------------|-----------|------|------|-----------|------|------|---------|

| PARAMETER                                         |                                                                  | MIN.      | TYP. | MAX. | MIN.      | TYP. | MAX. | UNITS   |

| Dynamic Range                                     |                                                                  |           |      |      |           |      |      |         |

| I <sub>in</sub> (1 nA—1 mA)                       |                                                                  | 120       |      |      | 120       |      |      | dB      |

| V <sub>in</sub> (10mV-10V)                        | R <sub>IN</sub> = 10kΩ                                           | 60        |      |      | 60        |      |      | dB      |

| Error, % of Full Scale                            | TA = 25°C, IIN = 1 nA to 1 mA                                    |           | .20  | 0.5  |           | .25  | 1.0  | %       |

| Error, % of Full Scale                            | T <sub>A</sub> = 0°C to +70°C,<br>I <sub>IN</sub> = 1 nA to 1 mA |           | .60  | 1.25 |           | .80  | 2.5  | %       |

| Error, Absolute Value                             | T <sub>A</sub> = 25°C, I <sub>IN</sub> = 1 nA to 1 mA            |           | 12   | 30   |           | 14   | 60   | mV      |

| Error, Absolute Value                             | T <sub>A</sub> = 0°C to +70°C,<br>I <sub>EN</sub> = 1 nA to 1 mA |           | 36   | 75   |           | 50   | 150  | mV      |

| Temperature Coefficient of VOUT                   | I <sub>IN</sub> = 1 nA to 1 mA                                   |           | 0.8  |      |           | 0.8  |      | mV/°C   |

| Power Supply Rejection Ratio                      | Referred to Output                                               |           | 2.5  |      |           | 2.5  |      | mV/V    |

| Offset Voltage (A <sub>1</sub> & A <sub>2</sub> ) | Before Nulling                                                   |           | 15   | 25   |           | 15   | 50   | l mv    |

| Wideband Noise                                    | At Output, for I <sub>IN</sub> = 100μA                           |           | 250  |      |           | 250  |      | μV(RMS) |

| Output Voltage Swing                              | R <sub>L</sub> = 10kΩ                                            | ± 12      | ± 14 |      | ±12       | ±14  |      |         |

|                                                   | R <sub>L</sub> = 2kΩ                                             | ±10       | ±13  |      | ±10       | ±13  |      | v       |

| Power Consumption                                 |                                                                  |           | 150  | 200  |           | 150  | 200  | mW      |

| Supply Current                                    |                                                                  |           | 5    | 6.7  |           | 5    | 6.7  | mA      |

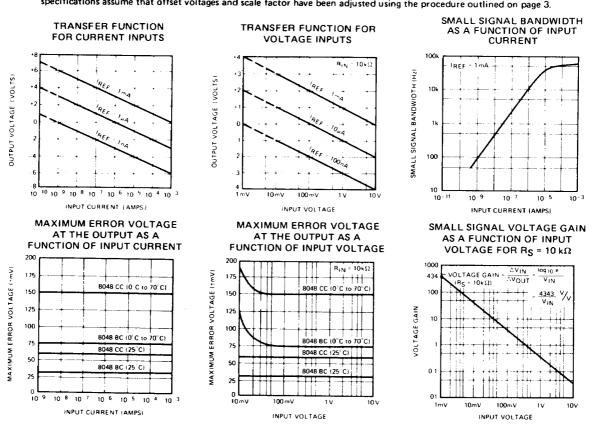

NOTE 1: Unless otherwise noted, specifications apply for V<sub>S</sub> = ±15V, T<sub>A</sub> = 25°C, I<sub>REF</sub> = 1mA, scale factor adjusted for 1V/decade. Accuracy specifications assume that offset voltages and scale factor have been adjusted using the procedure outlined on page 3.

### THEORY OF OPERATION

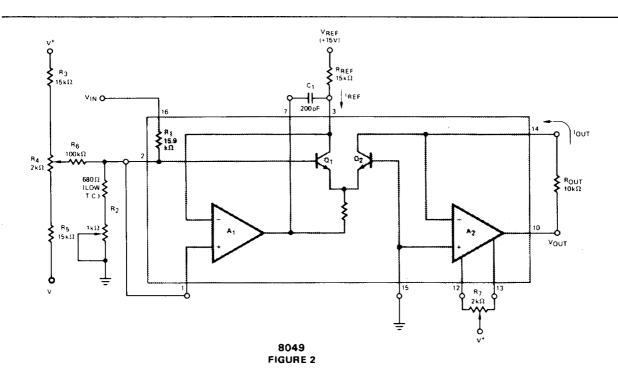

The 8049 relies on the same logarithmic properties of the transistor as the 8048. The input voltage forces a specific  $\Delta V_{BE}$  between  $Q_1$  and  $Q_2$  (Fig. 2). This  $V_{BE}$  difference is converted into a difference of collector currents by the transistor pair. The equation governing the behavior of the transistor pair is derived from (2) on Page 3 and is as follows:

$$|C_1|_{C_2} = \exp\left[q \triangle V_{BE} \right]$$

(5)

When numerical values for q/kT are put into this equation, it is found that a  $\Delta V_{BE}$  of 59mV (at 25°C) is required to change the collector current ratio by a factor of ten. But for ease of application, it is desirable that a 1 volt change at the input generate a tenfold change at the output. The required input attenuation is achieved by the network comprising R<sub>1</sub> and R<sub>2</sub>. In order that scale factors other than one decade per volt may be selected, R<sub>2</sub> is external to the chip. It should have a value of 1k $\Omega$ , adjustable ±20%, for one decade per volt. R<sub>1</sub> is a thin film resistor deposited on the monolithic chip; its temperature characteristics are chosen to compensate the temperature dependence of equation 5, as explained on Page 3.

The overall transfer function is as follows:

$$|OUT|_{REF} = \exp\left[\frac{-R_2}{(R_1 + R_2)} \times \frac{q V_{IN}}{kT}\right]$$

(6)

Substituting Vout = Iout x Rout gives:

$$V_{OUT} = R_{OUT} I_{REF} \exp \left[ \frac{-R_2}{(R_1 + R_2)} \times \frac{q V_{IN}}{kT} \right]$$

(7)

For voltage references equation 7 becomes

$$V_{OUT} = V_{REF} \times \frac{R_{OUT}}{R_{REF}} \exp \left[ \frac{-R_2}{(R_1 + R_2)} \times \frac{q V_{IN}}{kT} \right]$$

(8)

### OFFSET AND SCALE FACTOR ADJUSTMENT

As with the log amplifier, the antilog amplifier requires three adjustments. The first step is to null out the offset voltage of  $A_2$ . This is accomplished by reverse biasing the base-emitter of  $Q_2$ .  $A_2$  then operates as a unity gain buffer with a grounded input. The second step forces  $V_{IN} = 0$ ; the output is adjusted for  $V_{OUT} = 10V$ . This step essentially "anchors" one point on the transfer function. The third step applies a specific input and adjusts the output to the correct voltage. This sets the scale factor. Referring to Fig. 2, the exact procedure for 1 decade/volt is as follows:

- Connect the input (pin #16) to +15V. This reverse biases the base-emitter of Q<sub>2</sub>. Adjust R<sub>7</sub> for V<sub>OUT</sub> = 0V. Disconnect the input from +15V.

- 2) Connect the input to Ground. Adjust R4 for VOUT = 10V. Disconnect the input from Ground.

- Connect the input to a precise 2V supply and adjust R<sub>2</sub> for V<sub>OUT</sub> = 100mV.

The procedure outlined above optimizes the performance over a 3 decade range at the output (i. e., VOUT from 10mV to 10V). For a more limited range of output voltages, for example 1V to 10V, it would be better to use a precise 1 volt supply and adjust for VOUT = 1V. For other scale factors and/or starting points, different values for  $R_2$  and  $R_{REF}$  will be needed, but the same basic procedure applies.

### **MAXIMUM RATINGS**

Supply Voltage

Vin (Input Voltage)

Iref (Reference Current)

Voltage between Offset Null and V<sup>+</sup>

Power Dissipation

Operating Temperature Range

Output Short Circuit Duration

Storage Temperature Range

Lead Temperature (Soldering, 60 sec.)

±18 V ±15 V 2mA ±0.5 V 750 mW 0°C to +70°C Indefinite -65°C to +150°C 300°C

# **ELECTRICAL CHARACTERISTIC** (Note 1)

|                                                   | CONDITION                                                              | LA-8049-B |      |      | LA-8049-C |      |      |        |

|---------------------------------------------------|------------------------------------------------------------------------|-----------|------|------|-----------|------|------|--------|

| PARAMETER                                         |                                                                        | MIN.      | TYP. | MAX. | MIN.      | TYP. | MAX. | UNITS  |

| Dynamic Range (VOUT)                              | V <sub>OUT</sub> = 10mV to 10V                                         | 60        |      |      | 60        |      |      | dB     |

| Error, Absolute Value                             | $T_A = 25^{\circ}C$ , $0V \le V_{IN} \le 3V$                           |           | 3    | 10   |           | 5    | 25   | m∨     |

| Error, Absolute Value                             | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C,$<br>$0V \le V_{IN} \le 3V$ |           | 20   | 75   |           | 30   | 150  | m∨     |

| Temperature Coefficient, Referred to VIN          | V <sub>IN</sub> = 3V                                                   |           | 0.38 |      | Ì         | 0.55 |      | mV/°C  |

| Power Supply Rejection Ratio                      | Referred to Input, for<br>VIN = 0V                                     |           | 2.0  |      |           | 2.0  |      | μV/V   |

| Offset Voltage (A <sub>1</sub> & A <sub>2</sub> ) | Before Nulling                                                         |           | 15   | 25   |           | 15   | 50   | mV     |

| Wideband Noise                                    | Referred to Input, for<br>V <sub>IN</sub> = 0V                         |           | 26   |      |           | 26   |      | μV(RMS |

| Output Voltage Swing                              | R <sub>L</sub> = 10 kΩ                                                 | ±12       | ±14  |      | ±12       | ±14  |      | V      |

|                                                   | R <sub>L</sub> = 2kΩ                                                   | ±10       | ±13  |      | ±10       | ±13  |      | V      |

| Power Consumption                                 |                                                                        |           | 150  | 200  |           | 150  | 200  | mW     |

| Supply Current                                    |                                                                        | 1         | 5    | 6.7  |           | 5    | 6.7  | mA     |

1:0038.

NOTE 1: Unless otherwise noted, specifications apply for V<sub>S</sub> = ±15V, T<sub>A</sub> = 25°C, I<sub>REF</sub> = 1mA, scale factor adjusted for 1 decade (out) per volt (in). Accuracy specifications assume that offset voltages and scale factor have been adjusted using the procedure on page 5.

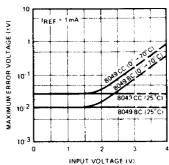

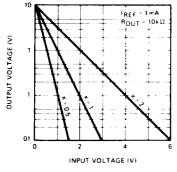

# AS A FUNCTION OF INPUT VOLTAGE

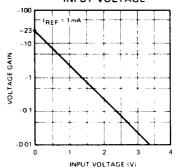

### SMALL SIGNAL VOLTAGE GAIN AS A FUNCTION OF INPUT VOLTAGE

### THEORY OF OPERATION

The 8048 relies for its operation on the well-known exponential relationship between the collector current and the base-emitter voltage of a transistor:

$$I_{C} = I_{S} \left[ e^{q \, V_{BE}} / _{kT} \right]$$

(1)

For base-emitter voltages greater than 100mV, Eq. (1) becomes

$$I_C = I_S e^{q V_{BE}/kT}$$

(2)

From Eq. (2), it can be shown that for two identical transistors operating at different collector currents, the  $V_{BE}$  difference ( $\Delta V_{BE}$ ) is given by:

$$\Delta V_{BE} = -2.303 \times \frac{kT}{q} \log 10 \left[ \frac{I_{C1}}{I_{C2}} \right]$$

(3)

Referring to Fig. 1, it is clear that the potential at the collector of  $Q_2$  is equal to the  $\Delta V_{BE}$  between  $Q_1$  and  $Q_2$ . The output voltage is  $\Delta V_{BE}$  multiplied by the gain of  $A_2$ :

$$V_{OUT} = -2.303 \left(\frac{R_1 R_2}{R_2}\right) \left(\frac{kT}{q}\right) \log_{10} \left[\frac{I_{IN}}{I_{REF}}\right]$$

(4)

The expression  $2.303 \times \frac{kT}{q}$  has a numerical value of 59mV at  $25^{\circ}$ C; thus in order to generate 1 volt/decade at the output, the ratio  $(R_1 + R_2)/R_2$  is chosen to be 16.9. For this scale factor to hold constant as a function of temperature, the  $(R_1 + R_2)/R_2$  term must have a 1/T characteristic to compensate for kT/q.

In the 8048 this is achieved by making  $R_1$  a thin film resistor, deposited on the monolithic chip. It has a nominal

value of  $15.9 k\Omega$  at  $25^{\circ} C$ , and its temperature coefficient is carefully designed to provide the necessary compensation. Resistor R<sub>2</sub> is external and should be a low T.C. type; it should have a nominal value of  $1 k\Omega$  to provide 1 volt/decade, and must have an adjustment range of  $\pm 20\%$  to allow for production variations in the absolute value of R<sub>1</sub>.

### OFFSET AND SCALE FACTOR ADJUSTMENT

A log amp, unlike an op-amp, cannot be offset adjusted by simply grounding the input. This is because the log of zero approaches minus infinity; reducing the input current to zero starves Q<sub>1</sub> of collector current and open the feedback loop around A<sub>1</sub>. Instead, it is necessary to zero the offset voltage of A<sub>1</sub> and A<sub>2</sub> separately, and then to adjust the scale factor. Referring to Fig. 1, this is done as follows:

- Temporarily connect a 10kΩ resistor (R<sub>0</sub>) between pins 2 and 7. With no input voltage, adjust R<sub>4</sub> until the output of A<sub>1</sub> (pin 7) is zero. Remove R<sub>0</sub>.

- Note that for a current input, this adjustment is not necessary since the offset voltage of A<sub>1</sub> does not cause any error for current-source inputs.

- Set I<sub>IN</sub> = I<sub>REF</sub> = 1mA. Adjust R<sub>5</sub> such that the output of A<sub>2</sub> (pin 10) is zero.

- 3) Set I<sub>IN</sub> = 1μA, I<sub>REF</sub> = 1mA. Adjust R<sub>2</sub> for V<sub>OUT</sub> = 3 volts (for a 1 volt/decade scale factor) or 6 volts (for a 2 volt/decade scale factor).

Step #3 determines the scale factor. Setting  $I_{1N}=1\mu A$  optimizes the scale factor adjustment over a fairly wide dynamic range, from 1mA to 1nA. Clearly, if the 8048 is to be used for inputs which only span the range 100 $\mu A$  to 1mA, it would be better to set  $I_{1N}=100\mu A$  in Step #3. Similarly, adjustment for other scale factors would require different  $I_{1N}$  and  $V_{OUT}$  values.

FIGURE 1. 8048 OFFSET AND SCALE FACTOR ADJUSTMENT

### **APPLICATIONS INFORMATION**

### Scale Factor Adjustment

The scale factor adjustment procedures outlined on Page 3 (8048) and Page 5 (8049) are primarily directed towards setting up 1 volt ( $\Delta V_{OUT}$ ) per decade ( $\Delta I_{IN}$  or  $\Delta V_{IN}$ ) for the log amp, or one decade ( $\Delta V_{OUT}$ ) per volt ( $\Delta V_{IN}$ ) for the antilog amp.

This corresponds to K = 1 in the respective transfer functions:

Log Amp:

$$V_{OUT} = -K \log_{10} \left[ \frac{I_{IN}}{I_{REF}} \right]$$

(9)

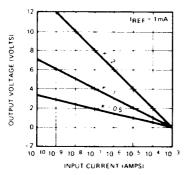

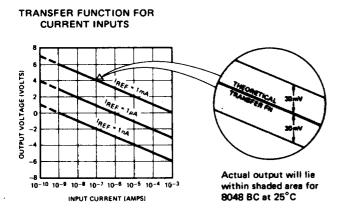

By adjusting  $R_2$  (Fig. 1 and Fig. 2) the scale factor "K" in equation 9 and 10 can be varied. The effect of changing K is shown graphically in Fig. 3 for the log amp, and Fig. 4 for the antilog amp. The nominal value of  $R_2$  required to give a specific value of K can be determined from equation 11. It should be remembered that  $R_1$  has a  $\pm 20\%$  tolerance in absolute value, so that allowance shall be made for adjusting the nominal value of  $R_2$  by  $\pm 20\%$ .

$$R_2 = \frac{941}{(K - .059)} \Omega \tag{11}$$

FIGURE 3

EFFECT OF VARYING "K" ON THE ANTILOG AMPLIFIER

FIGURE 4

### Frequency Compensation

Although the op-amps in both the 8048 and the 8049 are compensated for unity gain, some additional frequency compensation is required. This is because the log transistors in the feedback loop add to the loop gain. In the 8048, 150 pF should be connected between Pins 2 and 7 (Fig. 1). In the 8049, 200 pF between Pins 3 and 7 is recommended (Fig. 2).

### **Error Analysis**

Performing a meaningful error analysis of a circuit containing log and antilog amplifiers is more complex than dealing with a similar circuit involving only op-amps. In this data sheet every effort has been made to simplify the analysis task, without in any way compromising the validity of the resultant numbers.

The key difference in making error calculations in log/ antilog amps, compared with op-amps, is that the gain of the former is a function of the input signal level. Thus, it is necessary, when referring errors from output to input, or vice versa, to check the input voltage level, then determine the gain of the circuit by referring to the graphs given on Pages 2 and 4.

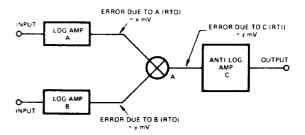

The various error terms in the log amplifier, the 8048, are referred to the output (RTO) of the device. The error terms in the antilog amplifier, the 8049, are referred to the input (RTI) of the device. The errors are expressed in this way because in the majority of systems a number of log amps interface with an antilog amp, as shown in Fig. 5.

FIGURE 5

It is very straightforward to estimate the system error at node (A) by taking the square root of the sum-of-the squares of the errors of each contributing block.

Total Error =

$$\sqrt{x^2 + y^2 + z^2}$$

at (A)

If required, this error can be referred to the system output through the voltage gain of the antilog circuit, using the voltage gain plot on Page 4.

The numerical values of x, y, and z in the above equation are obtained from the maximum error voltage plots given on Pages 2 and 4. For example, with the 8048BC, the maximum error at the output is 30mV at 25°C. This means that the measured output will be within 30mV of the theoretical transfer function, provided the unit has been adjusted per the procedures on Page 3. Fig. 6 illustrates this point.

To determine the maximum error over the operating temperature range, the 0 to 70°C absolute error values given in the table of electrical characteristics should be used. For intermediate temperatures, assume a linear increase in the error between the 25°C value and the 70°C value.

For the antilog amplifier, the only difference is that the error refers to the input, i. e., the horizontal axis. It will be noticed that the maximum error voltage of the 8049, over the temperature range, is strongly dependent on the input voltage. This is because the output amplifier, A2, has an offset voltage drift which is directly transmitted to the output. When this error is referred to the input, it must be divided by the voltage gain, which is input voltage dependent. At  $V_{\mbox{\scriptsize IN}}=3V$ , for example, errors at the output are multiplied by 1/.023 (= 43.5) when referred to the input.

It is important to note that both the 8048 and the 8049 require positive values of IREF, and the input and output currents (or voltages) respectively must also be positive. Application of negative IN to the 8048 or negative IREF to

either circuit will cause malfunction, and if maintained for long periods, would lead to device degradation. Some protection can be provided by placing a diode between pin 7 and ground.

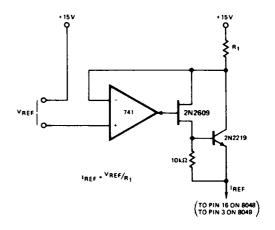

### SETTING UP THE REFERENCE CURRENT

In both the 8048 and the 8049 the input current reference pin (IREF) is not a true virtual ground. For the 8048, a fraction of the output voltage is seen on Pin 16 (Fig. 1). This does not constitute an appreciable error provided VREF is much greater than this voltage. A 10V or 15V reference satisfies this condition. For the 8049, a fraction of the input voltage appears on Pin 3 (Fig. 2), placing a similar restraint on the value of VREF.

Alternatively, IREF can be provided from a true current source. One method of implementing such a current source is shown in Fig. 7.

## LOG OF RATIO CIRCUIT, DIVISION

The 8048 may be used to generate the log of a ratio by modulating the IREF input. The transfer function remains the same, as defined by equation 9:

$$V_{OUT} = -K \log_{10} \left[ IIN \right]_{REF}$$

(9)

Clearly it is possible to perform division using just one 8048, followed by an 8049. For multiplication, it is generally necessary to use two log amps, summing their outputs into an antilog amp.

To avoid the problems caused by the IREF input not being a true virtual ground (discussed in the previous section), the circuit of Fig. 7 is again recommended if the IREF input is to be modulated.

FIGURE 6

FIGURE 7

### **DEFINITION OF TERMS**

In the definitions which follow, it will be noted that the various error terms are referred to the output of the log

DYNAMIC RANGE The dynamic range of the 8048 refers to the range of input voltages or currents over which the device is guaranteed to operate. For the 8049 the dynamic range refers to the range of output voltages over which the device is guaranteed to operate.

ERROR, ABSOLUTE VALUE The absolute error is a measure of the deviation from the theoretical transfer function, after performing the offset and scale factor adjustments as outlined on Pages 3 (8048) or 5 (8049). It is expressed in mV and referred to the linear axis of the transfer function plot. Thus, in the case of the 8048, it is a measure of the deviation from the theoretical output voltage for a given input current or voltage. For the 8049 it is a measure of the deviation from the theoretical input voltage required to generate a specific output voltage.

The absolute error specification is guaranteed over the dynamic range.

ERROR, % OF FULL SCALE The error as a percentage of full scale can be obtained from the following relationship:

Error, % of Full Scale =  $\frac{100 \times \text{Error, absolute value}}{\text{Full Scale Output Voltage}}$

amp, and to the input of the antilog amp. The reason for this is explained on Page 6.

TEMPERATURE COEFFICIENT OF VOUT OR VIN For the 8048 the temperature coefficient refers to the drift with temperature of VOUT for a constant input current. For the 8049 it is the temperature drift of the input voltage required to hold a constant value of VOUT.

POWER SUPPLY REJECTION RATIO The ratio of the voltage change in the linear axis of the transfer function (VOUT for the 8048, VIN for the 8049) to the change in the supply voltage, assuming that the log axis is held constant.

WIDEBAND NOISE For the 8048, this is the noise occurring at the output under the specified conditions. In the case of the 8049, the noise is referred to the input.

SCALE FACTOR For the log amp, the scale factor (K) is the voltage change at the output for a decade (i. e. 10:1) change at the input. For the antilog amp, the scale factor is the voltage change required at the input to cause a one decade change at the output. See equations 9 and 10.

### ORDERING INFORMATION

### LOGARITHMIC AMPLIFIER

| MODEL      | MAX. ERROR | OPER. TEMP<br>RANGE | PACKAGE            |  |  |

|------------|------------|---------------------|--------------------|--|--|

| LA-8048-BC | 30mV       | 0 to +70° C         | 16 pin Blactic DID |  |  |

| LA-8048-CC | 60mV       | - 0 to +70 C        | 16 pin Plastic DIP |  |  |

### **ANTI-LOGARITHMIC AMPLIFIER**

| MODEL      | MAX. ERROR | OPER. TEMP<br>RANGE | PACKAGE            |  |  |

|------------|------------|---------------------|--------------------|--|--|

| LA-8049-BC | 10mV       | 0 to +70° C         | 16 pin Dinatio DID |  |  |

| LA-8049-CC | 25mV       | 7 010+70 0          | 16 pin Plastic DIP |  |  |

### PACKAGE DIMENSIONS

16 PIN PLASTIC DIP