## 8031AH/8051AH

#### DESCRIPTION

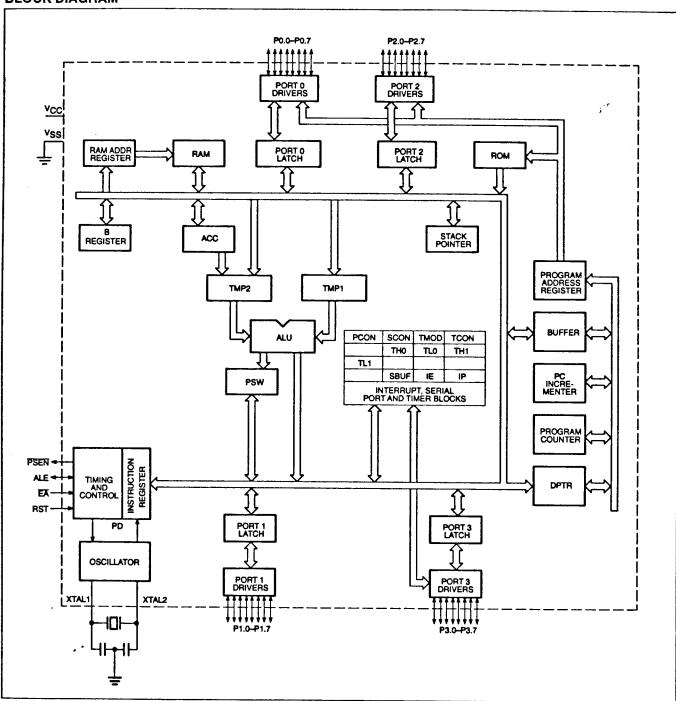

The Philips 8031AH/8051AH is a high-performance microcontroller fabricated with Philips high-density highly reliable +5V, depletion-load, N-channel, silicon-gate, N500 MOS process technology. It provides the hardware features, architectural enhancements and instructions that are necessary to make it a powerful and cost-effective controller for applications requiring up to 64k bytes of program memory and/or up to 64k bytes of data storage.

The 8051AH contains a 4k × 8 read-only program memory, a 128 × 8 read-only data memory, 32 I/O lines, two 16-bit counter/timers, a five-source, two-priority level nested interrupt structure, a serial I/O port for either multi-processor communications, I/O expansion or full duplex UART, and on-chip oscillator and clock circuits. The 8031AH is identical, except that it lacks the program memory. For systems that require extra capability, the 8051AH can be expanded using standard TTL compatible memories and byte oriented peripheral controllers.

The 8051AH microcontroller, like its 8048 predecessor, is efficient both as a controller and as an arithmetic processor. It has extensive facilities for binary and BCD arithmetic and excels in bit-handling capabilities. Efficient use of program memory results from an instruction set consisting of 44% one-byte, 41% two-byte, and 15% three-byte instructions. With a 12MHz crystal, 58% of the instructions execute in 1µs, 40% in 2µs and multiply and divide require only 4µs.

#### **FEATURES**

- Reduced supply current

- 4k×8 ROM (8051AH)

- 128 × 8 RAM

- Four 8-bit ports, 32 I/O lines

- Two 16-bit timer/event counters

- High-performance full-duplex serial channel

- External memory expandable to 128k

- Boolean processor

- Industry standard 8051 architecture:

- Non-paged jumps

- Direct addressing

- Four 8-register banks

- Stack depth up to 128-bytes

- Multiply, divide, subtract, compare

- Most instructions execute in 1µs

- 4μs multiply and divide

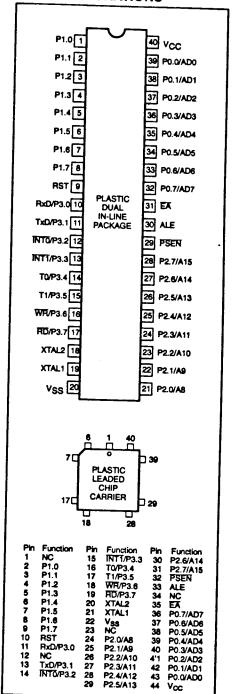

## PIN CONFIGURATIONS

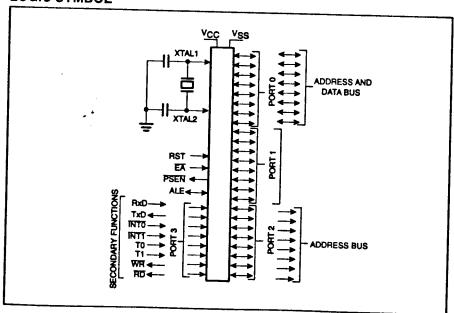

#### LOGIC SYMBOL

## 8031AH/8051AH

#### **PART NUMBER SELECTION**

| PHILIPS                        |                              |               | PHILIPS NOF   | RTH AMERICA   |                                                |              |                   |

|--------------------------------|------------------------------|---------------|---------------|---------------|------------------------------------------------|--------------|-------------------|

| ROMIess<br>(MARKING<br>NUMBER) | ROMiess<br>(ORDER<br>NUMBER) | ROM           | ROMiess       | ROM           | TEMPERATURE °C AND PACKAGE                     | FREQ.<br>MHz | DRAWING<br>NUMBER |

| MAF8031AH-2-12P                | MAF8031A-2 N                 | MAF8051AH-2P  | SCN8031HACN40 | SCN8051HACN40 | -40 to +85,<br>Plastic Dual<br>In-Line Package | 12<br>; '    | 0415C             |

| MAB8031AH-2-12P                | MAB8031A-2 N                 | MAB8051AH-2P  | SCN8031HCCN40 | SCN8051HCCN40 | 0 to +70,<br>Plastic Dual<br>In-Line Package   | 12           | 0415C             |

|                                |                              |               | SCN8031HCFN40 | SCN8051HCFN40 | 0 to +70,<br>Plastic Dual<br>In-Line Package   | 15           | 0415C             |

|                                |                              |               | SCN8031HAFN40 | SCN8051HAFN40 | -40 to +85,<br>Plastic Dual<br>In-Line Package | 15           | 0415C             |

| MAB8031AH-2-12WP               | MAB8031A-2 A                 | MAB8051AH-2WP | SCN8031HCCA44 | SCN8051HCCA44 | 0 to +70,<br>Plastic Leaded<br>Chip Carrier    | 12           | 0403G             |

| MAF8031AH-2-12WP               | MAF8031A-2 A                 | MAF8051AH-2WP | SCN8031HACA44 | SCN8051HACA44 | -40 to +85,<br>Plastic Leaded<br>Chip Carrier  | 12           | 0403G             |

|                                |                              |               | SCN8031HCFA44 | SCN8051HCFA44 | 0 to +70,<br>Plastic Leaded<br>Chip Carrier    | 15           | 0403G             |

|                                |                              |               | SCN8031HAFA44 | SCN8051HAFA44 | -40 to +85,<br>Plastic Leaded<br>Chip Carrier  | 15           | 0403G             |

## 8031AH/8051AH

#### **BLOCK DIAGRAM**

#### 8031AH/8051AH

#### **PIN DESCRIPTIONS**

|                 | PIN NO. |              |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|---------|--------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC        |         |              | TYPE       | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SS</sub> | 20      | 22           | 1          | Ground: 0V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Vcc             | 40      | 44           | ı          | Power Supply: This is the power supply voltage for normal, idle, and power-down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P0.0-0.7        | 39–32   | 43–36        | VO         | Port 0: Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s.                                                                                                                                                                                                                                                                                                                                                                                                                |

| P1.0-P1.7       | 1–8     | 2-9          | VO         | Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                   |

| P2.0-P2.7       | 21–28   | 24–31        | I/O        | Port 2: Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOV @Ri), port 2 emits the contents of the P2 special function register. |

| P3.0-P3.7       | 10–17   | 11,<br>13–19 | <i>V</i> O | Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally being pulled low will source current because of the pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 3 also serves the special features of the 80C51 family, as listed below:                                                                                                                                                                                                                                                                                                                        |

|                 | 10      | 11           | ı          | RxD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 | 11      | 13           | 0          | TxD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 | 12      | 14           | ı          | INTO (P3.2): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 13      | 15           | ı          | INT1 (P3.3): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 14      | 16           | ı          | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 | 15      | 17           | ı          | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 | 16      | 18           | 0          | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | 17      | 19           | 0          | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RST             | 9       | 10           | I          | Reset: A high on this pin for two machine cycles while the oscillator is running, resets the device.  An internal diffused resistor to V <sub>SS</sub> permits a power-on reset using only an external capacitor to V <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ALE             | 30      | 33           | 1/0        | Address Latch Enable: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PSEN            | 29      | 32           | 0          | Program Store Enable: The read strobe to external program memory. When the device is executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.                                                                                                                                                                                                                                                                                                                                                                                                               |

| EA              | 31      | 35           |            | External Access Enable: EA must be externally held low to enable the device to fetch code from external program memory locations 0000H to 0FFFH. If EA is held high, the device executes from internal program memory unless the program counter contains an address greater than 0FFFH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| XTAL1           | 19      | 21           | 1          | Crystal 1: Input to the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XTAL2           | 18      | 20           | 0          | Crystal 2: Output from the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

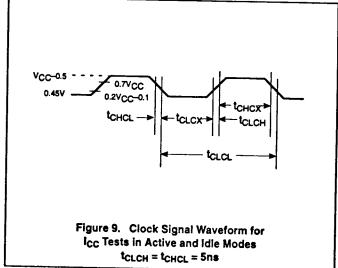

# OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier. The pins can be configured for use as an on-chip oscillator, as shown in the logic symbol.

To drive the device from an external clock source, XTAL2 should be driven while XTAL1 is connected to ground. There are no requirements on the duty cycle of the external clock signal, because the input to the internal clock circuitry is through a divide-by-two flip-flop. However, minimum and maximum

high and low times specified in the data sheet must be observed.

### **DESIGN CONSIDERATIONS**

At power-on, the voltage on  $V_{CC}$  and RST should come up at the same time for a proper start-up.

8031AH/8051AH

#### **ABSOLUTE MAXIMUM RATINGS 1, 2, 3**

| PARAMETER                                   | RATING       | UNIT |

|---------------------------------------------|--------------|------|

| Storage temperature range                   | -65 to +150  | •℃   |

| Voltage on any other pin to V <sub>SS</sub> | -0.5 to +7.0 | V    |

| Input, output current on any single pin     | 10           | mA   |

| Power dissipation                           | 1.0          | w    |

#### DC ELECTRICAL CHARACTERISTICS

$T_{amb} = 0^{\circ}C$  to +70°C,  $V_{CC} = 5V \pm 10\%$ ,  $V_{SS} = 0V^{4, 5}$

|                        |                                                              | TEST                                              | LIMITS       |                      |      |  |

|------------------------|--------------------------------------------------------------|---------------------------------------------------|--------------|----------------------|------|--|

| SYMBOL                 | PARAMETER                                                    | CONDITIONS                                        | MIN          | MAX                  | UNIT |  |

| V <sub>IL</sub>        | Input low voltage                                            |                                                   | -0.5         | 0.8                  | V    |  |

| V <sub>IH</sub>        | Input high voltage; except XTAL2, RST                        |                                                   | 2.0          | V <sub>CC</sub> +0.5 | V    |  |

| V <sub>IH1</sub>       | Input high voltage to RST for reset, XTAL2                   | XTAL1 to V <sub>SS</sub>                          | 2.5          | V <sub>CC</sub> +0.5 | V    |  |

| V <sub>OL</sub>        | Output low voltage; ports 1, 2, 3 <sup>6</sup>               | I <sub>OL</sub> = 1.6mA                           |              | 0.45                 | V    |  |

| V <sub>OL1</sub>       | Output low voltage; port 0, ALE, PSEN6                       | I <sub>OL</sub> = 3.2mA                           |              | 0.45                 | ٧    |  |

| V <sub>OH</sub>        | Output high voltage; ports 1, 2, 3                           | I <sub>OH</sub> = -80uA                           | 2.4          |                      | ٧    |  |

| V <sub>OH1</sub>       | Output high voltage; port 0, ALE, PSEN <sup>3</sup>          | I <sub>OH</sub> = -400uA                          | 2.4          |                      | V    |  |

| I <sub>IL</sub>        | Logical 0 input current; ports 1, 2, 3                       | V <sub>IN</sub> = 0.45V                           |              | -500                 | μА   |  |

| l <sub>lH1</sub>       | Input high current to RST for reset                          | V <sub>IN</sub> < V <sub>CC</sub> -1.5V           |              | 500                  | μА   |  |

| lu                     | Input leakage current; port 0, EA                            | 0.45 < V <sub>IN</sub> < V <sub>CC</sub>          |              | ±10                  | μА   |  |

| l <sub>IL2</sub>       | Logical 0 input current for XTAL2                            | XTAL1 = V <sub>SS</sub> , V <sub>IN</sub> = 0.45V |              | -3.2                 | mA   |  |

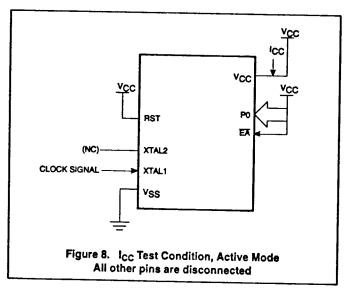

| lcc                    | Power supply current                                         | All outputs disconnected and EA = V <sub>CC</sub> | <del> </del> | 125                  | mA   |  |

| C <sub>IO</sub>        | Pin capacitance                                              |                                                   |              | 10                   | pF   |  |

| T <sub>amb</sub> = -40 | °C to +85°C, V <sub>CC</sub> = 5V ±10%, V <sub>SS</sub> = 0V |                                                   |              | ·.h.                 |      |  |

|                        |                                                              | TEST                                              | LIMITS       |                      |      |  |

| SYMBOL                 | PARAMETER                                                    | CONDITIONS                                        | MIN          | MAX                  | UNIT |  |

| V <sub>IH</sub>        | Input high voltage; except XTAL2, RST                        |                                                   | 2.1          | V <sub>CC</sub> +0.5 | ٧    |  |

| V <sub>IH1</sub>       | Input high voltage to RST and XTAL2                          | XTAL1 = V <sub>SS</sub>                           | 2.6          | V <sub>CC</sub> +0.5 | V    |  |

| l <sub>IL2</sub>       | Logical 0 input current for XTAL2                            | XTAL1 = V <sub>SS</sub> , V <sub>IN</sub> = 0.45V |              | -4.0                 | mA   |  |

| lcc                    | Power supply current                                         | All outputs disconnected and EA = V <sub>CC</sub> |              | 135                  | mA   |  |

#### NOTES:

- Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied.

- 2. For operating at elevated temperatures, the device must be derated based on +150°C maximum junction temperature.

- 3. This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maxima.

- Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

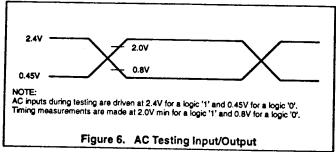

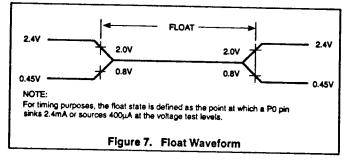

- 5. All voltage measurements are referenced to ground. For testing, all input signals swing between 0.45V and 2.4V with a transition time of 20ns maximum. All time measurements are referenced at input voltages of 0.8V and 2.0V and at output voltages of 0.8V and 2.0V as appropriate.

- 6. VOL is derated when the device rapidly discharges external capacitance. This AC noise is most pronounced during emission of address data. When using external memory, locate the latch or buffer as close as possible to the device.

7.  $C_L = 100pF$  for port 0, ALE and  $\overline{PSEN}$  outputs:  $C_L = 80pF$  for all other ports.

8031AH/8051AH

#### **AC ELECTRICAL CHARACTERISTICS**

$T_{amb} = 0$ °C to +70°C or -40°C to +85°C,  $V_{CC} = 5V \pm 20$ %,  $V_{SS} = 0V^{1,2}$

|                     | Ì        |                                                                                            | 12MHz CLOCK  |                                                  | VARIABLE CLOCK           |                                              |                          |

|---------------------|----------|--------------------------------------------------------------------------------------------|--------------|--------------------------------------------------|--------------------------|----------------------------------------------|--------------------------|

| SYMBOL              | FIGURE   | PARAMETER                                                                                  | MIN          | MAX                                              | MIN                      | MAX                                          | UNIT                     |

| 1/t <sub>CLCL</sub> |          | Oscillator frequency: Speed Versions SCN8051/31 C MAB8051/31 -2 MAF8051/31 -2 SCN8051/31 F |              |                                                  | 3.5<br>3.5<br>3.5<br>3.5 | 12<br>12<br>12<br>15                         | MHz<br>MHz<br>MHz<br>MHz |

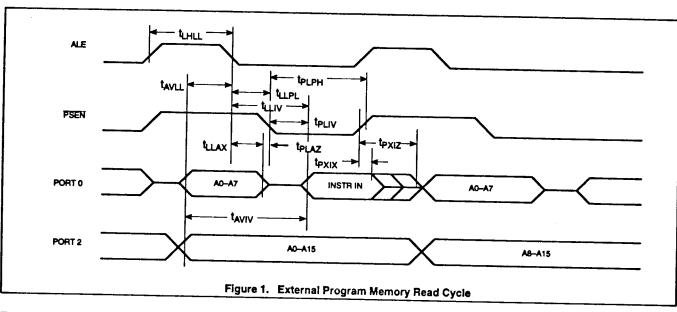

| tuни.               | 1        | ALE pulse width                                                                            | 127          |                                                  | 2t <sub>CLCL</sub> -40   | <del></del>                                  | ns                       |

| t <sub>avll</sub>   | 1        | Address valid to ALE low                                                                   | 43           | 1                                                | t <sub>CLCL</sub> -40    |                                              | ns                       |

| tlax                | 1        | Address hold after ALE low                                                                 | 48           |                                                  | t <sub>CLCL</sub> -35    |                                              | ns                       |

| teriv               | 1        | ALE low to valid instruction in                                                            |              | 233                                              | <u> </u>                 | 4t <sub>CLCL</sub> -100                      | ns                       |

| tlel                | 1        | ALE low to PSEN low                                                                        | 58           | Ť                                                | t <sub>CLCL</sub> -25    |                                              | ns                       |

| фгън                | 1        | PSEN pulse width                                                                           | 215          |                                                  | 3t <sub>CLCL</sub> -35   |                                              | ns                       |

| t <sub>PLIV</sub>   | 1        | PSEN low to valid instruction in                                                           |              | 125                                              |                          | 3t <sub>CLCL</sub> -125                      | ns                       |

| t <sub>РХІХ</sub>   | 1        | Input instruction hold after PSEN                                                          | 0            |                                                  | 0                        |                                              | ns                       |

| t <sub>PXIZ</sub>   | 1        | Input instruction float after PSEN                                                         | T            | 63                                               |                          | t <sub>CLCL</sub> -20                        | ns                       |

| t <sub>AVIV</sub>   | 1        | Address to valid instruction in                                                            |              | 302                                              |                          | 5t <sub>CLCL</sub> -115                      | ns                       |

| <sup>t</sup> PLAZ   | 1        | PSEN low to address float                                                                  |              | 20                                               |                          | 20                                           | ns                       |

| <b>P</b> XAV        | 1        | PSEN to address valid                                                                      | 75           | <del>                                     </del> | tc.c8                    |                                              | ns                       |

| Data Memor          | у        |                                                                                            | <del>1</del> | <del> </del>                                     |                          | <u>.                                    </u> | L                        |

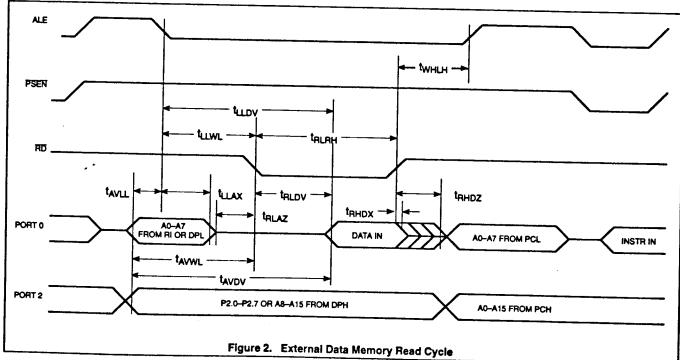

| t <sub>RLRH</sub>   | 2, 3     | RD pulse width                                                                             | 400          |                                                  | 6t <sub>CLCL</sub> -100  |                                              | ns                       |

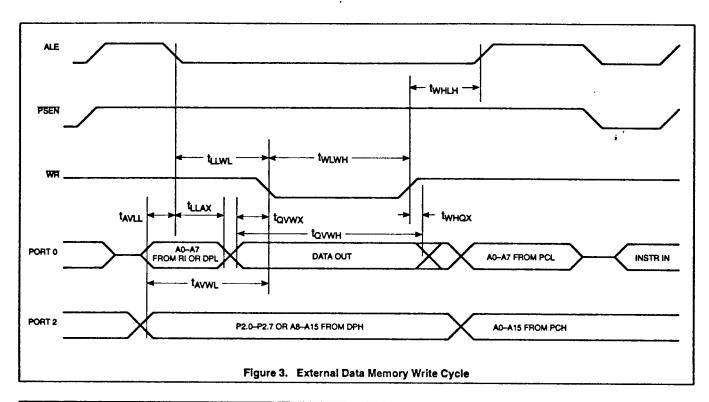

| twwh                | 2, 3     | WR pulse width                                                                             | 400          |                                                  | 6t <sub>CLCL</sub> -100  |                                              | ns                       |

| <sup>t</sup> RLDV   | 2, 3     | RD low to valid data in                                                                    |              | 252                                              |                          | 5t <sub>CLCL</sub> -165                      | ns                       |

| <sup>†</sup> янох   | 2, 3     | Data hold after RD                                                                         | 0            |                                                  | 0                        | 0202                                         | ns                       |

| t <sub>RHDZ</sub>   | 2, 3     | Data float after RD                                                                        |              | 97                                               |                          | 2t <sub>CLCL</sub> -70                       | ns                       |

| (TTDA               | 2, 3     | ALE low to valid data in                                                                   |              | 517                                              | ·                        | 8t <sub>CLCL</sub> -150                      | ns                       |

| <sup>t</sup> AVDV   | 2, 3     | Address to valid data in                                                                   |              | 585                                              |                          | 9t <sub>CLCL</sub> -165                      | ns                       |

| tuwi                | 2, 3     | ALE low to RD or WR low                                                                    | 200          | 300                                              | 3t <sub>CLCL</sub> -50   | 3t <sub>CLCL</sub> +50                       | ns                       |

| t <sub>AVWL</sub>   | 2, 3     | Address valid to WR low or RD low                                                          | 203          | <del></del>                                      | 4t <sub>CLCL</sub> -130  |                                              | ns                       |

| tavwx               | 2, 3     | Data valid to WR transition                                                                | 23           |                                                  | t <sub>CLCL</sub> -60    |                                              | ns                       |

| tа∨wн               | 2, 3     | Data valid to WR high                                                                      | 433          |                                                  | 7t <sub>CLCL</sub> -150  |                                              | ns                       |

| twhqx               | , · 2, 3 | Data hold after WR                                                                         | 33           |                                                  | t <sub>CLCL</sub> -50    |                                              | ns                       |

| RLAZ                | 2, 3     | RD low to address float                                                                    |              | 20                                               |                          | 20                                           | ns                       |

| lwhch               | 2, 3     | RD or WR high to ALE high                                                                  | 43           | 123                                              | t <sub>CLCL</sub> -40    | t <sub>CLCL</sub> +40                        | ns                       |

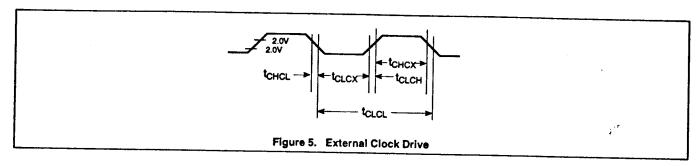

| External Clo        | ck       |                                                                                            |              |                                                  | L                        |                                              |                          |

| СНСХ                | 5        | High time                                                                                  | 20           |                                                  | 20                       |                                              | ns                       |

| CLCX                | 5        | Low time                                                                                   | 20           |                                                  | 20                       | <u>-</u>                                     | ns                       |

| CLCH                | 5        | Rise time                                                                                  |              | 20                                               |                          | 20                                           | ns                       |

| CHCL                | 5        | Fall time                                                                                  |              | 20                                               |                          | 20                                           | ns                       |

Parameters are valid over operating temperature range unless otherwise specified.

Load capacitance for port 0, ALE, and PSEN = 100pF, load capacitance for all other outputs = 80pF.

## 8031AH/8051AH

## **EXPLANATION OF THE AC SYMBOLS**

Each timing symbol has five characters. The first character is always "t" (= time). The other characters, depending on their positions, indicate the name of a signal or the logical status of that signal. The designations are:

status of that signal. The designations are:

A - Address

C - ClockD - Input dataH - Logic level high

I - Instruction (program memory contents)

L - Logic level low, or ALE

P - PSEN

Q - Output data

R - RD signal t - Time

V - Valid

W- WR signal

X - No longer a valid logic level

Z - Float

Examples: t<sub>AVLL</sub>= Time for address valid to ALE low.

tLLPL= Time for ALE low to

PSEN low.

## 8031AH/8051AH

# 8031AH/8051AH