# Chapter 18

# **Electrical Specifications and Timings**

This chapter contains electrical and timing information for the TMS370 family devices. This information is presented according to device category.

| Topic | Paç                                                                           | је         |

|-------|-------------------------------------------------------------------------------|------------|

| 18.1  | Timing Parameter Symbols                                                      | -2         |

| 18.2  | Parameter Measurements 18-                                                    | -2         |

| 18.3  | Absolute Maximum Ratings for All TMS370 Devices 18-                           | -3         |

| 18.4  | External Crystal/Clock Connections and Typical Circuits for Loads and Buffers | -4         |

| 18.5  | General-Purpose Output Signal Timings 18-                                     | -6         |

| 18.6  | EPROM/EEPROM Specifications                                                   | -7         |

| 18.7  | TMS370Cx0xA and TMS370Cx0x Specifications 18-                                 | -8         |

| 18.8  | TMS370Cx1xA and TMS370Cx1xB Specifications 18-1                               | 2          |

| 18.9  | TMS370Cx2xA and TMS370Cx2x Specifications 18-1                                | 6          |

| 18.10 | TMS370Cx32A Specifications                                                    | 20         |

| 18.11 | TMS370Cx36A Specifications                                                    | 24         |

| 18.12 | TMS370Cx4xA Specifications                                                    | 29         |

| 18.13 | TMS370Cx5xA and TMS370Cx5xB Specifications 18-3                               | 14         |

| 18.14 | TMS370Cx6xA Specifications                                                    | 13         |

| 18.15 | TMS370Cx7xA Specifications                                                    | <b>i1</b>  |

| 18.16 | TMS370Cx8xA Specifications                                                    | <b>7</b>   |

| 18.17 | TMS370Cx9xA Specifications                                                    | <b>i</b> 2 |

| 18.18 | TMS370CxAxA Specifications                                                    | <b>38</b>  |

| 18.19 | TMS370CxBxA Specifications                                                    | 73         |

| 18.20 | TMS370CxCxA Specifications                                                    | 79         |

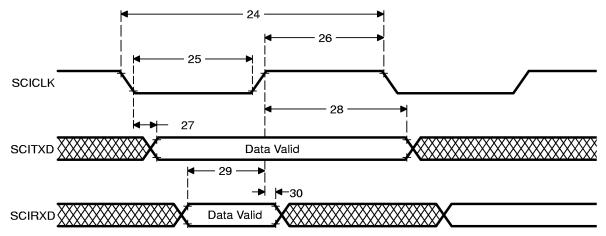

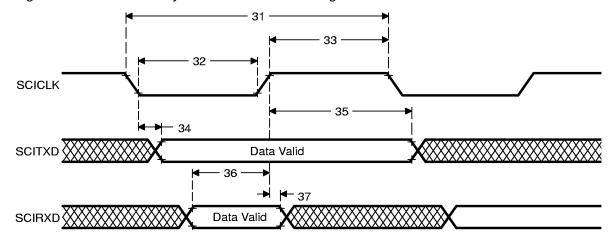

| 18.21 | SCI Timings                                                                   | <b>;4</b>  |

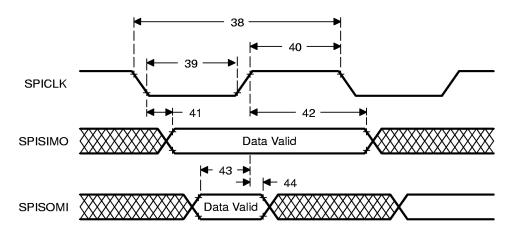

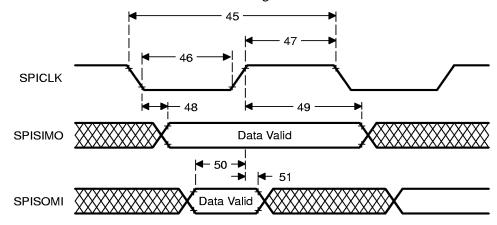

| 18.22 | <b>SPI Timings</b>                                                            | <b>36</b>  |

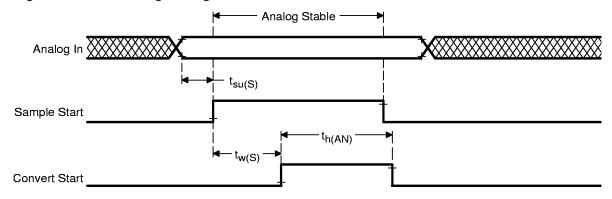

| 18.23 | Analog-to-Digital Converter 1 (ADC1) Module Specifications 18-8               | 39         |

| 18.24 | Analog-to-Digital Converter 2 (ADC2) Module Specifications 18-9               | )2         |

| 18.25 | Analog-to-Digital Converter 3 (ADC3) Module Specifications 18-9               | )4         |

### 18.1 Timing Parameter Symbols

Timing parameter symbols occur throughout this chapter. They were created in accordance with JEDEC standard 100A. To keep the symbols short, some of the signal names and other operational terms were abbreviated as follows:

| Α   | Address     | RXD  | SCIRXD     |

|-----|-------------|------|------------|

| AR  | Array mode  | S    | Slave mode |

| В   | Byte mode   | SC   | SYSCLK     |

| CI  | XTAL2/CLKIN | SCC  | SCICLK     |

| D   | Data        | SIMO | SPISIMO    |

| E   | EDS         | SOMI | SPISOMI    |

| FE  | Final       | SPC  | SPICLK     |

| ΙE  | Initial     | TXD  | SCITXD     |

| M   | Master mode | W    | Write      |

| PGM | Programming | WT   | WAIT       |

| R   | Read        |      |            |

Lowercase subscripts and their meanings are:

| С | Cycle time (period) | r  | Rise time              |

|---|---------------------|----|------------------------|

| d | Delay time          | su | Setup time             |

| f | Fall time           | V  | Valid time             |

| h | Hold time           | w  | Pulse duration (width) |

The following additional letters are used with these meanings:

| П | підп | V | valiu          |

|---|------|---|----------------|

| L | Low  | Z | High impedance |

#### 18.2 Parameter Measurements

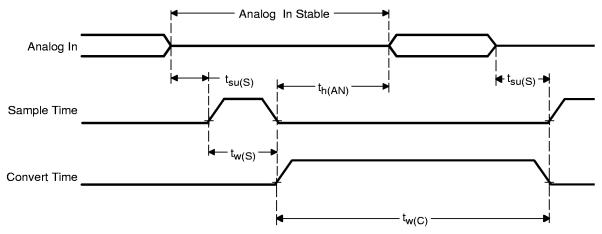

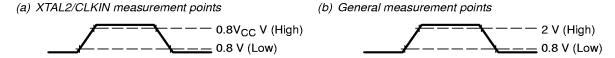

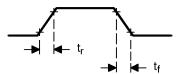

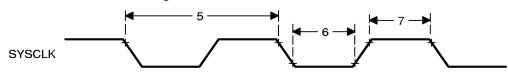

All timings are calculated between high and low measurement points as indicated in Figure 18–1.

Figure 18-1. Measurement Points for Timings

#### 18.3 Absolute Maximum Ratings for All TMS370 Devices

For all TMS370 devices, Table 18–1 provides the absolute maximum ratings over the operating free-air temperature range. This operating free-air temperature range is specified for your device in its respective section of this chapter.

Stresses beyond those listed in Table 18–1 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the recommended operating conditions for the specific device is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Table 18–1. Absolute Maximum Ratings Over Operating Free-Air Temperature Range (See Note 1)

| Parameter                               |                                                                                                                                                           | Maximum<br>Rating |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Supply voltage range, V <sub>C</sub>    | CC (see Note 1)                                                                                                                                           | -0.6 V to 7 V     |

| Input voltage range                     | All pins except MC                                                                                                                                        | -0.6 V to 7 V     |

|                                         | MC                                                                                                                                                        | -0.6 V to 14 V    |

| Input clamp current, I <sub>IK</sub> (V | V <sub>I</sub> < 0 V or V <sub>I</sub> > V <sub>CC</sub> )                                                                                                | ± 20 mA           |

| Output clamp current, IOK               | $(V_O < 0 \text{ V or } V_O > V_{CC})$                                                                                                                    | ± 20 mA           |

| Continuous output current               | t per buffer, I <sub>O</sub> (V <sub>O</sub> = 0 V to V <sub>CC</sub> ) (see Note 2)                                                                      | ± 10 mA           |

| Maximum supply current,                 | lcc                                                                                                                                                       | 170 mA            |

| Maximum supply current,                 | I <sub>SS</sub>                                                                                                                                           | -170 mA           |

| Continuous power dissipation            | TMS370Cx0xA, TMS370Cx0x, TMS370Cx1xA, TMS370Cx1xB, TMS370CxCxA                                                                                            | 500 mW            |

|                                         | TMS370Cx32A                                                                                                                                               | 800 mW            |

|                                         | TMS370Cx2xA, TMS370Cx2x, TMS370Cx36A, TMS370Cx4xA, TMS370Cx5xA, TMS370Cx5xB, TMS370Cx6xA, TMS370Cx7xA, TMS370Cx8xA, TMS370Cx9xA, TMS370CxAxA, TMS370CxBxA | 1 W               |

| Storage temperature rang                | ge, T <sub>stg</sub>                                                                                                                                      | -65°C to 150°C    |

Notes: 1) Unless otherwise noted, all voltage values are with respect to VSS (ground).

Electrical Specifications and Timings

Electrical characteristics are specified with all output buffers loaded with the specified I<sub>O</sub>. Exceeding the specified I<sub>O</sub> in any buffer may affect the levels on other buffers.

# 18.4 External Crystal/Clock Connections and Typical Circuits for Loads and Buffers

Figure 18–2 illustrates how to connect the crystal/ceramic resonator and the external clock signal. This figure is valid for all TMS370 family devices.

Figure 18-2. Recommended Crystal/Clock Connections

Notes: 1) The crystal/ceramic resonator frequency is four times the reciprocal of the system clock period.

2) The values of C1 and C2 are typically 15 pF and the value of C3 is typically 50 pF. See the manufacturer's recommendations for ceramic resonators.

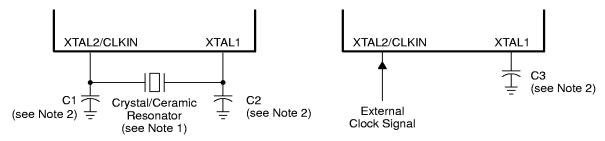

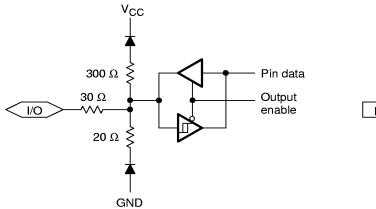

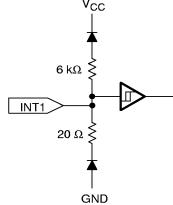

Figure 18–3 is an output load circuit that you can use for any TMS370 device.

Figure 18-3. Typical Output Load Circuit

Case 1:  $V_O = V_{OH} = 2.4 \text{ V}$ ; Load Voltage = 0 V Case 2:  $V_O = V_{OL} = 0.4 \text{ V}$ ; Load Voltage = 2.1 V

Note: All measurements are made with the pin loading as shown unless otherwise noted. All measurements are made with XTAL2/CLKIN driven by an external square wave signal with a 50% duty cycle and rise and fall times less than 10 ns unless otherwise stated.

Figure 18-4. Typical Buffer Circuitry

# 18.5 General-Purpose Output Signal Timings

Refer to Sections 18.1 and 18.2 for timing symbol definitions and parameter measurement points. The timings shown in this section are valid for all TMS370 family devices.

Table 18–2. General-Purpose Output Signal Timing Requirements

| Parameter      |           | Min | Nom | Max | Unit |

|----------------|-----------|-----|-----|-----|------|

| t <sub>r</sub> | Rise time |     | 30  |     | ns   |

| t <sub>f</sub> | Fall time |     | 30  |     | ns   |

Figure 18-5. Switching Time Measurement Points

### 18.6 EPROM/EEPROM Specifications

Refer to Sections 18.1 and 18.2 for timing symbol definitions and parameter measurement points. The timings shown in this section are valid for all 'C702, 'C722, 'CxxxA, and 'CxxxB family devices except the 'C3xxA device.

Table 18-3. EEPROM Timing Requirements for Programming

| Parameter              |                                                                                |    | Max | Unit |

|------------------------|--------------------------------------------------------------------------------|----|-----|------|

| t <sub>w(PGM)B</sub>   | Pulse duration, programming signal to ensure valid data is stored (byte mode)  | 10 |     | ms   |

| t <sub>w(PGM)</sub> AR | Pulse duration, programming signal to ensure valid data is stored (array mode) | 20 |     | ms   |

Table 18-4. Recommended EPROM Operating Conditions for Programming

| Parameter       | Parameter                                                            |                   |      | Nom  | Max  | Unit |

|-----------------|----------------------------------------------------------------------|-------------------|------|------|------|------|

| V <sub>CC</sub> | Supply voltage                                                       |                   | 4.75 | 5.5  | 6    | ٧    |

| V <sub>PP</sub> | Supply voltage at MC pin                                             |                   | 13   | 13.2 | 13.5 | ٧    |

| IPP             | Supply current at MC pin during programming (V <sub>PP</sub> = 13 V) |                   |      | 30   | 50   | mA   |

| SYSCLK          | System clock operating frequency Divide-by-4 clock                   |                   | 0.5  |      | 5    | MHz  |

|                 |                                                                      | Divide-by-1 clock | 2    |      | 5    | MHz  |

Table 18-5. EPROM Timing Requirements for Programming

| Parameter            |                                               | Min  | Nom  | Max | Unit |

|----------------------|-----------------------------------------------|------|------|-----|------|

| <sup>t</sup> w(EPGM) | Pulse duration, programming signal (see Note) | 0.40 | 0.50 | 3   | ms   |

Note: Programming pulse is active when both EXE (EPCTL.0) and VPPS (EPCTL.6) are set.

#### Note:

The parameters  $V_{PP}$  and  $t_{w(EPGM)}$  for EPROM are different for the TMS370Cxxx devices (vs. the TMS370CxxxA or TMS370CxxxB devices). Refer to subsection A.9.3, *Differences in EPROM Specifications*, on page A-10.

#### 18.7 TMS370Cx0xA and TMS370Cx0x Specifications

The tables in this section give specifications that apply to the devices in the TMS370Cx0xA and TMS370Cx0x categories. These devices include the TMS370C002A, TMS370C302A, TMS370C702, and SE370C702.

#### 18.7.1 TMS370Cx0xA and TMS370Cx0x Electrical Specifications

Stresses beyond those listed in Table 18–1 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the recommended operating conditions in Table 18–6 is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Table 18–6. Recommended Operating Conditions (See Note 1)

| Paran           | neter                        |                                              | Min                | Nom  | Max             | Unit |

|-----------------|------------------------------|----------------------------------------------|--------------------|------|-----------------|------|

| Vcc             | Supply voltage (see Note 1)  | Supply voltage (see Note 1)                  |                    |      | 5.5             | ٧    |

|                 | RAM data-retention supply vo | Itage (see Note 2)                           | 3                  |      | 5.5             | V    |

| V <sub>IL</sub> | Low-level input voltage      | All pins except MC                           | V <sub>SS</sub>    |      | 0.8             | ٧    |

|                 |                              | MC, normal operation                         | V <sub>SS</sub>    |      | 0.3             | ٧    |

| V <sub>IH</sub> | High-level input voltage     | All pins except MC, XTAL2/CLKIN, and RESET   | 2                  |      | V <sub>CC</sub> | ٧    |

|                 |                              | XTAL2/CLKIN                                  | 0.8V <sub>CC</sub> |      | V <sub>CC</sub> | ٧    |

|                 |                              | RESET                                        | 0.7V <sub>CC</sub> |      | Vcc             | ٧    |

| V <sub>MC</sub> | MC (mode control) voltage    | EEPROM write-protect override (WPO) mode     | 11.7               | 12   | 13              | ٧    |

|                 |                              | EPROM programming voltage (V <sub>PP</sub> ) | 13                 | 13.2 | 13.5            | ٧    |

|                 |                              | Microcomputer mode                           | V <sub>SS</sub>    |      | 0.3             | ٧    |

| T <sub>A</sub>  | Operating free-air tempera-  | L version                                    | 0                  |      | 70              | °C   |

|                 | ture                         | A version                                    | -40                |      | 85              | °С   |

|                 |                              | T version                                    | -40                |      | 105             | °C   |

Notes:

- 1) Unless otherwise noted, all voltage values are with respect to VSS (ground).

- 2) RESET must be activated externally when V<sub>CC</sub> or SYSCLK is out of the recommended operating range.

Table 18–7. Electrical Characteristics Over Recommended Operating Free-Air Temperature Range

| Param           | Parameter                                                      |          | Test Conditions                              | Min                | Тур | Max | Unit |

|-----------------|----------------------------------------------------------------|----------|----------------------------------------------|--------------------|-----|-----|------|

| V <sub>OL</sub> | Low-level output vo                                            | ltage    | I <sub>OL</sub> = 1.4 mA                     |                    |     | 0.4 | ٧    |

| V <sub>OH</sub> | High-level output vo                                           | oltage   | I <sub>OH</sub> = -50 μA                     | 0.9V <sub>CC</sub> |     |     | V    |

|                 |                                                                |          | I <sub>OH</sub> = −2 mA                      | 2.4                |     |     | V    |

| Iį              | Input current                                                  | MC       | 0 V ≤ V <sub>I</sub> ≤ 0.3 V                 |                    |     | 10  | μΑ   |

|                 |                                                                |          | 0.3 V < V <sub>I</sub> ≤ 13 V                |                    |     | 650 | μΑ   |

|                 |                                                                |          | 12 V ≤ V <sub>I</sub> ≤ 13 V<br>(see Note 1) |                    |     | 50  | mA   |

|                 |                                                                | I/O pins | $0 \ V \le V_I \le V_{CC}$                   |                    |     | ±10 | μΑ   |

| loL             | Low-level output cu                                            | ırrent   | V <sub>OL</sub> = 0.4 V                      | 1.4                |     |     | mA   |

| Іон             | High-level output co                                           | urrent   | V <sub>OH</sub> = 0.9V <sub>CC</sub>         | -50                |     |     | μΑ   |

|                 |                                                                |          | V <sub>OH</sub> = 2.4 V                      | -2                 |     |     | mA   |

| lcc             | Supply current (operating mode) OSC POWER bit = 0 (see Note 4) |          | See Notes 2 and 3<br>SYSCLK = 5 MHz          |                    | 20  | 36  | mA   |

|                 |                                                                |          | See Notes 2 and 3<br>SYSCLK = 3 MHz          |                    | 13  | 25  | mA   |

|                 |                                                                |          | See Notes 2 and 3<br>SYSCLK = 0.5 MHz        |                    | 5   | 11  | mA   |

| lcc             | Supply current (ST/OSC POWER bit =                             | ,        | See Notes 2 and 3<br>SYSCLK = 5 MHz          |                    | 10  | 17  | mA   |

|                 |                                                                |          | See Notes 2 and 3<br>SYSCLK = 3 MHz          |                    | 6.5 | 11  | mA   |

|                 |                                                                |          | See Notes 2 and 3<br>SYSCLK = 0.5 MHz        |                    | 2   | 3.5 | mA   |

| lcc             | Supply current (ST/OSC POWER bit =                             | ,        | See Notes 2 and 3<br>SYSCLK = 3 MHz          |                    | 4.5 | 8.6 | mA   |

|                 |                                                                |          | See Notes 2 and 3<br>SYSCLK = 0.5 MHz        |                    | 1.5 | 3.0 | mA   |

| Icc             | Supply current (HA                                             | LT mode) | See Note 2<br>XTAL2/CLKIN < 0.2 V            |                    | 1   | 30  | μΑ   |

Notes:

- 1) Input current Ipp is a maximum of 50 mA only when EPROM is being programmed.

- 2) Single-chip mode, ports configured as inputs or as outputs with no load. All inputs ≤ 0.2 V or ≥ V<sub>CC</sub> − 0.2 V.

- 3) XTAL2/CLKIN is driven with an external square wave signal with 50% duty cycle and rise and fall times less than 10 ns. Current can be higher with a crystal oscillator. At 5-MHz SYSCLK, this extra current = 0.01 mA x (total load capacitance + crystal capacitance in pF).

- 4) Maximum operating current = 5.6 (SYSCLK) + 8 mA.

- 5) Maximum standby current = 3 (SYSCLK) + 2 mA (OSC POWER bit = 0).

- 6) Maximum standby current = 2.24 (SYSCLK) + 1.9 mA (OSC POWER bit = 1, only valid up to 3 MHz of SYSCLK).

Electrical Specifications and Timings

#### 18.7.2 TMS370Cx0xA and TMS370Cx0x Timings

Refer to Sections 18.1 and 18.2 (both on page 18-2) for timing symbol definitions and parameter measurement points.

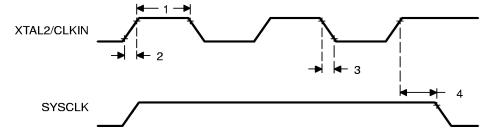

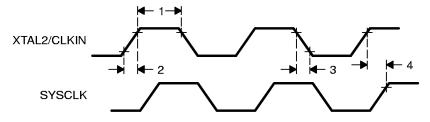

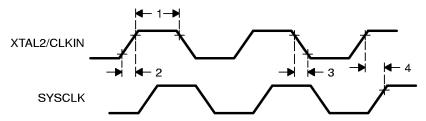

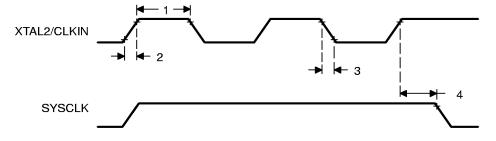

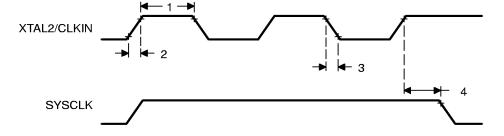

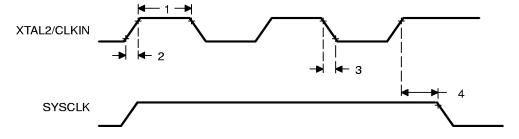

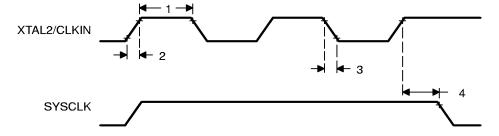

Table 18–8. External Clocking Requirements for Divide-by-4 Clock (See Note 1)

| No. | Parameter               | Parameter Parame |     |     | Unit |

|-----|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| 1   | t <sub>w(CI)</sub>      | Pulse duration, XTAL2/CLKIN (see Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20  |     | ns   |

| 2   | <sup>t</sup> r(Cl)      | Rise time, XTAL2/CLKIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 30  | ns   |

| 3   | t <sub>f(CI)</sub>      | Fall time, XTAL2/CLKIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 30  | ns   |

| 4   | <sup>t</sup> d(CIH-SCL) | Delay time, XTAL2/CLKIN rise to SYSCLK fall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 100 | ns   |

|     | CLKIN                   | Crystal operating frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2   | 20  | MHz  |

|     | SYSCLK                  | Internal system clock operating frequency (see Note 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.5 | 5   | MHz  |

- Notes: 1) For V<sub>IL</sub> and V<sub>IH</sub>, refer to recommended operating conditions in Table 18–6.

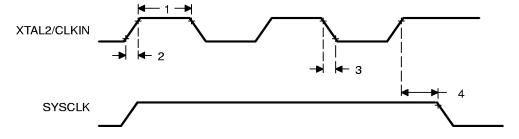

- 2) This pulse can be either a high pulse, as illustrated in Figure 18-6, which extends from the earliest valid high to the final valid high in an XTAL2/CLKIN cycle, or a low pulse, which extends from the earliest valid low to the final valid low in an XTAL2/CLKIN cycle.

- 3) SYSCLK = CLKIN/4

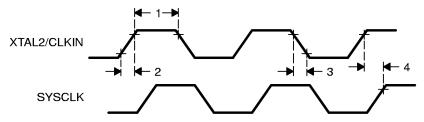

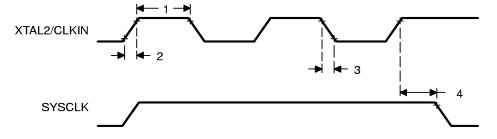

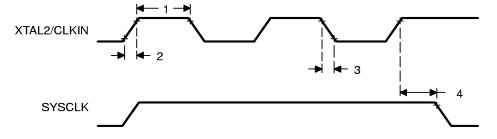

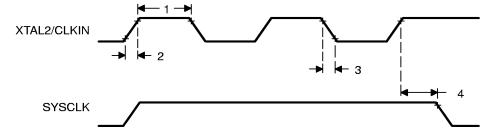

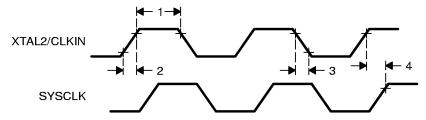

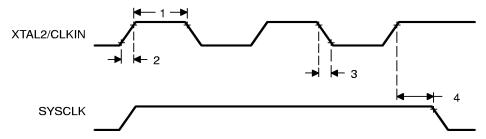

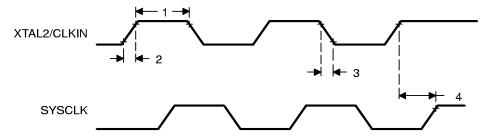

Figure 18-6. External Clock Timing for Divide-by-4 Clock

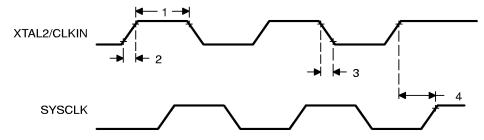

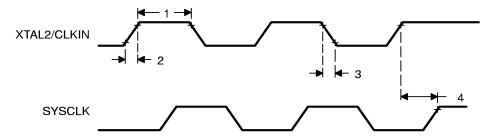

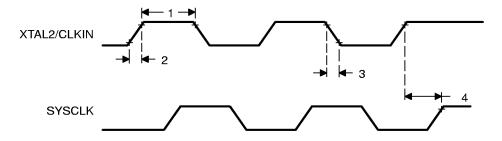

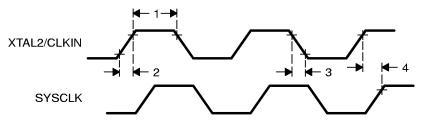

Table 18-9. External Clocking Requirements for Divide-by-1 Clock (PLL) (see Note 1)

| No. | Parameter               |                                                               | Min | Max | Unit |

|-----|-------------------------|---------------------------------------------------------------|-----|-----|------|

| 1   | t <sub>w(CI)</sub>      | Pulse duration, XTAL2/CLKIN (see Note 2)                      | 20  |     | ns   |

| 2   | t <sub>r(CI)</sub>      | Rise time, XTAL2/CLKIN                                        |     | 30  | ns   |

| 3   | t <sub>f(CI)</sub>      | Fall time, XTAL2/CLKIN                                        |     | 30  | ns   |

| 4   | <sup>t</sup> d(CIH-SCH) | Delay time, XTAL2/CLKIN rise to SYSCLK rise                   |     | 100 | ns   |

|     | CLKIN                   | CLKIN Crystal operating frequency                             |     | 5   | MHz  |

|     | SYSCLK                  | SYSCLK Internal system clock operating frequency (see Note 3) |     | 5   | MHz  |

Notes: 1) For V<sub>IL</sub> and V<sub>IH</sub>, refer to recommended operating conditions in Table 18–6.

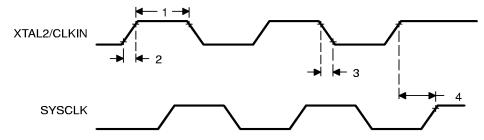

- 2) This pulse can be either a high pulse, as illustrated in Figure 18–7, which extends from the earliest valid high to the final valid high in an XTAL2/CLKIN cycle, or a low pulse, which extends from the earliest valid low to the final valid low in an XTAL2/CLKIN cycle.

- 3) SYSCLK = CLKIN/1

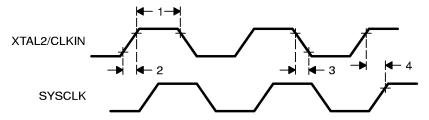

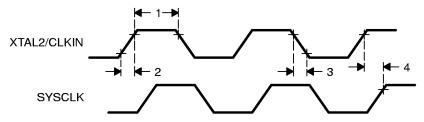

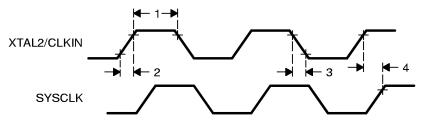

Figure 18-7. External Clock Timing for Divide-by-1 Clock

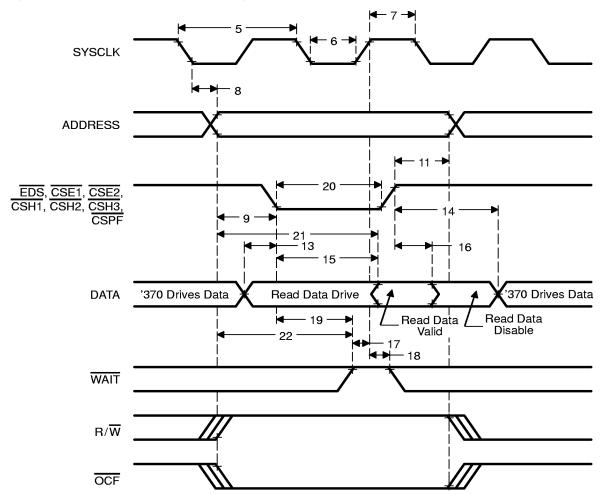

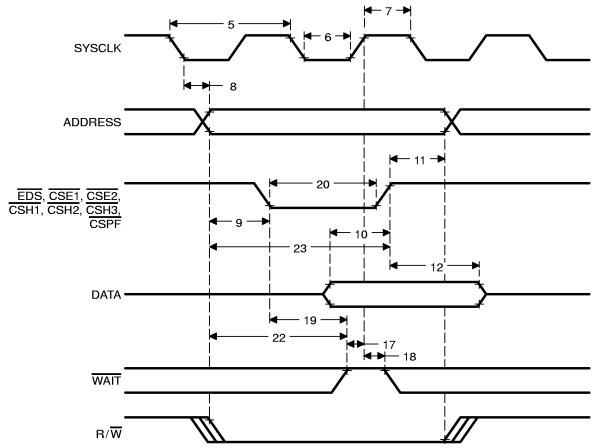

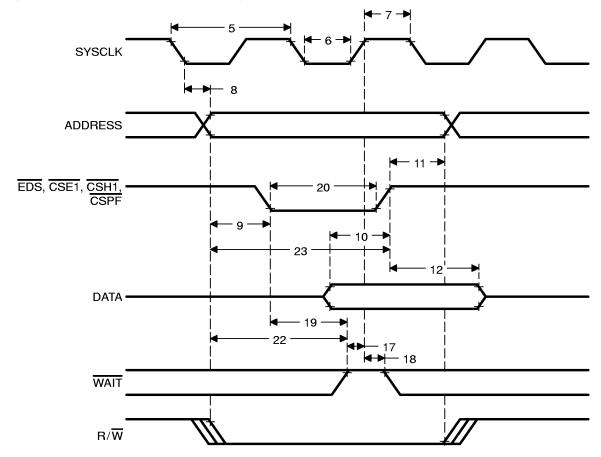

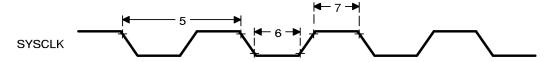

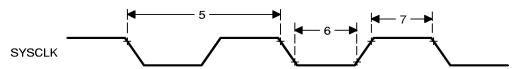

Table 18–10. Switching Characteristics and Timing Requirements (See Note)

| No. | Parameter                         | Parameter                   |                   |                        | Max                    | Unit |

|-----|-----------------------------------|-----------------------------|-------------------|------------------------|------------------------|------|

| 5   | t <sub>c</sub> Cycle time, SYSCLK |                             | Divide-by-4 clock | 200                    | 2000                   | ns   |

|     |                                   |                             | Divide-by-1 clock | 200                    | 500                    | ns   |

| 6   | t <sub>w(SCL)</sub>               | Pulse duration, SYSCLK low  |                   | 0.5t <sub>c</sub> – 20 | 0.5t <sub>c</sub>      | ns   |

| 7   | t <sub>w(SCH)</sub>               | Pulse duration, SYSCLK high |                   | 0.5t <sub>c</sub>      | 0.5t <sub>c</sub> + 20 | ns   |

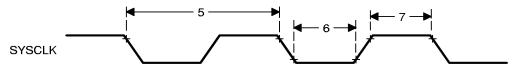

**Note:**  $t_c$  = system clock cycle time = 1/SYSCLK

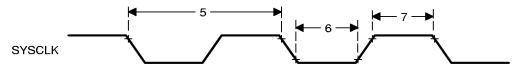

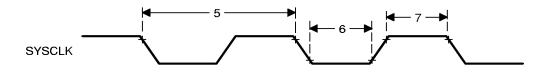

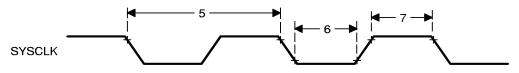

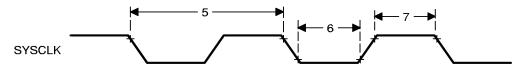

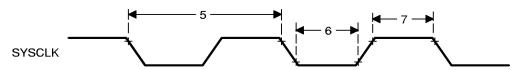

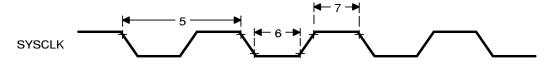

Figure 18-8. SYSCLK TIming

Electrical Specifications and Timings

#### 18.8 TMS370Cx1xA and TMS370Cx1xB Specifications

The tables in this section give specifications that apply to the devices in the TMS370Cx1xA and the TMS370Cx1xB categories. These devices include the TMS370C010A, TMS370C012A, TMS370C310A, TMS370C311A, TMS370C312A, TMS370C712B, SE370C712A, and SE370C712B.

#### 18.8.1 TMS370Cx1xA and TMS370Cx1xB Electrical Specifications

Stresses beyond those listed in Table 18–1 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the recommended operating conditions in Table 18–11 is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Table 18-11. Recommended Operating Conditions (See Note 1)

| Parai           | neter                       |                                              | Min                | Nom  | Max             | Unit |

|-----------------|-----------------------------|----------------------------------------------|--------------------|------|-----------------|------|

| v <sub>cc</sub> | Supply voltage (see Note 1) |                                              |                    | 5    | 5.5             | ٧    |

|                 | RAM data-retention supply v | roltage (see Note 2)                         | 3                  |      | 5.5             | ٧    |

| V <sub>IL</sub> | Low-level input voltage     | All pins except MC                           | V <sub>SS</sub>    |      | 0.8             | ٧    |

|                 |                             | MC, normal operation                         | V <sub>SS</sub>    |      | 0.3             | ٧    |

| V <sub>IH</sub> | High-level input voltage    | All pins except MC, XTAL2/CLKIN, and RESET   | 2                  |      | V <sub>CC</sub> | ٧    |

|                 |                             | XTAL2/CLKIN                                  | 0.8V <sub>CC</sub> |      | v <sub>cc</sub> | V    |

|                 |                             | RESET                                        | 0.7V <sub>CC</sub> |      | Vcc             | ٧    |

| V <sub>MC</sub> | MC (mode control) voltage   | EEPROM write-protect override (WPO) mode     | 11.7               | 12   | 13              | ٧    |

|                 |                             | EPROM programming voltage (V <sub>PP</sub> ) | 13                 | 13.2 | 13.5            | ٧    |

|                 |                             | Microcomputer mode                           | V <sub>SS</sub>    |      | 0.3             | V    |

| T <sub>A</sub>  | Operating free-air tempera- | L version                                    | 0                  |      | 70              | °C   |

|                 | ture                        | A version                                    | -40                |      | 85              | °C   |

|                 |                             | T version                                    | -40                |      | 105             | °C   |

Notes: 1) Unless otherwise noted, all voltage values are with respect to VSS (ground).

<sup>2)</sup> RESET must be externally activated when V<sub>CC</sub> or SYSCLK is not within the recommended operating range.

Table 18–12. Electrical Characteristics Over Recommended Operating Free-Air Temperature Range

| Parame          | eter                                                           |                          | Test Conditions                                                  | Min                | Тур | Max  | Unit |

|-----------------|----------------------------------------------------------------|--------------------------|------------------------------------------------------------------|--------------------|-----|------|------|

| V <sub>OL</sub> | Low-level output vo                                            | oltage                   | I <sub>OL</sub> = 1.4 mA                                         |                    |     | 0.4  | V    |

| V <sub>OH</sub> | High-level output ve                                           | oltage                   | I <sub>OH</sub> = -50 μA                                         | 0.9V <sub>CC</sub> |     |      | V    |

|                 |                                                                |                          | I <sub>OH</sub> = −2 mA                                          | 2.4                |     |      | V    |

| Iį              | Input current                                                  | MC                       | $0 \text{ V} \leq \text{V}_{\text{I}} \leq 0.3 \text{ V}$        |                    |     | 10   | μΑ   |

|                 |                                                                |                          | 0.3 V < V <sub>I</sub> ≤ 13 V                                    |                    |     | 650  | μΑ   |

|                 |                                                                |                          | 12 V ≤ V <sub>I</sub> ≤ 13 V<br>(see Note 1)                     |                    |     | 50   | mA   |

|                 |                                                                | I/O pins                 | $0 \text{ V} \leq \text{V}_{\text{I}} \leq \text{V}_{\text{CC}}$ |                    |     | ± 10 | μΑ   |

| l <sub>OL</sub> | Low-level output cu                                            | Low-level output current |                                                                  | 1.4                |     |      | mA   |

| ЮН              | High-level output co                                           | urrent                   | V <sub>OH</sub> = 0.9V <sub>CC</sub>                             | -50                |     |      | μΑ   |

|                 |                                                                |                          | V <sub>OH</sub> = 2.4 V                                          | -2                 |     |      | mA   |

| lcc             | Supply current (operating mode) OSC POWER bit = 0 (see Note 4) |                          | See Notes 2 and 3<br>SYSCLK = 5 MHz                              |                    | 20  | 36   | mA   |

|                 |                                                                |                          | See Notes 2 and 3<br>SYSCLK = 3 MHz                              |                    | 13  | 25   | mA   |

|                 |                                                                |                          | See Notes 2 and 3<br>SYSCLK = 0.5 MHz                            |                    | 5   | 11   | mA   |

| Icc             | Supply current (ST. OSC POWER bit =                            |                          | See Notes 2 and 3<br>SYSCLK = 5 MHz                              |                    | 10  | 17   | mA   |

|                 |                                                                |                          | See Notes 2 and 3<br>SYSCLK = 3 MHz                              |                    | 6.5 | 11   | mA   |

|                 |                                                                |                          | See Notes 2 and 3<br>SYSCLK = 0.5 MHz                            |                    | 2   | 3.5  | mA   |

| lcc             | Supply current (ST                                             | ,                        | See Notes 2 and 3<br>SYSCLK = 3 MHz                              |                    | 4.5 | 8.6  | mA   |

|                 |                                                                |                          | See Notes 2 and 3<br>SYSCLK = 0.5 MHz                            |                    | 1.5 | 3.0  | mA   |

| Icc             | Supply current (HA                                             | LT mode)                 | See Note 2<br>XTAL2/CLKIN < 0.2 V                                |                    | 1   | 30   | μА   |

Notes: 1)

- 1) Input current Ipp is a maximum of 50 mA only when EPROM is being programmed.

- 2) Single-chip mode, ports configured as inputs or as outputs with no load. All inputs ≤ 0.2 V or ≥ V<sub>CC</sub> − 0.2 V.

- 3) XTAL2/CLKIN is driven with an external square wave signal with 50% duty cycle and rise and fall times less than 10 ns. Current can be higher with a crystal oscillator. At 5-MHz SYSCLK, this extra current = 0.01 mA × (total load capacitance + crystal capacitance in pF).

- 4) Maximum operating current = 5.6(SYSCLK) + 8 mA.

- 5) Maximum standby current = 3(SYSCLK) + 2 mA (OSC POWER bit = 0).

- 6) Maximum standby current = 2.24(SYSCLK) + 1.9 mA (OSC POWER bit = 1; valid only up to 3-MHz SYSCLK).

Electrical Specifications and Timings

#### 18.8.2 TMS370Cx1xA and TMS370Cx1xB Timings

Refer to Sections 18.1 and 18.2 (both on page 18-2) for timing symbol definitions and parameter measurement points.

Table 18–13. External Clocking Requirements for Divide-by-4 Clock (See Note 1)

| No. | Parameter               |                                                        | Min | Max | Unit |

|-----|-------------------------|--------------------------------------------------------|-----|-----|------|

| 1   | t <sub>w(CI)</sub>      | Pulse duration, XTAL2/CLKIN (see Note 2)               | 20  |     | ns   |

| 2   | t <sub>r(CI)</sub>      | Rise time, XTAL2/CLKIN                                 |     | 30  | ns   |

| 3   | t <sub>f(CI)</sub>      | Fall time, XTAL2/CLKIN                                 |     | 30  | ns   |

| 4   | <sup>t</sup> d(CIH-SCL) | Delay time, XTAL2/CLKIN rise to SYSCLK fall            |     | 100 | ns   |

|     | CLKIN                   | Crystal operating frequency                            | 2   | 20  | MHz  |

|     | SYSCLK                  | Internal system clock operating frequency (see Note 3) | 0.5 | 5   | MHz  |

- Notes: 1) For V<sub>IL</sub> and V<sub>IH</sub>, refer to recommended operating conditions in Table 18–11.

- 2) This pulse may be either a high pulse, as illustrated in Figure 18-9, which extends from the earliest valid high to the final valid high in an XTAL2/CLKIN cycle or a low pulse, which extends from the earliest valid low to the final valid low in an XTAL2/CLKIN cycle.

- 3) SYSCLK = CLKIN/4

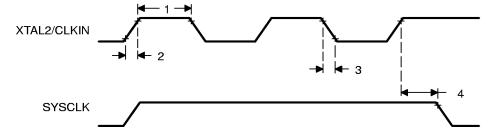

Figure 18–9. External Clock Timing for Divide-by-4 Clock

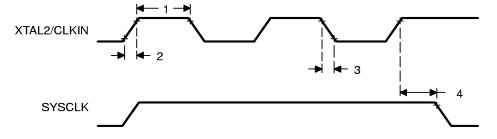

Table 18–14. External Clocking Requirements for Divide-by-1 Clock (PLL) (see Note 1)

| No. | Parameter                         |                                                               | Min | Max | Unit |

|-----|-----------------------------------|---------------------------------------------------------------|-----|-----|------|

| 1   | t <sub>w(CI)</sub>                | Pulse duration, XTAL2/CLKIN (see Note 2)                      | 20  |     | ns   |

| 2   | t <sub>r(CI)</sub>                | Rise time, XTAL2/CLKIN                                        |     | 30  | ns   |

| 3   | t <sub>f(CI)</sub>                | Fall time, XTAL2/CLKIN                                        |     | 30  | ns   |

| 4   | <sup>t</sup> d(CIH-SCH)           | Delay time, XTAL2/CLKIN rise to SYSCLK rise                   |     | 100 | ns   |

|     | CLKIN Crystal operating frequency |                                                               | 2   | 5   | MHz  |

|     | SYSCLK                            | SYSCLK Internal system clock operating frequency (see Note 3) |     | 5   | MHz  |

Notes: 1) For V<sub>IL</sub> and V<sub>IH</sub>, refer to recommended operating conditions in Table 18–11.

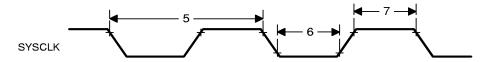

- 2) This pulse may be either a high pulse, as illustrated in Figure 18–10, which extends from the earliest valid high to the final valid high in an XTAL2/CLKIN cycle or a low pulse, which extends from the earliest valid low to the final valid low in an XTAL2/CLKIN cycle.

- 3) SYSCLK = CLKIN/1

Figure 18-10. External Clock Timing for Divide-by-1 Clock

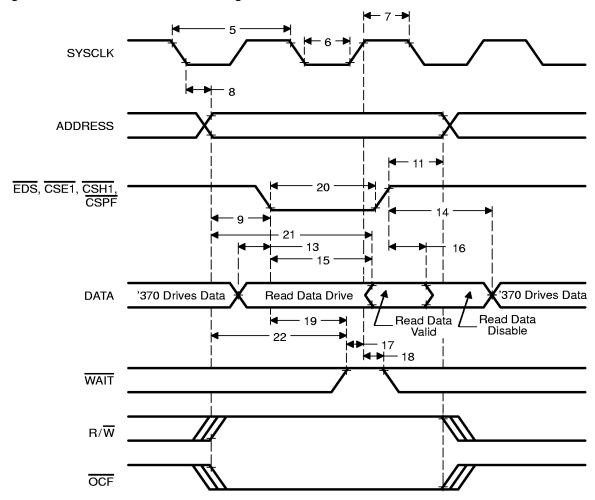

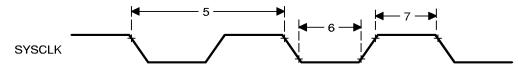

Table 18–15. Switching Characteristics and Timing Requirements (see Note)

| No. | Parameter                                |                             |                   | Min                    | Max                    | Unit |

|-----|------------------------------------------|-----------------------------|-------------------|------------------------|------------------------|------|

| 5   | t <sub>c</sub> Cycle time, SYSCLK Divide |                             | Divide-by-4 clock | 200                    | 2000                   | ns   |

|     |                                          |                             | Divide-by-1 clock | 200                    | 500                    | ns   |

| 6   | tw(SCL)                                  | Pulse duration, SYSCLK low  |                   | 0.5t <sub>c</sub> – 20 | 0.5t <sub>c</sub>      | ns   |

| 7   | tw(SCH)                                  | Pulse duration, SYSCLK high |                   | 0.5t <sub>c</sub>      | 0.5t <sub>c</sub> + 20 | ns   |

**Note:**  $t_c$  = system clock cycle time = 1/SYSCLK

Figure 18-11. SYSCLK Timing

Electrical Specifications and Timings

#### 18.9 TMS370Cx2xA and TMS370Cx2x Specifications

The tables in this section give specifications that apply to the devices in the TMS370Cx2xA TMS370Cx2x categories. These devices include the TMS370C022A, TMS370C320A, TMS370C020A. TMS370C322A, TMS370C722, and SE370C722.

#### 18.9.1 TMS370Cx2xA and TMS370Cx2x Electrical Specifications

Stresses beyond those listed in Table 18–1 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the recommended operating conditions in Table 18–16 is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Table 18–16. Recommended Operating Conditions (See Note 1)

| Paran           | neter                        |                                                | Min                | Nom  | Max             | Unit |

|-----------------|------------------------------|------------------------------------------------|--------------------|------|-----------------|------|

| V <sub>CC</sub> | Supply voltage               | Supply voltage                                 |                    |      | 5.5             | ٧    |

|                 | RAM data-retention supply vo | RAM data-retention supply voltage (see Note 2) |                    |      |                 | ٧    |

| VIL             | Low-level input voltage      | All pins except MC                             | V <sub>SS</sub>    |      | 0.8             | ٧    |

|                 |                              | MC, normal operation                           | V <sub>SS</sub>    |      | 0.3             | ٧    |

| V <sub>IH</sub> | High-level input voltage     | All pins except MC, XTAL2/CLKIN, and RESET     | 2                  |      | V <sub>CC</sub> | V    |

|                 |                              | XTAL2/CLKIN                                    | 0.8V <sub>CC</sub> |      | Vcc             | ٧    |

|                 |                              | RESET                                          | 0.7V <sub>CC</sub> |      | vcc             | V    |

| V <sub>MC</sub> | MC (mode control) voltage    | EEPROM write-protect override (WPO) mode       | 11.7               | 12   | 13              | ٧    |

|                 |                              | EPROM programming voltage (V <sub>PP</sub> )   | 13                 | 13.2 | 13.5            | V    |

|                 |                              | Microcomputer mode                             | V <sub>SS</sub>    |      | 0.3             | ٧    |

| T <sub>A</sub>  | Operating free-air tempera-  | L version                                      | 0                  |      | 70              | °C   |

|                 | ture                         | A version                                      | -40                |      | 85              | °C   |

|                 |                              | T version                                      | -40                |      | 105             | °C   |

- Notes: 1) Unless otherwise noted, all voltages are with respect to VSS (ground).

- 2) RESET must be externally activated when V<sub>CC</sub> or SYSCLK is out of the recommended operating range.

Table 18-17. Electrical Characteristics Over Recommended Operating Free-Air Temperature Range

| Paramo          | eter                                                           |                                                              | Test Conditions                              | Min                | Тур | Max | Unit |

|-----------------|----------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------|--------------------|-----|-----|------|

| V <sub>OL</sub> | Low-level output vo                                            | oltage                                                       | I <sub>OL</sub> = 1.4 mA                     |                    |     | 0.4 | ٧    |

| V <sub>OH</sub> | High-level output v                                            | oltage                                                       | I <sub>OH</sub> = -50 μA                     | 0.9V <sub>CC</sub> |     |     | ٧    |

|                 |                                                                |                                                              | $I_{OH} = -2 \text{ mA}$                     | 2.4                |     |     | ٧    |

| I <sub>I</sub>  | Input current                                                  | МС                                                           | 0 V < V <sub>I</sub> ≤ 0.3 V                 |                    |     | 10  | μА   |

|                 |                                                                |                                                              | 0.3 V < V <sub>I</sub> ≤ 13 V                |                    |     | 650 | μА   |

|                 |                                                                |                                                              | 12 V ≤ V <sub>I</sub> ≤ 13 V<br>(see Note 1) |                    |     | 50  | mA   |

|                 |                                                                | I/O pins                                                     | $0 \ V \le V_I \le V_{CC}$                   |                    |     | ±10 | μА   |

| l <sub>OL</sub> | Low-level output current                                       |                                                              | V <sub>OL</sub> = 0.4 V                      | 1.4                |     |     | mA   |

| I <sub>OH</sub> | High-level output current                                      |                                                              | $V_{OH} = 0.9V_{CC}$                         | -50                |     |     | μА   |

|                 |                                                                |                                                              | V <sub>OH</sub> = 2.4 V                      | -2                 |     |     | mA   |

| Icc             | Supply current (operating mode) OSC POWER bit = 0 (see Note 4) |                                                              | See Notes 2 and 3<br>SYSCLK = 5 MHz          |                    | 30  | 45  | mA   |

|                 |                                                                |                                                              | See Notes 2 and 3<br>SYSCLK = 3 MHz          |                    | 20  | 30  | mA   |

|                 |                                                                |                                                              | See Notes 2 and 3<br>SYSCLK = 0.5 MHz        |                    | 7   | 11  | mA   |

| lcc             | Supply current (ST OSC POWER bit =                             |                                                              | See Notes 2 and 3<br>SYSCLK = 5 MHz          |                    | 10  | 17  | mA   |

|                 |                                                                |                                                              | See Notes 2 and 3<br>SYSCLK = 3 MHz          |                    | 8   | 11  | mA   |

|                 |                                                                |                                                              | See Notes 2 and 3<br>SYSCLK = 0.5 MHz        |                    | 2   | 3.5 | mA   |

| Icc             | '''                                                            | Supply current (STANDBY mode) OSC POWER bit = 1 (see Note 6) |                                              |                    | 6   | 8.6 | mA   |

|                 |                                                                |                                                              | See Notes 2 and 3<br>SYSCLK = 0.5 MHz        |                    | 2   | 3.0 | mA   |

| lcc             | Supply current (HA                                             | LT mode)                                                     | See Note 2<br>XTAL2/CLKIN < 0.2 V            |                    | 2   | 30  | μА   |

- Notes: 1) Input current Ipp is a maximum of 50 mA only when EPROM is being programmed.

- 2) Single-chip mode, ports configured as inputs or as outputs with no load. All inputs  $\leq$  0.2 V or  $\geq$  V<sub>CC</sub> 0.2 V.

- 3) XTAL2/CLKIN is driven with an external square wave signal with 50% duty cycle and rise and fall times less than 10 ns. Current can be higher with a crystal oscillator. At 5-MHz SYSCLK, this extra current = 0.01 mA × (total load capacitance + crystal capacitance in pF).

- 4) Maximum operating current = 7.6(SYSCLK) + 7 mA.

- 5) Maximum standby current = 3(SYSCLK) + 2 mA (OSC POWER bit = 0).

- 6) Maximum standby current = 2.24(SYSCLK) + 1.9 mA (OSC POWER bit = 1; valid only up to 3-MHz SYSCLK).

Electrical Specifications and Timings

#### 18.9.2 TMS370Cx2xA and TMS370Cx2x Timings

Refer to Sections 18.1 and 18.2 (both on page 18-2) for timing symbol definitions and parameter measurement points.

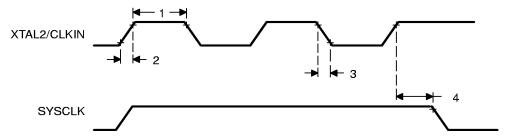

Table 18–18. External Clocking Requirements for Divide-by-4 Clock (See Note 1)

| No. | Parameter               |                                                        | Min | Max | Unit |

|-----|-------------------------|--------------------------------------------------------|-----|-----|------|

| 1   | t <sub>w(CI)</sub>      | Pulse duration, XTAL2/CLKIN (see Note 2)               | 20  |     | ns   |

| 2   | t <sub>r(CI)</sub>      | Rise time, XTAL2/CLKIN                                 |     | 30  | ns   |

| 3   | t <sub>f(CI)</sub>      | Fall time, XTAL2/CLKIN                                 |     | 30  | ns   |

| 4   | <sup>t</sup> d(CIH-SCL) | Delay time, XTAL2/CLKIN rise to SYSCLK fall            |     | 100 | ns   |

|     | CLKIN                   | Crystal operating frequency                            | 2   | 20  | MHz  |

|     | SYSCLK                  | Internal system clock operating frequency (see Note 3) | 0.5 | 5   | MHz  |

- Notes: 1) For V<sub>IL</sub> and V<sub>IH</sub>, refer to recommended operating conditions in Table 18–16.

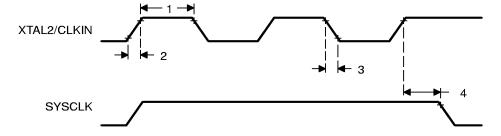

- 2) This pulse may be either a high pulse, as illustrated in Figure 18-12, which extends from the earliest valid high to the final valid high in an XTAL2/CLKIN cycle, or a low pulse, which extends from the earliest valid low to the final valid low in an XTAL2/CLKIN cycle.

- 3) SYSCLK = CLKIN/4

Figure 18–12. External Clock Timing for Divide-by-4 Clock

Table 18–19. External Clocking Requirements for Divide-by-1 Clock (PLL) (See Note 1)

| No. | Parameter               | Parameter                                                     |  |     | Unit |

|-----|-------------------------|---------------------------------------------------------------|--|-----|------|

| 1   | t <sub>w(CI)</sub>      | Pulse duration, XTAL2/CLKIN (see Note 2)                      |  |     | ns   |

| 2   | t <sub>r(CI)</sub>      | Rise time, XTAL2/CLKIN                                        |  | 30  | ns   |

| 3   | t <sub>f(CI)</sub>      | Fall time, XTAL2/CLKIN                                        |  | 30  | ns   |

| 4   | <sup>t</sup> d(CIH-SCH) | Delay time, XTAL2/CLKIN rise to SYSCLK rise                   |  | 100 | ns   |

|     | CLKIN                   | CLKIN Crystal operating frequency                             |  | 5   | MHz  |

|     | SYSCLK                  | SYSCLK Internal system clock operating frequency (see Note 3) |  | 5   | MHz  |

Notes: 1) For  $V_{IL}$  and  $V_{IH}$ , refer to recommended operating conditions in Table 18–16.

- 2) This pulse can be either a high pulse, as illustrated in Figure 18–13, which extends from the earliest valid high to the final valid high in an XTAL2/CLKIN cycle, or a low pulse, which extends from the earliest valid low to the final valid low in an XTAL2/CLKIN cycle.

- 3) SYSCLK = CLKIN/1

Figure 18-13. External Clock Timing for Divide-by-1 Clock

Table 18-20. Switching Characteristics and Timing Requirements (See Note)

| No. | Parameter           |                                        |                   | Min                    | Max                    | Unit |

|-----|---------------------|----------------------------------------|-------------------|------------------------|------------------------|------|

| 5   | t <sub>c</sub>      | Cycle time, SYSCLK Divide-by-4 clock 2 |                   | 200                    | 2000                   | ns   |

|     |                     |                                        | Divide-by-1 clock | 200                    | 500                    |      |

| 6   | tw(SCL)             | Pulse duration, SYSCLK low             |                   | 0.5t <sub>c</sub> – 20 | 0.5t <sub>c</sub>      | ns   |

| 7   | t <sub>w(SCH)</sub> | Pulse duration, SYSCLK high            |                   | 0.5t <sub>c</sub>      | 0.5t <sub>c</sub> + 20 | ns   |

**Note:**  $t_c$  = system-clock cycle time = 1/SYSCLK

Figure 18-14. SYSCLK Timing

Electrical Specifications and Timings

#### 18.10 TMS370Cx32A Specifications

The tables in this section give specifications that apply to the devices in the TMS370Cx32A category. These devices include the TMS370C032A, TMS370C332A, TMS370C732A, and SE370C732A.

### 18.10.1 TMS370Cx32A Electrical Specifications

Stresses beyond those listed in Table 18–1 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the recommended operating conditions in Table 18–21 is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Table 18–21. Recommended Operating Conditions (See Note 1)

| Param            | neter                       |                                                | Min                 | Nom  | Max              | Unit |

|------------------|-----------------------------|------------------------------------------------|---------------------|------|------------------|------|

| V <sub>CC1</sub> | Supply voltage              | 4.5                                            | 5                   | 5.5  | ٧                |      |

|                  | RAM data-retention supply v | RAM data-retention supply voltage (see Note 2) |                     |      | 5.5              | ٧    |

| V <sub>CC3</sub> | Analog supply voltage       |                                                | 4.5                 | 5    | 5.5              | ٧    |

| V <sub>SS3</sub> | Analog supply ground        | -0.3                                           | 0                   | 0.3  | ٧                |      |

| V <sub>IL</sub>  | Low-level input voltage     | All pins except MC                             | V <sub>SS1</sub>    |      | 0.8              | ٧    |

|                  |                             | MC, normal operation                           | V <sub>SS1</sub>    |      | 0.3              | ٧    |

| V <sub>IH</sub>  | High-level input voltage    | All pins except MC, XTAL2/CLKIN, and RESET     | 2                   |      | V <sub>CC1</sub> | ٧    |

|                  |                             | XTAL2/CLKIN                                    | 0.8V <sub>CC1</sub> |      | V <sub>CC1</sub> | ٧    |

|                  |                             | RESET                                          | 0.7V <sub>CC1</sub> |      | V <sub>CC1</sub> | ٧    |

| V <sub>MC</sub>  | MC (mode control) voltage   | EEPROM write-protect override (WPO) mode       | 11.7                | 12   | 13               | ٧    |

|                  |                             | EPROM programming voltage (V <sub>PP</sub> )   | 13                  | 13.2 | 13.5             | ٧    |

|                  |                             | Microcomputer mode                             | V <sub>SS1</sub>    |      | 0.3              | ٧    |

| T <sub>A</sub>   | Operating free-air tempera- | L version                                      | 0                   |      | 70               | °C   |

|                  | ture                        | A version                                      | -40                 |      | 85               | °C   |

|                  |                             | T version                                      | -40                 |      | 105              | °С   |

- Notes: 1) Unless otherwise noted, all voltage values are with respect to V<sub>SS1</sub>.

- 2) RESET must be externally activated when V<sub>CC1</sub> or SYSCLK is not within the recommended operating range.

Table 18-22. Electrical Characteristics Over Recommended Operating Free-Air Temperature Range

| Parameter        |                                                   | Test Conditions                                 | Min                                                                  | Тур                | Max | Unit |    |

|------------------|---------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------|--------------------|-----|------|----|

| V <sub>OL</sub>  | Low-level output vo                               | tage                                            | I <sub>OL</sub> = 1.4 mA                                             |                    |     | 0.4  | V  |

| V <sub>OH</sub>  | High-level output voltage                         |                                                 | I <sub>OH</sub> = -50 μA                                             | 0.9V <sub>CC</sub> |     |      | V  |

|                  |                                                   |                                                 | $I_{OH} = -2 \text{ mA}$                                             | 2.4                |     |      | V  |

| l <sub>l</sub>   | Input current                                     | МС                                              | $0 \text{ V} \le \text{V}_{\text{I}} \le 0.3 \text{ V}$              |                    |     | 10   | μА |

|                  |                                                   |                                                 | $0.3 \text{ V} < \text{V}_{\text{I}} \le 13 \text{ V}$               |                    |     | 650  | μΑ |

|                  |                                                   |                                                 | $12 \text{ V} \le \text{V}_{\text{I}} \le 13 \text{ V}$ (see Note 1) |                    |     | 50   | mA |

|                  |                                                   | I/O pins                                        | $0\ V \le V_I \le V_{CC1}$                                           |                    |     | ± 10 | μА |

| loL              | Low-level output cu                               | rrent                                           | V <sub>OL</sub> = 0.4 V                                              | 1.4                |     |      | mA |

| I <sub>OH</sub>  | High-level output cu                              | rrent                                           | V <sub>OH</sub> = 0.9V <sub>CC1</sub>                                | -50                |     |      | μА |

|                  |                                                   |                                                 | V <sub>OH</sub> = 2.4 V                                              | -2                 |     |      | mA |

| I <sub>CC1</sub> | Supply current (operating mode) OSC POWER bit = 0 |                                                 | See Notes 2 and 3<br>SYSCLK = 5 MHz                                  |                    | 35  | 45   | mA |

|                  |                                                   |                                                 | See Notes 2 and 3<br>SYSCLK = 3 MHz                                  |                    | 25  | 35   | mA |

|                  |                                                   |                                                 | See Notes 2 and 3<br>SYSCLK = 0.5 MHz                                |                    | 10  | 14   | mA |

| I <sub>CC1</sub> | Supply current (STA                               |                                                 | See Notes 2 and 3<br>SYSCLK = 5 MHz                                  |                    | 12  | 17   | mA |

|                  |                                                   |                                                 | See Notes 2 and 3<br>SYSCLK = 3 MHz                                  |                    | 8   | 13   | mA |

|                  |                                                   |                                                 | See Notes 2 and 3<br>SYSCLK = 0.5 MHz                                |                    | 3   | 4    | mA |

| I <sub>CC1</sub> |                                                   | Supply current (STANDBY mode) OSC POWER bit = 1 |                                                                      |                    | 6   | 8.6  | mA |

|                  |                                                   |                                                 | See Notes 2 and 3<br>SYSCLK = 0.5 MHz                                |                    | 2   | 3.0  | mA |

| I <sub>CC1</sub> | Supply current (HALT mode)                        |                                                 | See Note 2<br>XTAL2/CLKIN < 0.2 V                                    |                    | 15  | 40   | μА |

- Notes: 1) Input current Ipp is a maximum of 50 mA only when EPROM is being programmed.

- 2) Single-chip mode, ports configured as inputs or as outputs with no load. All inputs  $\leq$  0.2 V or  $\geq$  V CC1 0.2 V.

- 3) XTAL2/CLKIN is driven with an external square wave signal with 50% duty cycle and rise and fall times less than 10 ns. Current can be higher with a crystal oscillator. At 5-MHz SYSCLK, this extra current = 0.01 mA × (total load capacitance + crystal capacitance in pF).

Electrical Specifications and Timings

#### 18.10.2 TMS370Cx32A Timings

Refer to Sections 18.1 and 18.2 (both on page 18-2) for timing symbol definitions and parameter measurement points.

Table 18–23. External Clocking Requirements For Divide-by-4 Clock (See Note 1)

| No. | Parameter               | arameter                                                      |    |     | Unit |

|-----|-------------------------|---------------------------------------------------------------|----|-----|------|

| 1   | t <sub>w(CI)</sub>      | Pulse duration, XTAL2/CLKIN (see Note 2)                      | 20 |     | ns   |

| 2   | t <sub>r(CI)</sub>      | Rise time, XTAL2/CLKIN                                        |    | 30  | ns   |

| 3   | t <sub>f(CI)</sub>      | Fall time, XTAL2/CLKIN                                        |    | 30  | ns   |

| 4   | <sup>t</sup> d(CIH-SCL) | Delay time, XTAL2/CLKIN rise to SYSCLK fall                   |    | 100 | ns   |

|     | CLKIN                   | CLKIN Crystal operating frequency                             |    | 20  | MHz  |

|     | SYSCLK                  | SYSCLK Internal system clock operating frequency (see Note 3) |    | 5   | MHz  |

- **Notes:** 1) For V<sub>IL</sub> and V<sub>IH</sub>, refer to recommended operating conditions in Table 18–21.

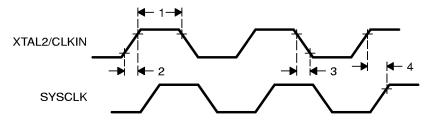

- 2) This pulse may be either a high pulse, as illustrated in Figure 18-15, which extends from the earliest valid high to the final valid high in an XTAL2/CLKIN cycle or a low pulse, which extends from the earliest valid low to the final valid low in an XTAL2/CLKIN cycle.

- 3) SYSCLK = CLKIN/4

Figure 18–15. External Clock Timing for Divide-by-4 Clock

Table 18–24. External Clocking Requirements for Divide-by-1 Clock (PLL) (See Note 1)

| No. | Parameter               |                                                        | Min | Max | Unit |

|-----|-------------------------|--------------------------------------------------------|-----|-----|------|

| 1   | t <sub>w(CI)</sub>      | Pulse duration, XTAL2/CLKIN (see Note 2)               | 20  |     | ns   |

| 2   | t <sub>r(CI)</sub>      | Rise time, XTAL2/CLKIN                                 |     | 30  | ns   |

| 3   | t <sub>f(CI)</sub>      | all time, XTAL2/CLKIN                                  |     | 30  | ns   |

| 4   | <sup>t</sup> d(CIH-SCH) | Delay time, XTAL2/CLKIN rise to SYSCLK rise            |     | 100 | ns   |

|     | CLKIN                   | CLKIN Crystal operating frequency                      |     | 5   | MHz  |

|     | SYSCLK                  | Internal system clock operating frequency (see Note 3) | 2   | 5   | MHz  |

$\textbf{Notes:} \quad \text{1) For V}_{IL} \text{ and V}_{IH}, \text{ refer to recommended operating conditions in Table 18-21}.$

- 2) This pulse can be either a high pulse, as illustrated in Figure 18–16, which extends from the earliest valid high to the final valid high in an XTAL2/CLKIN cycle or a low pulse, which extends from the earliest valid low to the final valid low in an XTAL2/CLKIN cycle.

- 3) SYSCLK = CLKIN/1

Figure 18-16. External Clock Timing for Divide-by-1 Clock

Table 18-25. Switching Characteristics and Timing Requirements (See Note)