# MOS INTEGRATED CIRCUIT $\mu$ PD75P218

# **4-BIT SINGLE-CHIP MICROCOMPUTER**

The  $\mu$ PD75P218 is a one-time PROM version that can be written to only once or an EPROM version that allows program writing, erasing, and rewriting, of the  $\mu$ PD75218 <sup>Note</sup>.

Since the program can be written by the user, the  $\mu$ PD75P218 is suitable for preproduction use during system development, or limited production.

Read this material together with the  $\mu$ PD75218 materials.

Note Under development

# **FEATURES**

- μPD75218 compatible

- On-chip 16K-byte mode/32K-byte mode switching function

- Operates at the same power supply voltage range (2.7 to 6.0 V) as the mask ROM version  $\mu$ PD75218.

- 32640  $\times$  8 bits of PROM

- 1024 × 4 bits of RAM

- No pull-down resistor for Port 6

- High breakdown voltage display output

- S0 to S8, T0 to T9: On-chip pull-down resistor

- S9, T10 to T15 : Open drain

- No power-on reset circuit

# Caution No mask-option pull-down resistor is provided.

# ORDERING INFORMATION

| Part Number          | Part Number Package                               |          |

|----------------------|---------------------------------------------------|----------|

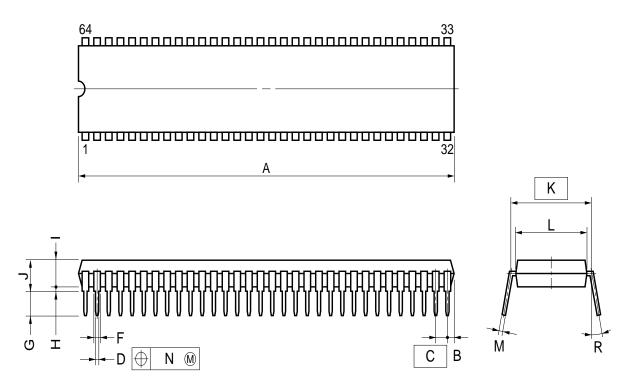

| μPD75P218CW          | 64-pin plastic shrink DIP (750 mil)               | Standard |

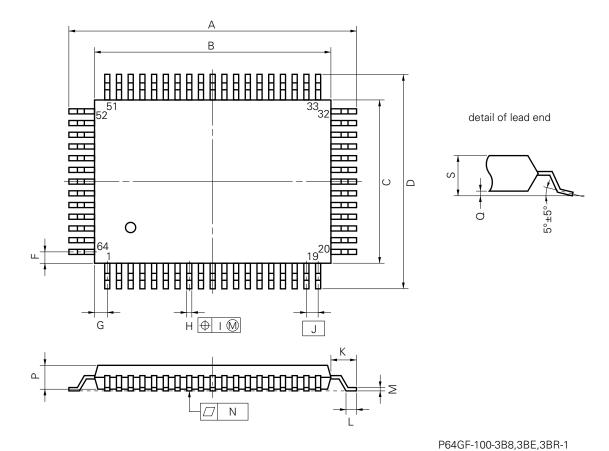

| $\mu$ PD75P218GF-3BR | 64-pin plastic QFP (14 $	imes$ 20 mm)             | Standard |

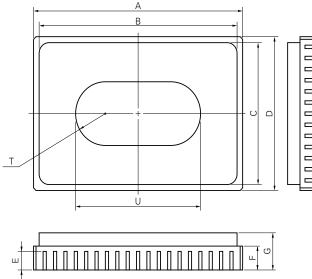

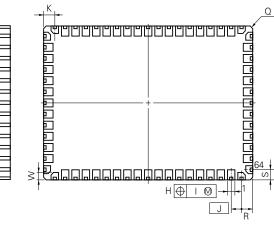

| $\mu$ PD75P218KB     | 64-pin ceramic LCC with window (14 $	imes$ 20 mm) | Standard |

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

# The word "PROM" in this document refers to the common parts of the one-time PROM products and EPROM products.

The information in this document is subject to change without notice.

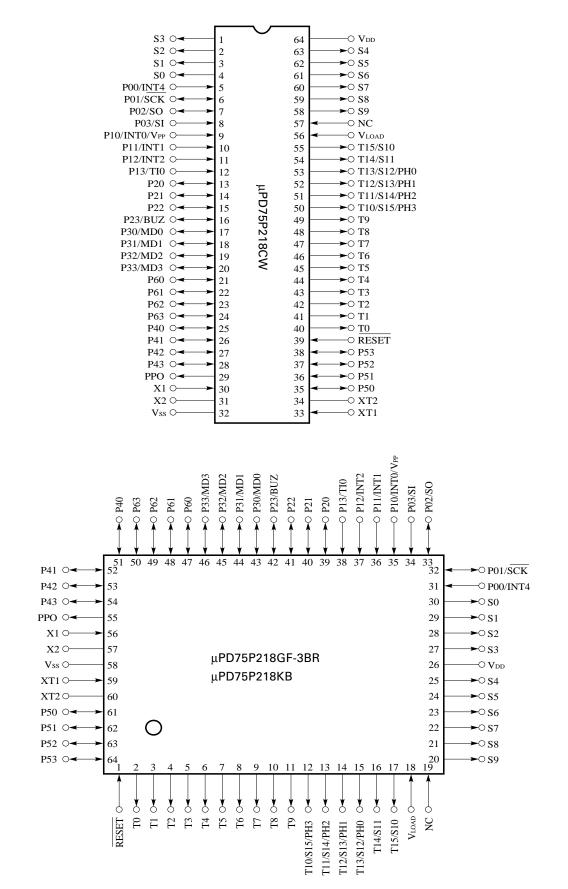

# PIN CONFIGURATION (Top View)

P00 - P03 PORT 0 4 BASIC INTERVAL  $\sqrt{}$ TIMER P10 - P13 PORT 1 4 CY SP (8) PROGRAM ♥ INTBT ALU COUNTER (15) SBS (2) TI0/P13 → TIMER/EVENT P20 - P23 PORT 2 4 COUNTER  $\sqrt{}$ #0 BANK P30/MD0 -PORT 3 4 P33/MD3 ♥ INTT0 P40 - P43 PORT 4 4 TIMER/PULSE GENERATOR GENERAL REG.  $\sqrt{}$ PRO 🗲 P50 - P53 PORT 5 4 PROM INTTPG PROGRAM PORT 6 P60 - P63 4 SI/P03 → MEMORY Υ DECODE SERIAL 32640 x 8 BITS RAM SO/P02 ←> AND INTERFACE V-1/ DATA MEMORY CONTROL SCK/P01 ↔ 1024 x 4 BITS 10 T0 - T9 INTSIO T10/S15/PH3 -4 T13/S12/PH0 FIP INT0/P10/VPP -CONTROL-INT1/P11 -T14/S11,T15/S10 2 LER/ INTERRUPT DRIVER INT2/P12 -CONTROL √¬∕ S0 - S9 10  $fx/2^{N}$ ┢ INT4/P00 → INTW SYSTEM CLOCK VLOAD → CPU CLOCK CLOCK GENERATOR WATCH STAND BY F DIVIDER CONTROL TIMER ۲ SUB MAIN INTKS PH0 - PH3 PORTH 4 BUZ/P23 XT1 XT2 X1 X2 NC VDD VSS RESET

# 1. PIN FUNCTIONS

# 1.1 PORT PINS

| Pin name  | Input/<br>output | Shared<br>pin | Fun                                                                                                 | Function                                                                              |   | When reset |

|-----------|------------------|---------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---|------------|

| P00       | Input            | INT4          | 4-bit input port (PORT0).                                                                           |                                                                                       | × | Input      |

| P01       | I/O              | SCK           |                                                                                                     |                                                                                       |   |            |

| P02       | I/O              | SO            |                                                                                                     |                                                                                       |   |            |

| P03       | Input            | SI            |                                                                                                     |                                                                                       |   |            |

| P10       | Input            | INT0/Vpp      | 4-bit input port (PORT1).                                                                           | With noise elimination                                                                |   | Input      |

| P11       | 1                | INT1          |                                                                                                     | function                                                                              |   |            |

| P12       |                  | INT2          |                                                                                                     |                                                                                       | - |            |

| P13       |                  | TIO           |                                                                                                     |                                                                                       |   |            |

| P20       | I/O              | -             | 4-bit I/O port (PORT2).                                                                             |                                                                                       | × | Input      |

| P21       |                  | -             |                                                                                                     |                                                                                       |   |            |

| P22       | 1                | -             |                                                                                                     |                                                                                       |   |            |

| P23       | 1                | BUZ           |                                                                                                     |                                                                                       |   |            |

| P30 - P33 | I/O              | MD0 - MD3     | Programmable 4-bit I/O port (PORT3).<br>I/O can be specified bit by bit.                            |                                                                                       |   | Input      |

| P40 - P43 | I/O              | _             | 4-bit I/O port (PORT4).<br>Can directly drive LEDs.                                                 | Data input/output pins<br>for the PROM write and<br>verify (Four low-order<br>bits).  | 0 | Input      |

| P50 - P53 | I/O              | _             | 4-bit I/O port (PORT5).<br>Can directly drive LEDs.                                                 | Data input/output pins<br>for the PROM write and<br>verify (Four high-order<br>bits). |   | Input      |

| P60 - P63 | I/O              | -             | Programmable 4-bit I/O port (PORT6).<br>I/O can be specified bit by bit.<br>Suitable for key input. |                                                                                       | × | Input      |

| PH0       | Output           | T13/S12       | 4-bit P-ch open drain high                                                                          |                                                                                       | × | High       |

| PH1       | ]                | T12/S13       | current output port (PORT                                                                           | H).                                                                                   |   | impedance  |

| PH2       | 1                | T11/S14       | Can directly drive LEDs.                                                                            |                                                                                       |   |            |

| PH3       | ]                | T10/S15       |                                                                                                     |                                                                                       |   |            |

# 1.2 NON-PORT PINS

| Pin name             | Input/<br>output | Shared<br>pin |                                       | Function                                                                                                                                                                         | When reset        |  |

|----------------------|------------------|---------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

| T0 - T9              |                  | -             | Note 1                                | Note 1         High breakdown voltage large current output pin           for digit output                                                                                        |                   |  |

| T10/S15 -<br>T13/S12 | Output           | PH3 - PH0     | Note 2                                | Note 2High breakdown voltage large current output pin<br>for digit/segment outputThe remainder of the pins can be used as PORTH.                                                 |                   |  |

| T14/S11,<br>T15/S10  |                  | _             |                                       | High breakdown voltage large current output pin<br>for digit/segment output<br>Static output is also available.                                                                  |                   |  |

| S9                   |                  |               |                                       | High breakdown voltage output pin for segment<br>output<br>Static output is also available.                                                                                      |                   |  |

| S0 - S8              |                  |               | Note 1                                | High breakdown voltage output pin for segment output                                                                                                                             | Low level         |  |

| PPO                  | Output           | -             | Output fo                             | r receiving pulse signal for timer/pulse generator                                                                                                                               | High<br>impedance |  |

| TIO                  | Input            | P13           |                                       | nput for receiving external event pulse signal for timer/<br>event counter                                                                                                       |                   |  |

| SCK                  | I/O              | P01           | Serial clo                            | Serial clock I/O                                                                                                                                                                 |                   |  |

| SO                   | I/O              | P02           | Serial data output or serial data I/O |                                                                                                                                                                                  | Input             |  |

| SI                   | Input            | P03           | Serial dat                            | Serial data input or normal input                                                                                                                                                |                   |  |

| INT4                 | Input            | P00           | -                                     | Edge detection vectored interrupt input<br>(either rising edge or falling edge detection)                                                                                        |                   |  |

| INT0                 | Input            | P10/VPP       | Edge dete                             | Edge detection vectored interrupt input with noise elimination                                                                                                                   |                   |  |

| INT1                 |                  | P11           | (detection                            | (detection edge selectable)                                                                                                                                                      |                   |  |

| INT2                 | Input            | P12           | Edge dete                             | Edge detection testable input (rising edge detection)                                                                                                                            |                   |  |

| BUZ                  | I/O              | P23           | Fixed freq                            | Fixed frequency output pin (for buzzer or system clock trimming)                                                                                                                 |                   |  |

| X1, X2               |                  | _             | generation<br>When ext                | Crystal/ceramic resonator connection for main system clock<br>generation.<br>When external clock is used, it is applied to X1, and its<br>reserve phase signal is applied to X2. |                   |  |

| XT1, XT2             |                  | -             |                                       | nnection for subsystem clock generation.<br>rnal clock is used, it is applied to XT1, and XT2 is open.                                                                           |                   |  |

| RESET                | Input            | _             | System re                             | eset input (low level active)                                                                                                                                                    |                   |  |

| MD0 - MD3            | I/O              | P30 - P33     | Operation                             | mode selection pins during the PROM write/verify cycles                                                                                                                          |                   |  |

| Vpp                  |                  | P10/INT0      |                                       | +12.5 V is applied as the programming voltage during the PROM write/verify cycles                                                                                                |                   |  |

| VLOAD                |                  | -             | Pull-down                             | resistor connection pin of FIP <sup>®</sup> controller/driver                                                                                                                    |                   |  |

| Vdd                  |                  | -             |                                       | ower supply. +6 V is applied as the programming uring the PROM write/verify cycles                                                                                               |                   |  |

| Vss                  |                  | -             | GND pote                              | ntial                                                                                                                                                                            |                   |  |

| NC Note 3            |                  | _             | No conne                              | ction                                                                                                                                                                            |                   |  |

Note 1. On-chip pull-down resistor

- 2. Open drain output

- 3. When using a printed board with a  $\mu$ PD75216A, 75217, or 75218, connect the NC pin to the VPRE.

# **1.3 PIN INPUT/OUTPUT CIRCUITS**

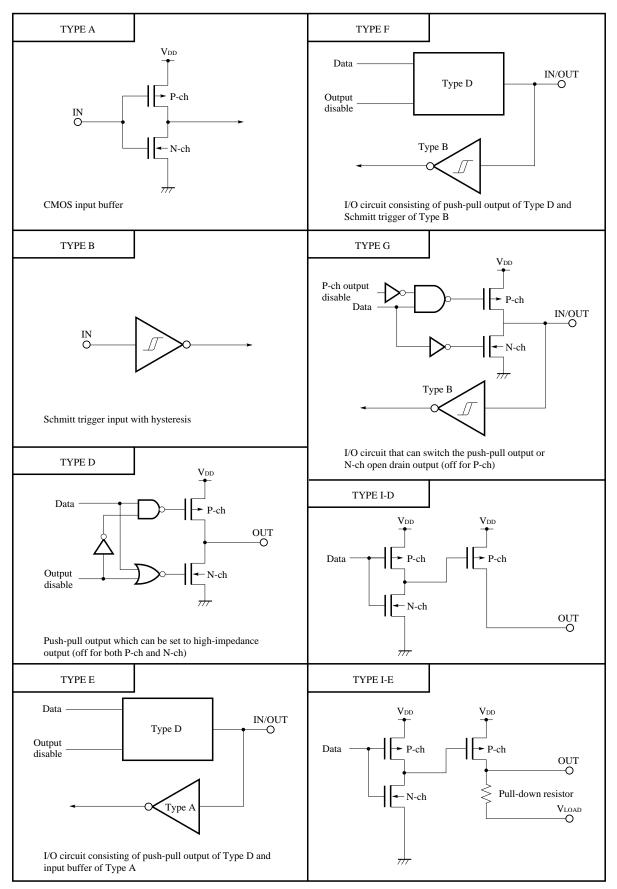

The input/output circuit diagram for each  $\mu$ PD75P218 pin is shown in Fig. 1-1 in a simplified manner. For the correspondence of the each pin and input/output type number, refer to Table 1-1.

| Pin name           | I/O type | Pin name                  | I/O type |

|--------------------|----------|---------------------------|----------|

| P00/INT4           | B        | P50 - P53                 | E        |

| P01/SCK            | Ð        | P60 - P63                 | E        |

| P02/SO             | G        | Т0 - Т9                   | I-E      |

| P03 - SI           | B        | T10/S15/PH3 - T13/S12/PH0 | I-D      |

| P10/INT0/VPP       | B        | T14/S11, T15/S10          | I-D      |

| P11/INT1, P12/INT2 |          | S0 - S8                   | I-E      |

| P13 - TI0          |          | S9                        | I-D      |

| P20 - P22          | E        | PPO                       | D        |

| P23/BUZ            |          | RESET                     | B        |

| P30/MD0 - P33/MD3  | E        | VLOAD                     | I-E      |

| P40 - P43          | E        |                           |          |

# Table 1-1 Pins and Input/Output Type Numbers

Remark I/O type enclosed with a circle indicates Schmitt triggered input.

Fig. 1-1 Pin Input/Output Circuit

# 1.4 PROCESSING OF UNUSED PINS

| Pin name                            | Recommended connection             |

|-------------------------------------|------------------------------------|

| P00/INT4                            | Connect to Vss                     |

| P01/SCK                             | Connect to Vss or VDD              |

| P02/SO                              | _                                  |

| P03/SI                              |                                    |

| P10/INT0/V <sub>PP</sub>            | Connect to Vss                     |

| P11/INT1, P12/INT2                  |                                    |

| P13/T10                             |                                    |

| P20 - P22                           | Input state: Connect to Vss or VDD |

| P23/BUZ                             | Output state: Open                 |

| P30/MD0 - P33/MD3                   |                                    |

| P40 - P43                           |                                    |

| P50 - P53                           |                                    |

| P60 - P63                           |                                    |

| PPO                                 | Open                               |

| S0 - S9                             |                                    |

| T15/S10, T14/S11                    |                                    |

| Т0 - Т9                             |                                    |

| T10/S15/PH3 - T13/S12/PH0           |                                    |

| XT1                                 | Connect to Vss or VDD              |

| XT2                                 | Open                               |

| VLOAD when no on-chip load resistor | Connect to Vss or VDD              |

# Table 1-2 Recommended Connection of Unused Pins

| Item                                              | Part number      | μPD75P216A                           | μPD75217                                                  | μPD75218 <b>Note</b> | μPD75P218                                                                               |

|---------------------------------------------------|------------------|--------------------------------------|-----------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------|

| ROM                                               |                  | One-time PROM<br>16K × 8             | $\begin{array}{c} Mask \ ROM \\ 24K \times 8 \end{array}$ | Mask ROM<br>32K × 8  | PROM<br>32K × 8                                                                         |

| RAM                                               |                  | 512 × 4                              | 768 × 4                                                   | 1024                 | 4 × 4                                                                                   |

| FIP control-                                      | segments         |                                      | 9 - 16 se                                                 | egments              |                                                                                         |

| ler/driver                                        | digits           |                                      | 9 - 16                                                    | digits               |                                                                                         |

| Pull-down                                         | P60 - P63        | Not available                        | Mask-                                                     | option               | Not available                                                                           |

| resistors                                         | S0 - S8, T0 - T9 | On-chip                              | Mask-                                                     | option               | On-chip                                                                                 |

|                                                   | SD9, T10 - T15   | Not available<br>(open drain)        | Mask-option                                               |                      | Not available<br>(open drain)                                                           |

| Pin connec-<br>tion                               | P10              | INT0/V <sub>PP</sub><br>(common use) | INT0 (common use)                                         |                      | INT0/V <sub>PP</sub><br>(common use)                                                    |

|                                                   | P30 - P33        | MD0 - MD3<br>(common use)            | No common use                                             |                      | MD0 - MD3<br>(common use)                                                               |

|                                                   | VPRE             | Not available (NC)                   | Available                                                 |                      | Not available (NC)                                                                      |

| Operating amb<br>ture                             | bient tempera-   | –10 to +70 °C                        | −40 to +85 °C                                             |                      | –40 to +70 °C                                                                           |

| Power supply                                      | voltage          | 5 V ± 10 %                           |                                                           | 2.7 - 6.0 V          |                                                                                         |

| Stack area                                        |                  | Bank 0                               | Bank 0 - 2                                                | Bank                 | 0 - 3                                                                                   |

| 16K-byte mode/32K-byte<br>mode switching function |                  | Not available                        |                                                           | Available            |                                                                                         |

| Package                                           |                  | 64-pin plastic<br>shrink DIP         | 64-pin plastic shrink DIP<br>64-pin plastic QFP           |                      | 64-pin plastic<br>shrink DIP<br>64-pin plastic QFP<br>64-pin ceramic<br>LCC with window |

# 2. DIFFERENCES BETWEEN THE $\mu\text{PD75P218}$ AND THE $\mu\text{PD75P216A},$ 75217, 75218

Note Under development

# 3. 16K-BYTE MODE/32K-BYTE MODE SWITCHING FUNCTION

16K-byte mode or 32K-byte mode can be selected by setting the stack bank selection register (SBS). The  $\mu$ PD75P218 can then be used to evaluate the  $\mu$ PD75216A,  $\mu$ PD75217, and  $\mu$ PD75218.

# 3.1 DIFFERENCES BETWEEN 16K-BYTE MODE AND 32K-BYTE MODE

| ltem                                                     | 16K-byte Mode          | 32K-byte Mode                                       |

|----------------------------------------------------------|------------------------|-----------------------------------------------------|

| Stack operation at subroutine call instruction execution | 2-byte stack           | 3-byte stack                                        |

| Stack area                                               | Bank 0                 | Bank 0 to bank 3                                    |

| CALL instruction                                         | 3 machine cycles       | 4 machine cycles                                    |

| TCALL instruction by GETI                                |                        |                                                     |

| CALLF instruction                                        | 2 machine cycles       | 3 machine cycles                                    |

| BRA instruction                                          | Undefined operation    | Normal operation                                    |

| CALLA instruction                                        |                        |                                                     |

| Program counter bit 14                                   | 0 fixed                | Corresponds to branch instruction, call instruction |

| Corresponding mask ROM version                           | μPD75216A (S-DIP, QFP) | μPD75217 (S-DIP, QFP)<br>μPD75218 (S-DIP, QFP)      |

## Table 3-1 16K-byte Mode and 32K-byte Mode Differences

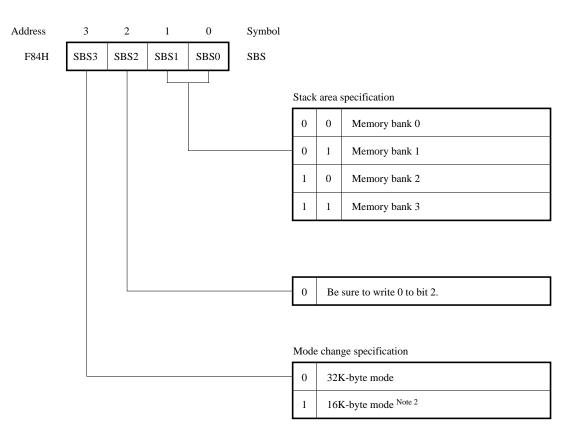

## 3.2 16K-BYTE MODE AND 32K-BYTE MODE SWITCHING

16K-byte mode and 32K-byte mode are switched by the stack bank selection register. The stack bank selection register format is shown in Fig. 3-1.

The stack bank selection register is set by 4-bit memory manipulation instruction. RESET input sets bit 3 of the stack bank selection register to "1" and changes from 32K-byte mode to 16K-byte mode. When 16K-byte mode is used, manipulating the stack bank selection register is unnecessary. When 32K-byte mode is used, the stack bank selection register must always be initialized to 00××B Note 1 at the beginning of the program.

Fig. 3-1 Stack Bank Selection Register Format

- Caution When using 32K-byte mode, execute a subroutine call instruction and an interrupt enable instruction after the stack bank selection register is set after **RESET** input.

- Notes 1. Set the desired value in  $\times\!\!\times$ .

- **2.** When the 16K-byte mode is used after RESET input, the stack bank selection register does not have to be manipulated.

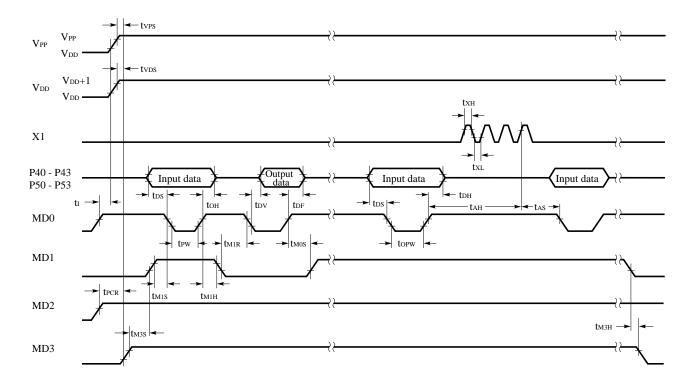

# 4. PROM (PROGRAM MEMORY) WRITE AND VERIFY

The PROM contained in the  $\mu$ PD75P218 is one-time PROM or EPROM for writing, erasing, and rewriting. Table 4-1 shows the pin functions during the write and verify cycles. Note that it is not necessary to enter an address, because the address is updated by pulsing the X1 clock pins.

| Pin Name                                                            | Function                                                                                                                                                                            |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vpp                                                                 | Normally 2.7 to 6 V; 12.5 V is applied during the write/verify cycles.                                                                                                              |

| X1, X2                                                              | After a write/verify write, the X1 and X2 clock pins are pulsed.<br>The inverted signal of the X1 should be input to the X2.<br>Note that these pins are also pulsed during a read. |

| MD0 - MD3                                                           | Operation mode selection pins during the write/verify cycles                                                                                                                        |

| P40 - P43 (Four low-order bits)<br>P50 - P53 (Four high-order bits) | 8-bit data input/output pins during the write/verify cycles                                                                                                                         |

| VDD                                                                 | Supply voltage<br>Normally 2.7 to 6 V; 6 V is applied during the write/verify cycles.                                                                                               |

#### Table 4-1 PROM Write and Verify Pin Functions

Cautions 1. The pins not used for write and verify should be processed as follows.

| Port 0 - 2, Port 6, XT1 ] |                                       |

|---------------------------|---------------------------------------|

| S0 - S9, T0 - T15         | Connect to GND (directly connectable) |

| RESET, PPO, VLOAD         |                                       |

| XT2                       | Open                                  |

- 2. An opaque film should be placed over the UV erase window of the  $\mu$ PD75P218KB except when erasing the EPROM contents.

- 3. The  $\mu$ PD75P218CW/GF does not have a UV erase window, thus the PROM contents cannot be erased with ultraviolet ray.

# 4.1 PROM WRITE AND VERIFY OPERATION

When +6 V and +12.5 V are applied to the V<sub>DD</sub> and V<sub>PP</sub> pins, respectively, the PROM is placed in the write/ verify mode. The operation is selected by the MD0 to MD3 pins, as shown in Table 4-2.

|         | Op   | eration Mod | On anotic n Martin |     |     |                                   |  |

|---------|------|-------------|--------------------|-----|-----|-----------------------------------|--|

| Vpp     | Vdd  | MD0         | MD1                | MD2 | MD3 | Operation Mode                    |  |

| +12.5 V | +6 V | Н           | L                  | Н   | L   | Clear program memory address to 0 |  |

|         |      | L           | н                  | н   | н   | Write mode                        |  |

|         |      | L           | L                  | Н   | Н   | Verify mode                       |  |

|         |      | Н           | ×                  | Н   | Н   | Program inhibit                   |  |

#### Table 4-2 PROM Write and Verify Operation Mode

$\times$ : Don't care.

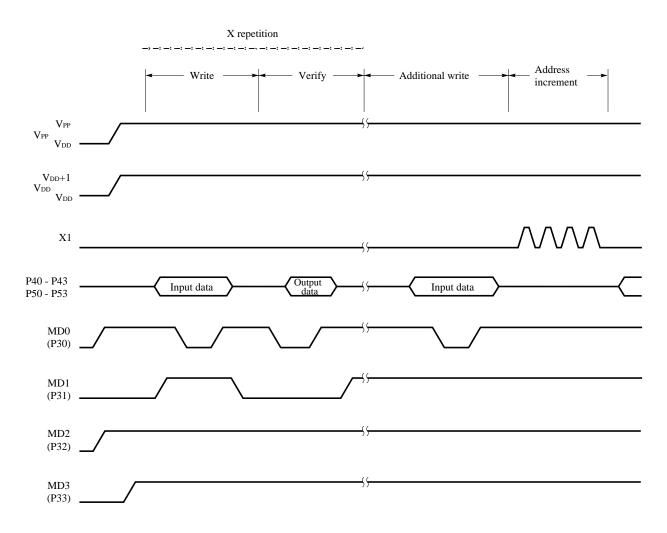

## 4.2 PROM WRITE/VERIFY PROCEDURE

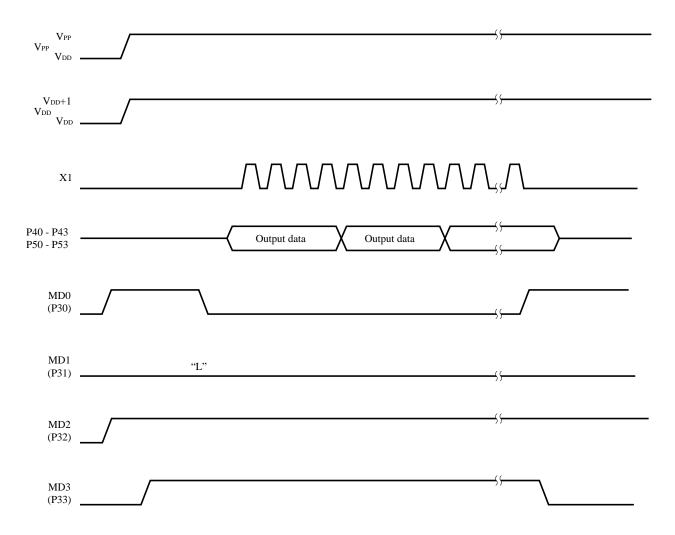

PROMs can be written at high speed using the following procedure: (see the following figure)

- (1) Connect unused pins to Vss. Set the X1 pin low.

- (2) Supply 5 volts to the VDD and VPP pins.

- (3) Wait for 10  $\mu$ s.

- (4) Select the zero clear program memory address mode.

- (5) Supply 6 volts to the  $V_{DD}$  and 12.5 volts to the  $V_{PP}$  pins.

- (6) Select the program inhibit mode.

- (7) Write data in the 1 ms write mode.

- (8) Select the program inhibit mode.

- (9) Select the verify mode. If the data is correct, proceed to step (10). If not, repeat steps (7), (8) and (9).

- (10) Perform one additional write (duration of 1 ms  $\times$  number of writes at (7) to (9)).

- (11) Select the program inhibit mode.

- (12) Apply four pulses to the X1 pin to increment the program memory address by one.

- (13) Repeat steps (7) to (12) until the end address is reached.

- (14) Select the zero clear program memory address mode.

- (15) Return the VDD and VPP pins back to + 5 volts.

- (16) Turn off the power.

# Fig. 4-1 PROM Write Timing

X: number of writes performed at (7) to (9)

# NEC

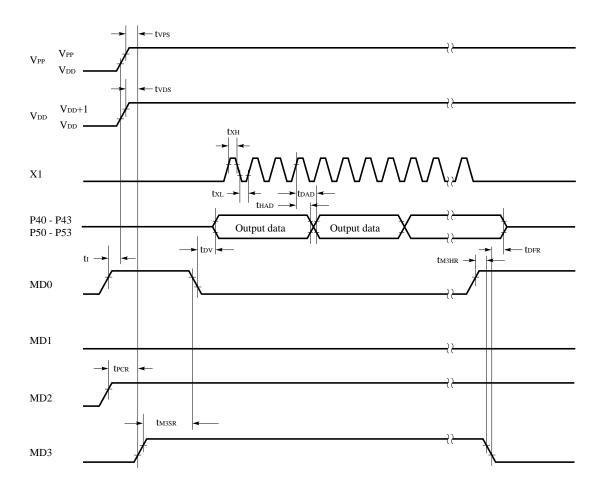

# 4.3 PROM READ PROCEDURE

The PROM contents can be read in the verify mode by using the following procedure: (see the following figure)

- (1) Connect unused pins to Vss. Set the X1 pin low.

- (2) Supply 5 volts to the VDD and VPP pins.

- (3) Wait for 10  $\mu$ s.

- (4) Select the clear program memory address mode.

- (5) Supply 6 volts to the VDD and 12.5 volts to the VPP pins.

- (6) Select the program inhibit mode.

- (7) Select the verify mode. Apply four pulses to the X1 pin. Every four clock pulses will output the data stored in one address.

- (8) Select the program inhibit mode.

- (9) Select the clear program memory address mode.

- (10) Return the VDD and VPP pins back to + 5 volts.

- (11) Turn off the power.

# 4.4 ERASING METHOD

The program data contents of the  $\mu$ PD75P218KB are erased by lighting ultraviolet ray whose wavelength is about 250 nm on the window. The minimum amount of radiation exposure required to erase the contents completely is 15 W·s/cm<sup>2</sup> (ultraviolet ray strength times erase time).

This corresponds to about 15 to 20 minutes when using a UV lamp on the market (wavelength 254 nm, strength 12 mW/cm<sup>2</sup>).

Cautions 1. The programmed data contents may also be erased if the uncovered window is exposed to direct sunlight or a fluorescent light even for several hours. Thus, to protect the data contents, cover the window with an opaque film.

NEC attaches quality-tested shading film to the UV EPROM products for shipping.

2. For normal EPROM erase, the distance between the light source and the window should be 2.5 cm or less.

**Remark** The erase time may be prolonged if the UV lamp is old or if the device window is dirty.

# 5. ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings (T<sub>a</sub> = 25 °C)

| Parameter             | Symbol | Conditions                           | Ratings               | Unit |

|-----------------------|--------|--------------------------------------|-----------------------|------|

| Power supply voltage  | VDD    |                                      | -0.3 to +7.0          | V    |

|                       | VLOAD  |                                      | Vdd - 40 to Vdd + 0.3 | V    |

|                       | VPP    |                                      | –0.3 to +13.5         | V    |

| Input voltage         | Vi     |                                      | -0.3 to VDD + 0.3     | V    |

| Output voltage        | Vo     | Other than display pins              | -0.3 to Vdd + 0.3     | V    |

|                       | Vod    | Display pins                         | Vdd - 40 to Vdd + 0.3 | V    |

| High-level output     | Іон    | Single pin; other than display pins  | -15                   | mA   |

| current               |        | Single pin; S0 - S9                  | -15                   | mA   |

|                       |        | Single pin; T0 - T15                 | -30                   | mA   |

|                       |        | Total of all pins other than display | -20                   | mA   |

|                       |        | Total of all display pins            | -120                  | mA   |

| Low-level output      | Iol    | Single pin                           | 17                    | mA   |

| current               |        | Total of all pins                    | 60                    | mA   |

| Operating temperature | Topt   |                                      | -40 to +70            | °C   |

| Storage temperature   | Tstg   |                                      | -65 to +150           | °C   |

# **Operating Power Supply Voltage** (T<sub>a</sub> = -40 to +70 $^{\circ}$ C)

| Parameter              | Conditions | MIN.   | MAX. | Unit |

|------------------------|------------|--------|------|------|

| CPU Note 1             |            | Note 2 | 6.0  | V    |

| Display controller     |            | 4.5    | 6.0  | V    |

| Timer/pulse generator  |            | 4.5    | 6.0  | V    |

| Other hardwares Note 1 |            | 2.7    | 6.0  | V    |

**Notes 1.** The CPU does not include the system clock oscillator, the display controller, or the timer/pulse generator.

2. Varies according to the cycle time. See AC Characteristics.

| Resonator            | Recommended constants | Parameter                                           | Conditions                                                                  | MIN. | TYP. | MAX. | Unit |

|----------------------|-----------------------|-----------------------------------------------------|-----------------------------------------------------------------------------|------|------|------|------|

| Ceramic<br>resonator |                       | Note 1<br>Oscillation (fxx)<br>frequency            | V <sub>DD</sub> = Oscillator<br>operating<br>voltage<br>range               | 2.0  |      | 6.2  | MHz  |

|                      | C1 = C2               | Note 2<br>Oscillation<br>stabilization time         | After VDD reaches<br>the minimum<br>oscillator operat-<br>ing voltage range |      |      | 4    | ms   |

| Crystal<br>resonator |                       | Note 1<br>Oscillation<br>frequency (fxx)            |                                                                             | 2.0  | 4.19 | 6.2  | MHz  |

|                      |                       | Note 2                                              | $V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$                                    |      |      | 10   | ms   |

|                      |                       | Oscillation<br>stabilization time                   |                                                                             |      |      | 30   | ms   |

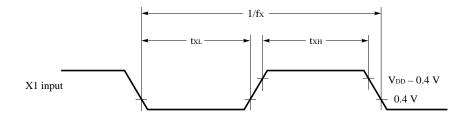

| External<br>clock    |                       | Note 1<br>X1 input fre-<br>quency (fx)              |                                                                             | 2.0  |      | 6.2  | MHz  |

|                      | mPD74HCU04            | X1 input high-<br>and low-level<br>width (txн, txL) |                                                                             | 81   |      | 250  | ns   |

Main System Clock Configurations (Ta = -40 to +70  $^{\circ}$ C, V <sub>DD</sub> = 2.7 to 6.0 V)

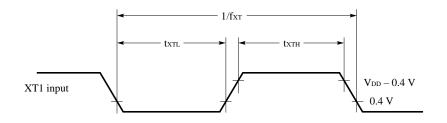

# Subsystem Clock Configurations (Ta = -40 to +70 $^\circ\text{C},$ V $_{DD}$ = 2.7 to 6.0 V)

| Resonator            | Recommended constants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Parameter                                              | Conditions                               | MIN. | TYP.   | MAX. | Unit |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------|------|--------|------|------|

| Crystal<br>resonator | XT1 XT2<br>Control Action State A |                                                        |                                          | 32   | 32.768 | 35   | kHz  |

|                      | $C3 \xrightarrow{\leq} 330 \text{ kW}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Note 2                                                 | $V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$ |      | 1.0    | 2    | s    |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Oscillation<br>stabilization time                      |                                          |      |        | 10   | S    |

| External<br>clock    | XT1 XT2<br>Open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | XT1 input<br>frequency (fxt)                           |                                          | 32   |        | 100  | kHz  |

|                      | $\bigwedge^{\wedge}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | XT1 input high-<br>and low-level<br>width (txth, txtL) |                                          | 5    |        | 15   | μs   |

- **Notes 1.** The oscillator frequency and input frequency indicate only the oscillator characteristics. Refer to the AC Characteristics for the instruction execution time.

- 2. The oscillation stabilization time is the time required for the oscillation to stabilize after VDD is applied and reaches the VDD spec or after STOP mode is released.

| Capacitance (7 | Ta = 25 ° | $^{\circ}C, V DD = 0 V$ |

|----------------|-----------|-------------------------|

|----------------|-----------|-------------------------|

| Para                  | ameter                      | Symbol | Conditions                      | MIN. | TYP. MAX. |    | Unit |

|-----------------------|-----------------------------|--------|---------------------------------|------|-----------|----|------|

| Input capacitar       | nce                         | CIN    | f = 1 MHz                       |      |           | 15 | pF   |

| Output<br>capacitance | Other than display output   | Соит   | Unmeasured pins returned to 0 V |      |           | 15 | pF   |

|                       | Display output              |        |                                 |      |           | 35 | pF   |

| Input/Output c        | nput/Output capacitance Cio |        |                                 |      |           | 15 | pF   |

# **Recommended Oscillation Circuit Constants**

# Main System Clock: Ceramic Resonator (T\_a = -40 to +70 $^\circ\text{C})$

| Manufacturer | Dentaurahan   | Frequency   | Capacita | ance (pF) | Oscillation | voltage (V) |

|--------------|---------------|-------------|----------|-----------|-------------|-------------|

| Manufacturer | Part number   | (MHz)       | MIN.     | MAX.      | MIN.        | MAX.        |

| Murata       | CSA×××MG      | 2.00 - 2.44 | 30       | 30        | 2.7         | 6.0         |

|              | CST×××MT      |             | On-chip  | On-chip   |             |             |

|              | CSA×××MG093   | 2.45 - 3.50 | 30       | 30        |             |             |

|              | CST×××MGW093  |             | On-chip  | On-chip   |             |             |

|              | CSA×××MGU     | 2.51 - 6.00 | 30       | 30        |             |             |

|              | CST×××MGWU    |             | On-chip  | On-chip   |             |             |

|              | CSA×××MG      | 2.45 - 3.50 | 30       | 30        | 3.0         |             |

|              | CST×××MGW     |             | On-chip  | On-chip   |             |             |

|              | CSA×××MG      | 2.51 - 6.00 | 30       | 30        | 3.3         |             |

|              | CST×××MGW     |             | On-chip  | On-chip   |             |             |

| Kyocera      | KBR – 2.0MS   | 2.0         | 47       | 47        | 2.7         | 6.0         |

|              | KBR – 4.0MWS  | 4.0         | 33       | 33        |             |             |

|              | KBR – 4.19MWS | 4.19        |          |           |             |             |

|              | KBR – 6.0MWS  | 6.0         |          |           |             |             |

# DC Characteristics (Ta = -40 to +70 °C, V dd = 2.7 to 6.0 V)

| Parameter                         | Symbol                                                  | C                                            | onditions                                                         |                                                 | MIN.                  | TYP. | MAX. | Unit |

|-----------------------------------|---------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------|-----------------------|------|------|------|

| High-level input voltage          | V <sub>IH1</sub>                                        | All except ports 0, 1, 6; X1, X2, XT1, RESET |                                                                   |                                                 | 0.7V <sub>DD</sub>    |      | VDD  | V    |

|                                   | V <sub>IH2</sub>                                        | Port 0, 1, RESET                             |                                                                   |                                                 | 0.75VDD               |      | VDD  | V    |

|                                   | VIH3                                                    | X1, X2, XT1                                  |                                                                   |                                                 | V <sub>DD</sub> - 0.4 |      | VDD  | V    |

|                                   | VIH4                                                    | Port 6                                       | V <sub>DD</sub> = 4.5 to 6                                        | .0 V                                            | 0.65VDD               |      | VDD  | V    |

|                                   |                                                         |                                              |                                                                   |                                                 | 0.7V <sub>DD</sub>    |      | VDD  | V    |

| Low-level input voltage           | VIL1                                                    | All except ports 0, 1, 6;                    | 0                                                                 |                                                 | 0.3VDD                | V    |      |      |

|                                   | VIL2                                                    | Port 0, 1, 6, RESET                          | 0                                                                 |                                                 | 0.2VDD                | V    |      |      |

|                                   | VIL3                                                    | X1, X2, XT1                                  |                                                                   |                                                 | 0                     |      | 0.4  | V    |

| High-level output voltage         | Vон                                                     | All outputs                                  | V <sub>DD</sub> = 4.5 to 6                                        | .0 V, Іон = –1 mA                               | V <sub>DD</sub> - 1.0 |      |      | V    |

|                                   |                                                         |                                              |                                                                   | Іон = -100 <i>µ</i> А                           | V <sub>DD</sub> - 0.5 |      |      | V    |

| Low-level output voltage          | Vol                                                     | Port 4, 5                                    | V <sub>DD</sub> = 4.5 to 6                                        | .0 V, IoL = 15 mA                               |                       | 0.4  | 2.0  | V    |

|                                   |                                                         | All outputs                                  | V <sub>DD</sub> = 4.5 to 6.0 V, I <sub>OL</sub> = 1.6 mA          |                                                 |                       |      | 0.4  | V    |

|                                   |                                                         |                                              | Ιοι = 400 μΑ                                                      |                                                 |                       |      | 0.5  | V    |

| High-level input leakage          | Ішні                                                    | All except X1, X2, XT1                       | cept X1, X2, XT1 V <sub>IN</sub> = V <sub>DD</sub>                |                                                 |                       |      | 3    | μA   |

| current                           | ILIH2                                                   | X1, X2, XT1                                  |                                                                   |                                                 |                       |      | 20   | μA   |

| Low-level input leakage           | rel input leakage IuL1 All except X1, X2, XT1 VIN = 0 V |                                              |                                                                   |                                                 |                       | -3   | μA   |      |

| current                           | ILIL2                                                   | X1, X2, XT1                                  |                                                                   |                                                 |                       |      | -20  | μA   |

| High-level output leakage current | Ігон                                                    | All outputs                                  | Vout = Vdd                                                        |                                                 |                       |      | 3    | μA   |

| Low-level output leakage current  | ILOL1                                                   | All except display<br>outputs                | Vout = 0 V                                                        |                                                 |                       |      | -3   | μA   |

|                                   | ILOL2                                                   | Display outputs                              | $V_{\text{OUT}} = V_{\text{LOAD}} = V_{\text{DD}} - 35 \text{ V}$ |                                                 |                       |      | -10  | μA   |

| Display output current            | Іор                                                     | S0-S9                                        | V <sub>DD</sub> = 4.5 to 6.                                       | .0 V                                            | -3                    | -5.5 |      | mA   |

|                                   |                                                         | T0-T15                                       | $V_{OD} = V_{DD} - 2$                                             | V                                               | -15                   | -22  |      | mA   |

| On-chip pull-down resistor        | R∟                                                      | Display outputs                              | Vod - Vload = 3                                                   | 35 V                                            | 25                    | 70   | 135  | kΩ   |

| Note 1                            | IDD1                                                    | 6.0 MHz crystal                              | $V_{DD} = 5 V \pm 10$                                             | ) % Note 2                                      |                       | 6.5  | 18.0 | mA   |

| Power supply current              |                                                         | oscillator                                   | $V_{DD} = 3 V \pm 10$                                             | ) % Note 3                                      |                       | 0.85 | 2.5  | mA   |

|                                   | IDD2                                                    |                                              | HALT mode                                                         | $V_{\text{DD}} = 5 \text{ V} \pm 10 \text{ \%}$ |                       | 1350 | 4000 | μA   |

|                                   |                                                         |                                              |                                                                   | $V_{\text{DD}}$ = 3 V $\pm$ 10 %                |                       | 450  | 1350 | μA   |

|                                   | IDD1                                                    | 4.19 MHz crystal                             | $V_{DD} = 5 \text{ V} \pm 10$                                     | ) % Note 2                                      |                       | 4.0  | 12.0 | mA   |

|                                   |                                                         | oscillator                                   | $V_{DD} = 3 V \pm 10$                                             | ) % Note 3                                      |                       | 0.55 | 1.5  | mA   |

|                                   | IDD2                                                    | C1 = C2 = 15 pF                              | HALT mode                                                         | $V_{\text{DD}}$ = 5 V $\pm$ 10 %                |                       | 900  | 2700 | μA   |

|                                   |                                                         |                                              |                                                                   | $V_{\text{DD}}$ = 3 V $\pm$ 10 %                |                       | 300  | 900  | μA   |

|                                   | Пррз                                                    | Note 4                                       | $V_{DD} = 3 V \pm 10$                                             | ) %                                             |                       | 100  | 300  | μA   |

|                                   | IDD4                                                    | 32kHz crystal                                | HALT mode                                                         | $V_{\text{DD}}$ = 3 V $\pm$ 10 %                |                       | 20   | 60   | μA   |

|                                   |                                                         | oscillator                                   | STOP mode                                                         | $V_{\text{DD}}=3~V\pm10~\%$                     |                       | 5    | 15   | μA   |

|                                   | IDD5                                                    | XT1 = 0 V                                    | $V_{DD} = 5 V \pm 10$                                             | ) %                                             |                       | 0.5  | 20   | μA   |

|                                   |                                                         | STOP mode                                    | $V_{DD} = 3 V \pm 10$                                             | ) %                                             |                       | 0.1  | 10   | μA   |

Notes 1. Does not include pull-down resistor current.

- 2. Value during high-speed operation and when the processor clock control (PCC) register is set to 0011.

- 3. Value during low-speed operation and when the PCC register is set to 0000.

- **4.** Value when the system clock control register (SCC) is set to 1001, generation of the main system clock pulse is stopped, and the CPU is operated by the subsystem clock pulse.

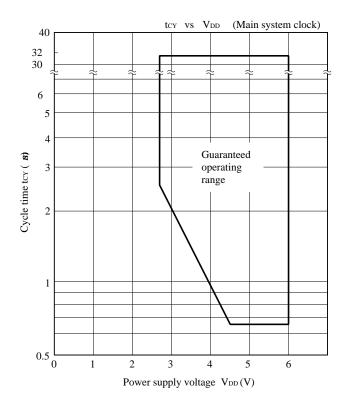

# AC Characteristics (T\_a = -40 to +70 $^\circ\text{C},$ V $_{DD}$ = 2.7 to 6.0 V)

| Parameter                                                             | Symbol | Сог                                  | nditions              |          | MIN.       | TYP. | MAX. | Unit |

|-----------------------------------------------------------------------|--------|--------------------------------------|-----------------------|----------|------------|------|------|------|

| Note 1                                                                | tcy    | Main system                          | V <sub>DD</sub> = 4.5 | to 6.0 V | 0.67       |      | 32   | μs   |

| CPU clock cycle time                                                  |        | clock                                |                       |          | 2.6        |      | 32   | μs   |

| (minimum instruction execu-<br>tion time = 1 machine cycle)           |        | Subsystem<br>clock                   |                       |          | 114        | 122  | 125  | μs   |

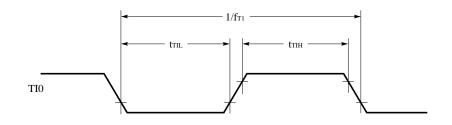

| TI0 input frequency                                                   | fтı    | $V_{DD} = 4.5 \text{ to } 6.0$       | V                     |          | 0          |      | 0.6  | MHz  |

|                                                                       |        |                                      |                       |          | 0          |      | 165  | kHz  |

| TI0 input low- and high-level                                         | tтıн,  | $V_{DD} = 4.5 \text{ to } 6.0$       | V                     |          | 0.83       |      |      | μs   |

| width                                                                 | t⊤ı∟   |                                      |                       |          | 3          |      |      | μs   |

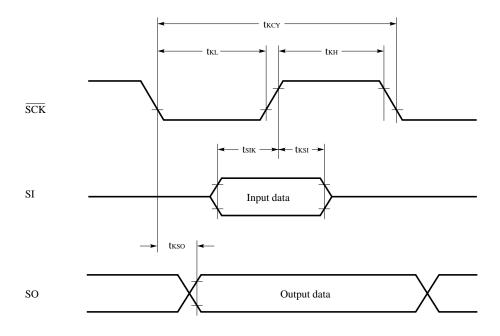

| SCK cycle time                                                        | tксү   | V <sub>DD</sub> = 4.5 to 6.0 V Input |                       | 0.8      |            |      | μs   |      |

|                                                                       |        |                                      |                       | Output   |            |      |      | μs   |

|                                                                       |        |                                      |                       | Input    | 3.2        |      |      | μs   |

|                                                                       |        |                                      |                       | Output   | 3.8        |      |      | μs   |

| SCK low- and high-level width                                         | tкн,   | $V_{DD} = 4.5$ to 6.0                | V                     | Input    | 0.4        |      |      | μs   |

|                                                                       | tĸ∟    |                                      |                       | Output   | tксу/2–50  |      |      | ns   |

|                                                                       |        |                                      |                       | Input    | 1.6        |      |      | μs   |

|                                                                       |        |                                      |                       | Output   | tксу/2–150 |      |      | ns   |

| SI setup time (to SCK $\uparrow$ )                                    | tsıк   |                                      |                       |          | 100        |      |      | ns   |

| SI hold time (from $\overline{SCK} \uparrow$ )                        | tκsı   |                                      |                       |          | 400        |      |      | ns   |

| $\overline{\text{SCK}} \downarrow \rightarrow \text{SO}$ output delay | tκso   | $V_{DD} = 4.5$ to 6.0                | V                     |          |            |      | 300  | ns   |

| time                                                                  |        |                                      |                       | -        |            |      | 1000 | ns   |

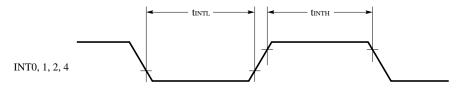

| Interrupt inputs                                                      | tinth, |                                      |                       | INT0     | Note 2     |      |      | μs   |

| low- and high-level width                                             | tintl  |                                      |                       | INT1     | 2tcy       |      |      | μs   |

|                                                                       |        |                                      |                       | INT2,4   | 10         |      |      | μs   |

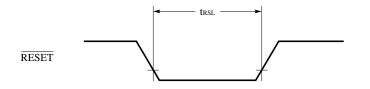

| RESET low-level width                                                 | trsl   |                                      |                       |          | 10         |      |      | μs   |

- NEC

- Notes 1. The CPU clock  $(\Phi)$  cycle time is determined by the oscillator frequency of the connected resonator, the system clock control register (SCC), and the processor clock control register (PCC).

The right chart shows the cycle time tcy characteristics for power supply voltage  $V_{DD}$  during the main system clock operation.

**2.** 2tcy or 128/fxx, depending on the setting of the interrupt mode register (IM0).

# AC Timing Test Points (Except X1, XT1)

**Clock Timing**

**TI0** Timing

# Serial Transfer Timing

# Interrupt Input Timing

**RESET** Input Timing

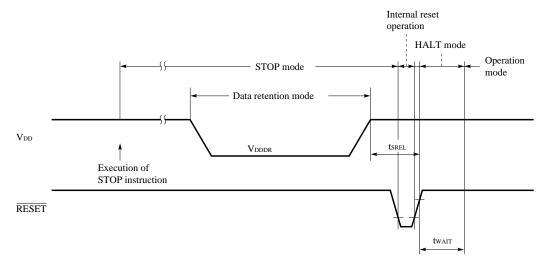

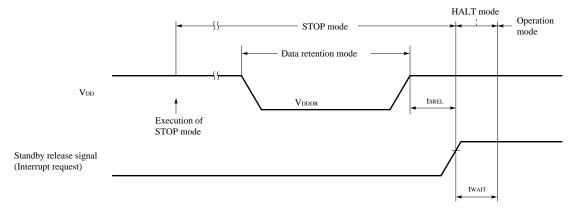

# Data Memory STOP Mode Low Voltage Data Retention Characteristics (Ta = -40 to +70 °C)

| Parameter                             | Symbol        | Conditions                   | MIN. | TYP.                            | MAX. | Unit |

|---------------------------------------|---------------|------------------------------|------|---------------------------------|------|------|

| Data retention voltage                | VDDDR         |                              | 2.0  |                                 | 6.0  | V    |

| Data retention current Note 1         | Idddr         | $V_{DDDR} = 2.0 V$           |      | 0.1                             | 10   | μA   |

| Release signal SET time               | <b>t</b> SREL |                              | 0    |                                 |      | μs   |

| Oscillation stabilization time Note 2 | twait         | Release by RESET input       |      | 2 <sup>17</sup> /f <sub>x</sub> |      | ms   |

|                                       |               | Release by interrupt request |      | Note 3                          |      | ms   |

Notes 1. Does not include pull-down resistor current.

- **2.** The oscillation stabilization WAIT time is the time during which the CPU operation is stopped to prevent unstable operation while the oscillation is started.

- **3.** The WAIT time depends on the setting of the basic interval timer mode register (BTM) according to the following table.

| BTM3 BTM2 BTN | BTM1   | DTMO   | WAIT time |                                        |                                        |  |  |

|---------------|--------|--------|-----------|----------------------------------------|----------------------------------------|--|--|

| D I WI3       | DIIVIZ | DIIVII | BTM0      | (fxx = 6.0  MHz)                       | (fxx = 4.19 MHz)                       |  |  |

| -             | 0      | 0      | 0         | 2 <sup>20</sup> /fxx (approx. 175 ms)  | 2 <sup>20</sup> /fxx (approx. 250 ms)  |  |  |

| -             | 0      | 1      | 1         | 2 <sup>17</sup> /fxx (approx. 21.8 ms) | 2 <sup>17</sup> /fxx (approx. 31.3 ms) |  |  |

| -             | 1      | 0      | 1         | 2 <sup>15</sup> /fxx (approx. 5.46 ms) | 2 <sup>15</sup> /fxx (approx. 7.82 ms) |  |  |

| -             | 1      | 1      | 1         | 2 <sup>13</sup> /fxx (approx. 1.37 ms) | 2 <sup>13</sup> /fxx (approx. 1.95 ms) |  |  |

# Data Retention Timing (STOP mode is released by RESET input)

# Data Retention Timing (STOP mode is released by interrupt signal)

# DC Programming Characteristics (Ta = $25 \pm 5$ °C, V DD = $6.0 \pm 0.25$ V, VPP = $12.5 \pm 0.3$ V, Vss = 0 V)ParameterSymbolConditionsMIN.TYP.MAX.Unit

| Parameter                 | Symbol | Conditions           | MIN.      | TYP. | MAX.   | Unit |

|---------------------------|--------|----------------------|-----------|------|--------|------|

| High-level input voltage  | VIH1   | All except X1, X2    | 0.7VDD    |      | Vdd    | V    |

|                           | VIH2   | X1, X2               | VDD - 0.5 |      | Vdd    | V    |

| Low-level input voltage   | VIL1   | All except X1, X2    | 0         |      | 0.3VDD | V    |

|                           | VIL2   | X1, X2               | 0         |      | 0.4    | V    |

| Input leakage current     | lu     | VIN = VIL OF VIH     |           |      | 10     | μA   |

| High-level output voltage | Vон    | Іон = –1 mA          | Vdd - 1.0 |      |        | V    |

| Low-level output voltage  | Vol    | lo∟ = 1.6 mA         |           |      | 0.4    | V    |

| VDD power supply current  | loo    |                      |           |      | 30     | mA   |

| VPP power supply current  | Ірр    | MD0 = VIL, MD1 = VIH |           |      | 30     | mA   |

# Cautions 1. VPP must not exceed +13.5 V, including overshoot.

# 2. VDD is to be applied prior to VPP and to be removed after VPP is removed.

| Parameter                                                 | Symbol           | Note 1 | Conditions                                  | MIN.  | TYP. | MAX. | Unit |

|-----------------------------------------------------------|------------------|--------|---------------------------------------------|-------|------|------|------|

| Address setup time Note 2 (to MD0 $\downarrow$ )          | tas              | tas    |                                             | 2     |      |      | μs   |

| MD1 setup time (to MD0 $\downarrow$ )                     | T <sub>M1S</sub> | toes   |                                             | 2     |      |      | μs   |